("глубокое понижение энергопитания"). Это режим минимального энергопотребления, когда в процессоре

отключено максимальное количество функциональных блоков.Penryn поддерживает технологию Dynamic Acceleration. Она заключается в том, что когда одно из ядер не задействовано, оно может отключаться, в то время, как второе может работать даже на повышенной от номинала частоте до тех пор, пока тепловыделение процессора находится в рамках установленного производителем TDP.

Тактовые частоты некоторых настольных и серверных процессоров с микроархитектурой Penryn превышают 3 ГГц.

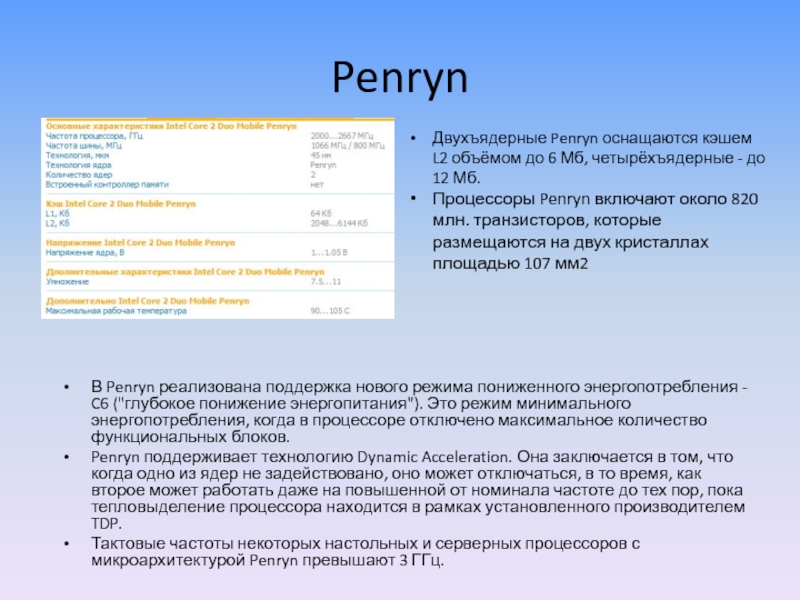

Двухъядерные Penryn оснащаются кэшем L2 объёмом до 6 Мб, четырёхъядерные - до 12 Мб.

Процессоры Penryn включают около 820 млн. транзисторов, которые размещаются на двух кристаллах площадью 107 мм2