Слайд 1Проектирование центральных и периферийных устройств ЭВС

Слайд 2Литература для изучения материала

Таненбаум «Архитектура компьютера»

Поворознюк «Архитектура компьютеров» в2-х частях

Цилькер,

Орлов «Организация ЭВМ и систем»

Хамахер, Вранешич, Заки «Организация ЭВМ»

Пескова, Гуров,

Кузин «Центральные и периферийные устройства электронных вычислительных средств»

Тихонов, Баранов «Организация ЭВМ и систем»

Гук «Аппаратные средства IBM PC. Энциклопедия»

Хорошевский «Архитектура вычислительных систем»

Слайд 3Принцип работы устройства управления

Слайд 4Способы адресации информации

Способом адресации называется механизм получения исполнительного адреса из

исходного.

Применение различных способов адресации обусловлено причинами:

- необходимость получения наименьшей разрядности

адресного поля команды при адресации оперативной памяти большой емкости;

- требование удобства адресации элементов массивов данных в циклических программах;

- необходимость обеспечения возможности написания программ, перемещаемых программ, не зависящих от абсолютных адресов памяти.

Слайд 5Способы адресации информации

Непосредственная адресация – способ адресации, при котором в

адресном поле команды размещается сам операнд, подлежащий обработке;

Прямая адресация –

способ адресации, при котором исполнительный адрес совпадает с исходным;

Регистровая адресация - используется для обращения к рабочим регистрам выбранного банка рабочих регистров. Команды с регистровой адресацией содержат в коде операции поле, которое определяет номер регистра;

Косвенная адресация – в адресном поле команды указывают адрес ячейки памяти, в которой хранится исполнительный адрес;

Относительная адресация (в некоторых случаях называемая индексной) – исходный адрес состоит из адреса индекса Ax и смещения D. Адрес индекса является номером регистра или адресом ячейки), где хранится значение индекса Х. Исполнительный адрес AE при относительной адресации получают посредством сложения содержимого регистра или ячейки (AX)=Х, указываемых адресом индекса AX, и смещения D, т.е. AE =(AX) + D = X + D;

Неявная адресация - подразумевает, что адрес к регистрам или памяти не указывается при помощи операнда. Адрес регистра определяется самой инструкцией и содержится в коде операции;

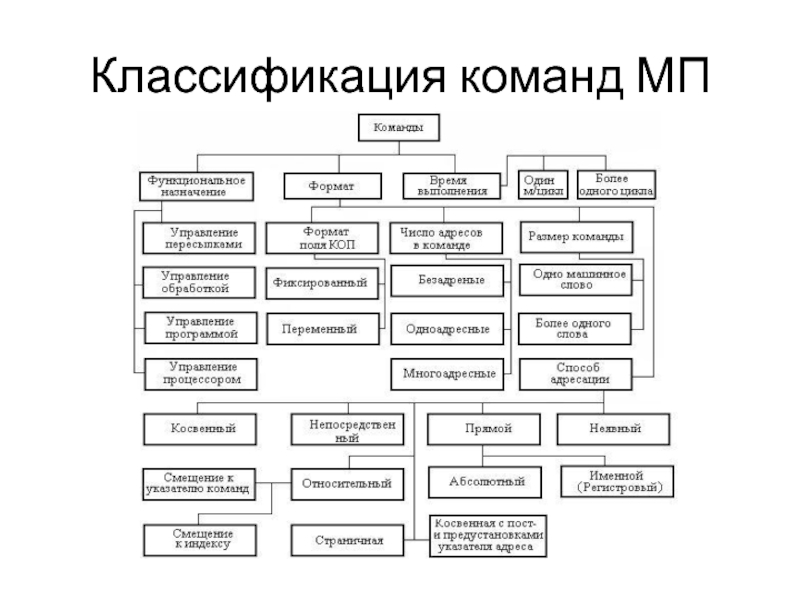

Слайд 6Классификация устройств управления

Функциональная ориентация – универсальные УУ, специализированные УУ;

Принцип организации

цикла выполнения команды – синхронные УУ, асинхронные УУ, смешанные (синхронно-асинхронные)

УУ;

Количество уровней управления – одноуровневые УУ, многоуровневые УУ;

Метод хранения программы – УУ с внутренним хранением программ, УУ с внешним хранением программ;

Порядок следования команд программы – УУ с естественным порядком следования команд, УУ с принудительным порядком следования команд;

Формат реализуемых команд – одноадресные, двухадресные, трехадресные УУ, УУ с переменной адресностью команд; безадресные УУ;

Способ реализации команд – централизованные УУ, распределенные УУ;

Способ построения управляющего автомата – схемные УУ, микропрограммные УУ.

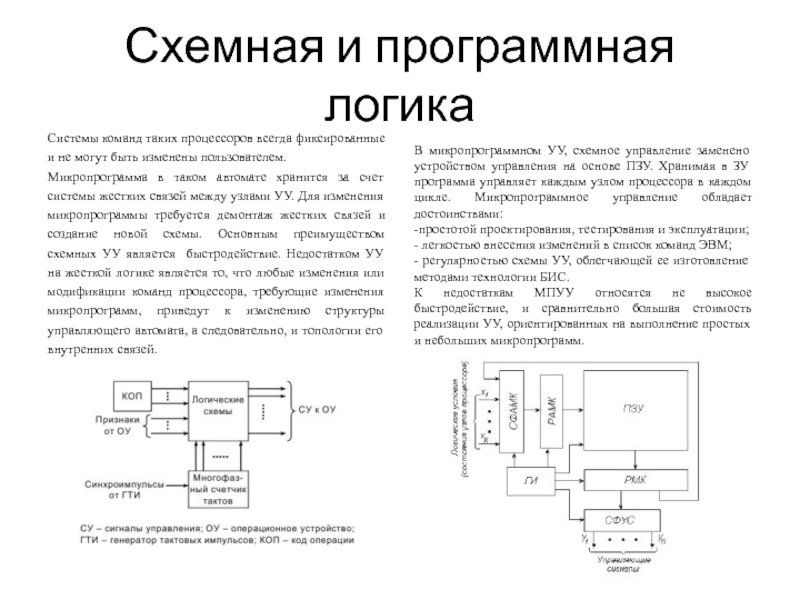

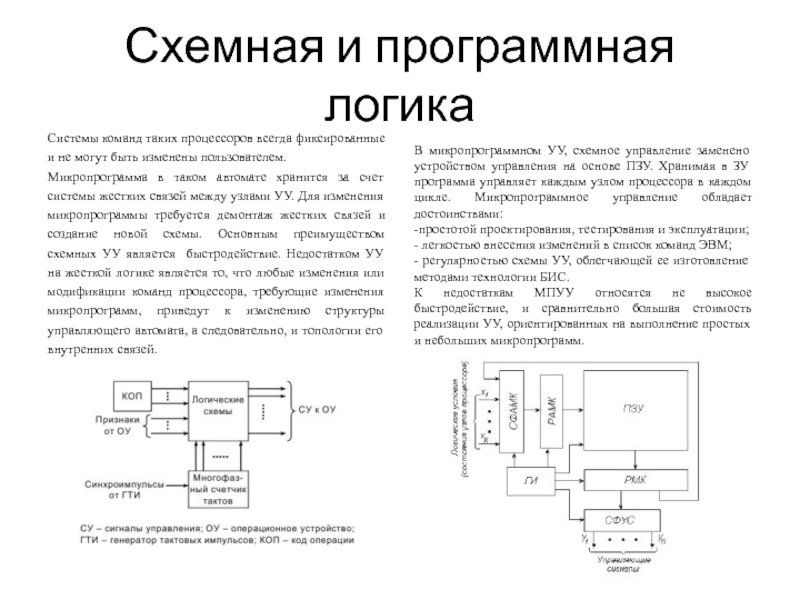

Слайд 7Схемная и программная логика

Системы команд таких процессоров всегда фиксированные и

не могут быть изменены пользователем.

Микропрограмма в таком автомате хранится

за счет системы жестких связей между узлами УУ. Для изменения микропрограммы требуется демонтаж жестких связей и создание новой схемы. Основным преимуществом схемных УУ является быстродействие. Недостатком УУ на жесткой логике является то, что любые изменения или модификации команд процессора, требующие изменения микропрограмм, приведут к изменению структуры управляющего автомата, а следовательно, и топологии его внутренних связей.

В микропрограммном УУ, схемное управление заменено устройством управления на основе ПЗУ. Хранимая в ЗУ программа управляет каждым узлом процессора в каждом цикле. Микропрограммное управление обладает достоинствами:

-простотой проектирования, тестирования и эксплуатации;

- легкостью внесения изменений в список команд ЭВМ;

- регулярностью схемы УУ, облегчающей ее изготовление методами технологии БИС.

К недостаткам МПУУ относятся не высокое быстродействие, и сравнительно большая стоимость реализации УУ, ориентированных на выполнение простых и небольших микропрограмм.

Слайд 8Компоненты процессорной системы

Слайд 9Регистровая структура ЦП

Программно-доступные регистры разделяются на:

регистры общего назначения;

сегментные

регистры;

регистр флагов;

указатель команды.

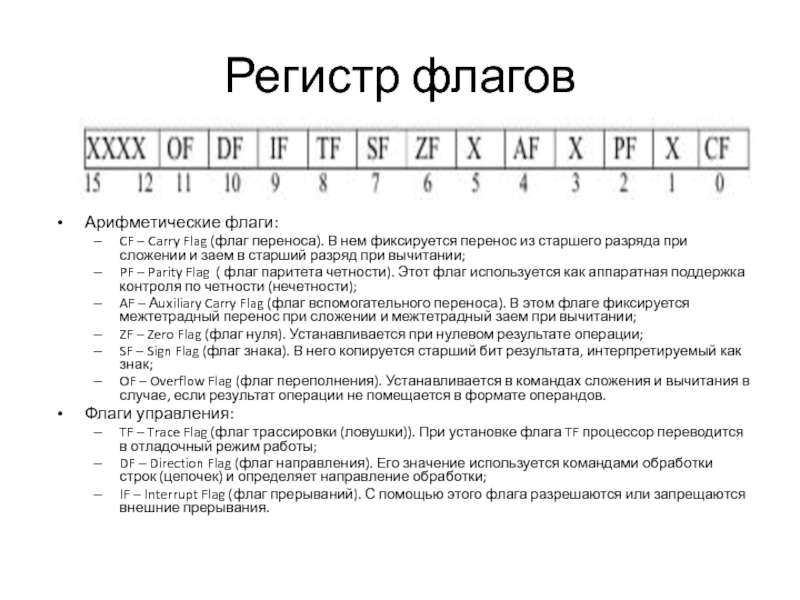

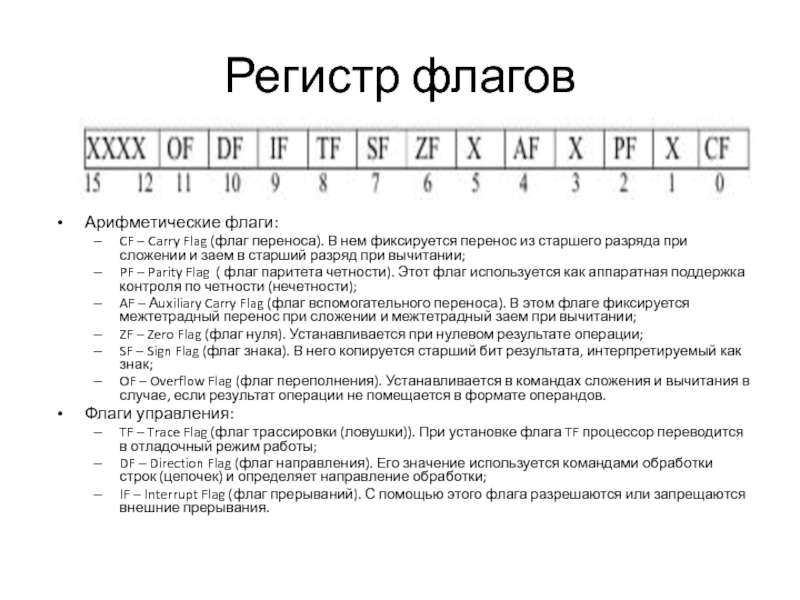

Слайд 10Регистр флагов

Арифметические флаги:

CF – Carry Flag (флаг переноса). В нем

фиксируется перенос из старшего разряда при сложении и заем в

старший разряд при вычитании;

PF – Parity Flag ( флаг паритета четности). Этот флаг используется как аппаратная поддержка контроля по четности (нечетности);

AF – Аuxiliary Carry Flag (флаг вспомогательного переноса). В этом флаге фиксируется межтетрадный перенос при сложении и межтетрадный заем при вычитании;

ZF – Zero Flag (флаг нуля). Устанавливается при нулевом результате операции;

SF – Sign Flag (флаг знака). В него копируется старший бит результата, интерпретируемый как знак;

OF – Overflow Flag (флаг переполнения). Устанавливается в командах сложения и вычитания в случае, если результат операции не помещается в формате операндов.

Флаги управления:

TF – Trace Flag (флаг трассировки (ловушки)). При установке флага TF процессор переводится в отладочный режим работы;

DF – Direction Flag (флаг направления). Его значение используется командами обработки строк (цепочек) и определяет направление обработки;

IF – Interrupt Flag (флаг прерываний). С помощью этого флага разрешаются или запрещаются внешние прерывания.

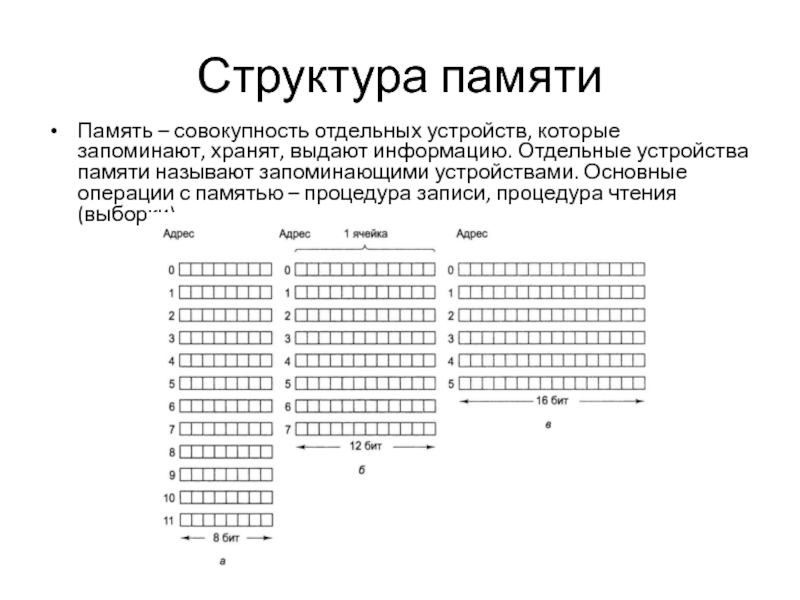

Слайд 13Структура памяти

Память – совокупность отдельных устройств, которые запоминают, хранят, выдают

информацию. Отдельные устройства памяти называют запоминающими устройствами. Основные операции с

памятью – процедура записи, процедура чтения (выборки).

Слайд 14Структура памяти

Под физической ОП понимают конкретное физическое устройство памяти, адресация

в котором осуществляется в соответствии с используемой схемой дешифрации адреса

и управления выборкой данных.

Под реальной ОП понимают устройство ОП, для которого может быть установлено соответствие между адресами обращения и выборкой информации. Объем реальной ОП не превышает объема физической памяти.

Виртуальная ОП — это память, границы которой определяются допустимым адресным пространством. Объем ВП может значительно превышать объем реальной ОП.

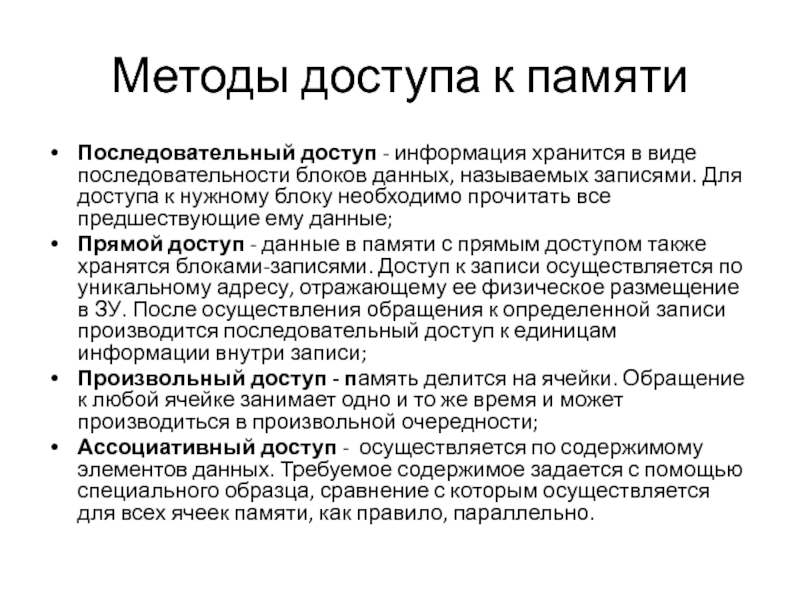

Слайд 15Методы доступа к памяти

Последовательный доступ - информация хранится в виде

последовательности блоков данных, называемых записями. Для доступа к нужному блоку

необходимо прочитать все предшествующие ему данные;

Прямой доступ - данные в памяти с прямым доступом также хранятся блоками-записями. Доступ к записи осуществляется по уникальному адресу, отражающему ее физическое размещение в ЗУ. После осуществления обращения к определенной записи производится последовательный доступ к единицам информации внутри записи;

Произвольный доступ - память делится на ячейки. Обращение к любой ячейке занимает одно и то же время и может производиться в произвольной очередности;

Ассоциативный доступ - осуществляется по содержимому элементов данных. Требуемое содержимое задается с помощью специального образца, сравнение с которым осуществляется для всех ячеек памяти, как правило, параллельно.

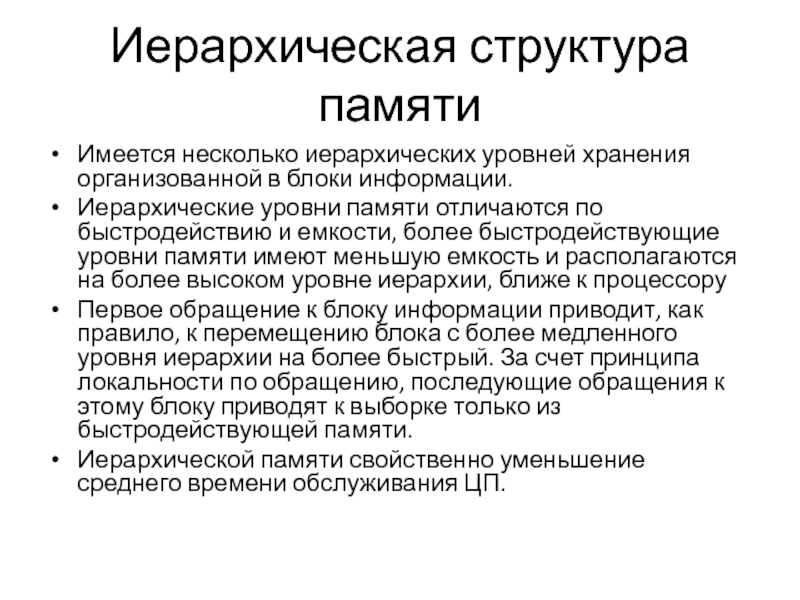

Слайд 17Иерархическая структура памяти

Имеется несколько иерархических уровней хранения организованной в блоки

информации.

Иерархические уровни памяти отличаются по быстродействию и емкости, более быстродействующие

уровни памяти имеют меньшую емкость и располагаются на более высоком уровне иерархии, ближе к процессору

Первое обращение к блоку информации приводит, как правило, к перемещению блока с более медленного уровня иерархии на более быстрый. За счет принципа локальности по обращению, последующие обращения к этому блоку приводят к выборке только из быстродействующей памяти.

Иерархической памяти свойственно уменьшение среднего времени обслуживания ЦП.

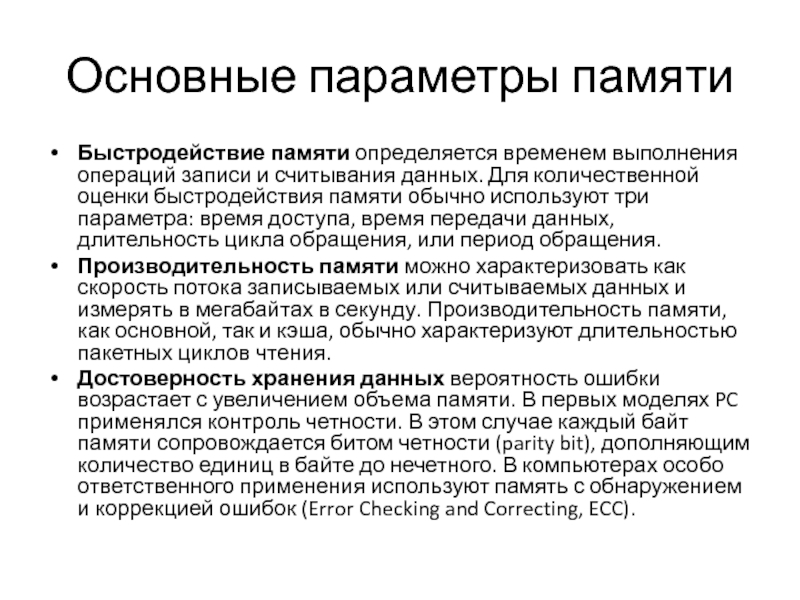

Слайд 18Основные параметры памяти

Быстродействие памяти определяется временем выполнения операций записи и

считывания данных. Для количественной оценки быстродействия памяти обычно используют три

параметра: время доступа, время передачи данных, длительность цикла обращения, или период обращения.

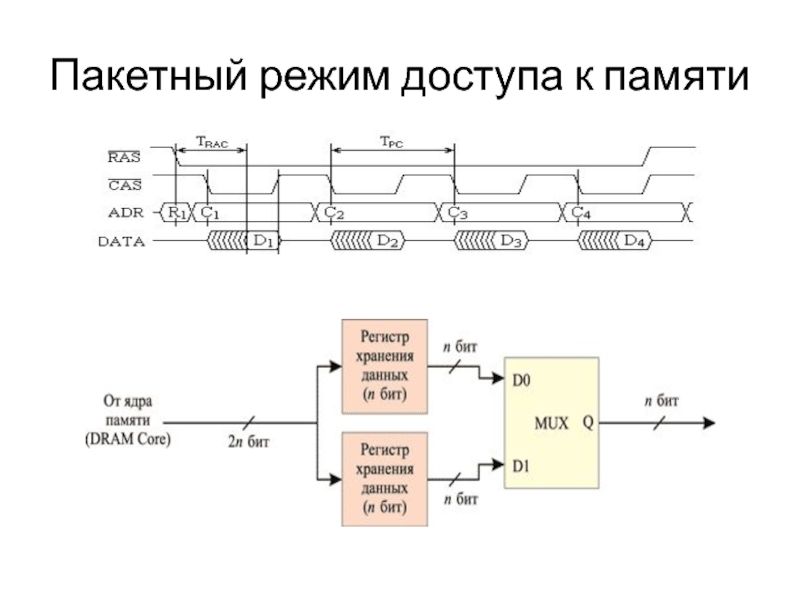

Производительность памяти можно характеризовать как скорость потока записываемых или считываемых данных и измерять в мегабайтах в секунду. Производительность памяти, как основной, так и кэша, обычно характеризуют длительностью пакетных циклов чтения.

Достоверность хранения данных вероятность ошибки возрастает с увеличением объема памяти. В первых моделях PC применялся контроль четности. В этом случае каждый байт памяти сопровождается битом четности (parity bit), дополняющим количество единиц в байте до нечетного. В компьютерах особо ответственного применения используют память с обнаружением и коррекцией ошибок (Error Checking and Correcting, ECC).

Слайд 19Статическая память

SRAM – энергозависимая память, обладает очень малым временем доступа,

основана на использовании триггеров в качестве запоминающего элемента.

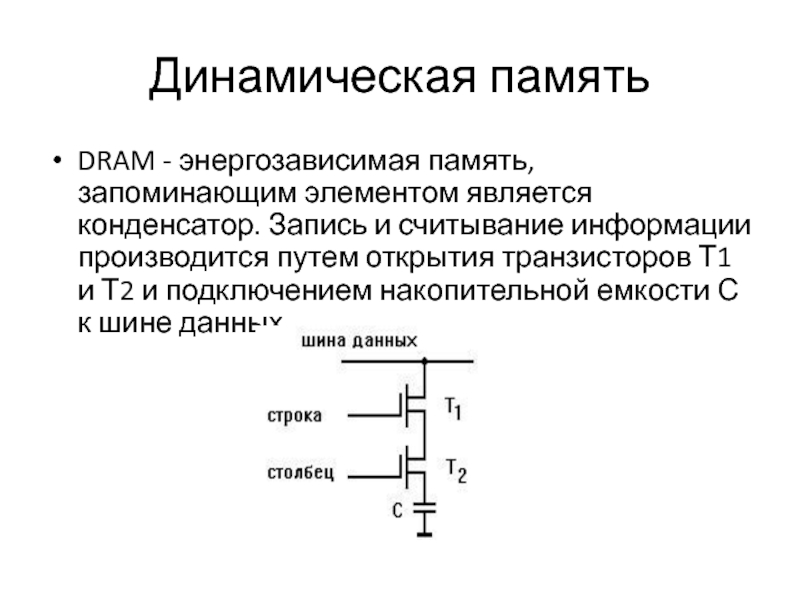

Слайд 20Динамическая память

DRAM - энергозависимая память, запоминающим элементом является конденсатор. Запись

и считывание информации производится путем открытия транзисторов Т1 и Т2

и подключением накопительной емкости С к шине данных.

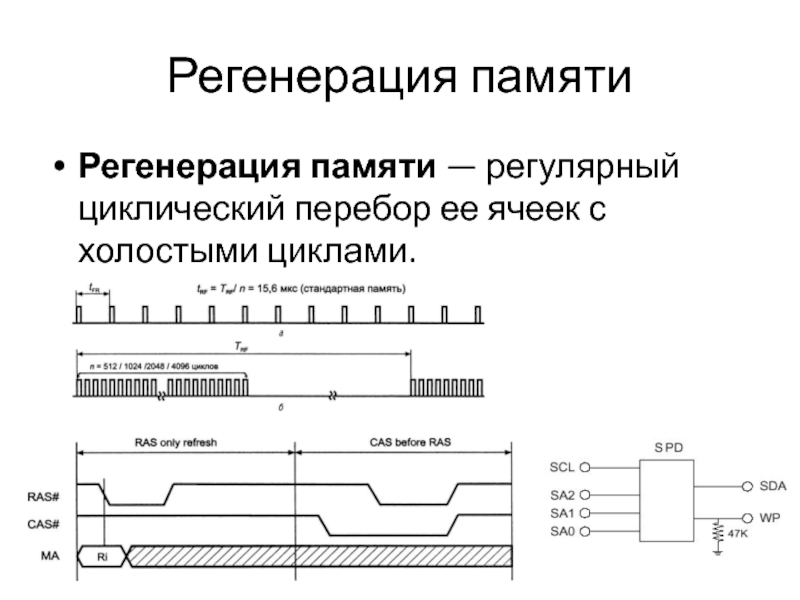

Слайд 24Регенерация памяти

Регенерация памяти — регулярный циклический перебор ее ячеек с

холостыми циклами.

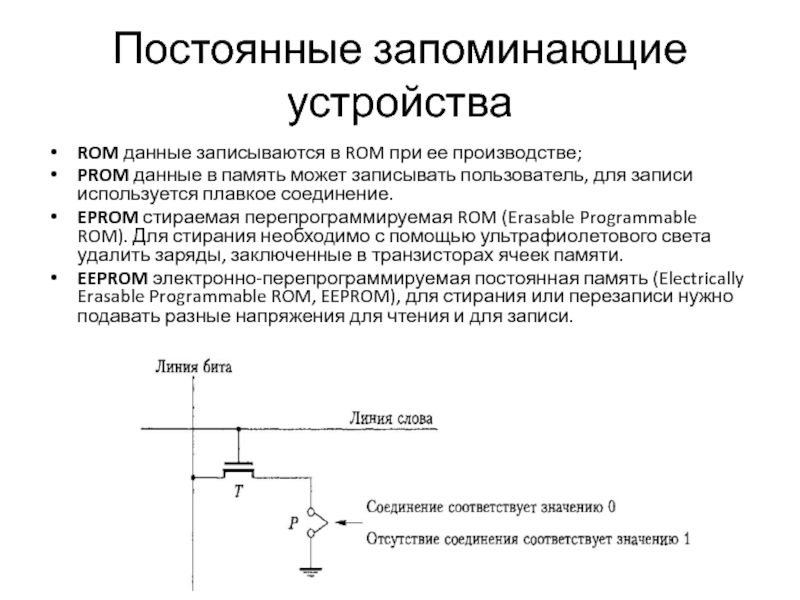

Слайд 25Постоянные запоминающие устройства

ROM данные записываются в ROM при ее производстве;

PROM

данные в память может записывать пользователь, для записи используется плавкое

соединение.

EPROM стираемая перепрограммируемая ROM (Erasable Programmable ROM). Для стирания необходимо с помощью ультрафиолетового света удалить заряды, заключенные в транзисторах ячеек памяти.

EEPROM электронно-перепрограммируемая постоянная память (Electrically Erasable Programmable ROM, EEPROM), для стирания или перезаписи нужно подавать разные напряжения для чтения и для записи.

Слайд 26Стековая память

При занесении в стек очередного слова происходит следующее:

УС:=

УС -1; ОП[(УС)]:=ШД.

При извлечении слова из стека реализуются следующие операции:

Ш

Д:= ОП[(УС)]; УС := УС +1.

Слайд 28Кэш-память

Параметры кэш-памяти:

размер строки;

способ отображения основной памяти на кэш-память;

алгоритм замещения информации

в заполненной кэш-памяти;

алгоритм согласования содержимого основной и кэш-памяти;

число уровней кэш-памяти.

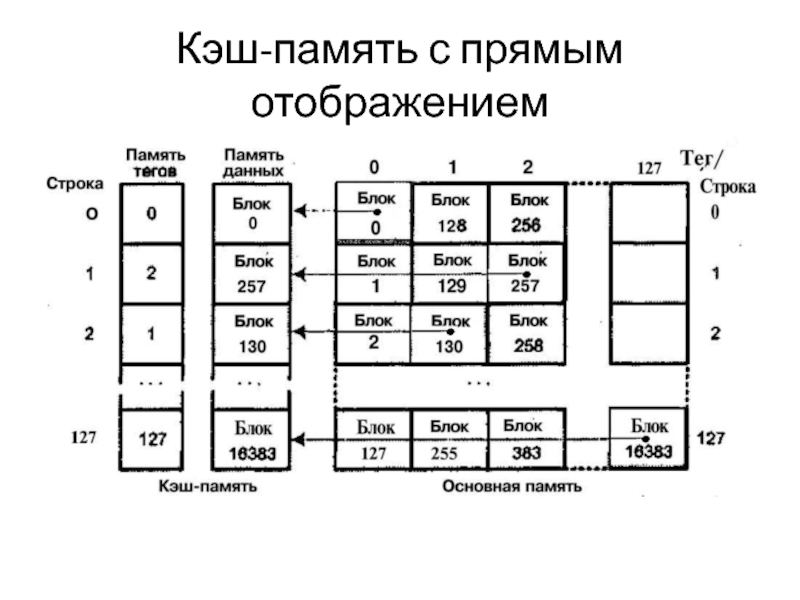

Слайд 29Кэш-память с прямым отображением

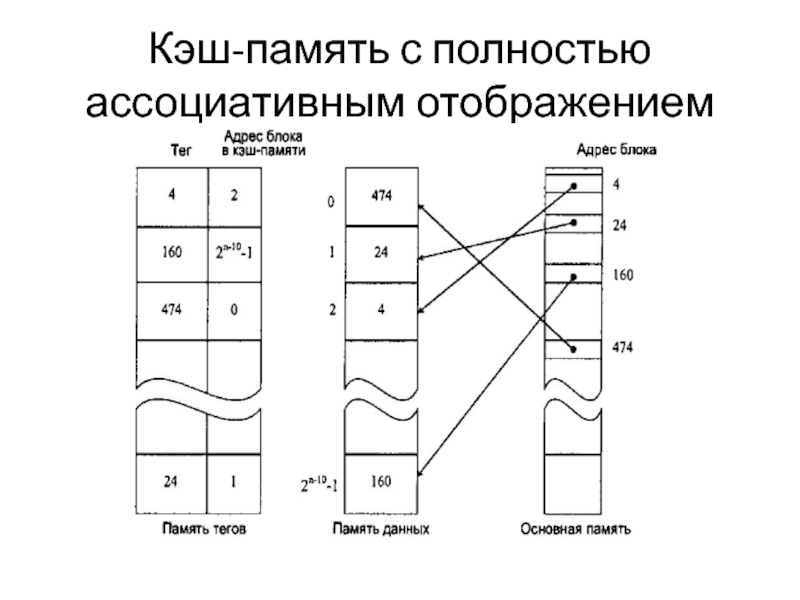

Слайд 30Кэш-память с полностью ассоциативным отображением

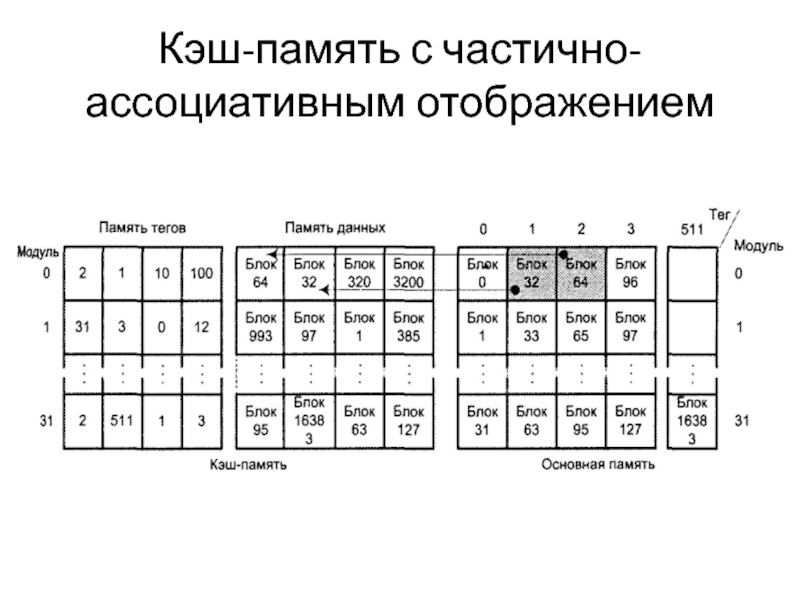

Слайд 31Кэш-память с частично-ассоциативным отображением

Слайд 32Алгоритмы замещения кэш-памяти

Алгоритм наиболее давнего использования (LRU);

Алгоритм работающий по принципу

«первый вошел, первый вышел» (FIFO);

Алгоритм наименее частого использования (LFU);

Алгоритм произвольного

выбора строки для замены.

Слайд 33Стратегии обновления основной памяти и стратегии замещения

Методы обновления ОП:

Методы сквозной

записи;

Методы обратной записи.

Стратегии замещения при промахе:

разместить записываемый блок в кэш-памяти;

не

размещать записываемый блок в кэш-памяти. Блок модифицируется в ОП и не загружается в кэшпамять.

![Проектирование центральных и периферии?ных устрои?ств ЭВС лекция 2 Стековая памятьПри занесении в стек очередного слова происходит следующее: УС:= УС Стековая памятьПри занесении в стек очередного слова происходит следующее: УС:= УС -1; ОП[(УС)]:=ШД.При извлечении слова из стека](/img/thumbs/3f3f25e07c7e86a65ec0930700c2c266-800x.jpg)