Слайд 1Для увеличения емкости ЗУ производится их каскадирование. Известны два основных

способа увеличения емкости памяти ЗУ: способ наращиваемой разрядности хранимого слова

и способ наращиваемого числа хранимых слов.

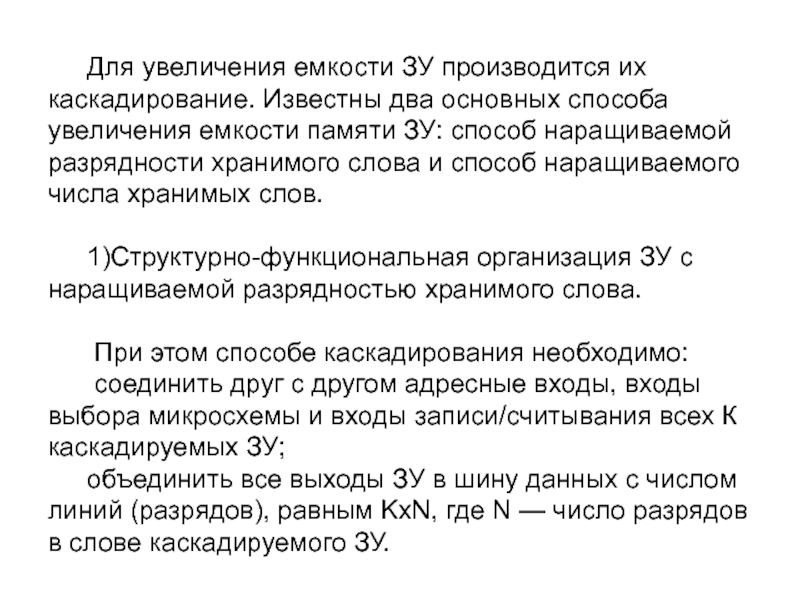

1)Структурно-функциональная организация ЗУ с наращиваемой разрядностью хранимого слова.

При этом способе каскадирования необходимо:

соединить друг с другом адресные входы, входы выбора микросхемы и входы записи/считывания всех К каскадируемых ЗУ;

объединить все выходы ЗУ в шину данных с числом линий (разрядов), равным KxN, где N — число разрядов в слове каскадируемого ЗУ.

Слайд 2

Структурно-функциональная организация ЗУ с наращиваемой разрядностью хранимого слова

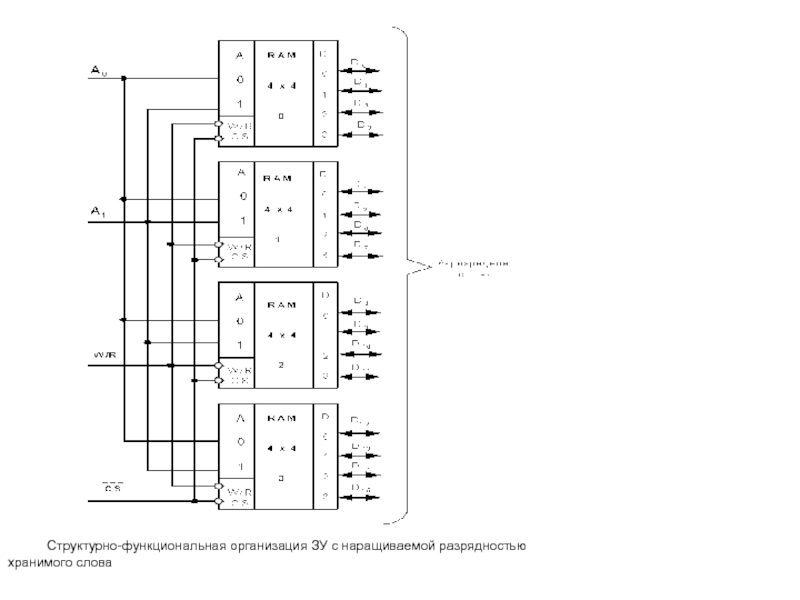

Слайд 32)Структурно-функциональная организация ЗУ с наращиваемым числом хранимых слов.

Для реализации

этого способа каскадирования ЗУ необходимо располагать, по крайней мере, одним

дешифратором. Кроме того, ЗУ должны иметь не менее одного входа выбора микросхемы.

Одноименные адресные входы А1 Ао и входы записи/ считывания W/R всех ЗУ соединены друг с другом. Входы выбора микросхемы CS запоминающих устройств RAM0-RAM3 соединены соответственно с выходами дешифратора 0-3.

Старшие разряды А3, А2 адресного кода активизируют один из выходов дешифратора, устанавливая на нем уровень логического 0. Если, например, активным является выход 2, то на вход RAM2 поступает сигнал CS = 0 и в зависимости от значения сигнала W/R происходит запись или считывание данных в ячейку памяти RAM-2, определяемую младшими разрядами A1 A0 адресного кода. Так как на входы других ЗУ поступает сигнал CS = 1, они находятся в нерабочем состоянии.

Слайд 4

Структурно-функциональная организация ЗУ с наращиваемым числом хранимых слов

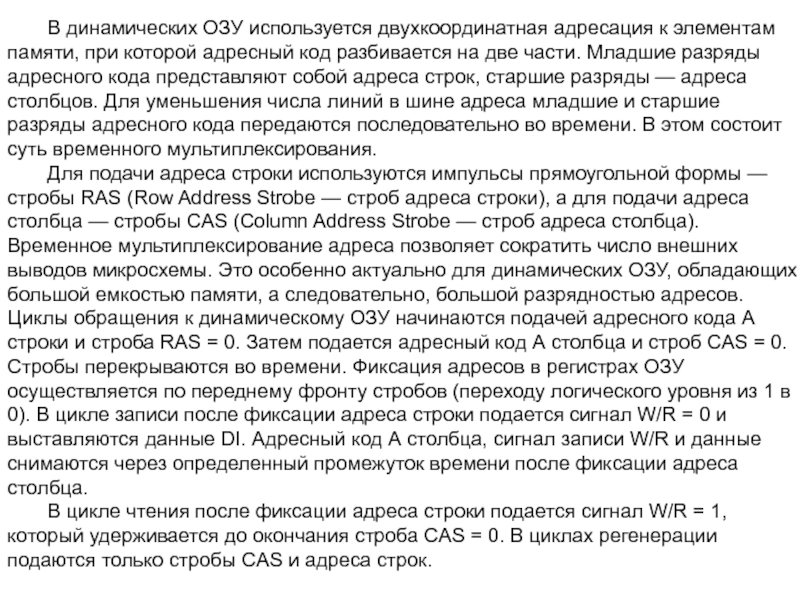

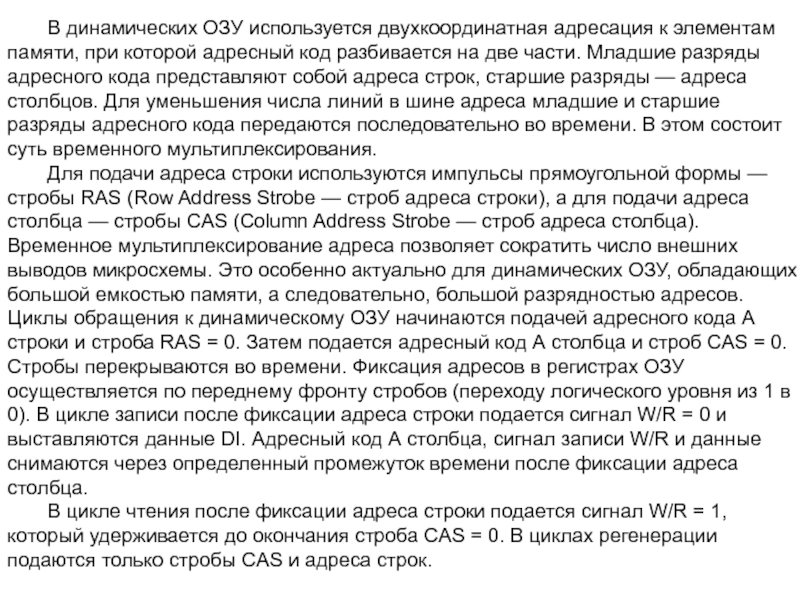

Слайд 5В динамических OЗУ используется двухкоординатная адресация к элементам памяти, при

которой адресный код разбивается на две части. Младшие разряды адресного

кода представляют собой адреса строк, старшие разряды — адреса столбцов. Для уменьшения числа линий в шине адреса младшие и старшие разряды адресного кода передаются последовательно во времени. В этом состоит суть временного мультиплексирования.

Для подачи адреса строки используются импульсы прямоугольной формы — стробы RAS (Row Address Strobe — строб адреса строки), а для подачи адреса столбца — стробы CAS (Column Address Strobe — строб адреса столбца). Временное мультиплексирование адреса позволяет сократить число внешних выводов микросхемы. Это особенно актуально для динамических ОЗУ, обладающих большой емкостью памяти, а следовательно, большой разрядностью адресов. Циклы обращения к динамическому ОЗУ начинаются подачей адресного кода А строки и строба RAS = 0. Затем подается адресный код А столбца и строб CAS = 0. Стробы перекрываются во времени. Фиксация адресов в регистрах ОЗУ осуществляется по переднему фронту стробов (переходу логического уровня из 1 в 0). В цикле записи после фиксации адреса строки подается сигнал W/R = 0 и выставляются данные DI. Адресный код А столбца, сигнал записи W/R и данные снимаются через определенный промежуток времени после фиксации адреса столбца.

В цикле чтения после фиксации адреса строки подается сигнал W/R = 1, который удерживается до окончания строба CAS = 0. В циклах регенерации подаются только стробы CAS и адреса строк.

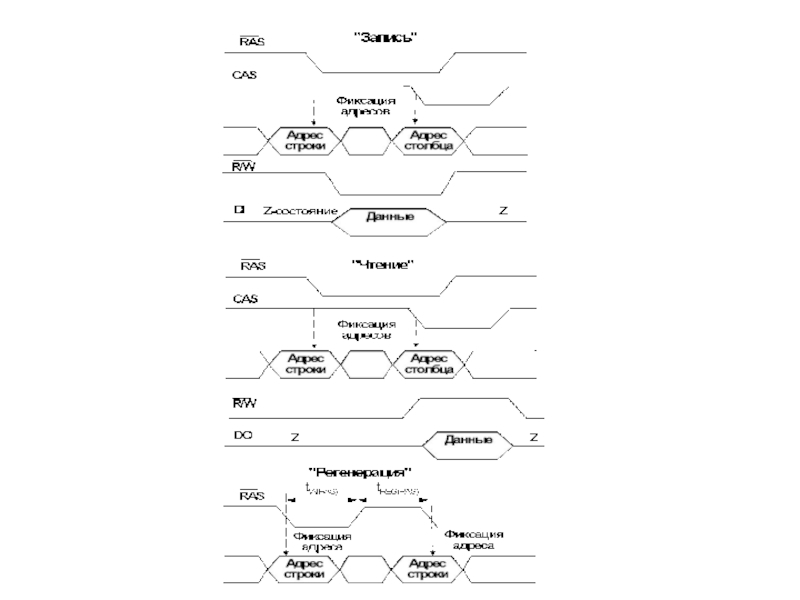

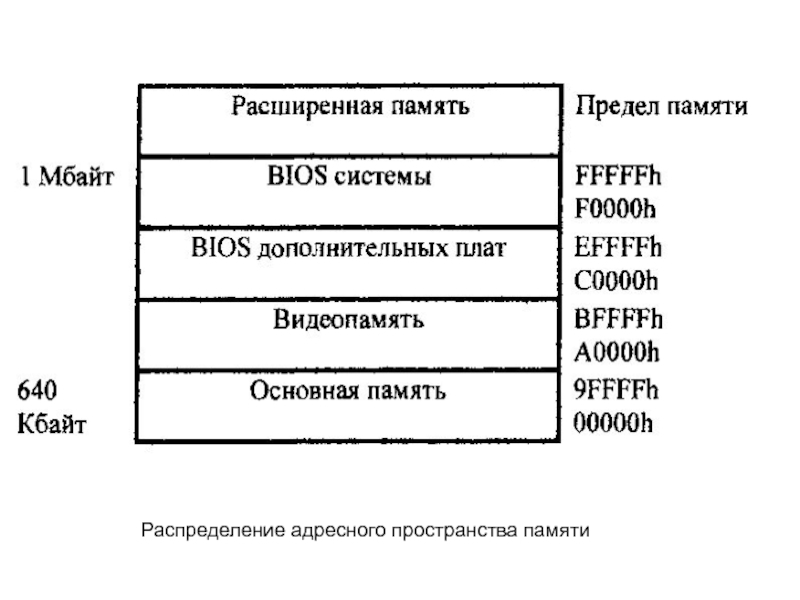

Слайд 7Распределение адресного пространства памяти

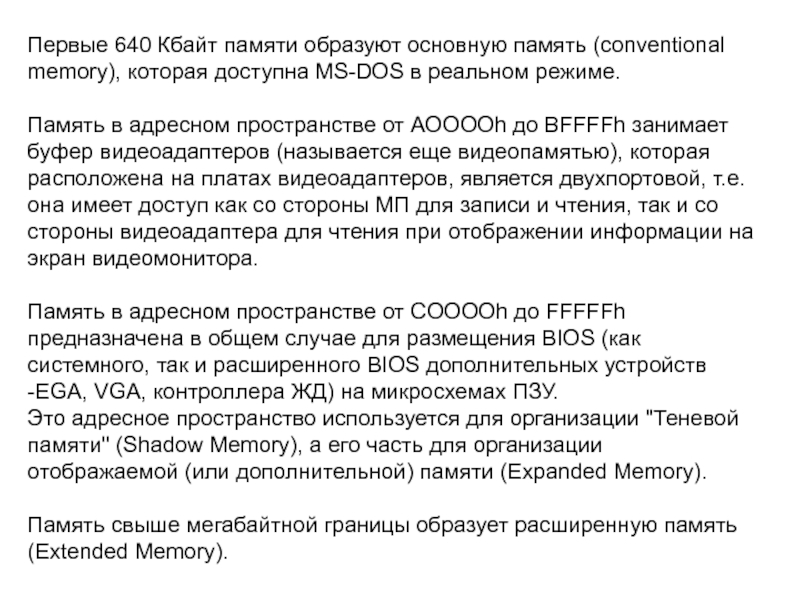

Слайд 8Первые 640 Кбайт памяти образуют основную память (conventional memory), которая

доступна MS-DOS в реальном режиме.

Память в адресном пространстве от AOOOOh

до BFFFFh занимает буфер видеоадаптеров (называется еще видеопамятью), которая расположена на платах видеоадаптеров, является двухпортовой, т.е. она имеет доступ как со стороны МП для записи и чтения, так и со стороны видеоадаптера для чтения при отображении информации на экран видеомонитора.

Память в адресном пространстве от COOOOh до FFFFFh предназначена в общем случае для размещения BIOS (как системного, так и расширенного BIOS дополнительных устройств -EGA, VGA, контроллера ЖД) на микросхемах ПЗУ.

Это адресное пространство используется для организации "Теневой памяти" (Shadow Memory), а его часть для организации отображаемой (или дополнительной) памяти (Expanded Memory).

Память свыше мегабайтной границы образует расширенную память (Extended Memory).

Слайд 9Адресное пространство основной памяти в реальном режиме адресации распределено следующим

образом:

00000h-003FFh занимают 256 4-х байтных вектора прерываний, каждый вектор является

полным начальным адресом (2 байта - сегмент, 2 байта -смещение) программы обработки соответствующего прерывания (как аппаратного, так и программного). Поэтому чтобы определить точку входа в программу обработки прерывания (иначе обработчик прерывания) с номером N, необходимо умножить значение номера прерывания N на 4 и прочитать четыре байта.

00400h-004FFh (ROM Bios Data area) используется операционной системой для хранения информации о конфигурации системы, о других установках и для организации буфера клавиатуры. Данная область памяти заполняется процедурой самотестирования POST при самотестировании компьютера после включения питания.

00500h-OO6FFh (DOS Data area) - область данных BIOS, которая используется для собственных нужд.

Слайд 10Границы остальных модулей, начинающихся с адреса 00700h, зависят от операционной

системы, поэтому ниже дается только перечень блоков для DOS:

- модуль расширения

ввода/вывода (io.sys);

- программа обработки функций 21h прерывания DOS (модуль IBMDOS.com);

- буферная область DOS;

- резидентная часть командного процессора (COMMAND.com);

- программы обработки прерываний DOS 22h, 23h и 24h;

- резидентные (TSR) программы, т.е. программы, остающиеся в памяти после первоначального к ним обращения. В виде TSR программ оформляются дополнительные драйверы внешних устройств (например, драйвер поддержки кириллицы, экрана и клавиатуры) или драйверы нестандартных устройств (контроллер манипулятора типа "мышь").

- память, распределяемая DOS для программ пользователей, которая состоит из сегментов кода, данных и стека.

Слайд 11Последняя часть 640 Кбайтной области памяти занимает транзитная часть командного

процессора COMMAND.com, которая может временно заниматься прикладными программами, а при

переходе в DOS транзитная часть восстанавливается с диска.

Системная BIOS расположена в адресном пространстве от FOOOOh до FFFFFh и содержит процедуру самотестирования при включении питания и перезагрузки POST, коды и данные программ обработки прерываний BOIS, некоторую справочную информацию. Точки входа в конкретную программу обработки можно определить, прочитав и расшифровав вектора прерываний.

ПЗУ BIOS содержит по адресу FOOO:FFFEh байт, позволяющий идентифицировать тип ПЭВМ (данная, информация сохранена и в современных ПК):

Слайд 12FFh - оригинальный IBM PC;

FEh - XT, Portable PC;

FDh -

PCjr;

FCh - AT;

FBh - XT с памятью 640 К на

системной плате;

FAh - PS/2 модель 25 или 30;

F9h - Convertible PC;

F8h - PS/2 модели 55SX, 70,80;

9Ah - Comrad XT, Compaq Plus;

30h - Sperry PC;

2Dh - Compaq PC, Compaq Deskpro.

Дата создания BIOS занимает в ПЗУ BIOS 8 байтов начиная с адреса F000:FFF5h и хранится в формате ASCII в виде мм/дд/гг, где мм - номер месяца; дд - день; гг - год. Дата создания BIOS (а также другие идентификационные характеристики) используется часто для идентификации компьютера и привязки своего программного обеспечения (ПО) к данному компьютеру (один из вариантов защиты от копирования ПО).

Слайд 13расширенная память

(Extended Memory) располагается в адресном пространстве свыше 1 Мбайтной

границы до предела физической памяти. Доступ к расширенной памяти возможен

только для МП i80286 и выше. Полноценное использование extended memory выполняется в защищенном режиме

Однако MS-DOS и другие операционные системы, использующая процессоры i8086 в реальном режиме, не имеет полноценного доступа к этой памяти. То же относится и к программам, разработанным для выполнения в среде MS-DOS.

Однако в составе MS-DOS версии 4.0 и более поздних версий появился драйвер расширенной памяти HYMEM.SYS. Этот драйвер расширяет основное пространство 640 Кбайт еще примерно на 64 Кбайта и предоставляет относительно удобное средство для хранения в расширенной памяти массивов данных.

Будучи установлен в операционной системе, драйвер HYMEM.SYS представляет интерфейс в соответствии со спецификацией XMS (Extended Memory Specification), разработанной корпорациями Lotus, Intel, Microsoft, AST Research. Для управления такой памятью используются аппаратные средства, поддерживающие спецификацию расширенной памяти, или XMS (Extended Memory Specification).

Слайд 14Первые 64 Кбайт расширенной памяти (памяти, физические адреса которой превышают

1 Мбайт) образуют НМА (High Memory Area). Доступ к НМА

требует управления контроллером клавиатуры - микросхемой 8042 в IBM PC AT, расположенной на системной плате. 21-й разряд физического адреса (линия А20) проходит через контроллер клавиатуры, и линия может быть им блокирована (разрыв линии) или разблокирована (идет передача адреса по линии). Если линия А20 разблокирована, НМА доступна для любой программы, работающей в реальном режиме.

В этом случае перенос, возникающий при формировании 20-разрядного физического адреса, не будет игнорироваться, как это имеет место в процессоре 8086. По этой причине адресу памяти, сегментная часть которого содержит значение FFFFh, а смещение превышает OOOFh, будет соответствовать 21-разрядный физический адрес, превышающий границу в 1 Мбайт. Однако если линия А20 блокирована, перенос будет игнорироваться в i80286 и выше.

Начиная с версии 4,0 MS-DOS, НМА может использоваться для размещения ядра операционной системы или прикладных программ. В этом случае в файл конфигурации системы помещается строка

dos-high.

Обрабатывая данную команду, MS-DOS полностью захватывает всю НМА, и в дальнейшем эта область расширенной памяти используется MS-DOS. Сюда переносится резидентная часть ядра и при необходимости другие резидентные программы. При этом предполагается, что в системе инсталлирован драйвер HIMEM.SYS, разблокировавший линию А20.

Слайд 15Память EMB (Extended Memory Block) образует один или несколько блоков,

расположенных в адресном пространстве выше НМА. Для доступа к ним

XMS-драйвер переключает процессор в защищенный режим. Поэтому программы реального режима могут использовать ЕМВ только для хранения данных.

XMS-драйверы включают в каскад прерывания 2Fh собственную "эхо-секцию". Она, получив управление, проверяет значение регистра АН: если AH=43h, драйвер сообщает о своем присутствии (AL=80h) либо передает в регистрах ES:BX адрес точки входа в функцию управления (AL-Oh). Возвращаемый адрес точки входа используется в дальнейшем для непосредственного обращения к XMS-драйверу. Номер функции в этом обращении задается драйверу в регистре АН. В случае успеха XMS-драйвер возвращает АХ=0. При возникновении ошибки АХ=1, а код ошибки передается в регистре BL.

Слайд 16Отображаемая (дополнительная) память (Expanded Memory)

В отличие от расширенной памяти, отображаемая

(или дополнительная) память с помощью специальной аппаратуры и программного обеспечения

позволяет МП осуществлять доступ к физической памяти, расположенной выше 1 Мбайтной границы, через специально организованные окна (фреймы) памяти, лежащие ниже границы 1 Мбайт, т.е. отображает дополнительную, сверх 1 Мбайта, память через окна в диапазоне адресов, лежащих ниже границы 1 Мбайт. Такой способ пригоден и для компьютеров, использующих процессор Intel 8086, не обладающий возможностью адресации расширенной памяти (имеется только 20 линий адресной шины).

Таким образом, прикладные программы MS DOS могут использовать не более 640 Кбайт оперативной памяти. Однако, если в системе поддерживается EMS-спецификация, появляется возможность использовать до 32 Мбайт дополнительной памяти платы. Область адресов, зарезервированная для BlOSa, занята полностью программами ПЗУ только в PS/2, а для IBM PC XT и IBM PC AT в этом диапазоне есть свободное окно размером не менее 64 Кбайт.

Слайд 17Системная или "теневая" память (Shadow RAM)

В современных компьютерах скорость физического

доступа к оперативной памяти намного выше скорости доступа к ПЗУ.

Поэтому процедуры обработки прерываний BIOS (хранятся в ПЗУ) выполняются намного медленнее остальных программ, расположенных в ОЗУ.

Для устранения данного дисбаланса в ходе начальной загрузки после выполнения процедуры самотестирования POST содержимое ПЗУ адресного пространства COOOOh-FFFFFh (системное BIOS из ПЗУ системной платы, BIOS видеоадаптера и BIOS НЖД) переписывается в оперативную память "теневой" памяти объемом 256 Кбайт.

После копирования информации из ПЗУ устанавливается соответствующий разряд в регистре управления памяти ПЗУ, а схемы управления платы "теневой" памяти заменяют это обращение обращением к "теневой" памяти за более короткое время.

Но не все адресное пространство COOOOh-FFFFFh занято BIOS. Оставшаяся свободной "теневая" память, называемая также UMB-блоком (Upper Memory Block) может включаться в адресное пространство MS-DOS и использоваться ею как основная и НМА-память.

Слайд 18типы передач DMA (ПДП)

1) Передача память-память (Memory-to-memory DMA). Используется для передачи

блока данных из одного места памяти в другое. Исходный адрес

определяется в регистрах нулевого канала, выходной - в регистрах первого канала. Число циклов обмена (число байт минус 1) задается в регистре начального счетчика циклов канала 0. Передача происходит с использованием рабочего регистра контроллера в качестве промежуточного звена для хранения информации. При передаче память-память может быть задан специальный режим фиксации адреса (Address hold), при котором значение текущего адреса в регистре нулевого канала не изменяется, при этом весь выходной блок памяти заполняется одним и тем же элементом данных, находящимся по заданному адресу.

Передача память-память может быть реализована только в компьютерах IBM PC/XT. В IBM PC/AT канал 0 используется для каскадирования двух контроллеров (см. ниже) и передача память-память невозможна.

Слайд 192) Автоинициализация (автозагрузка, Autoinitialization). После завершения обычной передачи, использованный канал DMA

маскируется и должен быть перепрограммирован для дальнейшей работы с ним.

При автоинициализации маскировка канала после окончания передачи не происходит, а регистры текущего адреса и счетчик циклов автоматически загружаются из соответствующих регистров с начальными значениями. Таким образом, для продолжения (повторения) обмена достаточно выставить сигнал запроса на DMA по данному каналу.

3) Режим фиксированных приоритетов. В этом режиме канал 0 всегда имеет максимальный приоритет, а канал 3 - минимальный. При каскадном соединении контроллеров DMA приоритеты ведомого контроллера "вставляются" на место приоритетов соответствующего канала ведущего. Так, при подключении ведомого к 0-му каналу ведущего, все каналы ведомого наиболее приоритетные. Любая передача по каналу с более высоким приоритетом будет выполняться раньше, чем по каналу с более низким приоритетом.

Слайд 204) Циклический сдвиг приоритетов. Позволяет избежать "забивания" шины одним каналом при

одновременной передаче по нескольким каналам. Каждому каналу, по которому прошла

передача, автоматически присваивается низший приоритет, после чего право на передачу получает канал с наивысшим приоритетом, для которого передача в данный момент возможна. Таким образом, если в начале работы распределение приоритетов было обычным (канал 0 - наивысший), и пришли сигналы запроса на DMA по 1-му и 2-му каналам, то сначала будет выполняться передача по первому каналу, затем он получит низший приоритет (а канал 2, соответственно, высший, т. к. сдвиг приоритетов циклический) и передача выполнится по 2-му каналу, который затем получит низший приоритет, а высший приоритет получит, соответственно, канал 3, который и будет обладать преимущественным правом на передачу.

Слайд 215) Сжатие времени передачи (Compressed transfer timing). В случае, если временные

характеристики быстродействия обменивающихся устройств совпадают, DMA может сократить время выполнения

каждого такта передачи на 2 цикла CLK за счет исключения тактов ожидания, входящих в каждый цикл передачи.

Слайд 22Программное управление контроллером DMA

Программное управление контроллером DMA осуществляется через порты

ввода-вывода. Доступ к каждому регистру контроллера может быть осуществлен через

свои порты ввода-вывода.

Запись в порт 8h инициализирует команду DMA. Чтение из порта 8h считывает регистр состояния DMA. Описание битов указанных регистров смотри выше.

Запись в порт 9h позволяет программно установить или сбросить запрос на DMA в регистре запросов по одному из каналов. Описание битов: О -1 - выбор канала (00 - 0,01-1,10-2,11-3);

2 - установка запроса на DMA (1-установить, 0-сбросить);

3 - 7 - не используются.

Запись в порт Ah позволяет установить или сбросить бит маски в регистре масок для одного из каналов. Формат команды как в порте 9h.

Слайд 23Запись в порт Bh устанавливает значение в регистре режимов одного

из 4-х каналов DMA. Биты 0 и I задают номер

канала (00 - 0, 01 - 1, 10 - 2, 11 - 3). В биты 2-7 заносятся значения, передаваемые соответственно в биты 0-6 регистра режимов (см. выше).

Запись в порт Dh задает программный сброс контроллера (Master Clear). Вывод любого байта в этот порт имеет тот же эффект, что и аппаратный сброс контроллера. При программном сбросе очищаются регистры команд, состояния, запросов и рабочий регистр. Так же сбрасывается триггер-защелка и устанавливается все биты масок в регистре масок. После программного сброса контроллер переходит в цикл ожидания.

Вывод любого байта в порт Eh очищает регистр масок - сбрасывает биты масок всех 4-х каналов DMA и таким образом разрешает прием запросов на DMA по всем каналам.

Слайд 24Через порт Fh можно задать произвольное значение регистра масок DMA.

Для этого необходимо в битах 0 - 3 передаваемого байта

установить требуемое значение масок каналов 0-3 соответственно и вывести это значение в порт.

Страничные регистры DMA предназначены для задания номера страницы памяти, с которой будет производится обмен. Под номером страницы понимаются старшие биты полного 32-битового адреса ОЗУ, т.е. начальные сегментные адреса страниц будут кратны 10000h (0, 10000h, 20000h, ...,). Напомним, что архитектура DMA позволяет работать только со страницей памяти размером 64 К, а логика, обеспечивающая переключение страниц устроена так, что страницы имеют жесткие границы, описанные выше