Слайд 18086

16-разрядный процессор 8086 объединял в себе три важнейшие устройства ЭВМ:

АЛУ,

выполняющее арифметические и логические операции

Блок управления, осуществляющий согласованное управление различными

узлами микро-ЭВМ

Блок ввода/вывода, осуществляющий управление потоками вводы/вывода

8086 мог явно адресоваться к 216 =65536 ячейкам памяти, что было не достаточно. Тогда было предложено задавать адрес двумя 16-разрядными числами (сегментом и смещением), в результате появилась возможность адресоваться к 1Мб памяти.

С целью ускорения расчетов для этого процессора был создан математический сопроцессор, резко повысивший скорость математических расчетов.

Слайд 2Организация ЦП старших моделей фирмы Intel

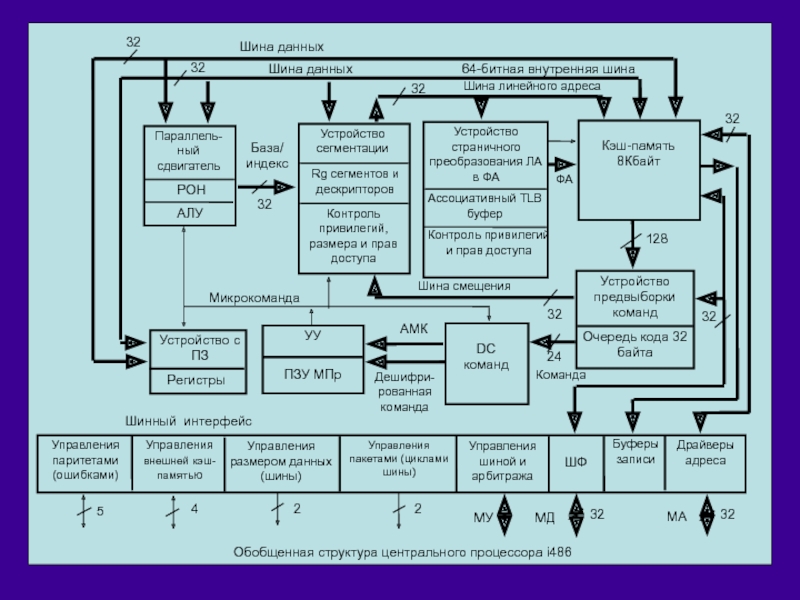

Слайд 4Функциональные устройстра i486

В состав ЦП входит 10 внутренних функциональных устройств,

которые работают параллельно:

устройство шинного интерфейса (или просто шинный интерфейс ШИ);

кэш-память

на 8 Кбайт;

устройство предвыборки команд (опережающей выборки);

двухступенчатый дешифратор команд;

УУ;

устройство целочисленной арифметики,

устройство с ПЗ,

устройство сегментации;

устройство страничного преобразования адресов.

Архитектура ЦП 80486 похожа на архитектуру ЦП 80386 с добавлением внутренней кэш-памяти и УПЗ (сопроцессора) на кристалле, что сразу отразилось на структуре локального интерфейса ЦП, ШИ ЦП включает раздельные 32-разрядные МА и МД, магистраль управления шиной и арбитража, а также добавлены группы шин управления пакетами (определения циклов шины), управления размером передаваемых данных (8, 16 и 32 бита), управления кэш-памятью, управления паритетами (ошибками передачи данных, с ПЗ) и буфер данных для временного хранения данных при сквозной записи, выдаваемых из ЦП на МД, когда последняя занята.

Слайд 5Функциональные устройстра i486

В ВМ86 локальная магистраль адреса данных 20 бит

и совмещенная с шиной данных, а в старших моделях магистрали

адреса и данных раздельные, что позволило длительность нормального цикла шины существенно сократить (вместо 4 тактов стала 2 такта).

Отличительной чертой внутренней структуры ЦП 80486 является наличие большого числа внутренних магистралей различной разрядности для связи и взаимодействия основных устройств, наличие многопортовых внутренних памятей, что позволяет организовать параллельную работу устройств.

Устройство предвыборки команд (УПК) работает в режиме опережающей выборки команд, т.е. когда ШИ свободен осуществляется подкачка новых строк либо в кэш-память, если будущей строки нет в кэш-памяти, либо сразу в ОК и кэш-память параллельно, если там есть не менее 16 свободных байт, т.е. для опережающей выборки начальный адрес последней загруженной в ОК команды должен быть больше адреса выполняемой команды не менее 16 байт (одна выровненная строка) . Для этого глубина ОК составляет 32 байта или две строки. Поэтому, кроме исключительных ситуаций, ситуация, когда А кэш практически исключена.

Исключительные ситуации возникают при нарушении работы конвейера команд (команды УП, БП, CALL, INT, аппаратные прерывания).

Слайд 6Функциональные устройстра i486

Так как глубина ОК в 2 раза больше

длины строки, то можно без простоев пополнять очередь команд, когда

начальный адрес команды больше адреса последней выбранной команды по границе адресов кратной 16 байтам, что и обеспечивает алгоритм опережающей выборки команд. При этом считанная из ОП строка (при выполнении процедуры замещения строки (16 байт) из ОП (пакетный кэшируемый цикл)) параллельно записывается в кэш-память и буфер ОК, что не требует приостановки (простоя) работы ОК даже после возникновения исключительных ситуаций (т.е. не требует дополнительного такта обращения к кэш-памяти (чтение с перехватом)).

Если в программе встречаются повторяющиеся участки программ (циклы, подпрограммы), то УПК получает их копии из кэш-памяти, т.е., если Акэш-памяти, а ОК пуста или требует пополнения (имеется от 16 и более свободных байт [IPок-IPтек>=16]), то данная процедура выполняется за один такт, т.к. из кэш-памяти считывается сразу вся строка (16 байт) и записывается в ОК в этом же такте (расслоение обращений в кэш-памяти по одному из портов и в буфере ОК.

Кроме того, реализована опережающая выборка команд из ОК, т.е. в каждом такте на первой стадии работы конвейера команд выбраны два слова: управляющая часть команды, которая подается в устройство дешифрации, и следующее слово, которое может быть командой, операндом или смещением в команде (два слова или двойных слова).

Слайд 7Функциональные устройстра i486

Таким образом, для повышения быстродействия ЦП, т.е. обеспечения

бесперебойной (без задержек) работы очереди команд используются следующие методы:

Опережающая выборка

команд в кэш-память, когда ШИ свободен.

Параллельная запись строки в ОК и кэш-память, если Акэш.

Если Акэш, то строка за один такт считывается из кэш-памяти и параллельно все 16 байт записываются в ОК, т.к. обе памяти с расслоением обращений на 16 байт.

Глубина ОК в 2 раза больше длины строки, что позволяет без простоев (параллельно) выполнять подкачку строк в ОК из ОП или кэш-памяти.

Использование пакетных циклов передачи данных между ОП и ЦП.

Опережающая выборка команд из ОК, что позволяет сразу передавать второе слово команды на обработку.

Таким образом, УПК позволяет обеспечить максимальную загрузку СШ, так как использует для предвыборки только холостые циклы шины и никогда не задерживает выполнение программы.

При считывании из ОК код операции подается в устройство дешифрирования, а смещение в команде - в устройство сегментации для вычисления линейного или физического адреса операнда.

Слайд 8Функциональные устройстра i486

Устройство дешифрирования преобразует поля КОП в управляющие сигналы

и точки входа в память микропрограмм. Первая ступень дешифратора инициирует

обращение к памяти за операндом, при этом одновременно обрабатываются байты префиксов команд, признака адресации и смещения, а на выходах УУ формируются микрокоды для устройства сегментации и устройств целочисленной арифметики и ПЗ.

УУ обеспечивает выполнение большинства команд за один такт синхронизации по конвейерному принципу.

Имеется 5 уровней конвейера:

выборка команды из ОК;

первая ступень дешифрации, сегментация и контроль атрибутов сегмента: дешифрация ПА и вычисление линейного или физического адреса с параллельным контролем атрибутов защиты сегмента;

страничное преобразование через буфер TLB на основе частично-ассоциативного АЗУ или таблицы каталогов и страниц, контроль атрибутов защиты страницы, дешифрация КОП и выборка операнда из кэш-памяти по сформированному ФА;

выполнение операции в УЦА или УПЗ;

запись результата в регистр или кэш-память и инициализация сквозной записи: если ШИ свободен, то инициируется одиночный непакетный цикл записи в ОП, иначе запись в буфер записи ШИ (отложенная запись).

Слайд 9Функциональные устройстра i486

Устройство целочисленной арифметики включает АЛУ, 8 программно-доступных РОН,

параллельный сдвигатель и несколько специализированных регистров. Содержимое РОН подается в

устройство сегментации по отдельной шине (двухпортовый доступ). АЛУ позволяет выполнять любую операцию за один такт.

УПЗ также выполняет большинство операций за один такт благодаря конвейерной организации вычислений, расслоению обращений к внутренней кэш-памяти и наличию двух внутренних шин данных по 32 бита для приема операнда и выдачи результата.

На втором уровне конвейера также выполняется преобразование ЛА в ФА в устройстве сегментации и параллельно контроль атрибутов (прав доступа) сегментов.

Устройство сегментации содержит: глобальные и локальные таблицы дескрипторов, хранимые в ОП, регистры селекторов (6 регистров) и теневые 8-байтные регистры дескрипторов, а также схемы для формирования сигналов сегментных ошибок по атрибутам, размеру и т.д. для формирования векторов прерываний.

Устройство страничного преобразования включает в себя TLB буфер и средства для организации системы защиты страниц. Кроме того, при отсутствии описания страницы в TLB буфере в его состав входят таблицы каталогов и страниц, хранящиеся в ОП.

Слайд 10Внутренняя кэш-память ЦП i486

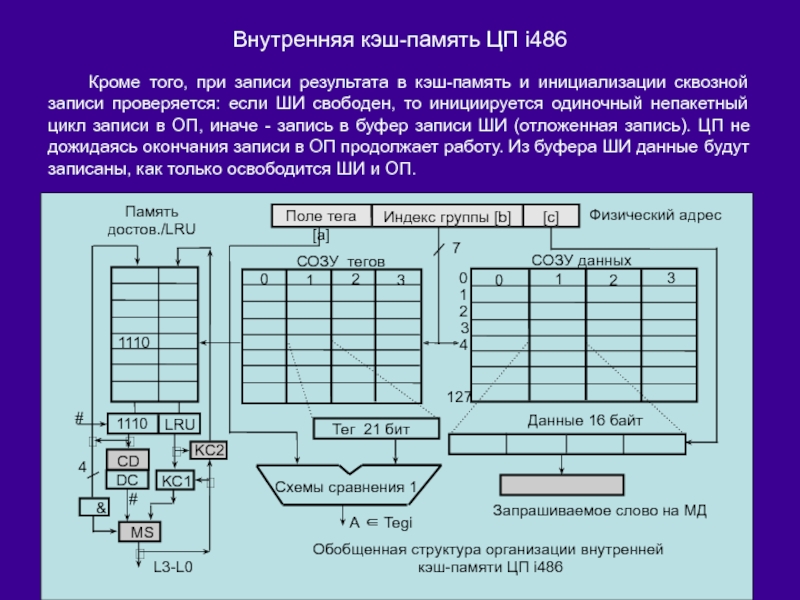

Внутренняя кэш-память построена на основе четырех модулей

с частично-ассоциативным распределением общей емкость 8 Кбайт (по 2 Кбайта

в каждом модуле) Длина строки 16 байт. Отсюда, ФА делится на 3 поля: 4-разрядное поле С для указания номера байта в строке, 7-разрядное поле b индекса группы из четырех строк и 21-разрядное поле тегов а. ЧАЗУ состоит из четырех 21-разрядных модулей памяти тегов и четырех 32-разрядных модулей памяти данных, а также и 7-разрядного модуля памяти бит достоверности и LRU состояний кандидатов на удаление (D/LRU) емкостью по 128 ячеек для каждого модуля. В памяти D/LRU 4 бита отводятся для указания бит достоверности строк для каждого модуля ЧАЗУ и 3 бита для хранения кода LRU состояния (кандидата на замещение).

Для внутренней кэш-памяти используется стратегия сквозной записи, а замещение по стратегии псевдо LRU стека. Особенностью реализации алгоритма замещения является то, что замещение выполняется только при промахе и только в операциях чтения, а при операциях записи (без предварительного чтения) при промахе запись выполняется сразу только в ОП, что исключает выполнение процедуры замещения строки. Такая ситуация характерна только при выполнении команд пересылки типа MOV из РОН в ОП, а вероятность, того, что после этих команд будет обращение к этой же строке в ближайшее время не велика. Поэтому данный метод можно отнести к методам увеличения быстродействия внутренней кэш-памяти за счет сокращения времени на выполнение операции замещения строки.

Слайд 11Внутренняя кэш-память ЦП i486

Кроме того, при записи результата в кэш-память

и инициализации сквозной записи проверяется: если ШИ свободен, то инициируется

одиночный непакетный цикл записи в ОП, иначе - запись в буфер записи ШИ (отложенная запись). ЦП не дожидаясь окончания записи в ОП продолжает работу. Из буфера ШИ данные будут записаны, как только освободится ШИ и ОП.

Слайд 12Внутренняя кэш-память ЦП i486

Биты достоверности сбрасываются при очистке внутренней кэш-памяти

при загрузке ОС (и при сбросе RESET). Для сброса

бит достоверности предусмотрен специальный цикл шины “Очистка кэш-памяти”. При выполнении процедуры замещения сначала замещаемые строки загружаются в кэш-память в группы строк, у которых имеется хотя бы один не установленный бит достоверности, а затем, когда все 4 бита достоверности равны “1”, замещаемая строка определяется по стратегии псевдо-LRU.

Можно выделить две ситуации, когда содержимое кэш-памяти отличается от данных в ОП:

а) когда цикл записи в память задерживается из-за буферирования данных в FIFO ШИ (отложенная запись);

б) когда какой-либо внешний ведущий модуль СШ изменяет область памяти, отображаемую на кэш-память, например, обновление данных со стороны видеопроцессора.

В ЦП i486 имеется возможность изменять конфигурацию кэш-памяти, для чего в регистре управления CR0 отведены два бита: разрешение кэширования (т.е. заполнение строк кэш-памяти) и разрешение сквозной записи в память, что позволяет получить 4 возможных конфигурации.

Слайд 13Внутренняя кэш-память ЦП i486

Таким образом можно выделить следующие методы повышения

производительности ЦП за счет использования внутренней кэш-памяти:

• Использование ЧАЗУ, имеющего а)

более высокое быстродействие, по сравнению с ПАЗУ; б) позволяет выполнять чтение за один такт; в) сокращает число промахов, по сравнению с прямым распределением;

• Использование сквозной записи сокращает число считываний с 42% до 8% (в 5 раз) из ОП за счет пространственной и временной локальности, а число записей, остается неизменным, но они не влияют на быстродействие кэш-памяти, т.к. кэш-память не дожидается окончания записи в ОП. Процедура обновления ОП выполняется словами, а не строками по сравнению с обратной записью.;

• Использования стратегии псевдо LRU стека, что сокращает число промахов, а следовательно, время на процедуры замещения строк;

• Использование буфера отложенной записи в ШИ;

• Использование алгоритма работы регистрового файла, в качестве которого используется буфер ШИ, т.е. если в буфере ШИ имеются данные, накопленные при сквозной записи для отложенной записи в ОП, то при обращении к кэш-памяти при промахе (АTeg) считывание строки из ОП имеет более высокий приоритет, перед освобождением буфера ШИ, т.е. сначала затребованная строка считывается из ОП и помещается в кэш-память, а затем данные из буфера ШИ записываются в ОП.

Слайд 14 Организация внешней памяти

В ЦП i486 используется ОП с расслоение обращений

на 16 байт. Поэтому при считывании строки за одно обращение

к ОП и передачи первого слова строки в кэш-память последующие данные будут переданы за 3 такта. Таким образом, считывание и передача строки в кэш-память требует минимум 5 тактов (вместо 8). Отсюда, введение пакетных циклов шины позволяет сократить число обращений к ОП при выполнении процедур замещения строк, а, следовательно, повысить производительность ВС. Пакетные циклы могут применяться только, если считываемые данные выровнены по границе 16 байт при выполнении процедур замещения строк, работе с массивами данных, при обработке строковых переменных. Пакетные циклы могут использоваться только на операциях чтения.

Внешняя кэш-память (БИС i82485) построена на основе четырех модулей с частично-ассоциативным распределением общей емкость N=64, 128, 256 и 512 Кбайт Длина строки 16 байт. Отсюда, ФА делится на 3 поля: 4-разрядное поле С для указания номера байта в строке, k-разрядное поле b индекса группы из четырех строк и m-разрядное поле тегов [а].

Для внешней кэш-памяти используется стратегия обратной записи, а замещение по стратегии псевдо LRU стека. Стратегия псевдо LRU стека позволяет сократить число промахов. Обратная запись с одной стороны сокращает число обращений к ОП по операциям считывания из-за пространственной и временной локальности данных и команд, а с другой в сквозной записи нет необходимости, так как она уже реализована во внутренней кэш-памяти, а внешняя кэш-память имеет достаточно большую емкость и содержит все копии содержимого внутренней кэш-памяти и данных, используемых за достаточно большой промежуток времени.

Слайд 15Повышение производительности ЦП i486 достигнуто за счет:

• применения конвейерного принципа выполнения

команд и операций в УЦА и УПЗ (большинство команд выполняются

за один такт);

• введение внутренней кэш-памяти сокращает:

время доступа к памяти;

число обращений к системной шине и ОП:

сокращается число считываний из ОП;

появилась возможность организации опережающей (предвыборки) выборки команд;

введение очереди команд с буфером на две строки;

использование в ОК принципа обхода внутренней кэш-памяти при пополнении очереди команд;

• Организации ОП;

расслоение обращений;

введение пакетируемых кэшируемых и некэшируемых циклов шины.

• Организации внутренней кэш-памяти;

сквозная запись;

расслоение обращений с параллельным доступом в 16 байт к кэш-памяти и ОК;

многопортовая кэш-память;

использование стратегии замещения псевдо LRU стека.

• Возможность подключения дополнительной внешней кэш-памяти для мультипро-граммных режимов работы.

Слайд 16Организация шины процессора и циклы шины

ШИ ЦП i486 предназначен для

связи с другими устройствами. Сигналы шины по их функциям классифицируются

(объединяются) в группы (см. рис.1);

адреса 32 бита;

данных 32 бита;

управления и арбитража;

определения цикла шины;

управление размером передаваемых данных;

управления внешней кэш-памятью;

управления ошибками передач и с ПЗ.

Среди особенностей ШИ ЦП i486 следует отметить;

немультиплексированные 32-разрядные шины адреса и данных;

одночастотную (1х) синхронизацию (ранее было две частоты для различных устройств путем деления опорной частоты);

операции захвата, блокирования и псевдоблокирования шины;

пакетные передачи по 16 байт;

кэшируемые передачи;

поддержку согласованности внутренней и внешней кэш-памяти (УУ ЦП вырабатывает управляющие сигналы для внешней кэш-памяти, а наличие внешней кэш-памяти задается в регистрах управления ЦП);

обработку ошибок с ПЗ (ранее сопроцессор подключался к СШ и был внешним по отношению к БИС ЦП);

поддержку 8/16-разрядных периферийных устройств для совместимости с младшими моделями и другие.

Слайд 17Организация шины процессора и циклы шины

Адресное пространство команд отделено от

адресного пространства ввода/вывода, т.е. их адреса могут пересекаться. Допускается адресация

памяти до 4 Гбайт (32-разрядные адреса). Адресные пространства памяти и ввода/вывода имеют аппаратную поддержку защиты и мультизадачности.

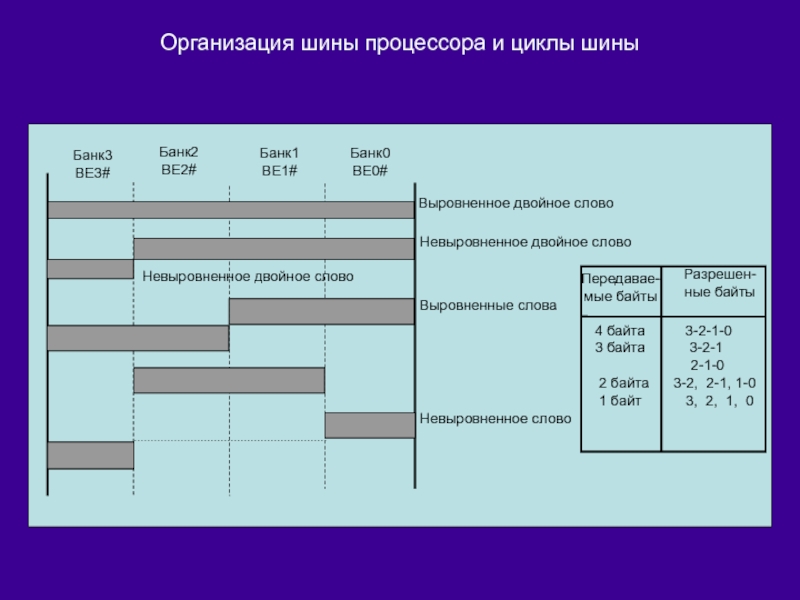

ОП реализована в виде четырех банков памяти по байту. Для программиста доступны 8/16/32-разрядные данные, задаваемые префиксом и КОП и другие структуры данных (строки, ПЗ и т.д.).

Для реализации доступа к байту, слову, двойному слову на аппаратном уровне ЦП вырабатывает сигналы на шину управление, определяющие выбор банков ОП, к которым осуществляется обращение.

Данные считаются выровненными в ОП, если адрес кратен их ширине. Однако в ЦП i486 данные считаются выровненными, если их можно считать за одно обращение к памяти.

Выравнивание данных влияет на производительность процессора, так как передача выровненных слов и двойных слов занимает один цикл шины, а не выровненных два.

Слайд 18Организация шины процессора и циклы шины

Слайд 19Структура портов ввода/вывода.

Порты ввода/вывода имеют 3 типа структур: 8-,

16-, 32-разрядные. ЦП поддерживает два базовых способа адресации к портам

ВВ:

• по командам IN и OUT через отдельное адресное пространство ВВ, которое имеет две модификации:

прямая адресация портов ВВ с помощью байта (номера порта ВВ), указываемого в команде, и допускает адреса в диапазоне от 0 до 255;

косвенная регистровая адресация через регистр DX с отображением на адресное пространство ВВ 64 Кбайта (диапазон от 0 до 65535):

• с отображением на адресное пространство памяти, причем порты ВВ считаются адресами памяти и для доступа к портам применяется система команд общего назначения (без использования команд IN и OUT), а также обеспечивается защита памяти механизмом сегментации и страничной организации.

16-разрядные порты должны быть выровнены по четным адресам, чтобы все слова можно было передавать за один цикл шины, а 32-разрядные порты ВВ - по адресам, кратным четырем.

Для взаимодействия с 8-, 16- и 32-разрядными внешними устройствами имеется возможность задавать размер шины с помощью сигналов шинного интерфейса ЦП BS16# и BS8#. Размер шины задается в префиксе команды или в КОП.

Слайд 20Циклы шины.

Взаимодействие ЦП с внешними компонентами системы по отношению

к ЦП реализуются с помощью циклов шины, которые образуют две

основные группы:

1. Группа циклов передачи данных, в которую входят циклы:

предвыборки команд из памяти:

считывание данных из памяти:

считывание данных из подсистемы ввода/вывода:

запись данных в память:

запись данных в подсистему ввода/вывода.

2. Группа особых циклов шины, в которую входят циклы:

подтверждение прерывания:

четыре специальных цикла шины:

останов (формирует код команда HLT);

отключение (ЦП прекращает все операции по защите);

очистка кэш-памяти (сброс битов достоверности внутренней кэш-памяти);

обратная запись ("выгрузка") кэш-памяти и очистка (сброс битов достоверности внутренней кэш-памяти, достоверное состояние внешней кэш-памяти переписывается в ОП ("выгрузка") и сброс битов достоверности внешней кэш-памяти).

Слайд 21Организация передачи данных в циклах шины

В циклах шины по шинам

процессора пересылаются команды, операнды и другие данные (различная управляющая информация).

Каждый элемент данных (байт, слово, двойное слово, строка и т.д.) идентифицируются адресом и сигналами разрешения байт к банкам памяти BE[i]#.

Передача данных осуществляется двумя основными способами:

1. С помощью непакетных циклов шины, которые подразделяются на:

некэшируемые операции считывания или записи памяти или ВВ:

одиночные передачи;

многоцикловые последовательности;

кэшируемые операции считывания из памяти (включая предвыборку команд):

многоцикловые последовательности;

2. С помощью пакетных циклов шины, которые подразделяются на:

для небольших размеров шины некэшируемые операции считывания из памяти или ВВ:

кэшируемые операции считывания из памяти (включая предвыборку команд).

Слайд 22Организация передачи данных в циклах шины

Непакетный цикл шины это такой

цикл, в котором для доступа к одному элементу данных необходимо

выполнить обращение к памяти или УВВ (режим без расслоения обращений).

Некэшируемые циклы шины - это такие циклы, когда считанные данные не поступают в кэш-память.

Одиночные передачи за цикл шины передают один элемент данных.

Многоцикловые последовательности представляют собой серию циклов одиночных передач данных, размещаемых в последовательных ячейках памяти (например, считывая 128-разрядные команды или 64-разрядные операнды с ПЗ).

Кэшируемые циклы шины служат для заполнения строки внутренней кэш-памяти процессора.

Пакетные циклы шины являются самым быстрым способом передачи данных и в одном цикле могут передавать до 16 байт. Используется при расслоении обращений доступа к памяти. Самый быстрый пакетный цикл требует 2 такта для обращения к памяти и первой передачи и по одному такту для всех последующих передач (5 тактов), а непакетные по два такта на каждую передачу (8 тактов). Пакетные циклы имеют ограничения: они могут передавать только выровненные строки по смежным адресам, кратным 16.

Слайд 23Организация передачи данных в циклах шины

Непакетный цикл шины.

Минимальная длительность одного

цикла шины составляет 2 такта (типа 2-2: 2 такта на

чтение и 2 на запись) , однако за счет введения в цикл шины дополнительных тактов состояния ожидания длительностью цикла шины можно варьировать в широких пределах в зависимости от быстродействия памяти.

Назначение непакетных циклов:

одиночных - для передачи одного элемента данных (формата байт, слово, двойное сло-во) за цикл шины по записи или считыванию, например, при сквозной записи в кэш-память;

многоцикловые последовательности для передачи элемента данных, длина которого превышает установленную разрядность шины данных (например, при передаче не выровненных данных, 64-разрядных данных с ПЗ - 4 цикла для 16-разрядной шины и 2 цикла для 32-разрядной шины, 128-разрядных команд, 32-разрядных данных по 8/16-разрядной шине и т.д.). Отсюда, многоцикловая последовательность требует "указания" длины передаваемых данных, формируе-мой внутренними запросами процессора (КОП, тип данных) или внешними запросами системы памяти.

Кэшируемые многоцикловые последовательности используются для заполнения строк внутренней кэш-памяти при замещении за 4 цикла шины минимум по 2 такта на каждый цикл (8 тактов).

Слайд 24Организация передачи данных в циклах шины

Пакетные циклы шины.

Кэшируемые пакетные циклы

шины служат для кэшируемых считываний при замещении строки из 16

байт, а также для считывания чисел с ПЗ, считываний из дескрипторных таблиц (8байт) и других типов передач через кэш-память.

Некэшируемые пакетные циклы шины - это такие циклы, когда считанные данные не поступают в кэш-память. Они также оказывают значительное влияние на производительность системы. Любое многоцикловое считывание процессор может преобразовать в пакет, а длиной пакета можно управлять (например, при работе со строками, при считывании 128-разрядных команд (минимум 2 пакетных цикла), даже если они не выровнены в памяти (максимум 2 много-цикловых непакетных и 1 пакетный).

Слайд 25 Построение систем на основе ЦП i486

Слайд 26 Построение систем на основе ЦП i486

В основе построения систем на

базе ЦП i486 лежит модульный принцип. Связь ЦП с УВВ

и внешней памятью осуществляется по системной шине, включающей МА, МД и МУ. Поэтому для организации связи с внешними устройствами служит контроллер шины.

Контроллер шины реализован на основе БИС программируемых логических устройств, включающих в себя регистр адреса, системный контроллер шины, шинные формирователи.

На рисунке приведена простейшая типовая структура сопряжения ЦП i486 с внешними устройствами. С помощью декодера адреса осуществляется выбор группы устройств или устройства, с которым будет выполняться обмен по шине (памяти или УВВ), Внешняя память (ОП) большой емкости строится на БИС динамической памяти.

В отличие от статической памяти, память динамического типа требует периодической регенерации своего содержимого. Процесс регенерации выполняется в промежутках времени между обращениями к памяти или ее модулям или, если этого времени недостаточно, по таймеру регенерации динамического ОЗУ.

Периферийные БИС, практически все, являются многофункциональными и программируемыми. Интегрированные системные периферийные устройства имеют одинаковые интерфейсы и выполняют группу функций по назначению: например, связи с центральной частью процессора (блок таймеров, система прерываний, ПДП, регенерация динамической памяти, генератор тактов ожидания)

Слайд 27 Построение систем на основе ЦП i486