Слайд 4 Арифметические основы АЛУ

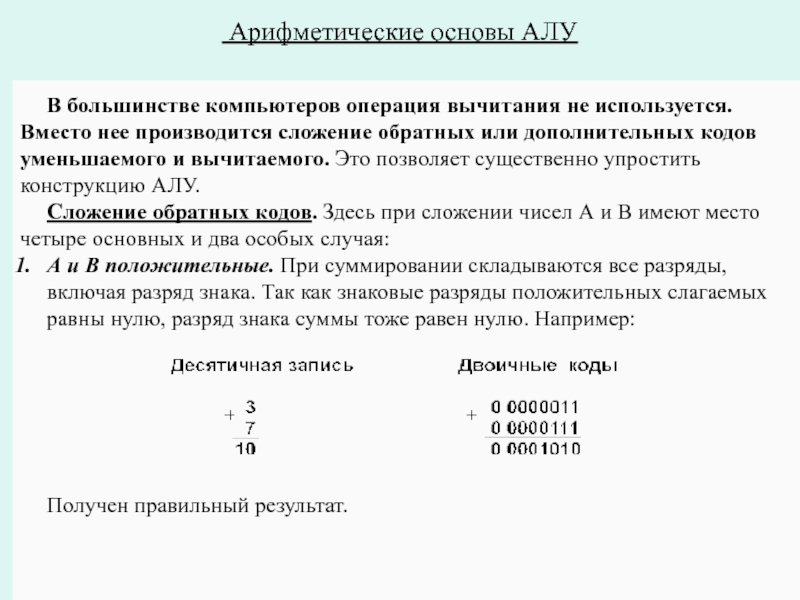

В большинстве компьютеров операция вычитания не используется.

Вместо нее производится сложение обратных или дополнительных кодов уменьшаемого и

вычитаемого. Это позволяет существенно упростить конструкцию АЛУ.

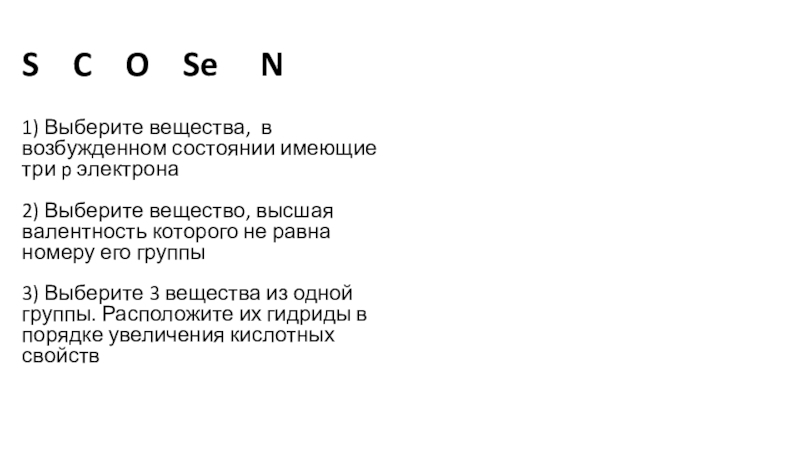

Сложение обратных кодов. Здесь при сложении чисел А и В имеют место четыре основных и два особых случая:

А и В положительные. При суммировании складываются все разряды, включая разряд знака. Так как знаковые разряды положительных слагаемых равны нулю, разряд знака суммы тоже равен нулю. Например:

Получен правильный результат.

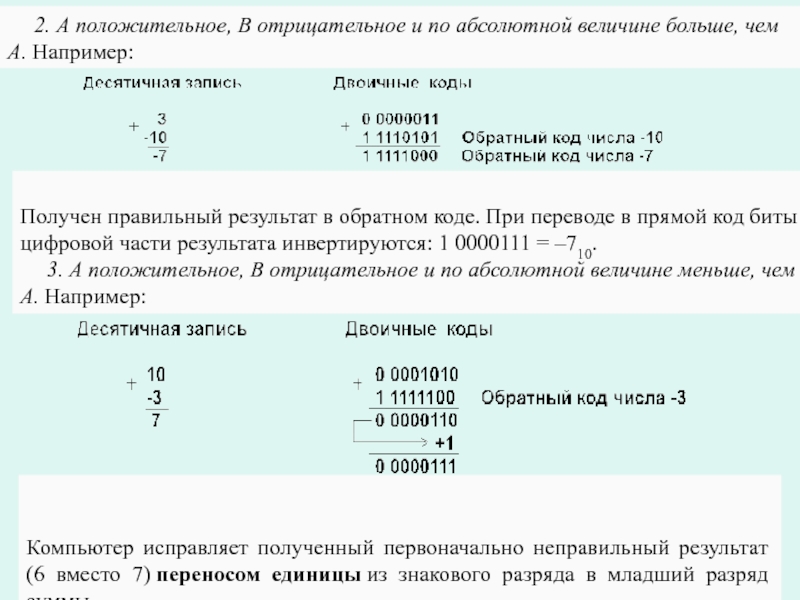

Слайд 52. А положительное, B отрицательное и по абсолютной величине больше,

чем А. Например:

Получен правильный результат в обратном коде. При переводе в

прямой код биты цифровой части результата инвертируются: 1 0000111 = –710.

3. А положительное, B отрицательное и по абсолютной величине меньше, чем А. Например:

Компьютер исправляет полученный первоначально неправильный результат (6 вместо 7) переносом единицы из знакового разряда в младший разряд суммы.

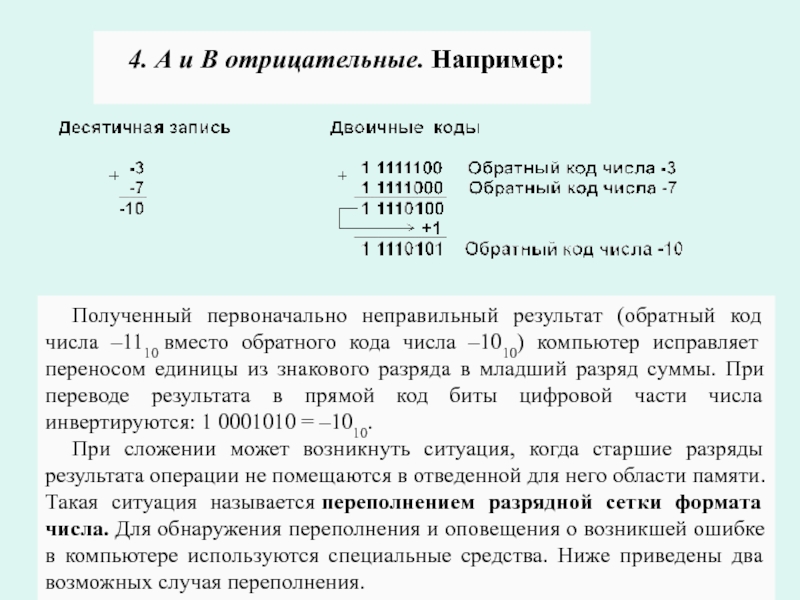

Слайд 64. А и В отрицательные. Например:

Полученный первоначально неправильный результат (обратный код

числа –1110 вместо обратного кода числа –1010) компьютер исправляет переносом единицы

из знакового разряда в младший разряд суммы. При переводе результата в прямой код биты цифровой части числа инвертируются: 1 0001010 = –1010.

При сложении может возникнуть ситуация, когда старшие разряды результата операции не помещаются в отведенной для него области памяти. Такая ситуация называется переполнением разрядной сетки формата числа. Для обнаружения переполнения и оповещения о возникшей ошибке в компьютере используются специальные средства. Ниже приведены два возможных случая переполнения.

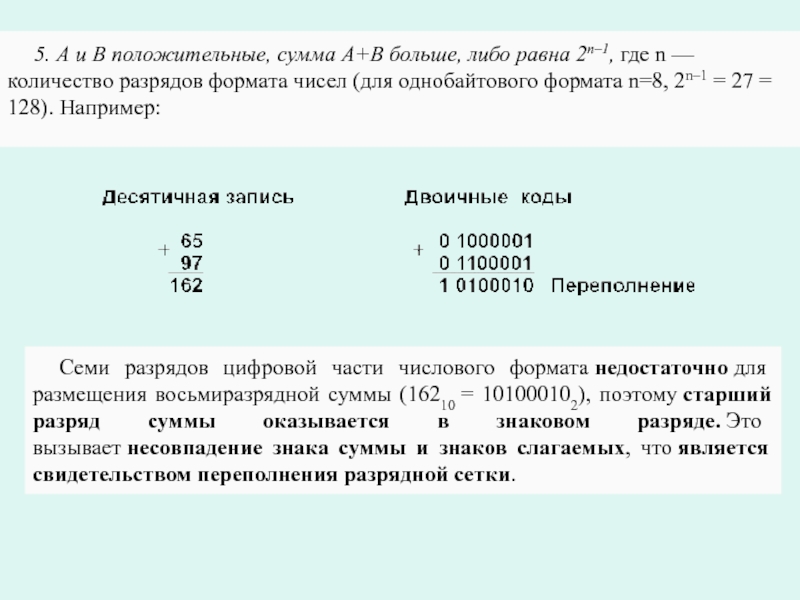

Слайд 75. А и В положительные, сумма А+В больше, либо равна

2n–1, где n — количество разрядов формата чисел (для однобайтового формата

n=8, 2n–1 = 27 = 128). Например:

Семи разрядов цифровой части числового формата недостаточно для размещения восьмиразрядной суммы (16210 = 101000102), поэтому старший разряд суммы оказывается в знаковом разряде. Это вызывает несовпадение знака суммы и знаков слагаемых, что является свидетельством переполнения разрядной сетки.

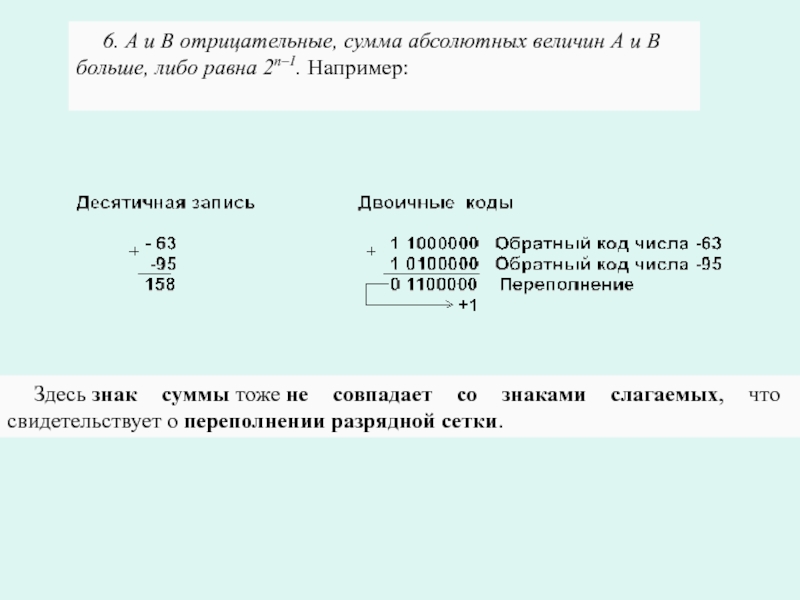

Слайд 86. А и В отрицательные, сумма абсолютных величин А и

В больше, либо равна 2n–1. Например:

Здесь знак суммы тоже не совпадает со знаками слагаемых,

что свидетельствует о переполнении разрядной сетки.

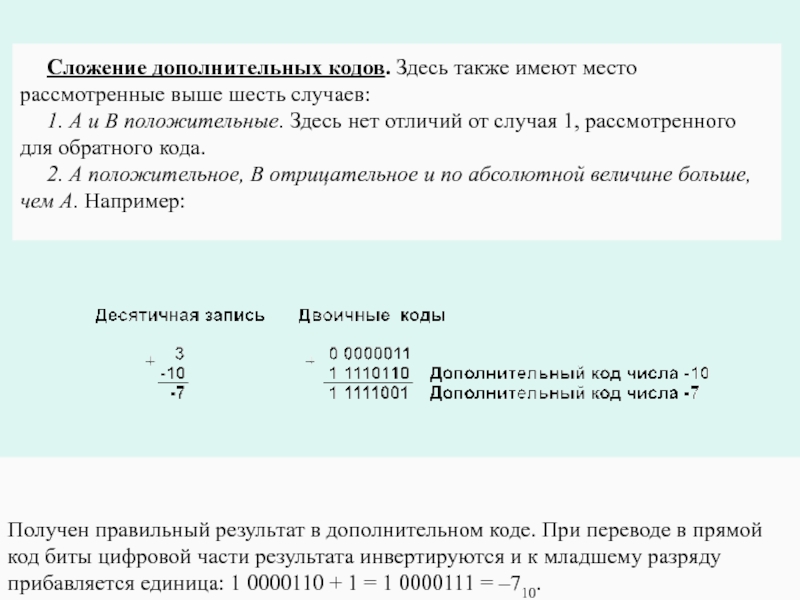

Слайд 9Сложение дополнительных кодов. Здесь также имеют место рассмотренные выше шесть случаев:

1.

А и В положительные. Здесь нет отличий от случая 1, рассмотренного

для обратного кода.

2. А положительное, B отрицательное и по абсолютной величине больше, чем А. Например:

Получен правильный результат в дополнительном коде. При переводе в прямой код биты цифровой части результата инвертируются и к младшему разряду прибавляется единица: 1 0000110 + 1 = 1 0000111 = –710.

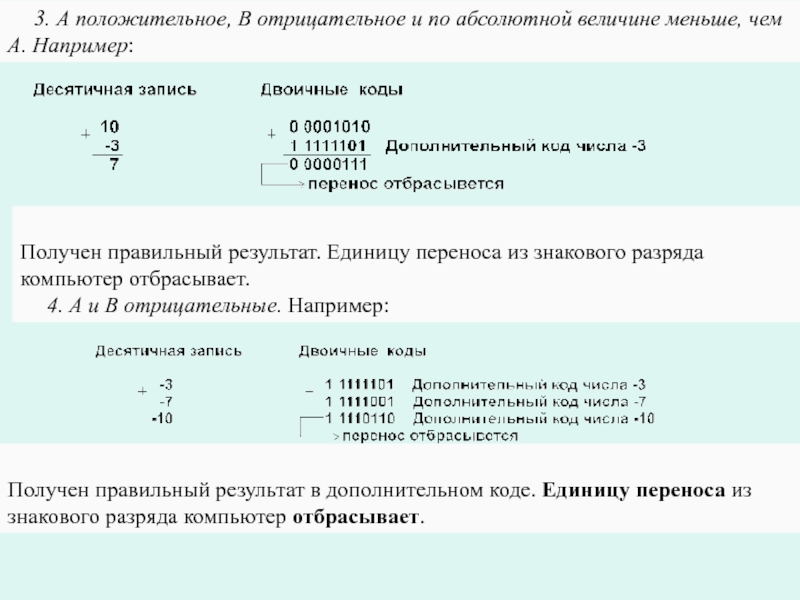

Слайд 103. А положительное, B отрицательное и по абсолютной величине меньше,

чем А. Например:

Получен правильный результат. Единицу переноса из знакового разряда компьютер

отбрасывает.

4. А и В отрицательные. Например:

Получен правильный результат в дополнительном коде. Единицу переноса из знакового разряда компьютер отбрасывает.

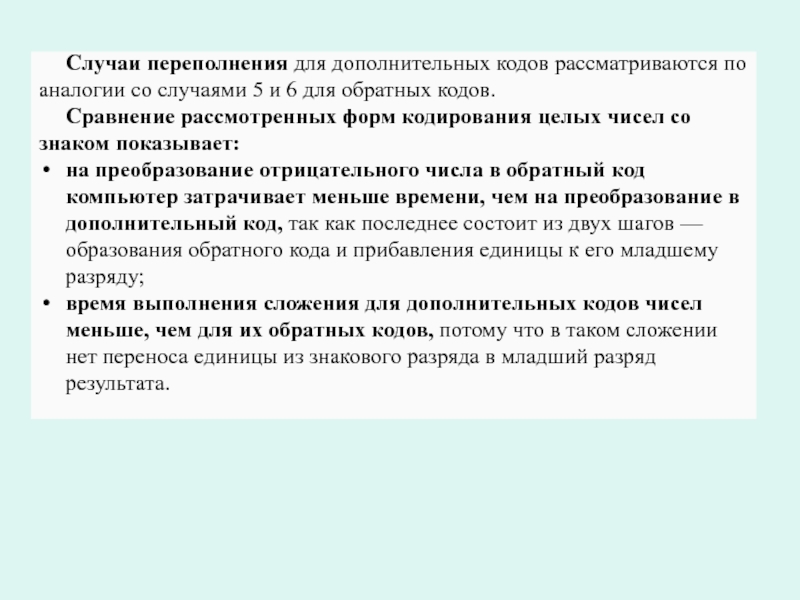

Слайд 11Случаи переполнения для дополнительных кодов рассматриваются по аналогии со случаями 5

и 6 для обратных кодов.

Сравнение рассмотренных форм кодирования целых чисел

со знаком показывает:

на преобразование отрицательного числа в обратный код компьютер затрачивает меньше времени, чем на преобразование в дополнительный код, так как последнее состоит из двух шагов — образования обратного кода и прибавления единицы к его младшему разряду;

время выполнения сложения для дополнительных кодов чисел меньше, чем для их обратных кодов, потому что в таком сложении нет переноса единицы из знакового разряда в младший разряд результата.

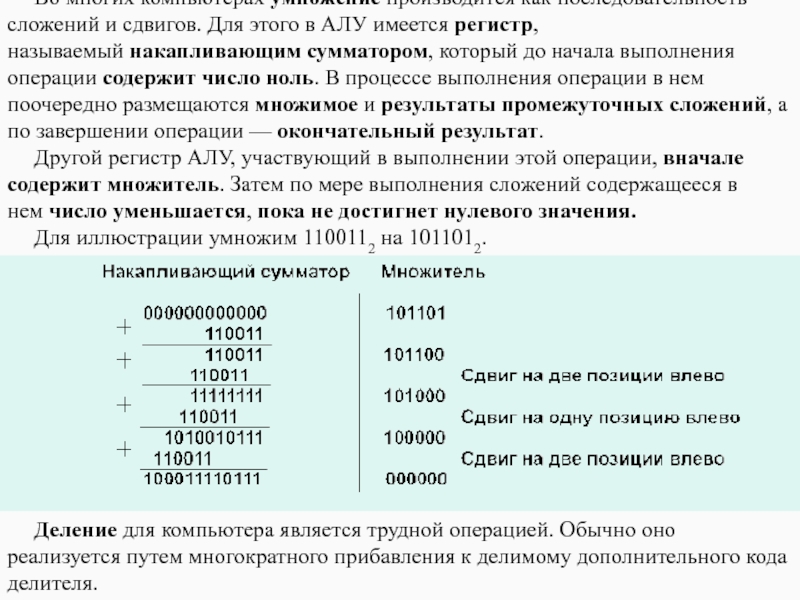

Умножение и деление

Во многих компьютерах умножение производится как последовательность сложений и сдвигов. Для этого в АЛУ имеется регистр, называемый накапливающим сумматором, который до начала выполнения операции содержит число ноль. В процессе выполнения операции в нем поочередно размещаются множимое и результаты промежуточных сложений, а по завершении операции — окончательный результат.

Другой регистр АЛУ, участвующий в выполнении этой операции, вначале содержит множитель. Затем по мере выполнения сложений содержащееся в нем число уменьшается, пока не достигнет нулевого значения.

Для иллюстрации умножим 1100112 на 1011012.

Деление для компьютера является трудной операцией. Обычно оно реализуется путем многократного прибавления к делимому дополнительного кода делителя.

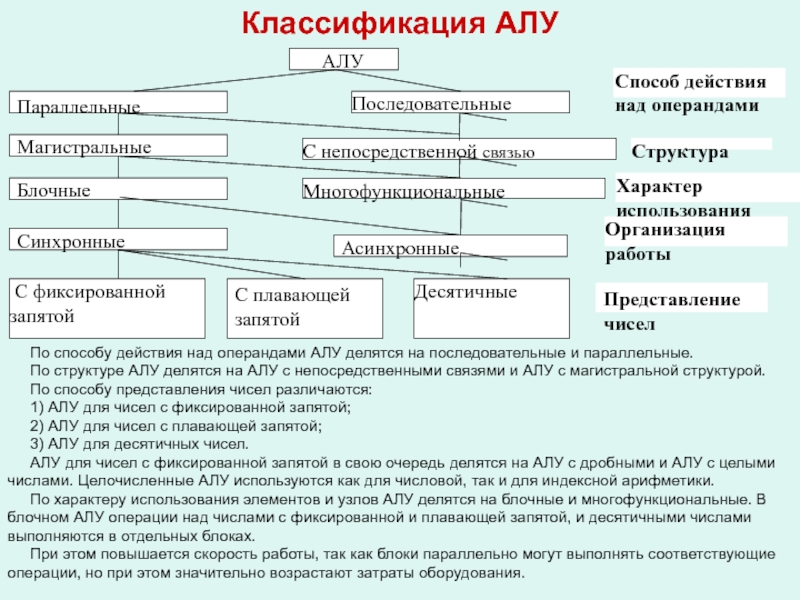

Слайд 13Классификация АЛУ

По способу действия над операндами АЛУ делятся на последовательные

и параллельные.

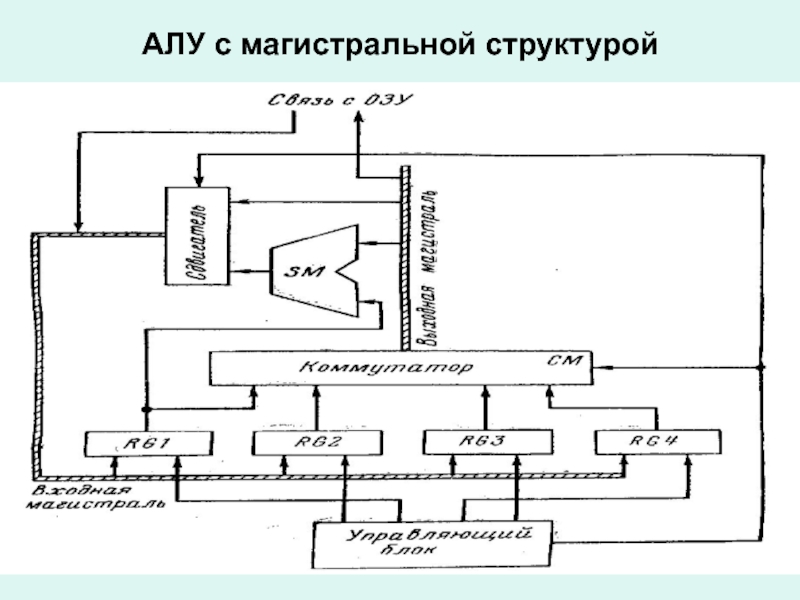

По структуре АЛУ делятся на АЛУ с непосредственными связями

и АЛУ с магистральной структурой.

По способу представления чисел различаются:

1) АЛУ для чисел с фиксированной запятой;

2) АЛУ для чисел с плавающей запятой;

3) АЛУ для десятичных чисел.

АЛУ для чисел с фиксированной запятой в свою очередь делятся на АЛУ с дробными и АЛУ с целыми числами. Целочисленные АЛУ используются как для числовой, так и для индексной арифметики.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей запятой, и десятичными числами выполняются в отдельных блоках.

При этом повышается скорость работы, так как блоки параллельно могут выполнять соответствующие операции, но при этом значительно возрастают затраты оборудования.

Слайд 14Вариант Подробной классификации АЛУ

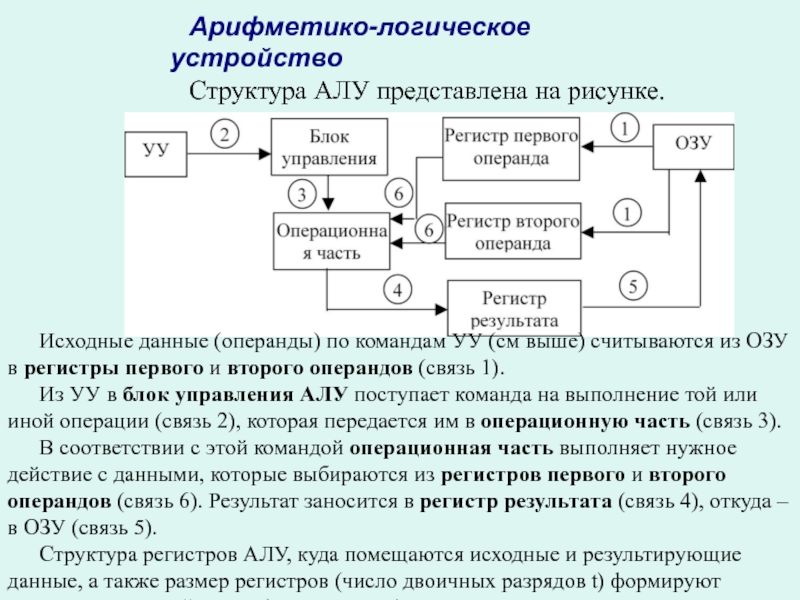

Слайд 15Арифметико-логическое устройство

Структура АЛУ представлена на рисунке.

Исходные данные (операнды) по командам

УУ (см выше) считываются из ОЗУ в регистры первого и

второго операндов (связь 1).

Из УУ в блок управления АЛУ поступает команда на выполнение той или иной операции (связь 2), которая передается им в операционную часть (связь 3).

В соответствии с этой командой операционная часть выполняет нужное действие с данными, которые выбираются из регистров первого и второго операндов (связь 6). Результат заносится в регистр результата (связь 4), откуда – в ОЗУ (связь 5).

Структура регистров АЛУ, куда помещаются исходные и результирующие данные, а также размер регистров (число двоичных разрядов t) формируют понятие разрядной сетки (далее – сетки), которое используется ниже.

Слайд 16

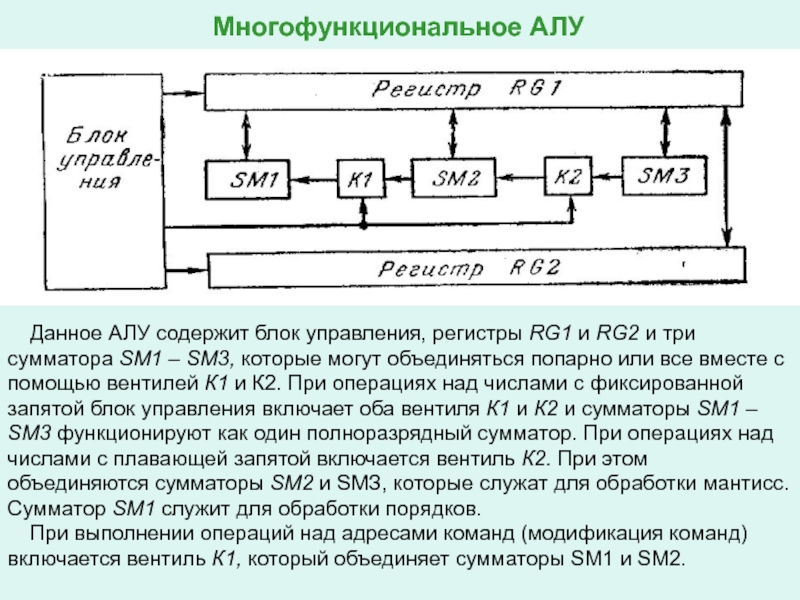

Многофункциональное АЛУ

Данное АЛУ содержит блок управления, регистры RG1 и

RG2 и три сумматора SM1 – SM3, которые могут объединяться

попарно или все вместе с помощью вентилей К1 и К2. При операциях над числами с фиксированной запятой блок управления включает оба вентиля К1 и К2 и сумматоры SМ1 – SM3 функционируют как один полноразрядный сумматор. При операциях над числами с плавающей запятой включается вентиль К2. При этом объединяются сумматоры SМ2 и SМЗ, которые служат для обработки мантисс. Сумматор SM1 служит для обработки порядков.

При выполнении операций над адресами команд (модификация команд) включается вентиль К1, который объединяет сумматоры SM1 и SM2.

Слайд 17АЛУ с непосредственными связями и накапливающим сумматором

Сумматор, схемы для

выполнения логических операций и cдвигов, а также схемы передач информации

соединены непосредственно с выходами соответствующих регистров. При этом операнды, участвующие в микрооперации, снимаются с определенных регистров и результаты образуются также в определенных регистрах. В многорегистровых АЛУ с магистральной структурой входы схем для выполнения сложения, логических операций и сдвигов соединены с магистральными шинами, на которые с помощью коммутатора может быть подключена информация с любого регистра АЛУ, а выходы этой аппаратуры подключены через коммутатор ко входным цепям регистров. При этом операнды для выполнения микроопераций могут быть взяты из любых регистров и результат также может быть передан в любой регистр.

В состав АЛУ входят три триггерных peгиcтpa RG1 – RG3 и управляющий блок.

Регистр RG1 имеет только схемы приема и выдачи информации. Регистры RG2,

RG3 имеют схемы приема, выдачи информации и схемы сдвига. Регистр RG3 одновременно является сумматором накапливающего типа. В RG3 также реализованы схемы выполнения поразрядных логических операций.

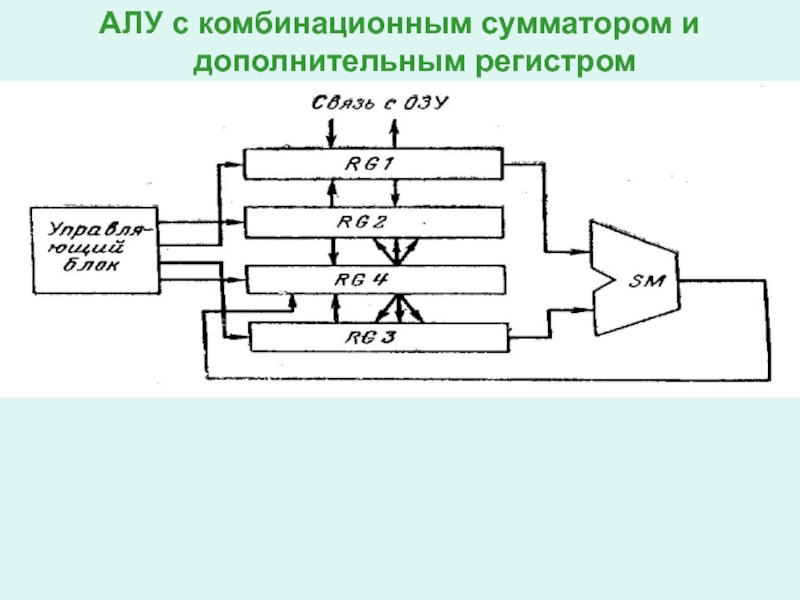

Слайд 18АЛУ с комбинационным сумматором и дополнительным регистром

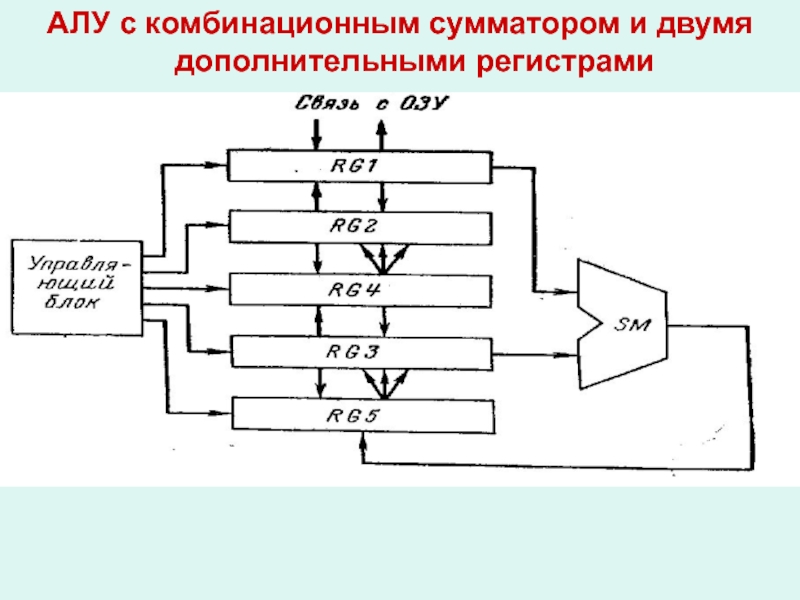

Слайд 19АЛУ с комбинационным сумматором и двумя дополнительными регистрами

Слайд 21Алгоритмы сложения (вычитания) и умножения

Структурная схема микропрограммы сложения

Слайд 22Выполнение этого алгоритма состоит в следующем:

Первое слагаемое а устанавливается на

Рг1, анализируется его знак: если знак отрицательный, то операнд инвертируется

и передается на Рг3, если положительный - передается без инверсии через Рг2 на Рг3

Второе слагаемое также устанавливается на Рг1 и анализируется его знак: если знак отрицательный, то операнд инвертируется, если положительный - сразу начинается суммирование операндов на Рг2 ( сумматоре )

После суммирования анализируется знак результата: если результат отрицательный, то он инвертируется, если положительный - добавляется “+1” ЦП к младшему разряду результата и выполняется анализ признаков переполнения

В случае переполнения разрядной сетки машины формируется признак переполнения ϕ, если переполнение отсутствует, то выполняется переход на конец микропрограммы сложения.

Для того, чтобы структурная схема, показанная на рис. 4 могла выполнять операцию вычитания, достаточно перед выполнением операции инвертировать знак второго слагаемого.

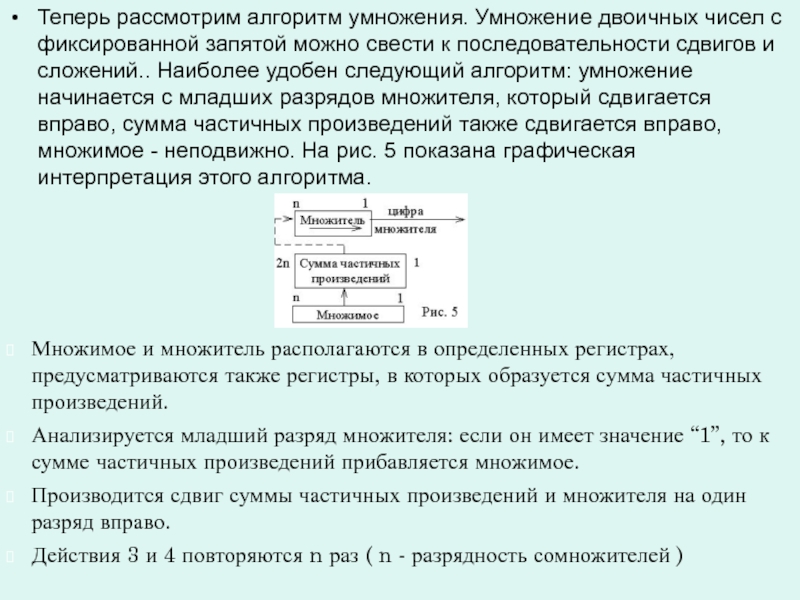

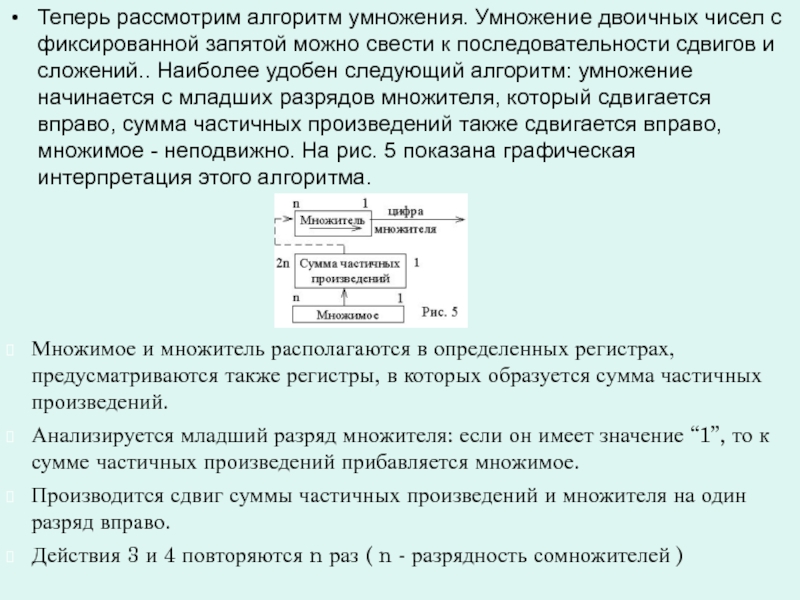

Слайд 23Теперь рассмотрим алгоритм умножения. Умножение двоичных чисел с фиксированной запятой

можно свести к последовательности сдвигов и сложений.. Наиболее удобен следующий

алгоритм: умножение начинается с младших разрядов множителя, который сдвигается вправо, сумма частичных произведений также сдвигается вправо, множимое - неподвижно. На рис. 5 показана графическая интерпретация этого алгоритма.

Множимое и множитель располагаются в определенных регистрах, предусматриваются также регистры, в которых образуется сумма частичных произведений.

Анализируется младший разряд множителя: если он имеет значение “1”, то к сумме частичных произведений прибавляется множимое.

Производится сдвиг суммы частичных произведений и множителя на один разряд вправо.

Действия 3 и 4 повторяются n раз ( n - разрядность сомножителей )

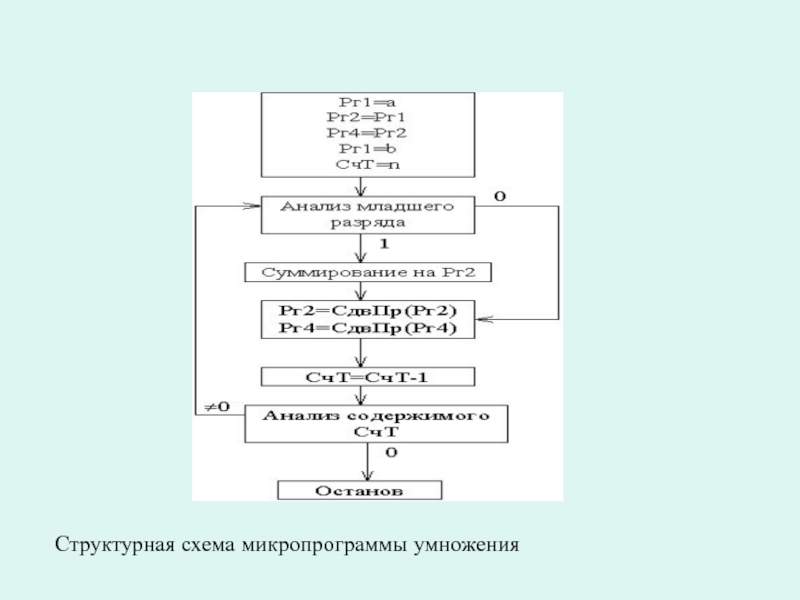

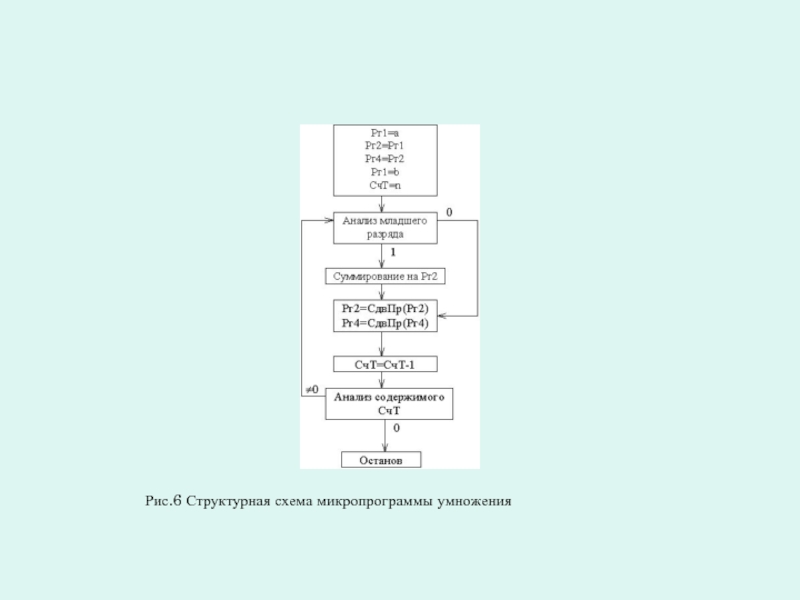

Слайд 24Структурная схема микропрограммы умножения

Слайд 26Умножение в вычислительной машине обычно сводится к последовательности операций прибавления

множимого к сумме уже ранее вычисленных частичных произведений и сдвига

получаемых сумм вправо на один разряд. Код множителя разряд за разрядом подается на элемент схемы, проверяющий наличие в поданном разряде 1 или 0. Если в данном разряде стоит 1, производится прибавление кода множимого к сумме, стоящей в сумматоре. Затем производится сдвиг новой суммы вправо на один разряд. Если в данном разряде множителя стоит 0, прибавление множимого не производится, а лишь выполняется сдвиг кода сумматора вправо на один разряд. Следует отметить, что произведение двух n-разрядных чисел может иметь 2n значащих разрядов. В ЭВМ, работающих с дробными числами, младшие n разрядов произведения часто отбрасываются.

Знак произведения получается в результате поразрядного сложения знаков сомножителей.

Для выполнения умножения АЛУ должно содержать, как минимум, три регистра: регистр, в котором находится множимое; регистр, в котором находится множитель, и регистр, в котором в процессе выполнения умножения накапливаются частичные произведения (будем называть его сумматором частичных произведений).

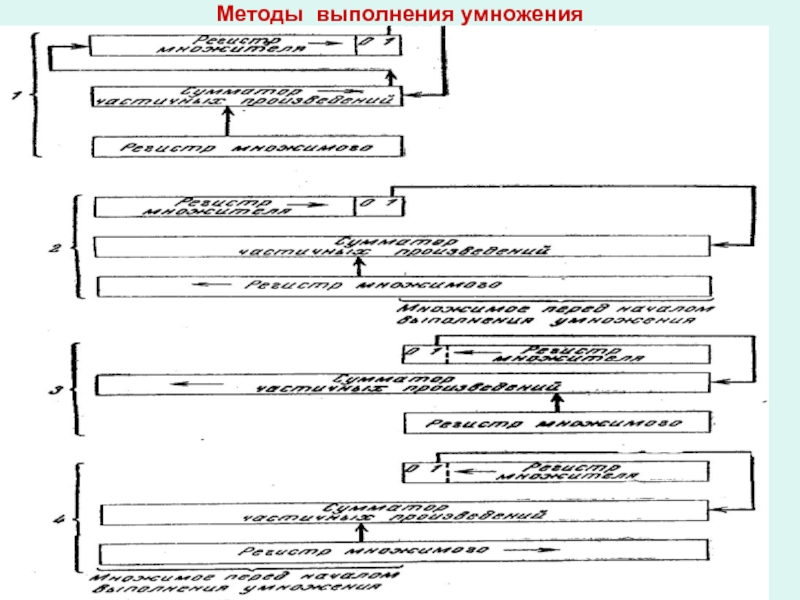

В зависимости от схем этих регистров возможны четыре метода выполнения умножения:

1. Умножение начиная с младших разрядов множителя при неподвижном множимом;

2. Умножение начиная с младших разрядов множителя при неподвижных частичных произведениях;

3. Умножение начиная со старших разрядов множителя при неподвижном множимом;

4. Умножение начиная со старших разрядов множителя при неподвижных частичных произведениях.

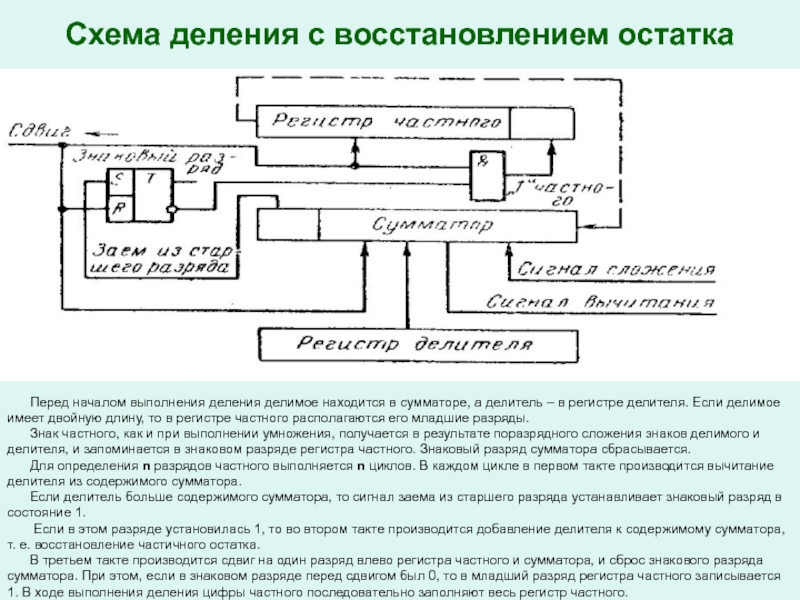

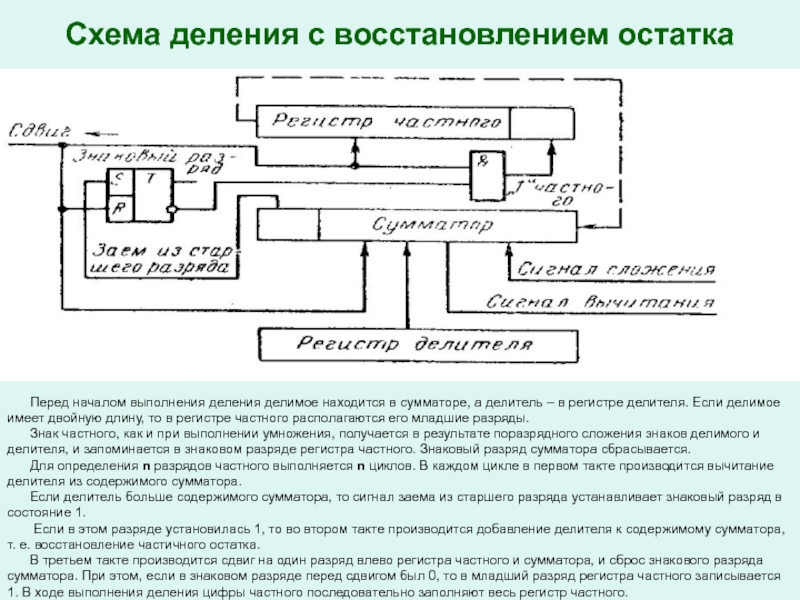

Слайд 27Схема деления с восстановлением остатка

Перед началом выполнения деления делимое находится

в сумматоре, а делитель – в регистре делителя. Если делимое

имеет двойную длину, то в регистре частного располагаются его младшие разряды.

Знак частного, как и при выполнении умножения, получается в результате поразрядного сложения знаков делимого и делителя, и запоминается в знаковом разряде регистра частного. Знаковый разряд сумматора сбрасывается.

Для определения n разрядов частного выполняется n циклов. В каждом цикле в первом такте производится вычитание делителя из содержимого сумматора.

Если делитель больше содержимого сумматора, то сигнал заема из старшего разряда устанавливает знаковый разряд в состояние 1.

Если в этом разряде установилась 1, то во втором такте производится добавление делителя к содержимому сумматора, т. е. восстановление частичного остатка.

В третьем такте производится сдвиг на один разряд влево регистра частного и сумматора, и сброс знакового разряда сумматора. При этом, если в знаковом разряде перед сдвигом был 0, то в младший разряд регистра частного записывается 1. В xoдe выполнения деления цифры частного последовательно заполняют весь регистр частного.

Слайд 28Обобщенная структурная схема АЛУ

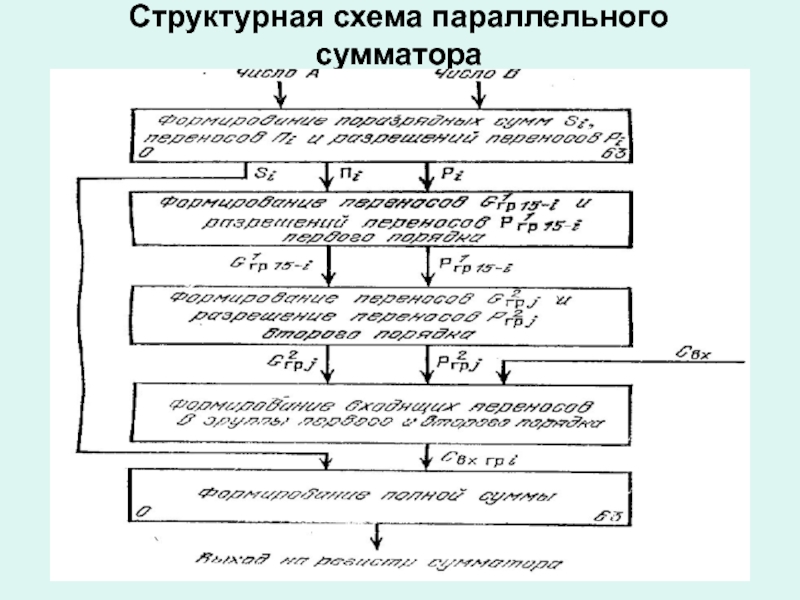

Слайд 29Структурная схема параллельного сумматора

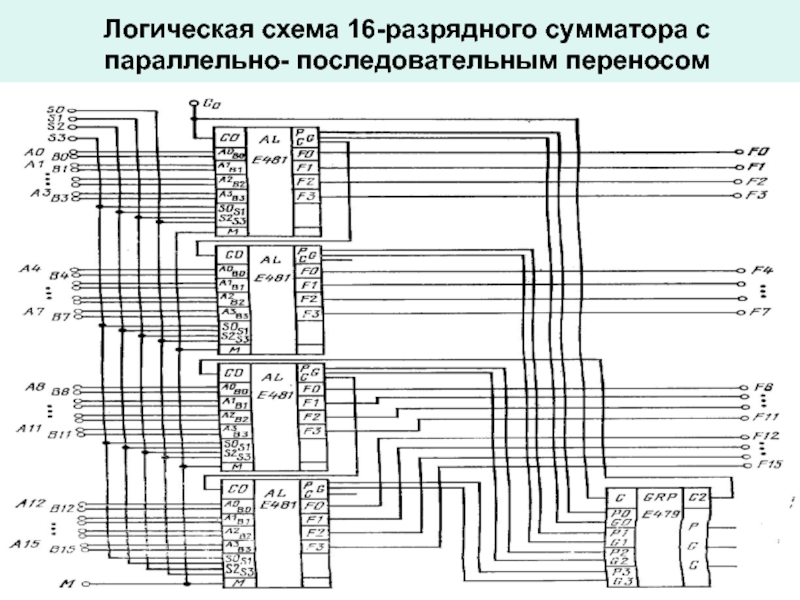

Слайд 30Логическая схема 16-разрядного сумматора с параллельно- последовательным переносом

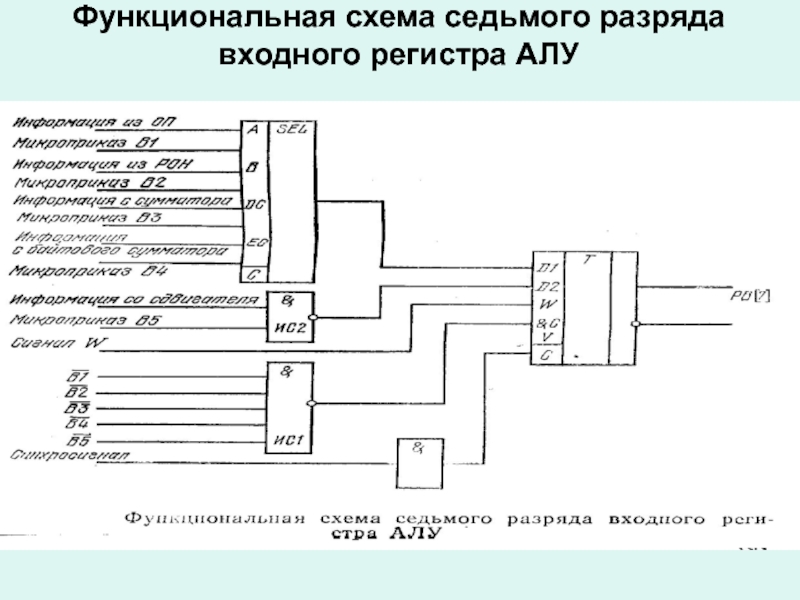

Слайд 31Функциональная схема седьмого разряда входного регистра АЛУ

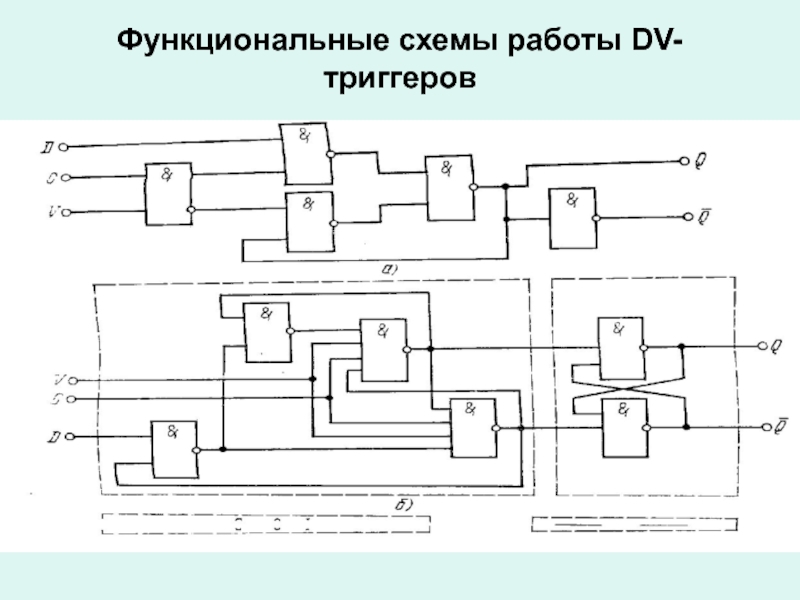

Слайд 32Функциональные схемы работы DV-триггеров

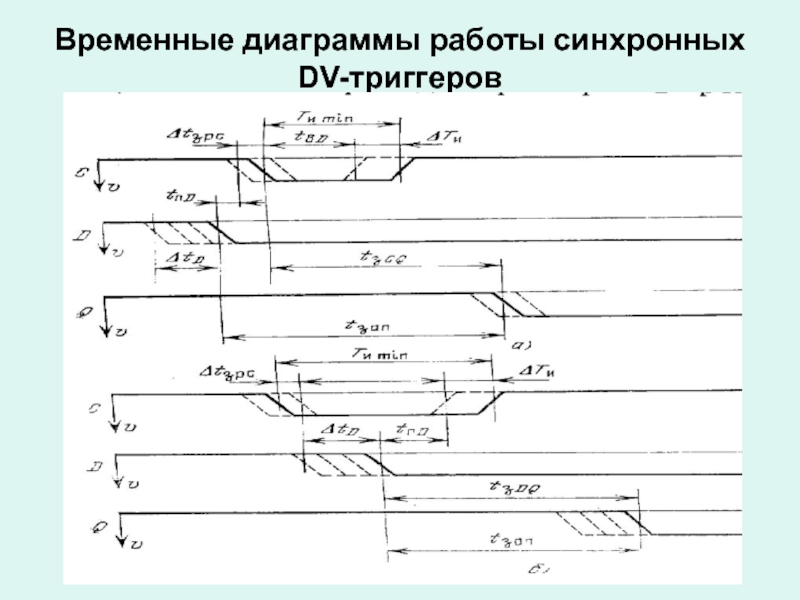

Слайд 33Временные диаграммы работы синхронных DV-триггеров

Слайд 35Арифметико-логическое устройство

Общие сведения, функции и классификация

Выполнили:

cтуденты группы ИС-1-07

Гринкевич Я.В.

Мандрыкин Д.А.

Киселев

П.Д.

Руководитель:

Мальшаков В. Д.

Москва, 2009г.

Слайд 36АЛУ реализует важную часть процесса обработки данных. Она заключается в

выполнении набора простых операций. Операции АЛУ подразделяются на три основные

категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление,...). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ,...). Операции над битами обычно подразумевают сдвиги.

АЛУ можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре. Подробная классификация АЛУ показана на рис. 3.

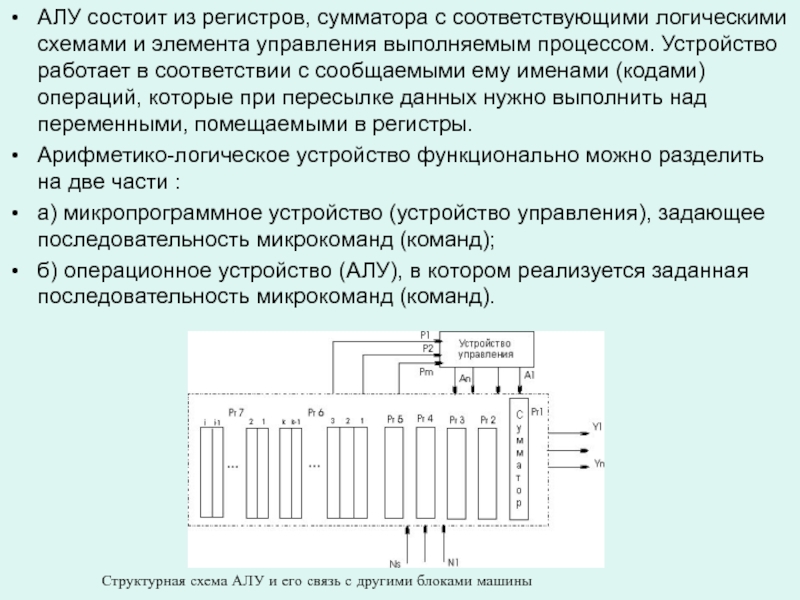

Слайд 38АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и

элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми

ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Структурная схема АЛУ и его связь с другими блоками машины

Слайд 39В состав АЛУ входят регистры Рг1 - Рг7, в которых

обрабатывается информация , поступающая из оперативной или пассивной памяти N1,

N2, ...NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, ..., Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2,..., Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2,..., рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, ...,уs, в ОЗУ.

Слайд 40Рг1 - сумматор (или сумматоры) - основной регистр АЛУ, в

котором образуется результат вычислений;

Рг2, РгЗ - регистры слагаемых, сомножителей,

делимого или делителя (в зависимости от выполняемой операции);

Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

Рг6 - k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе . Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

Функции регистров, входящих в АЛУ

Слайд 41Алгоритмы сложения (вычитания) и умножения

Структурная схема микропрограммы сложения

Слайд 42Выполнение этого алгоритма состоит в следующем:

Первое слагаемое а устанавливается на

Рг1, анализируется его знак: если знак отрицательный, то операнд инвертируется

и передается на Рг3, если положительный - передается без инверсии через Рг2 на Рг3

Второе слагаемое также устанавливается на Рг1 и анализируется его знак: если знак отрицательный, то операнд инвертируется, если положительный - сразу начинается суммирование операндов на Рг2 ( сумматоре )

После суммирования анализируется знак результата: если результат отрицательный, то он инвертируется, если положительный - добавляется “+1” ЦП к младшему разряду результата и выполняется анализ признаков переполнения

В случае переполнения разрядной сетки машины формируется признак переполнения ϕ, если переполнение отсутствует, то выполняется переход на конец микропрограммы сложения.

Для того, чтобы структурная схема, показанная на рис. 4 могла выполнять операцию вычитания, достаточно перед выполнением операции инвертировать знак второго слагаемого.

Слайд 43Теперь рассмотрим алгоритм умножения. Умножение двоичных чисел с фиксированной запятой

можно свести к последовательности сдвигов и сложений.. Наиболее удобен следующий

алгоритм: умножение начинается с младших разрядов множителя, который сдвигается вправо, сумма частичных произведений также сдвигается вправо, множимое - неподвижно. На рис. 5 показана графическая интерпретация этого алгоритма.

Множимое и множитель располагаются в определенных регистрах, предусматриваются также регистры, в которых образуется сумма частичных произведений.

Анализируется младший разряд множителя: если он имеет значение “1”, то к сумме частичных произведений прибавляется множимое.

Производится сдвиг суммы частичных произведений и множителя на один разряд вправо.

Действия 3 и 4 повторяются n раз ( n - разрядность сомножителей )

Слайд 44Рис.6 Структурная схема микропрограммы умножения