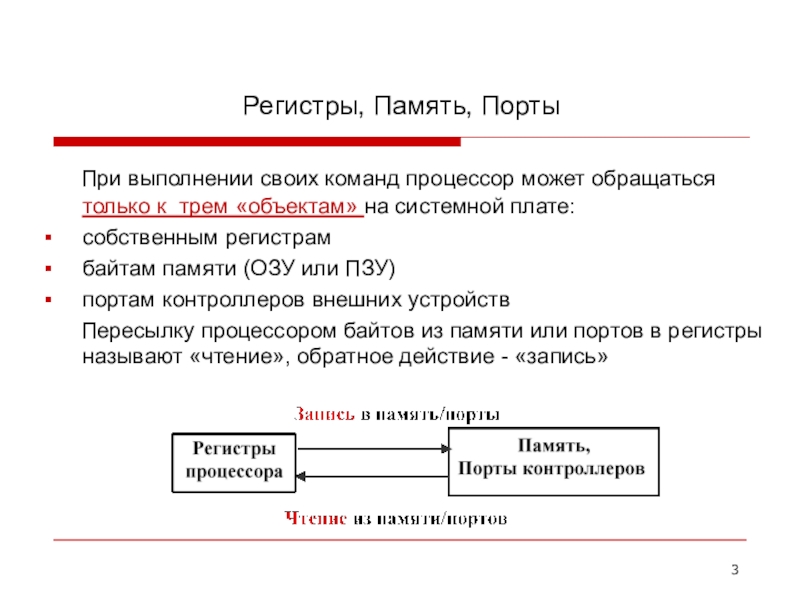

только к трем «объектам» на системной плате:

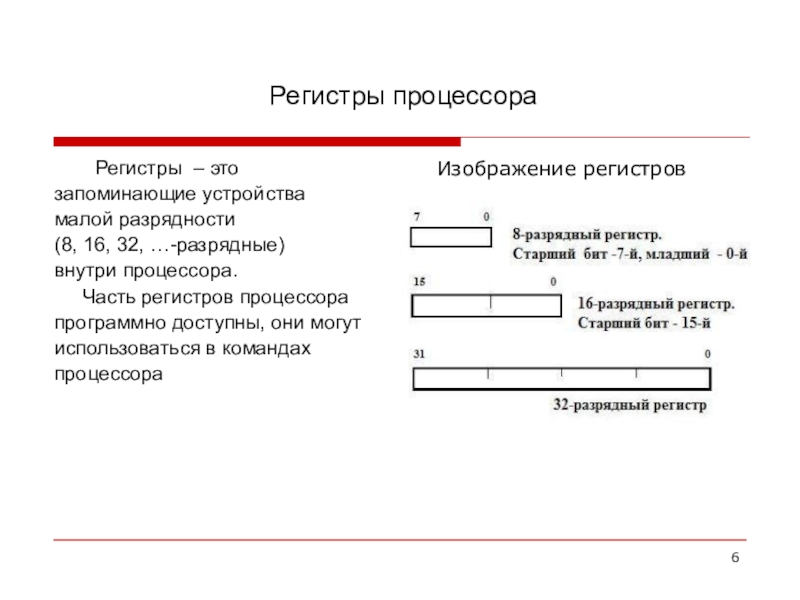

собственным регистрам

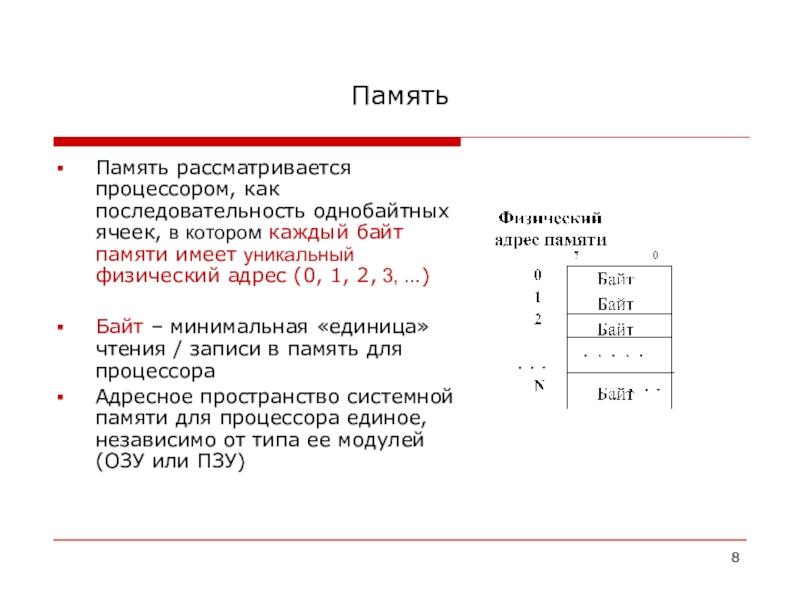

байтам памяти (ОЗУ

или ПЗУ)портам контроллеров внешних устройств

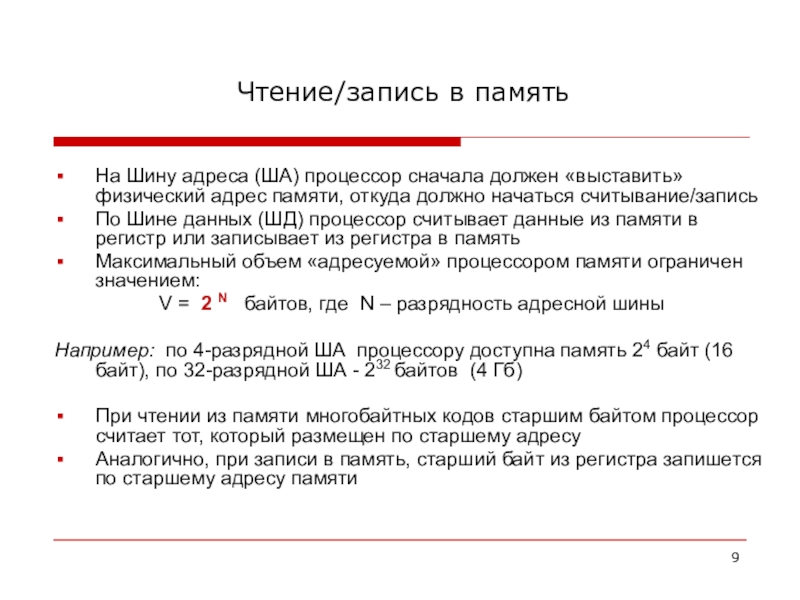

Пересылку процессором байтов из памяти или портов в регистры называют «чтение», обратное действие - «запись»