Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

мат сопроц

Содержание

- 1. мат сопроц

- 2. Математический сопроцессорФизический факультет, ЭВУ и системы, 7семестр,2010Математический

- 3. Основные понятияФизический факультет, ЭВУ и системы, 7семестр,2010

- 4. Схема взаимодействия центрального процессора и сопроцессораФизический факультет,

- 5. Физический факультет, ЭВУ и системы, 7семестр,2010 Схема

- 6. В случае отсутствия сопроцессораПрикладная программа использует инструкции

- 7. Форматы данных FPU позволяет представлять следующие категории

- 8. Не-числаКроме вещественных чисел (конечных нормализованных и денормализованных,

- 9. Не-числа могут определять такие случаи неопределённость (IND),

- 10. Устройство FPUФизический факультет, ЭВУ и системы, 7семестр,2010Модуль

- 11. Форматы чисел, поддерживаемых сопроцессоромФизический факультет, ЭВУ и системы, 7семестр,2010

- 12. Программная модель FPUФизический факультет, ЭВУ и системы,

- 13. Программная модель сопроцессоровФизический факультет, ЭВУ и системы, 7семестр,2009

- 14. Физический факультет, ЭВУ и системы, 7семестр,2010 Для

- 15. Старший байт регистра состояния содержит:Бит занятости B

- 16. Младший байт регистра состояния содержит флажки особых

- 17. Регистр тегов содержит 8 тегов - признаков,

- 18. Сопроцессор использует теги, чтобы определить переполнение или

- 19. Регистры математического сопроцессораФизический факультет, ЭВУ и системы,

- 20. Используемая литература:Книга «Процессоры «Pentium 4,Athlon и Duron»»,авторы

- 21. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Математический сопроцессор.

Форматы данных FPU.

Программная модель FPU.

Исключения и интерфейс сопроцессора

Физический

факультет, ЭВУ и системы, 7 семестр,2010

Слайд 2Математический сопроцессор

Физический факультет, ЭВУ и системы, 7семестр,2010

Математический сопроцессор — сопроцессор

для расширения командного множества центрального процессора и обеспечивающий его функциональностью

модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля. Он может как представлять собой устройство в отдельном корпусе, так находиться вместе с центральным процессором на одном кристалле.Слайд 3Основные понятия

Физический факультет, ЭВУ и системы, 7семестр,2010

Основным исполнительным устройством

математического сопроцессора является устройство обработки чисел с плавающей запятой(FPU –

floating point unit).Как правило, он не может самостоятельно выполнять программный код и получает поток инструкций от центрального процессора. Таким образом программы для центрального процессора и математического сопроцессора находятся в одном потоке инструкций.

Однако сопроцессор при этом обладает собственным микропрограммным автоматом, набором регистров и исполнительными устройствами, таком образом являясь функционально независимым.

Слайд 4Схема взаимодействия центрального процессора и сопроцессора

Физический факультет, ЭВУ и системы,

7семестр,2010

Сопроцессор подключен к шинам центрального процессора, а также имеет

несколько специальных сигналов для синхронизации процессоров между собой.Часть командных кодов центрального процессора зарезервирована для сопроцессора, он следит за потоком команд, игнорируя другие команды. Центральный процессор, наоборот, игнорирует команды сопроцессора, занимаясь только вычислением адреса в памяти, если команда предполагает к ней обращение. Центральный процессор делает цикл фиктивного считывания, позволяя сопроцессору считать адрес с адресной шины. Если сопроцессору необходимо дополнительное обращение к памяти (для чтения или записи результатов), он выполняет его через захват шины.

Слайд 5Физический факультет, ЭВУ и системы, 7семестр,2010

Схема взаимодействия центрального процессора

и сопроцессора

После получения команды и необходимых данных сопроцессор начинает её

выполнение. Пока сопроцессор выполняет команду, центральный процессор выполняет программу дальше, параллельно с вычислениями сопроцессора. Если следующая команда также является командой сопроцессора, процессор останавливается и ожидает завершения выполнения сопроцессором предыдущей команды.Также существует специальная команда ожидания (FWAIT), принудительно останавливающая процессор до завершения вычислений (если для продолжения программы необходимы их результаты).

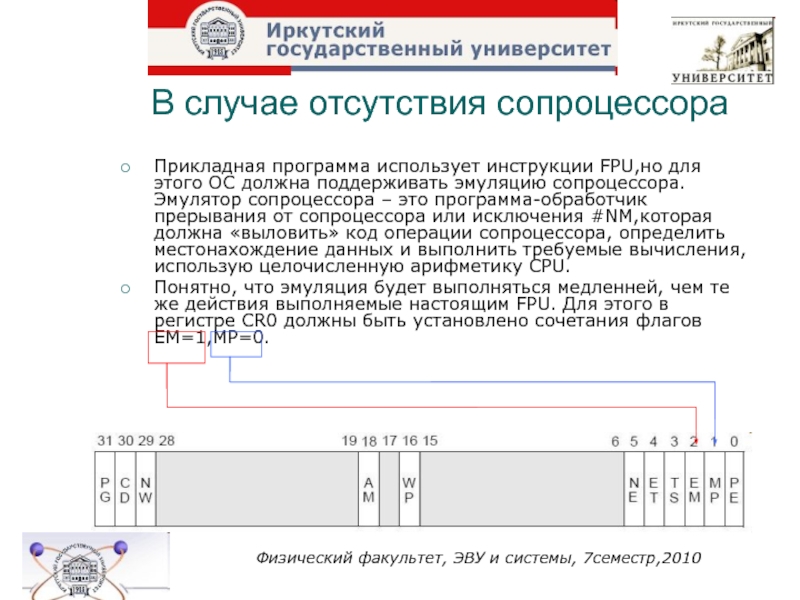

Слайд 6В случае отсутствия сопроцессора

Прикладная программа использует инструкции FPU,но для этого

ОС должна поддерживать эмуляцию сопроцессора. Эмулятор сопроцессора – это программа-обработчик

прерывания от сопроцессора или исключения #NM,которая должна «выловить» код операции сопроцессора, определить местонахождение данных и выполнить требуемые вычисления, использую целочисленную арифметику CPU.Понятно, что эмуляция будет выполняться медленней, чем те же действия выполняемые настоящим FPU. Для этого в регистре CR0 должны быть установлено сочетания флагов EM=1,MP=0.

Физический факультет, ЭВУ и системы, 7семестр,2010

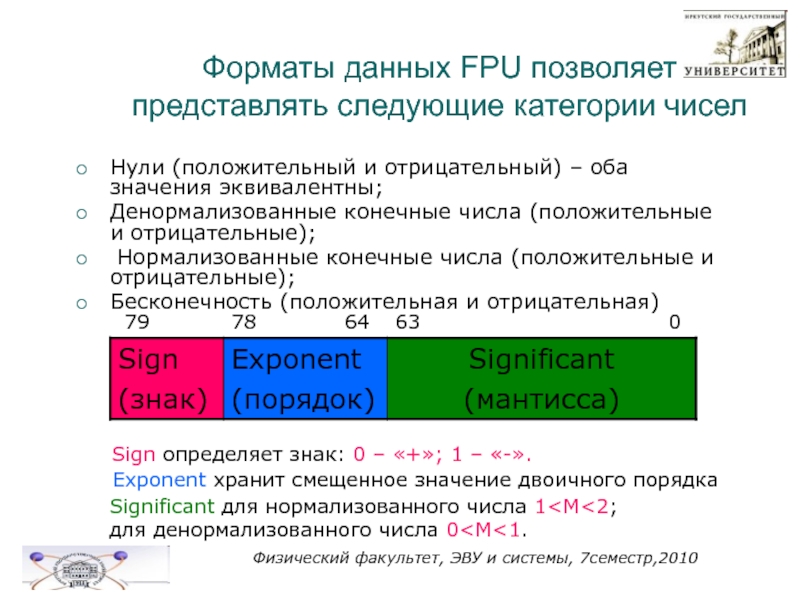

Слайд 7Форматы данных FPU позволяет представлять следующие категории чисел

Нули (положительный и

отрицательный) – оба значения эквивалентны;

Денормализованные конечные числа (положительные и отрицательные);

Нормализованные конечные числа (положительные и отрицательные);Бесконечность (положительная и отрицательная)

Физический факультет, ЭВУ и системы, 7семестр,2010

79

78

64

63

0

Sign определяет знак: 0 – «+»; 1 – «-».

Exponent хранит смещенное значение двоичного порядка

Significant для нормализованного числа 1

Слайд 8Не-числа

Кроме вещественных чисел (конечных нормализованных и денормализованных, нулей и бесконечности)

регистры сопроцессора могут содержать не-числа NaN (Not a Number) четырех

видов:-SNaN и +SNaN – порядок 111…111, мантисса 1,0ххх…ххх (ненулевая). Эти сигнализирующие не-числа (signaling NaN) вызывают исключения сопроцессора, если с ними пытаются выполнить арифметические действия.

-QNaN и +QNaN – порядок 111…111, мантисса 1,1ххх…ххх (ненулевая). Эти «тихие» не-числа (quiet NaN) не вызывают исключений при арифметических операциях.

Физический факультет, ЭВУ и системы, 7семестр,2010

Слайд 9Не-числа могут определять такие случаи

неопределённость (IND), возникает при комплексном

результате (например, при вычислении квадратного корня из отрицательного числа) и

в некоторых других случаях,недействительное значение (qNaN, sNaN) - может использоваться компилятором (для предотвращения использования неинициализированных переменных) или отладчиком,

нуль - в формате с плавающей запятой, нуль также считается специальным значением.

Физический факультет, ЭВУ и системы, 7семестр,2010

Слайд 10Устройство FPU

Физический факультет, ЭВУ и системы, 7семестр,2010

Модуль операций с плавающей

запятой представляет собой стековый калькулятор, работающий по принципу обратной польской

записи. Перед операцией аргументы помещаются в LIFO-стек, при выполнении операции необходимое количество аргументов снимается со стека. Результат операции помещается в стек, где может быть использован в дальнейших вычислениях или может быть снят со стека для записи в память. Также поддерживается и прямая адресация аргументов в стеке относительно вершины.Поддерживаемые математические операции: арифметические операции, сравнение, деление по модулю, округление, смена знака, модуль, квадратный корень, синус, косинус, частичный тангенс, частичный арктангенс, загрузка константы (0, 1, число пи, log2(10), log2(e), lg(2), ln(2)) и некоторые другие специфические операции.

Слайд 11Форматы чисел, поддерживаемых сопроцессором

Физический факультет, ЭВУ и системы, 7семестр,2010

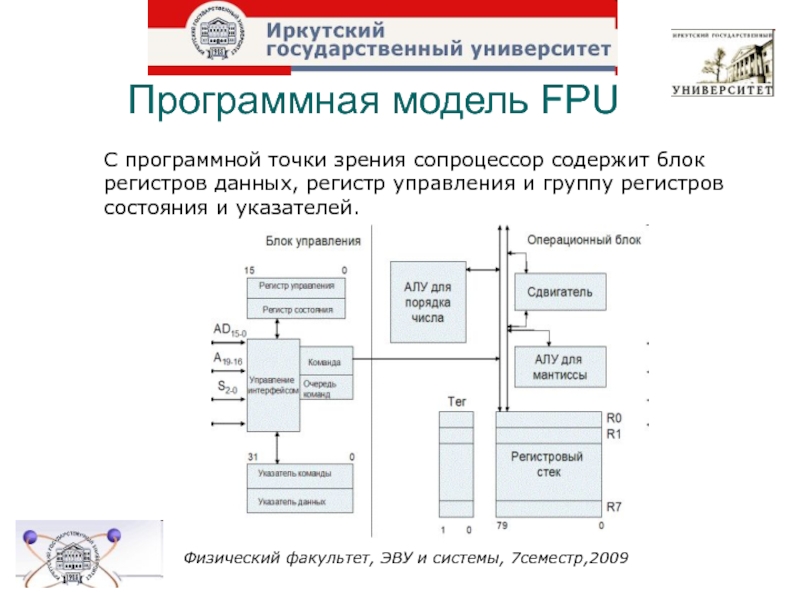

Слайд 12Программная модель FPU

Физический факультет, ЭВУ и системы, 7семестр,2009

С программной

точки зрения сопроцессор содержит блок

регистров данных, регистр управления и

группу регистров состояния и указателей.

Слайд 14Физический факультет, ЭВУ и системы, 7семестр,2010

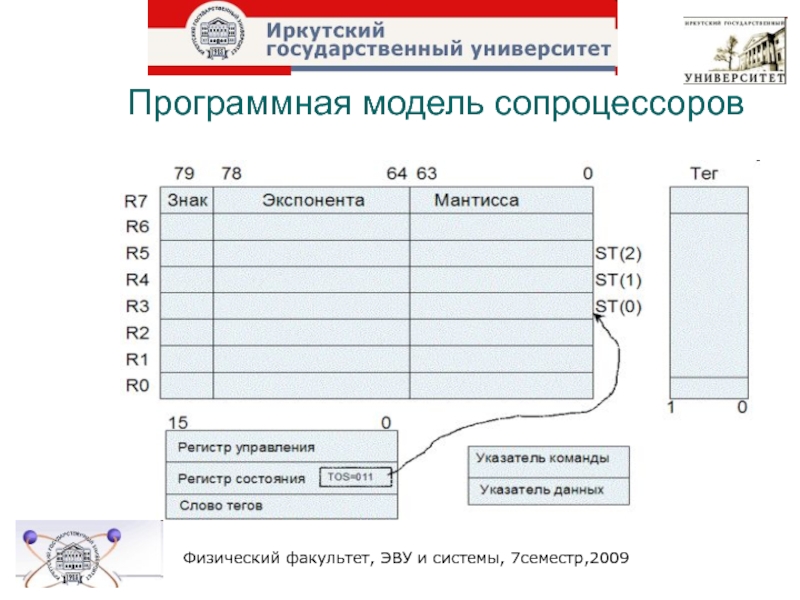

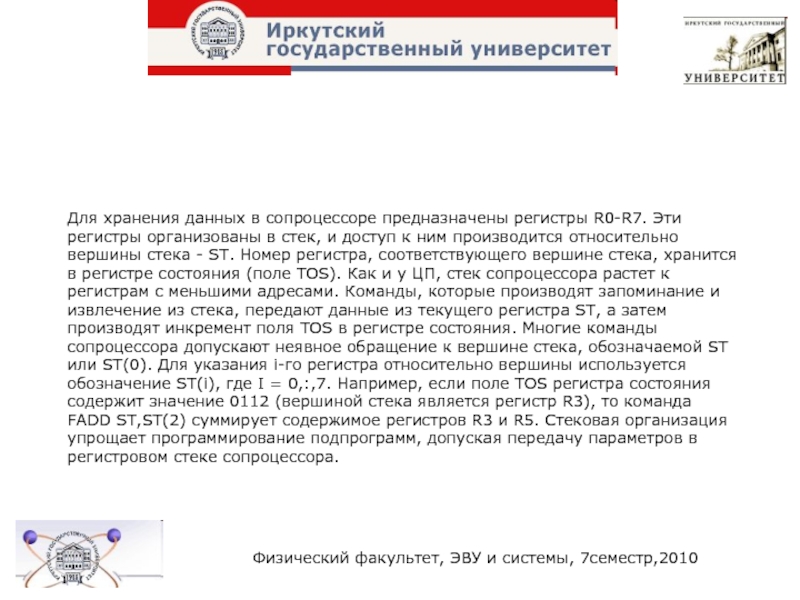

Для хранения данных в

сопроцессоре предназначены регистры R0-R7. Эти регистры организованы в стек, и

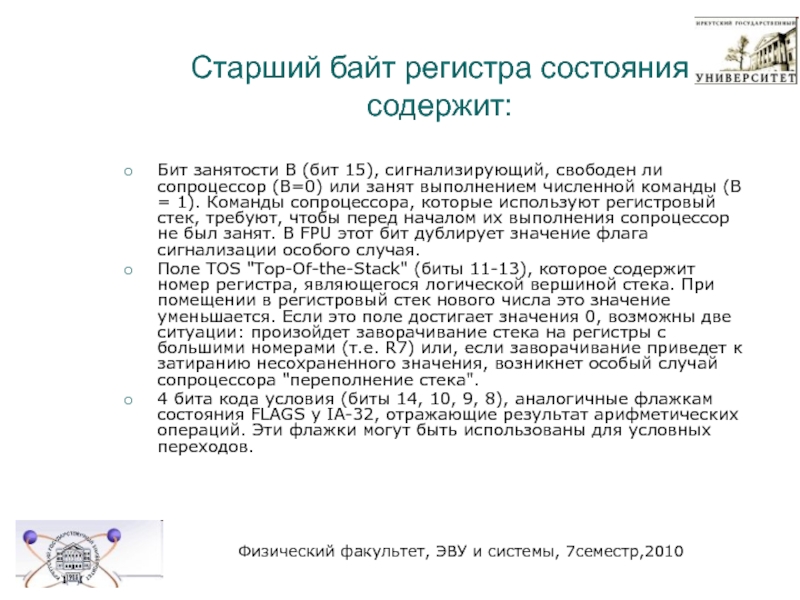

доступ к ним производится относительно вершины стека - ST. Номер регистра, соответствующего вершине стека, хранится в регистре состояния (поле TOS). Как и у ЦП, стек сопроцессора растет к регистрам с меньшими адресами. Команды, которые производят запоминание и извлечение из стека, передают данные из текущего регистра ST, а затем производят инкремент поля TOS в регистре состояния. Многие команды сопроцессора допускают неявное обращение к вершине стека, обозначаемой ST или ST(0). Для указания i-го регистра относительно вершины используется обозначение ST(i), где I = 0,:,7. Например, если поле TOS регистра состояния содержит значение 0112 (вершиной стека является регистр R3), то команда FADD ST,ST(2) суммирует содержимое регистров R3 и R5. Стековая организация упрощает программирование подпрограмм, допуская передачу параметров в регистровом стеке сопроцессора.Слайд 15Старший байт регистра состояния содержит:

Бит занятости B (бит 15), сигнализирующий,

свободен ли сопроцессор (B=0) или занят выполнением численной команды (B

= 1). Команды сопроцессора, которые используют регистровый стек, требуют, чтобы перед началом их выполнения сопроцессор не был занят. В FPU этот бит дублирует значение флага сигнализации особого случая.Поле TOS "Top-Of-the-Stack" (биты 11-13), которое содержит номер регистра, являющегося логической вершиной стека. При помещении в регистровый стек нового числа это значение уменьшается. Если это поле достигает значения 0, возможны две ситуации: произойдет заворачивание стека на регистры с большими номерами (т.е. R7) или, если заворачивание приведет к затиранию несохраненного значения, возникнет особый случай сопроцессора "переполнение стека".

4 бита кода условия (биты 14, 10, 9, 8), аналогичные флажкам состояния FLAGS у IA-32, отражающие результат арифметических операций. Эти флажки могут быть использованы для условных переходов.

Физический факультет, ЭВУ и системы, 7семестр,2010

Слайд 16Младший байт регистра состояния содержит флажки особых случаев сопроцессора: переполнение

стека, потеря точности, потеря значащих разрядов, численное переполнение, деление на

ноль, денормализация, недействительная операция. Если соответствующий особый случай возник и не был замаскирован (в слове управления), это приведет к генерации центральным процессором особого случая сопроцессора (#16).Младшее слово регистра управления содержит биты масок особых случаев. Сопроцессор допускает индивидуальное маскирование особых случаев. Если тот или иной особый случай замаскирован, при возникновении соответствующей ситуации сопроцессор выполняет некоторые заранее определенные внутренние действия, которые зачастую приемлемы для большинства применений. Например, если замаскирован особый случай деления на ноль, то выполнение операции 85,32/0 даст результат + ∞.

Старшее слово регистра управления содержит два поля: управление точностью PC (биты 8 и 9) и управление округлением RC (биты 10 и 11). Биты управления точностью можно использовать для понижения точности вычислений. По умолчанию используется расширенная точность (PC = 112), можно также использовать двойную точность (PC = 102) и одинарную точность (PC = 002)

Физический факультет, ЭВУ и системы, 7семестр,2010

Слайд 17Регистр тегов содержит 8 тегов - признаков, характеризующих содержимое соответствующего

численного регистра сопроцессора. Тег может принимать следующие значения:

00 - в

регистре находится действительное число;01 - нулевое число в регистре;

10 - недействительное число (бесконечность, денормализованное число, не-число);

11 - пустой регистр.

Физический факультет, ЭВУ и системы, 7семестр,2010

Слайд 18Сопроцессор использует теги, чтобы определить переполнение или опустошение стека. Если

при помещении в стек очередного числа окажется, что декрементированный TOS

указывает на непустой регистр (соответствующий тег не равен 112), сопроцессор сигнализирует о переполнении стека. Если при извлечении из стека числа окажется, что инкрементированный TOS указывает на пустой регистр (соответствующий тег равен 112), сопроцессор сигнализирует об опустошении стека.Физический факультет, ЭВУ и системы, 7семестр,2010

Для команд сопроцессора выделена группа кодов, начинающаяся с 11011ххх. В ассемблерах мнемоники команд сопроцессора начинаются с "F": FADD (сложение), FCOM (сравнение), FCOS (косинус), FDIV (деление) и т.п.

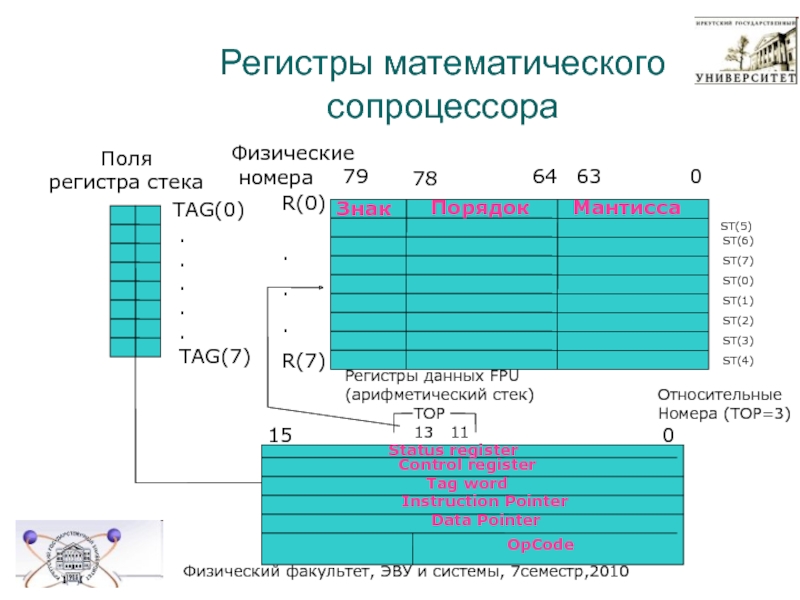

Слайд 19Регистры математического сопроцессора

Физический факультет, ЭВУ и системы, 7семестр,2010

Знак

Порядок

Мантисса

Поля

регистра стека

TAG(0)

.

.

.

.

.

TAG(7)

79

78

64

63

0

R(0)

.

.

.

R(7)

Физические

номера

ST(5)

ST(6)

ST(7)

ST(0)

ST(1)

ST(2)

ST(3)

ST(4)

Относительные

Номера

(ТОР=3)

Регистры данных FPU

(арифметический стек)

Status register

Control register

Tag word

Instruction Pointer

Data Pointer

OpCode

15

0

TOP

13

11Слайд 20Используемая литература:

Книга «Процессоры «Pentium 4,Athlon и Duron»»,авторы Михаил Гук, Виктор

Юров

Книга «Ассемблер. Учебник для ВУЗов», авторы Михаил Гук, Виктор

ЮровКнига «Архитектура ЭВМ»,автор Мюллер

http://www.intuit.ru/department/hardware/csorg/8/2.htm

http://ar-pc.ru/pc/200636/l

soft-tlt.ru/programmsi1.html

http://cs.njit.edu/~sohn/cs650/

Физический факультет, ЭВУ и системы, 7семестр,2010