Слайд 1Микропроцессор

Микропроцессор (МП) - программно-аппаратное устройство, изготовленные в одном кристалле, в

виде большой (БИС) или сверхбольшой интегральной схемы (СБИС) и предназначенные

для обработки информации представленной в двоичной форме (арифметические и логические операции над двоичными информацией).

Микропроцессорные системы (МПС) - программно-аппаратная система ядром которого является МП и память, обладающая в идеале возможностями приема, обработки и вывода любой информации (сигнал, текст, видео, речь и т.д.) в заданной разработчиком форме и алгоритму.

Слайд 2Классификация МП.

По разрядности данных: 8-, 16- ,32- , 64- разрядные

По конструктивному исполнению делятся:

- однокристальные МП;

- многокристальные

МП.

К однокристальным относятся МП вся схема которой расположено в теле одного кристалла и выполняет все заданные функции.

Многокристальные МП делятся на два класса:

- многокристальные МП с фиксированной разрядностью в 4 и 8 разрядов, из которых с помощью объединяющих интерфейсных микросхем можно собрать 8,16,32 и 64 разрядные МП;

- секционные многокристальные МП с разделением функции выполняемого одним кристаллом, например: 8 разрядная секция АЛУ; 8 разрядная секция РОН, 8 разрядная секция УУ и т.д.. из комплекта которых можно собрать 8 разрядный МП

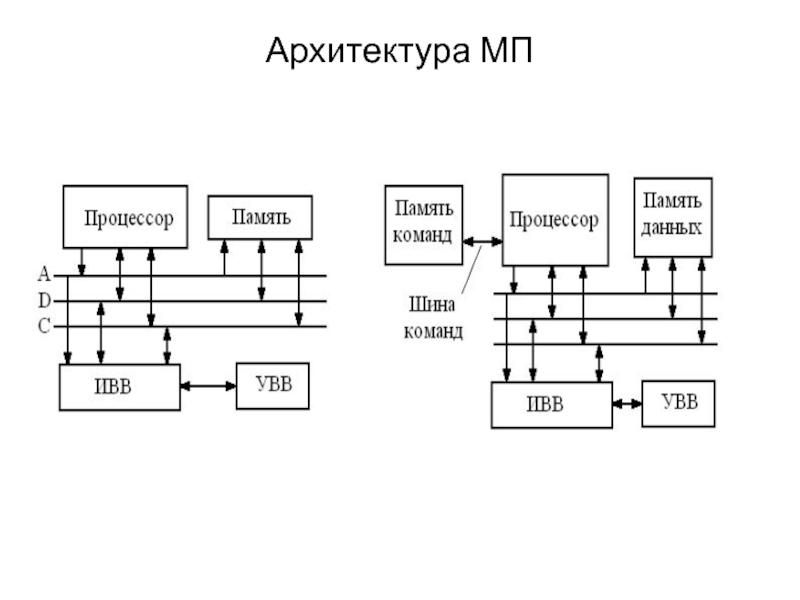

Слайд 3Архитектура

Архитектура процессоров делится на два вида:

- фон-Неймановская,

когда в МП реализуется концепция хранимой программы: программы и данные

хранятся в одной и той же памяти;

- Гарвардская архитектура. Особенностью этой архитектуры является то, что память данных и программ разделены и имеют отдельные шины.

Слайд 6Микроконтроллер

Микроконтроллером называется МПС с встроенной памятью программ

и данных, а также встроенным интерфейсом для подключения внешних устройств,

предназначенные для использования в системах управления технологическим оборудованием и/или процессами.

В общем смысле под архитектурой процессора понимается его программная модель, то есть программно-видимые свойства. Под микроархитектурой понимается внутренняя реализация этой программной модели. Для одной и той же архитектуры применяются существенно различные микроархитектурные реализации. Сейчас существует множество архитектур процессоров, которые делятся на три категории – RISC, CISC и VLIW.

Слайд 7Микроархитектура МП

RISC - Reduced (Restricted) Instruction Set Computer - процессоры

(компьютеры) с сокращенной системой команд. Система команд отличается относительной простотой,

коды инструкций имеют четкую структуру, как правило, с фиксированной длиной.

CISC - Complete Instruction Set Computer - процессоры (компьютеры) с полным набором инструкций, к которым относится и семейство х86.

Отличием CISC –процессоров от RISC –процессоров является:

регистры существенно неоднородны;

широкий набор команд усложняет декодирование инструкций, на что расходуются аппаратные ресурсы;

возрастает число тактов, необходимое для выполнения инструкций.

К RISC –процессорам относятся первые х86, которые имеют самую сложную в мире систему команд. В процессорах семейства х86, начиная с 486, применяется комбинированная архитектура - CISC-процессор имеет RISC-ядро.

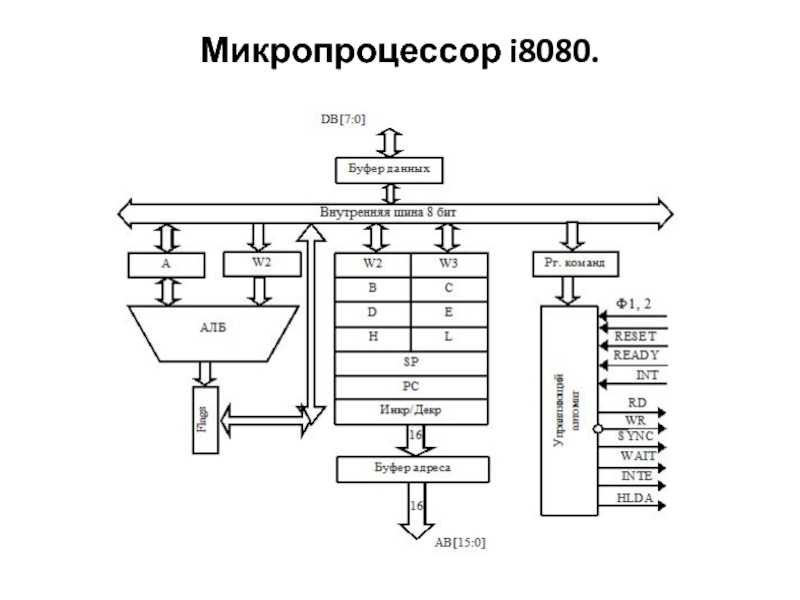

Слайд 9Назначение входных и выходных линий МП

Ф1,Ф2 - сигналы тактового

генератора частотой 1..2,5 МГц;

RESET - сброс (начальная установка и

запуск программы с адреса 0000);

READY - входной сигнал готовности памяти или ВУ к обмену (обеспечивает асинхронный режим обмена);

INT - запрос внешнего прерывания;

HOLD - захват шины (требование прямого доступа в память со стороны ВУ);

WR - запись - выходной сигнал, определяющий направление передачи информации по шине данных от процессора к памяти или ВУ;

RD - чтение - выходной сигнал, определяющий направление передачи информации по шине данных от памяти или ВУ к процессору;

SYNC - выходной сигнал, идентифицирующий наличие на шине данных дополнительной управляющей информации (PSW);

WAIT - выходной сигнал, отмечающий состояние ожидания или останова МП;

INTE - выходной сигнал, подтверждающий режим внешних прерываний;

HLDA - выходной сигнал, подтверждающий режим прямого доступа в память (подтверждение захвата).

Слайд 10Командный цикл микропроцессора.

В основе работы МП лежит командный цикл -

действия по выбору из памяти и выполнению одной команды. В

зависимости от типа и формата команды, способов адресации и числа операндов командный цикл может включать в себя различное число обращений к памяти .

Любой командный цикл (КЦ) начинается с извлечения из памяти первого байта команды по адресу, хранящемуся в PC. Команды i8080 имеют длину 1, 2 или 3 байта, причем в первом байте содержится информация о длине команды. В случае 2- или 3-байтовой команды реализуются дополнительные обращения к памяти по соседним адресам.

После считывания команды начинается ее выполнение, причем в процессе выполнения может потребоваться еще одно или несколько обращений к памяти или ВУ (чтение операнда, запись результата).

Для реализации команды i8080 может потребоваться от 1 до 5 обращений к памяти (ВУ). Действия МПС по передаче в/из МП одного байта данных/команды называются машинным циклом.

Слайд 11Машинные циклы и их идентификация

Командный цикл представляет собой последовательность машинных

циклов (МЦ), причем КЦ i8080 может содержать от 1 до

5 МЦ, которые принято обозначать M1, M2,..M5.

МЦ обязательно включает в себя действия по передаче байта информации. Кроме того, в некоторых МЦ дополнительно реализуются действия по пересылке и/или преобразованию информации внутри МП. Поэтому длительность МЦ может быть различной - за счет различного числа содержащихся в них машинных тактов (T1, T2,...).

Машинный такт образует пара сигналов тактового генератора Ф1, Ф2, поэтому длительность такта постоянна - период тактового генератора (за исключением такта Tw - см. ниже).

С помощью входа READY можно не только согласовывать работу МП с устройствами различного быстродействия, но и реализовывать пошаговый и потактовый режимы работы МП:

- выдача адреса;

- выдача информации о начатом МЦ;

- анализ значения входных сигналов;

- при необходимости – ожидание сигнала готовности;

- прием/выдача данных;

- при необходимости – внутренняя обработка/пересылка данных.

Слайд 12Машинный цикл

При реализации одного МЦ процессор может:

принять из памяти байт

команды или принять из памяти байт данных;

принять из УВВ байт

данных;

принять из стека байт данных;

принять вектор прерывания;

выдать в память байт данных;

выдать в стек байт данных;

выдать на УВВ байт данных.

Для выдачи более полной информации о состоянии МП в текущем МЦ используется мультиплексированные шины данных. В начале каждого МЦ на линий шины данных D [7:0] выдается байт дополнительной управляющей информации записывающиеся во внешний регистр состояния (PSW), разряды которого имеют следующее значение:

D0 - подтверждение прерывания; D1 - запись (в ЗУ) или вывод (на УВыв);

D2 - обращение в стек; D3 - подтверждение останова;

D4 - вывод (на УВыв); D5 - M1 (считывание из памяти первого байта команды);

D6 - ввод (из УВв); D7 - чтение (из ЗУ).

Наличие управляющей информации отмечается специальным выходным сигналом SYNC.

Слайд 13Организация прямого доступа к памяти.

В современных ЭВМ широко используется прямой

доступ к памяти (ПДП), что дает возможность использовать в МПС

быстродействующих внешних запоминающих устройств таких как накопители на магнитных дисках (НМД). ПДП обеспечивает высокую скорость обмена данными за счет, того, что управление обменом производится не программным путем, а электронными схемами. Такие электронные схемы, внешние по отношению к процессору, размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти.

При подключении контроллера ПДП возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Одним из путей решения этой проблемы является использование тех машинных циклов процессора, в которых он не обменивается данными с памятью и принудительным отключением процессора от шин системного интерфейса.

Для реализации такого режима работы ПДП системный интерфейс МПС дополняется двумя линиями для передачи управляющих сигналов "Требование прямого доступа к памяти" (HOLD) и "Предоставление прямого доступа к памяти" (HLDA).

Слайд 14Структура микропроцессора Intel 8085

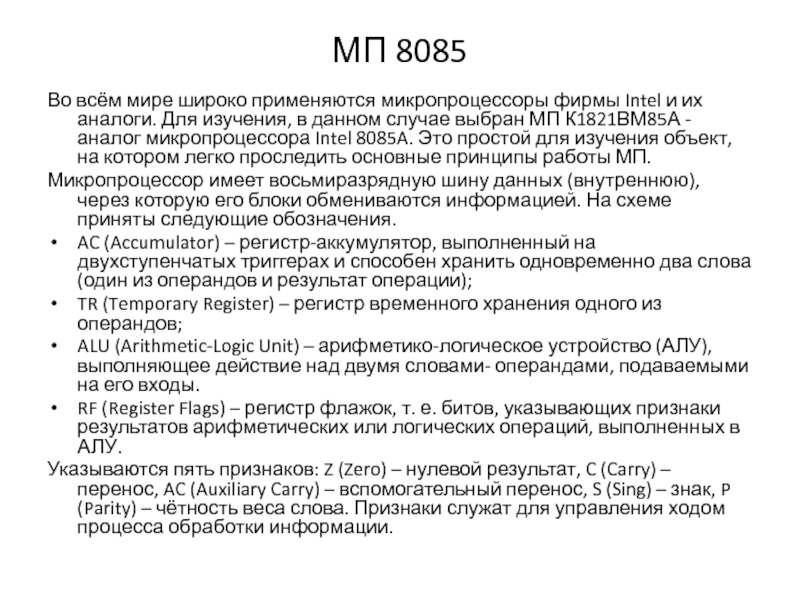

Слайд 15МП 8085

Во всём мире широко применяются микропроцессоры фирмы Intel и

их аналоги. Для изучения, в данном случае выбран МП К1821ВМ85А

- аналог микропроцессора Intel 8085A. Это простой для изучения объект, на котором легко проследить основные принципы работы МП.

Микропроцессор имеет восьмиразрядную шину данных (внутреннюю), через которую его блоки обмениваются информацией. На схеме приняты следующие обозначения.

AC (Accumulator) – регистр-аккумулятор, выполненный на двухступенчатых триггерах и способен хранить одновременно два слова (один из операндов и результат операции);

TR (Temporary Register) – регистр временного хранения одного из операндов;

ALU (Arithmetic-Logic Unit) – арифметико-логическое устройство (АЛУ), выполняющее действие над двумя словами- операндами, подаваемыми на его входы.

RF (Register Flags) – регистр флажок, т. е. битов, указывающих признаки результатов арифметических или логических операций, выполненных в АЛУ.

Указываются пять признаков: Z (Zero) – нулевой результат, C (Carry) – перенос, AC (Auxiliary Carry) – вспомогательный перенос, S (Sing) – знак, P (Parity) – чётность веса слова. Признаки служат для управления ходом процесса обработки информации.

Слайд 16Машинные циклы МП 8085

Микропроцессор К1821ВМ85А имеет следующие типы машинных циклов:

-

выборки команды (OF, Opcode Fetch).

- чтения из памяти (MR, Memory

Read).

- записи в память (MW, Memory Write).

- чтение из ВУ (IOR, Input-Output Read).

- записи в ВУ (IOW, Input-Output Write).

- подтверждение прерывания (INA, Interrupt Acknowledge).

- освобождения шин (BI, Bus Idle).

- останов (HALT).

В начале каждого машинного цикла генерируются сигналы состояния, идентифицирующие тип цикла и действующие в течение всего цикла

S1, S0 - сигналы состояния МП, сообщаемые внешней среде. Формируются в начале и сохраняются во время всего машинного цикла.

IO/M – сигнал выбора памяти или внешнего устройства. При высоком уровне происходит обращение к ВУ, при низком – к памяти.

Совместно с сигналами S1, S0 сигнал IO/M идентифицирует тип машинного цикла. Сигналы состояния и управляющие сигналы RD, WR и INTA для различных машинных циклов имеют значения,