Слайд 1Основные принципы планарной технологии

Слайд 2Планарная технология

Основным технологическим методом создания современных интегральных микросхем остается разработанная

в конце 50-х годов двадцатого столетия

планарная технология.

Практически все современные процессы создания широко используемых интегральных микросхем различного назначения основываются на технологических операциях планарной технологии.

1959

Год появления –

Слайд 3 Планарная технология

позволяет реализовать групповой процесс изготовления элементов интегральных схем

на полупроводниковой подложке

одновременно и

на одном кристалле

Слайд 4Планарный процесс

(от англ. planar, от лат. planus – плоский, ровный),

– совокупность технологических операций, проводимых для получения полупроводниковых приборов с

электронно-дырочными переходами, границы которых выходят на одну и ту же плоскую поверхность пластины полупроводника и находятся под слоем защитного диэлектрического покрытия.

совокупность технологических операций, проводимых для получения на пластинах практически любых полупроводниковых приборов и интегральных схем, в том числе и таких, у которых границы электронно-дырочных переходов не выходят на одну плоскую поверхность.

Слайд 5Основные операции планарной технологии

легирование полупроводника (диффузия примесей в полупроводник

и ионная имплантация)

окисление кремния

травление (жидкостное химическое травление –

ЖХТ и плазмохимическое травление – ПХТ

фотолитография

высокотемпературные обработки полупроводниковых структур (отжиги в различных средах)

осаждения тонких пленок различных материалов (слоев проводников и диэлектриков).

Слайд 6Легирование атомами примеси

Сущность процессов легирования полупроводника заключается в создании на

поверхности полупроводника источника примеси и проведении отжига, при котором примесь

проникает с поверхности в глубь материала за счет теплового движения атомов.

Слайд 7Окисление кремния

В результате процесса окисления происходит взаимодействие поверхностного слоя кремния

с кислородом и создание на поверхности полупроводника пленки оксида SiO2

или окисла.

Слайд 8Травление

Травление – это технологическая операция удаления обрабатываемого материала в процессе

химического взаимодействия и растворения в подходящем травителе. Локальное травление –

это удаление материала с определенной, заранее заданной части поверхности, соприкасающейся с травителем. Другие участки, на которые не должно распространяться действие травления, должны быть защищены инертными к действию травителя материалами.

Слайд 9Локальное травление и фотолитография

Дальнейшим развитием локального травления является

метод фотолитографии, использующий в качестве защитного слоя стойкое к действию

травителей вещество, меняющее свою растворимость под действием света (химически стойкое органическое полимерное соединение - фоторезист).

Слайд 10Технологический маршрут

Изготовление каждого полупроводникового прибора (соответственно, интегральной микросхемы) идет

по строго определенной последовательности. Такая последовательность называется технологическим маршрутом изготовления.

Основные технологические маршруты создания кремниевых ИС:

Биполярные

КМОП

БиКМОП

Слайд 11Сопроводительный лист

На предприятиях микроэлектроники данная последовательность отражена в маршрутной карте

(сопроводительном листе) соответствующей партии пластин, на которых будут изготовлены конкретные

полупроводниковые приборы. В сопроводительном листе отражаются режимы технологических операций и результаты контрольных измерений различных физических и электрических параметров получаемых слоёв и структур (после соответствующей операции)

Слайд 12Принципы планарной технологии

взаимосвязь конструкции интегральных микросхем и технологии их

изготовления

совместимость элементов (на одном кристалле)

локальность технологических обработок

послойное формирование элементов микросхем

Слайд 13Взаимосвязь конструкции интегральных микросхем и технологии их изготовления

Проектирование конструкции интегральной

микросхемы связано с технологией ее создания.

Необходимо учитывать влияние паразитных связей

между элементами.

Необходимость учёта технологического разброса при выборе значений параметров полупроводниковых приборов

Слайд 14Конструктивно-технологические ограничения при разработке и изготовлении интегральных микросхем

Наряду с конструктивными,

эксплутационными и электрическими параметрами для интегральных микросхем вводятся данные, отражающие

ограничения технологии. Они определяют оптимальную конструкцию.

Для производства микросхем понятия «проектирование» и «технология» тесно взаимосвязаны, при этом технологии принадлежит определяющая роль.

Слайд 15Совместимость элементов интегральных микросхем

Единый групповой метод изготовления.

Основной элемент – самый

сложный элемент ИС - транзистор.

На основе транзистора изготавливаются другие элементы

ИС.

Несовместимость элементов – не всегда «препятствие» для создания ИС, но значительное повышение себестоимости

Слайд 16Локальность технологических обработок

Во время технологических операций обрабатывается не вся

поверхность пластины.

Методы локальных технологий:

масочная технология: трафареты и

шаблоны (фотошаблоны);

безмасочные технологии (электронный луч, ионный луч, лазер) – по программе с ЭВМ.

Слайд 17Послойное формирование элементов микросхем

Локальные обработки различных участков пластины выполняют

многократно.

Фотолитографический цикл: 2 типа

Слайд 18

Послойное формирование элементов микросхем

Фотолитографический цикл: 1 тип

ЛЕГИРОВАНИЕ

Окисление

Фотолитография

Травление

через ФРМ

Удаление ФР

Легирование

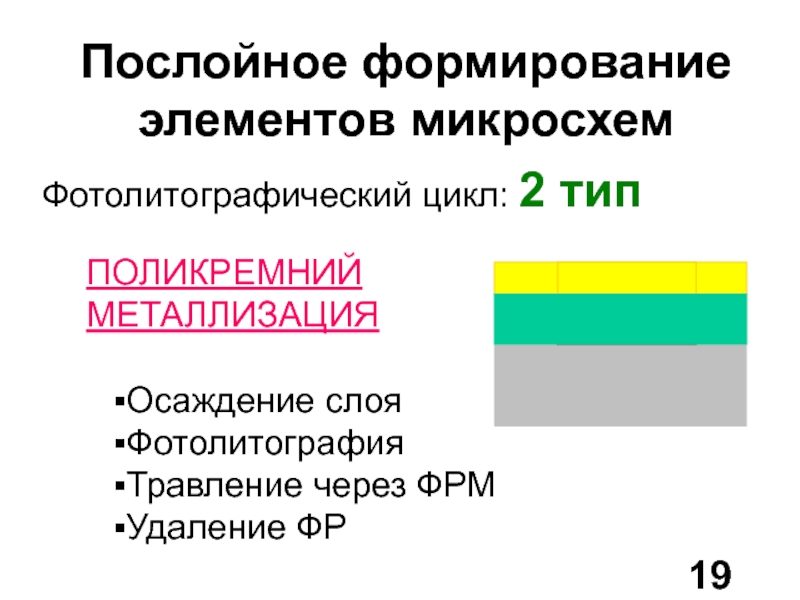

Слайд 19

Послойное формирование элементов микросхем

Фотолитографический цикл: 2 тип

ПОЛИКРЕМНИЙ МЕТАЛЛИЗАЦИЯ

Осаждение

слоя

Фотолитография

Травление через ФРМ

Удаление ФР

Слайд 20Технологический маршрут изготовления интегральных микросхем на основе биполярных изопланарных транзисторов

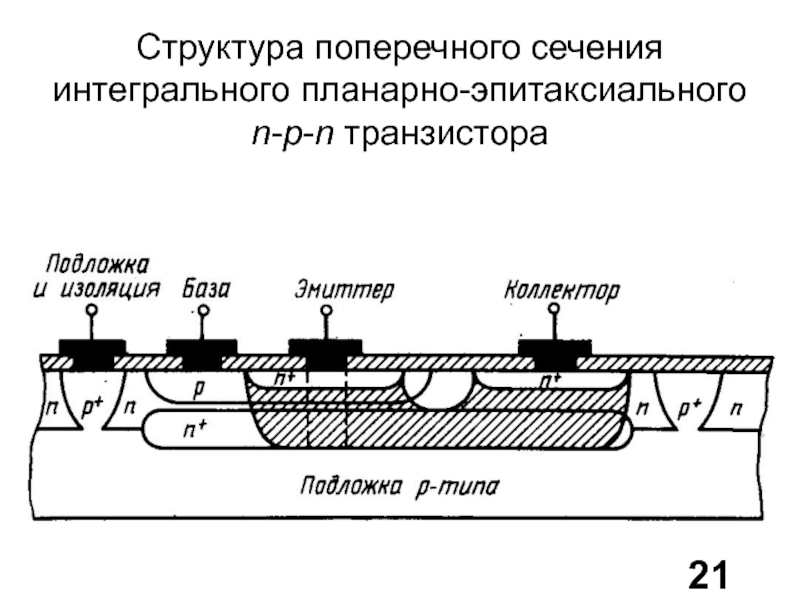

Слайд 21Структура поперечного сечения интегрального планарно-эпитаксиального

n-p-n транзистора

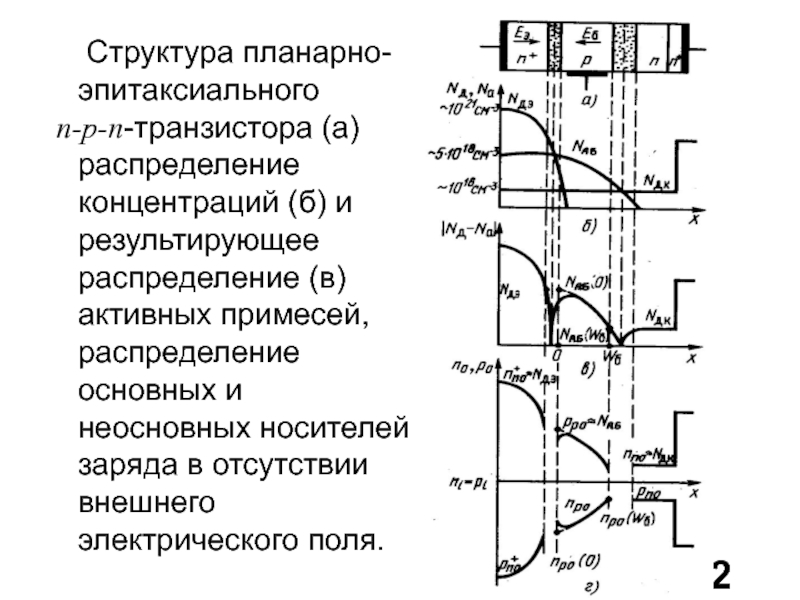

Слайд 22 Структура планарно-эпитаксиального

n-p-n-транзистора (а) распределение концентраций (б)

и результирующее распределение (в) активных примесей, распределение основных и неосновных

носителей заряда в отсутствии внешнего электрического поля.

Слайд 23 Для разделения приборов в составе кристалла используется

комбинированная изоляция:

диэлектрическая и

изоляция p-n-переходом.

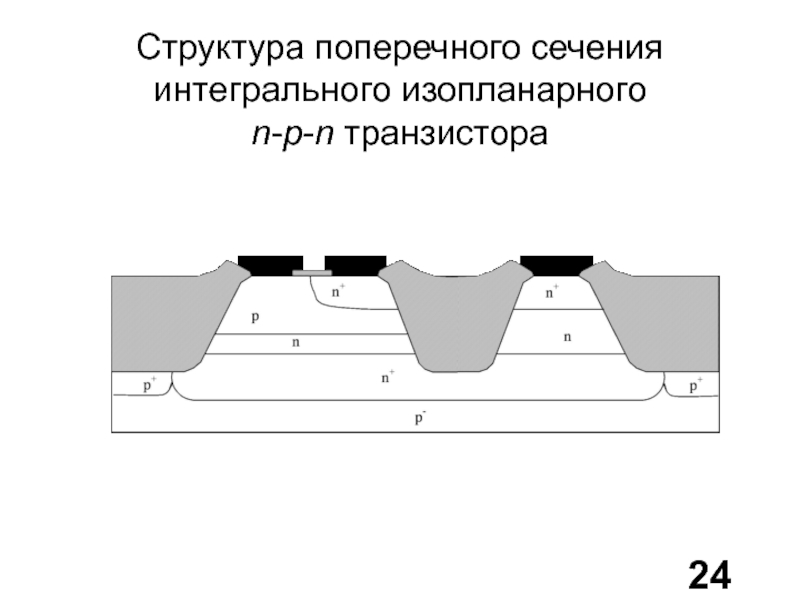

Слайд 24Структура поперечного сечения интегрального изопланарного

n-p-n транзистора

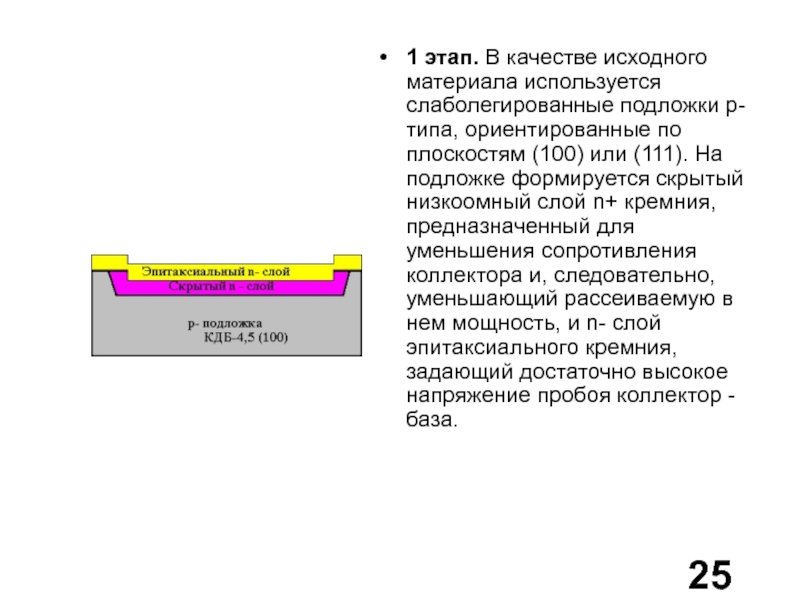

Слайд 251 этап. В качестве исходного материала используется слаболегированные подложки p-

типа, ориентированные по плоскостям (100) или (111). На подложке формируется

скрытый низкоомный слой n+ кремния, предназначенный для уменьшения сопротивления коллектора и, следовательно, уменьшающий рассеиваемую в нем мощность, и n- слой эпитаксиального кремния, задающий достаточно высокое напряжение пробоя коллектор - база.

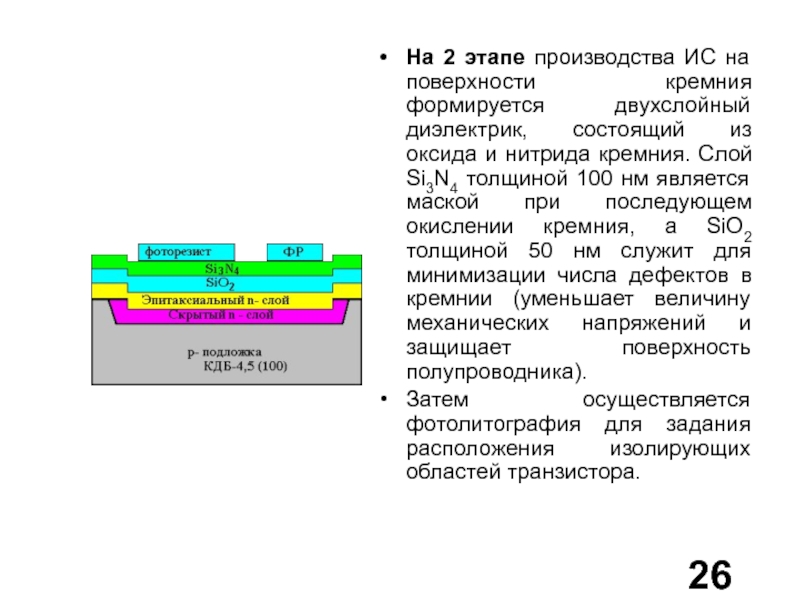

Слайд 26На 2 этапе производства ИС на поверхности кремния формируется двухслойный

диэлектрик, состоящий из оксида и нитрида кремния. Слой Si3N4 толщиной

100 нм является маской при последующем окислении кремния, а SiO2 толщиной 50 нм служит для минимизации числа дефектов в кремнии (уменьшает величину механических напряжений и защищает поверхность полупроводника).

Затем осуществляется фотолитография для задания расположения изолирующих областей транзистора.

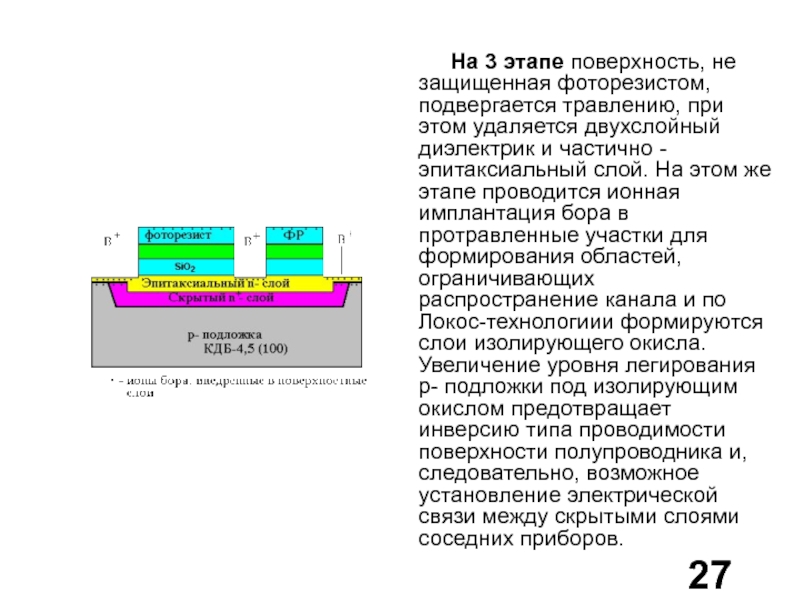

Слайд 27 На 3 этапе поверхность, не

защищенная фоторезистом, подвергается травлению, при этом удаляется двухслойный диэлектрик и

частично - эпитаксиальный слой. На этом же этапе проводится ионная имплантация бора в протравленные участки для формирования областей, ограничивающих распространение канала и по Локос-технологиии формируются слои изолирующего окисла. Увеличение уровня легирования p- подложки под изолирующим окислом предотвращает инверсию типа проводимости поверхности полупроводника и, следовательно, возможное установление электрической связи между скрытыми слоями соседних приборов.

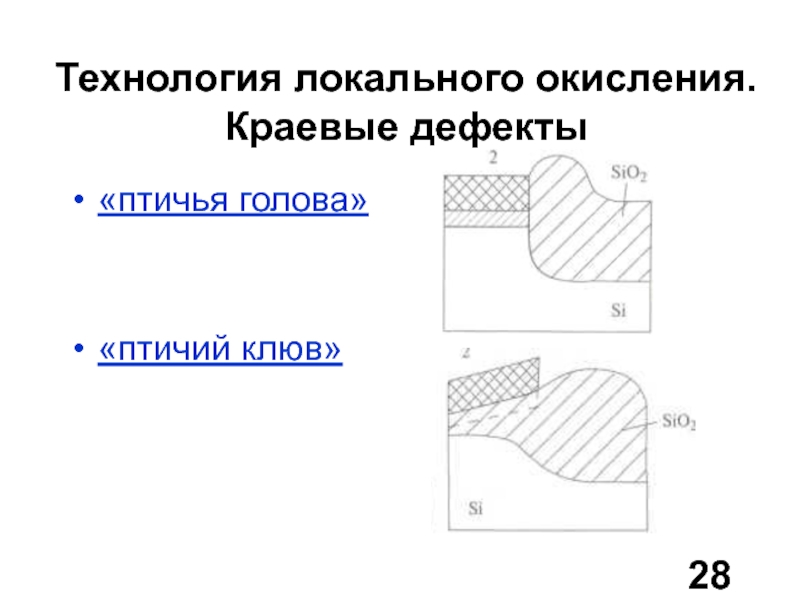

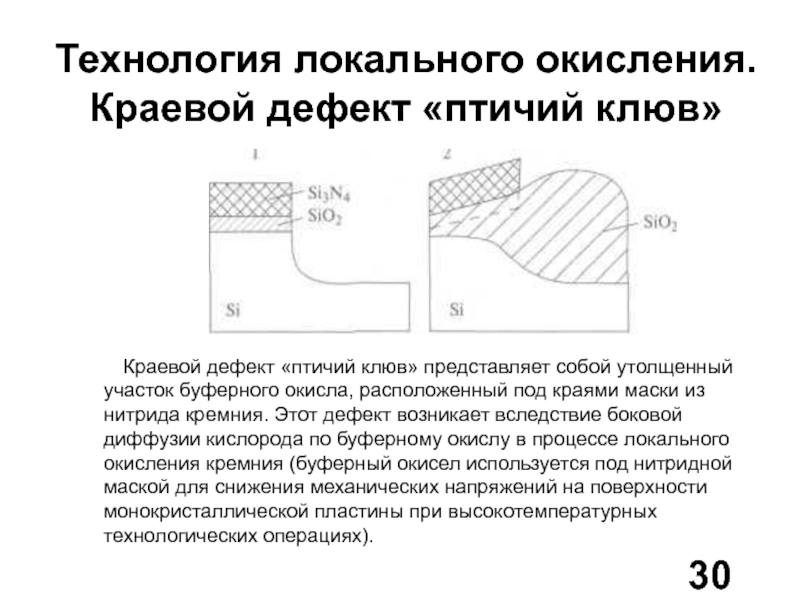

Слайд 28Технология локального окисления.

Краевые дефекты

«птичья голова»

«птичий клюв»

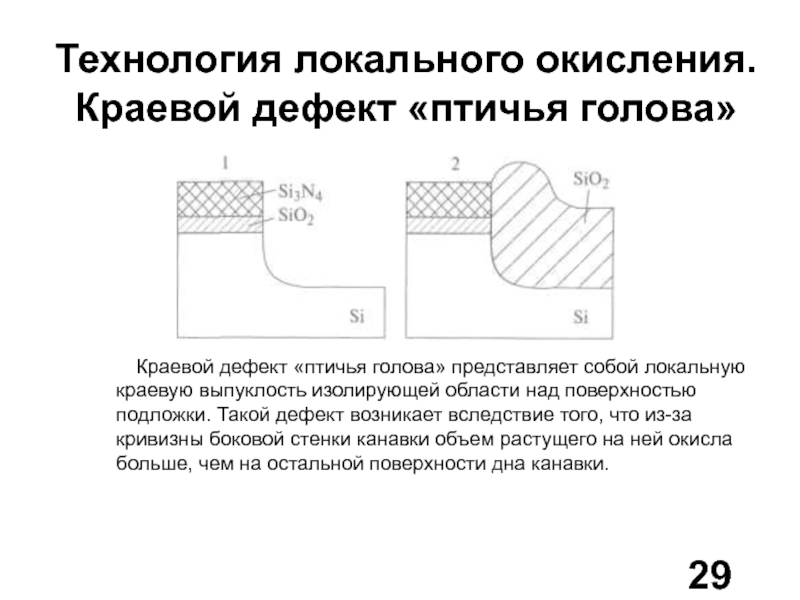

Слайд 29Технология локального окисления.

Краевой дефект «птичья голова»

Краевой дефект «птичья голова» представляет собой локальную краевую выпуклость

изолирующей области над поверхностью подложки. Такой дефект возникает вследствие того, что из-за кривизны боковой стенки канавки объем растущего на ней окисла больше, чем на остальной поверхности дна канавки.

Слайд 30Технология локального окисления.

Краевой дефект «птичий клюв»

Краевой дефект «птичий клюв» представляет собой утолщенный участок буферного

окисла, расположенный под краями маски из нитрида кремния. Этот дефект возникает вследствие боковой диффузии кислорода по буферному окислу в процессе локального окисления кремния (буферный окисел используется под нитридной маской для снижения механических напряжений на поверхности монокристаллической пластины при высокотемпературных технологических операциях).

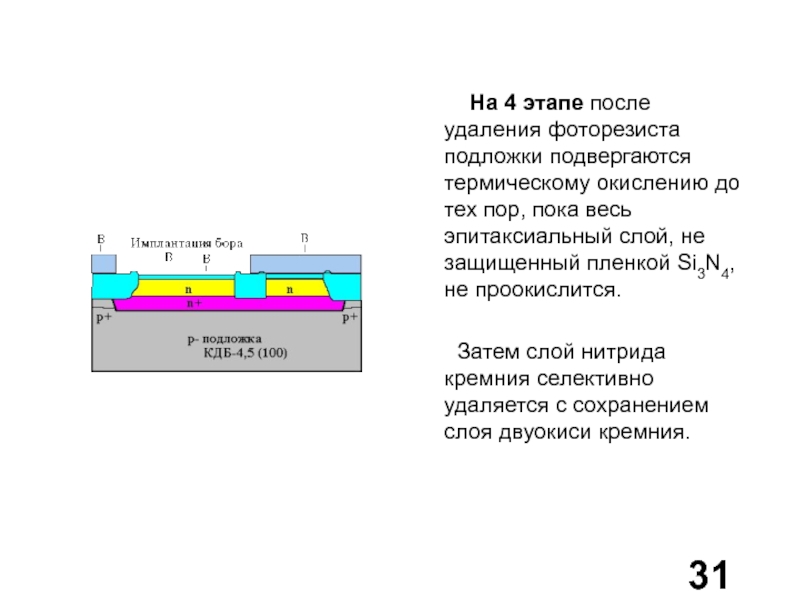

Слайд 31 На 4 этапе после удаления

фоторезиста подложки подвергаются термическому окислению до тех пор, пока весь

эпитаксиальный слой, не защищенный пленкой Si3N4, не проокислится.

Затем слой нитрида кремния селективно удаляется с сохранением слоя двуокиси кремния.

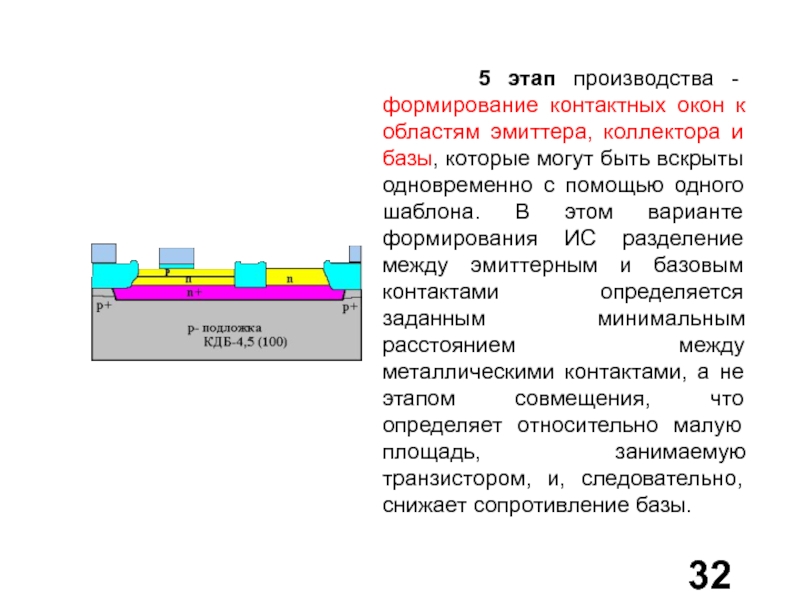

Слайд 32

5 этап производства - формирование

контактных окон к областям эмиттера, коллектора и базы, которые могут

быть вскрыты одновременно с помощью одного шаблона. В этом варианте формирования ИС разделение между эмиттерным и базовым контактами определяется заданным минимальным расстоянием между металлическими контактами, а не этапом совмещения, что определяет относительно малую площадь, занимаемую транзистором, и, следовательно, снижает сопротивление базы.

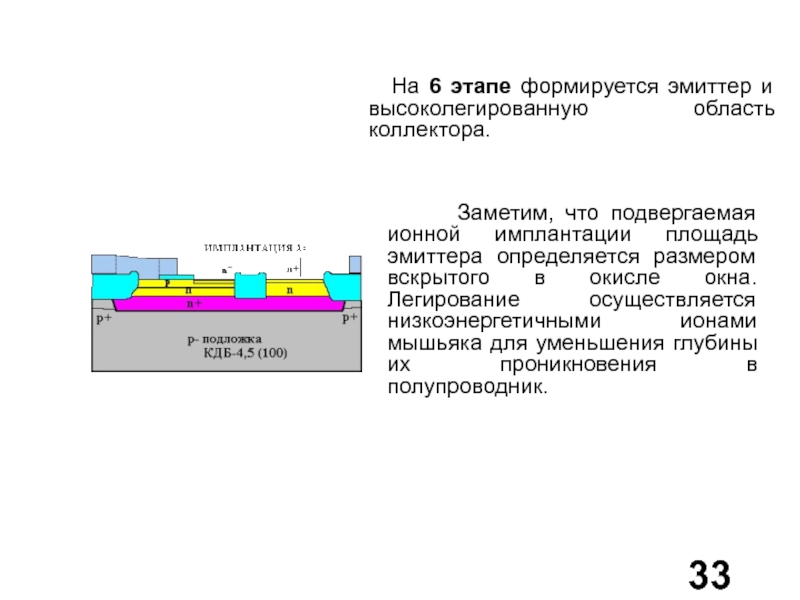

Слайд 33 На 6 этапе формируется эмиттер и высоколегированную

область коллектора.

Заметим, что подвергаемая

ионной имплантации площадь эмиттера определяется размером вскрытого в окисле окна. Легирование осуществляется низкоэнергетичными ионами мышьяка для уменьшения глубины их проникновения в полупроводник.

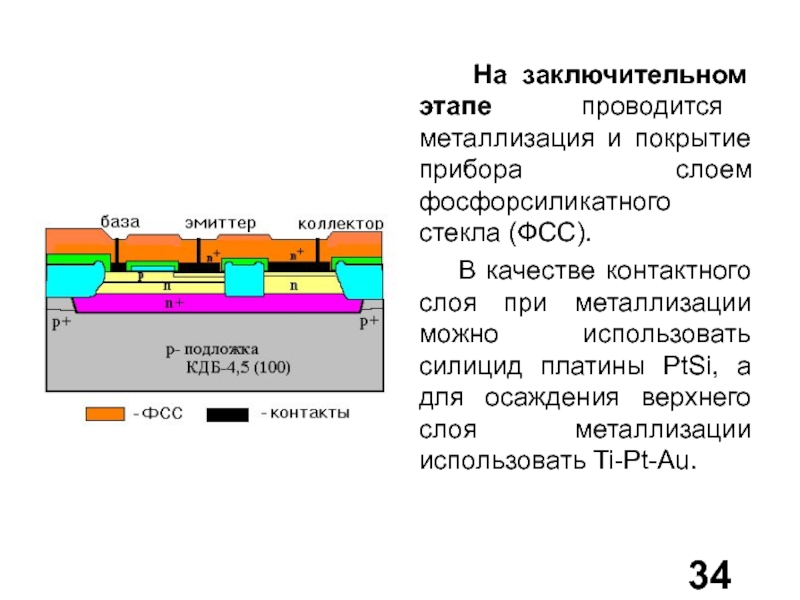

Слайд 34 На заключительном этапе проводится металлизация и покрытие

прибора слоем фосфорсиликатного стекла (ФСС).

В

качестве контактного слоя при металлизации можно использовать силицид платины PtSi, а для осаждения верхнего слоя металлизации использовать Ti-Pt-Au.

Слайд 35Технология МОП интегральных микросхем

Слайд 36Преимущества МОП ИС над биполярными ИС

малые размеры и площадь

упрощенная изоляция

низкая

потребляемая и рассеиваемая мощность

устойчивость к перегрузкам

высокое входное сопротивление

помехоустойчивость

низкая себестоимость производства

Слайд 37 Первый транзистор, работающий на эффекте поля, был

продемонстрирован в 1960 году. Сначала полевые транзисторы с двуокисью кремния

в качестве подзатворного диэлектрика формировались на подложке n- типа проводимости. Затем из-за большей подвижности электронов, чем у дырок при формировании сверхбольших быстродействующих интегральных схем стали использовать n- канальные транзисторы, формируемые на p- подложке.

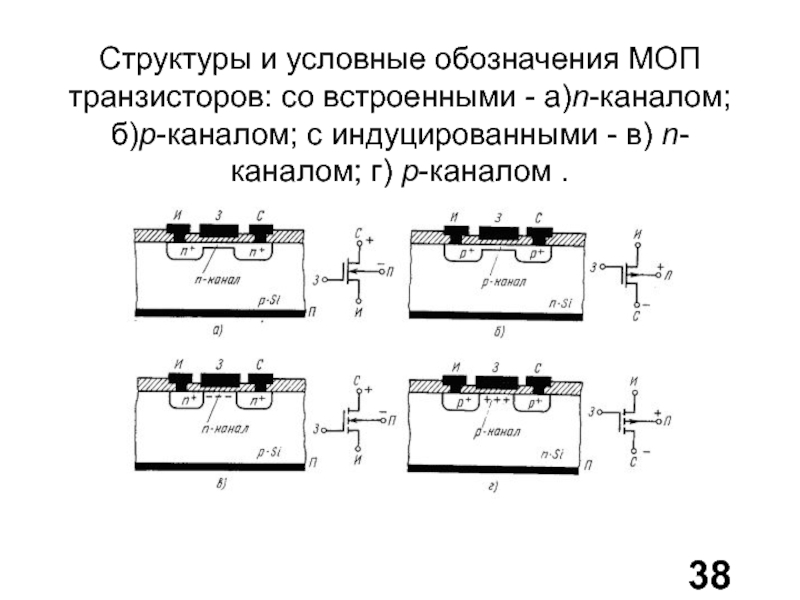

Слайд 38Структуры и условные обозначения МОП транзисторов: со встроенными - а)n-каналом;

б)p-каналом; с индуцированными - в) n-каналом; г) p-каналом .

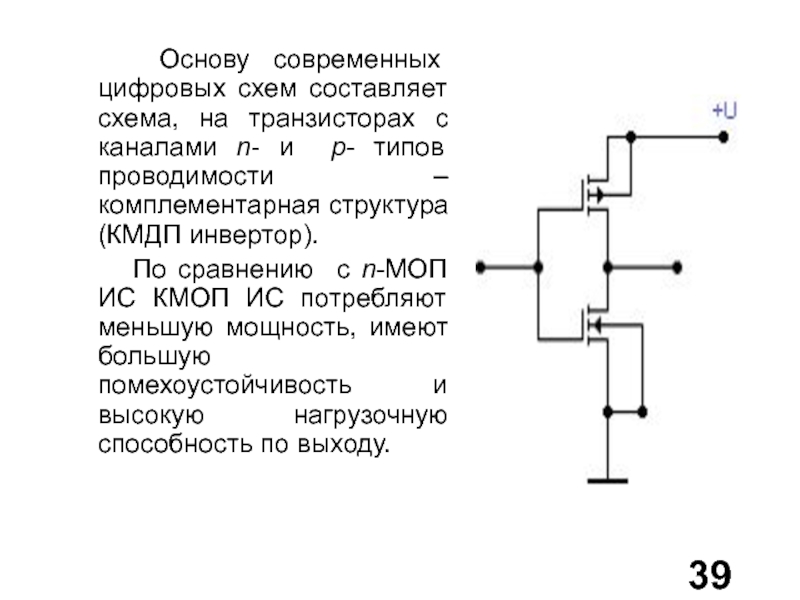

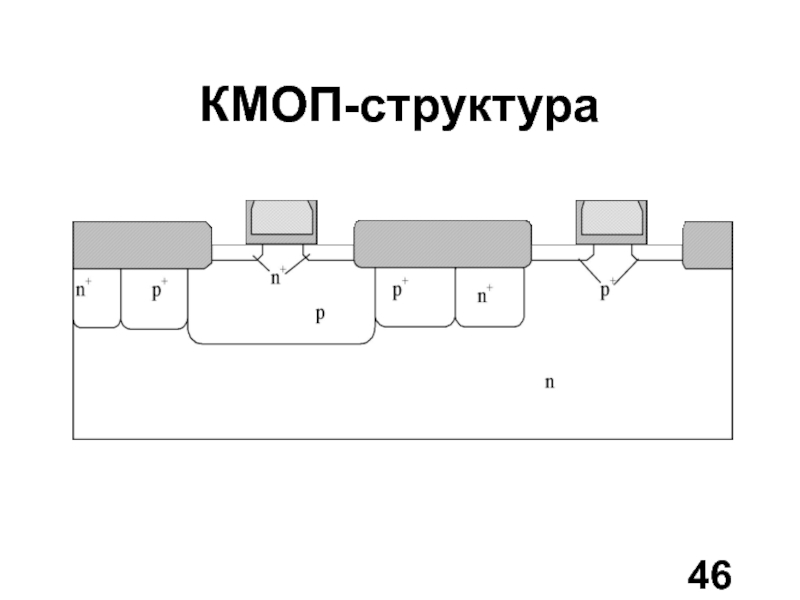

Слайд 39 Основу современных цифровых схем составляет схема, на

транзисторах с каналами n- и p- типов проводимости – комплементарная

структура (КМДП инвертор).

По сравнению с n-МОП ИС КМОП ИС потребляют меньшую мощность, имеют большую помехоустойчивость и высокую нагрузочную способность по выходу.

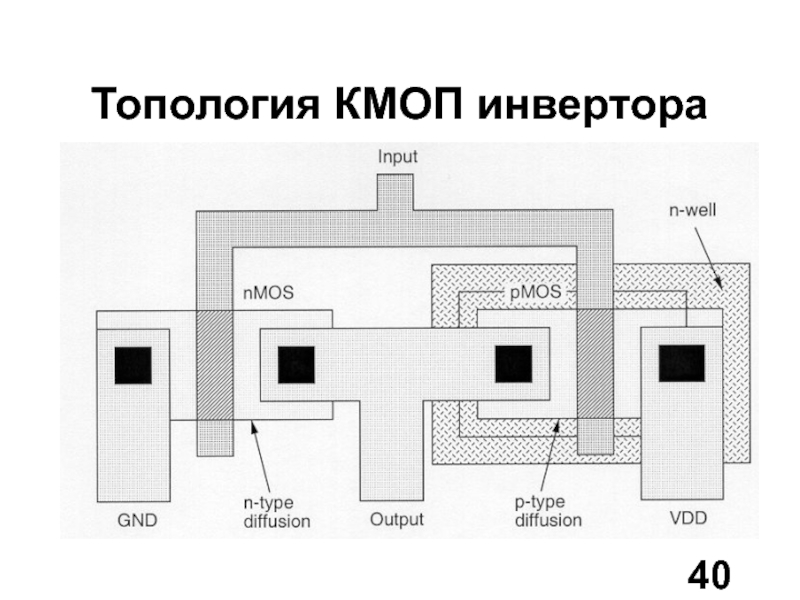

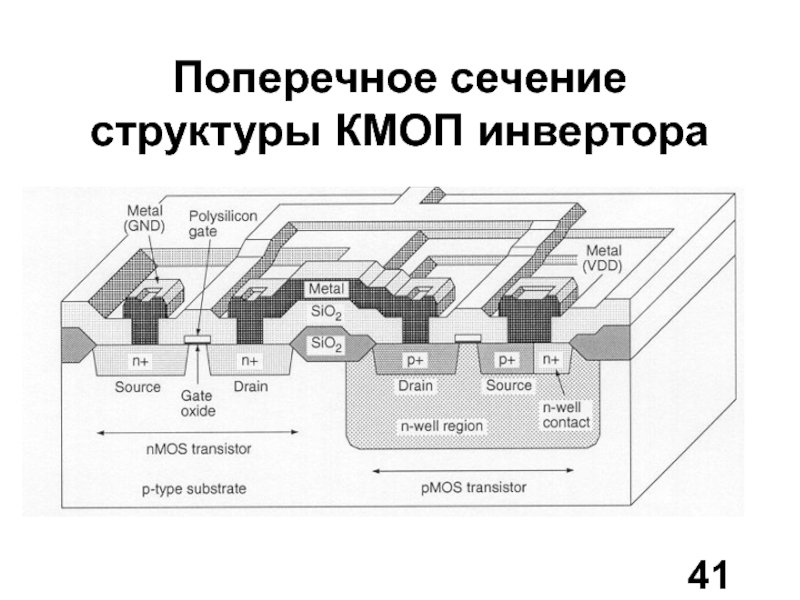

Слайд 41Поперечное сечение структуры КМОП инвертора

Слайд 42Технологический маршрут изготовления КМОП интегральных микросхем

с p-карманом

Слайд 43 ИС на транзисторах со структурой металл-диэлектрик-полупроводник

(МДП) получили широкое распространение.

В качестве

диэлектрика в настоящее время используют диоксид кремния SiO2

(МОП-структуры).

Также в качестве тонкого диэлектрика применяют пленку оксинитрида кремния SiNO.

Слайд 44 Выбор подложки

для КМОП технологии

В качестве подложки выбирают кремний p- типа проводимости легированный бором

КДБ (100) с концентрацией примеси 1015 - 1016 см-3.

Ориентация кремниевой подложки (100) имеет преимущество по сравнению с (111), заключающееся в более высокой подвижности электронов, обусловленной низкой плотностью поверхностных состояний на границе кремний-диэлектрик.

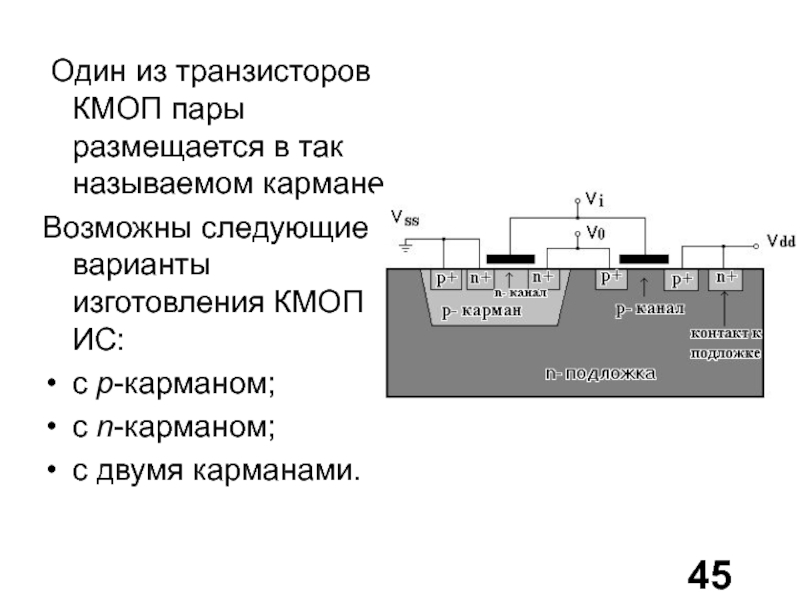

Слайд 45 Один из транзисторов КМОП пары размещается в так называемом

кармане.

Возможны следующие варианты изготовления КМОП ИС:

с p-карманом;

с n-карманом;

с двумя

карманами.

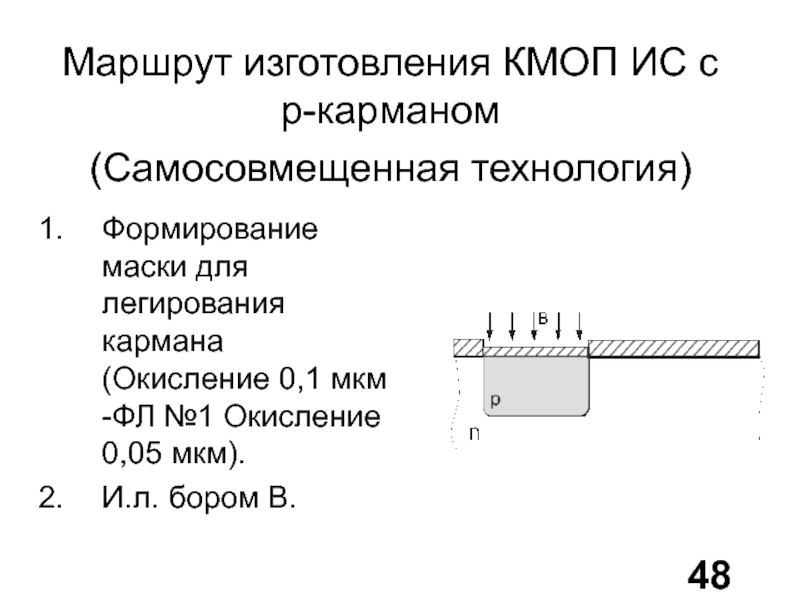

Слайд 48Маршрут изготовления КМОП ИС с p-карманом

(Самосовмещенная технология)

Формирование маски

для легирования кармана (Окисление 0,1 мкм -ФЛ №1 Окисление 0,05

мкм).

И.л. бором B.

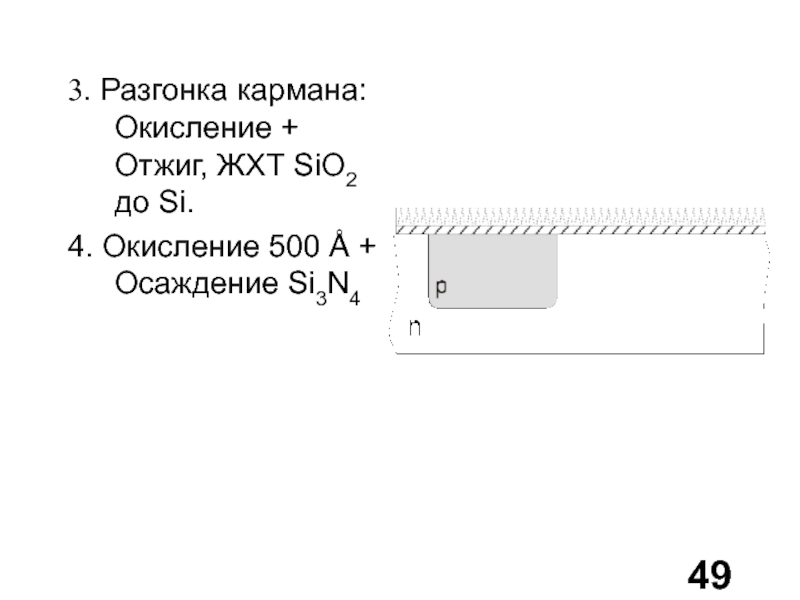

Слайд 493. Разгонка кармана: Окисление + Отжиг, ЖХТ SiO2 до Si.

4.

Окисление 500 Å + Осаждение Si3N4

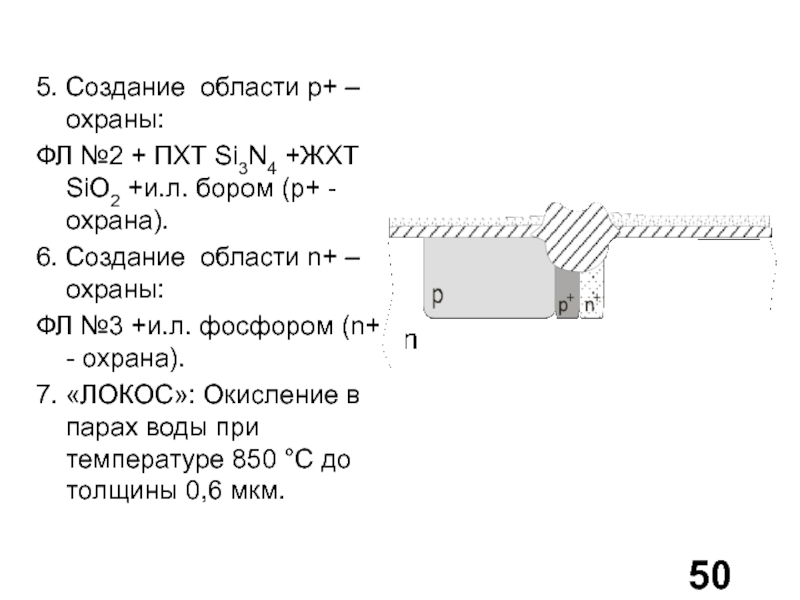

Слайд 505. Создание области р+ – охраны:

ФЛ №2 + ПХТ Si3N4

+ЖХТ SiO2 +и.л. бором (р+ - охрана).

6. Создание области n+

– охраны:

ФЛ №3 +и.л. фосфором (n+ - охрана).

7. «ЛОКОС»: Окисление в парах воды при температуре 850 °С до толщины 0,6 мкм.

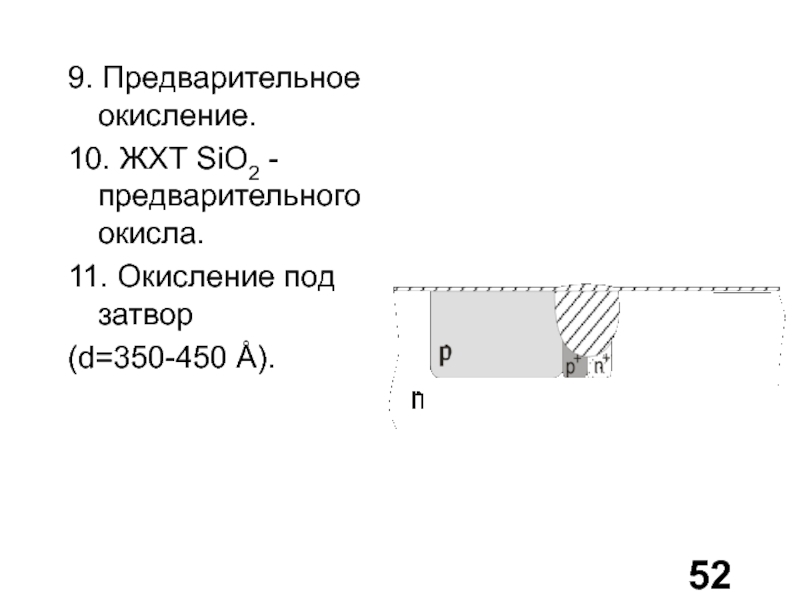

Слайд 529. Предварительное окисление.

10. ЖХТ SiO2 - предварительного окисла.

11. Окисление под

затвор

(d=350-450 Å).

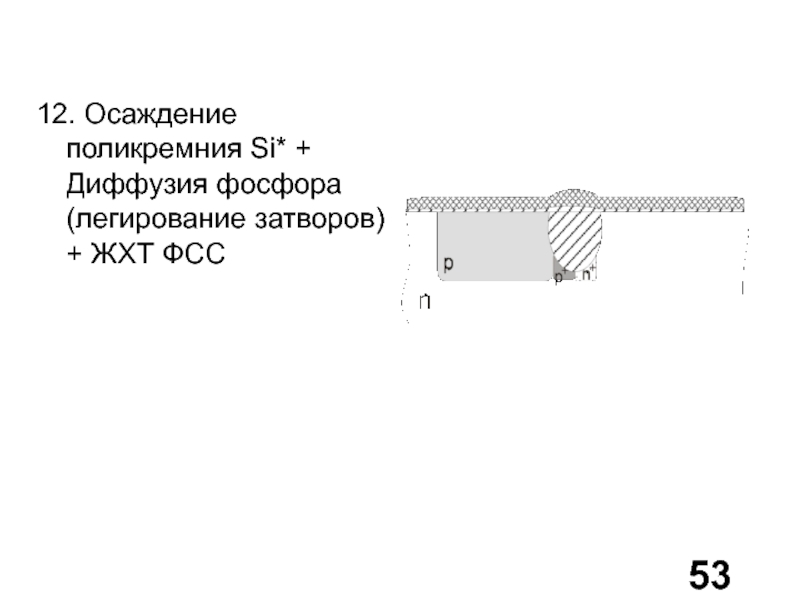

Слайд 5312. Осаждение поликремния Si* + Диффузия фосфора (легирование затворов) +

ЖХТ ФСС

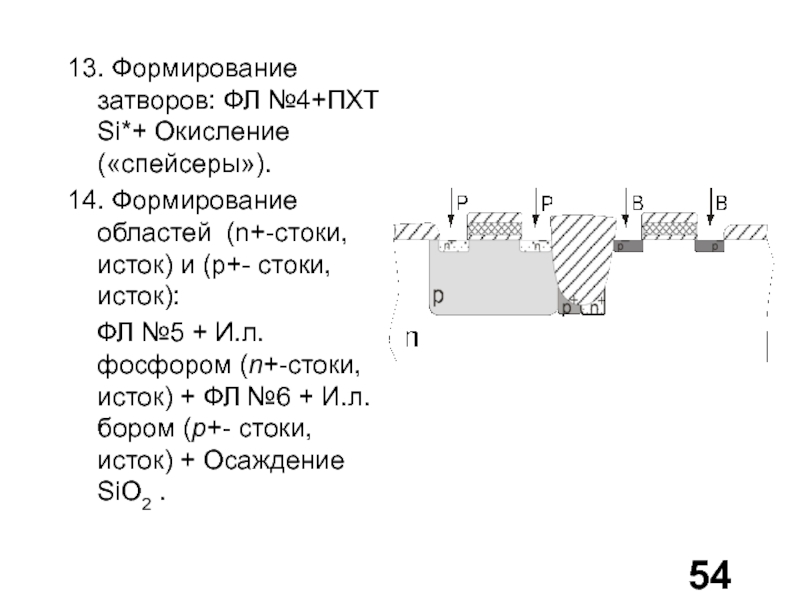

Слайд 5413. Формирование затворов: ФЛ №4+ПХТ Si*+ Окисление («спейсеры»).

14. Формирование

областей (n+-стоки, исток) и (p+- стоки, исток):

ФЛ №5

+ И.л. фосфором (n+-стоки, исток) + ФЛ №6 + И.л. бором (p+- стоки, исток) + Осаждение SiO2 .

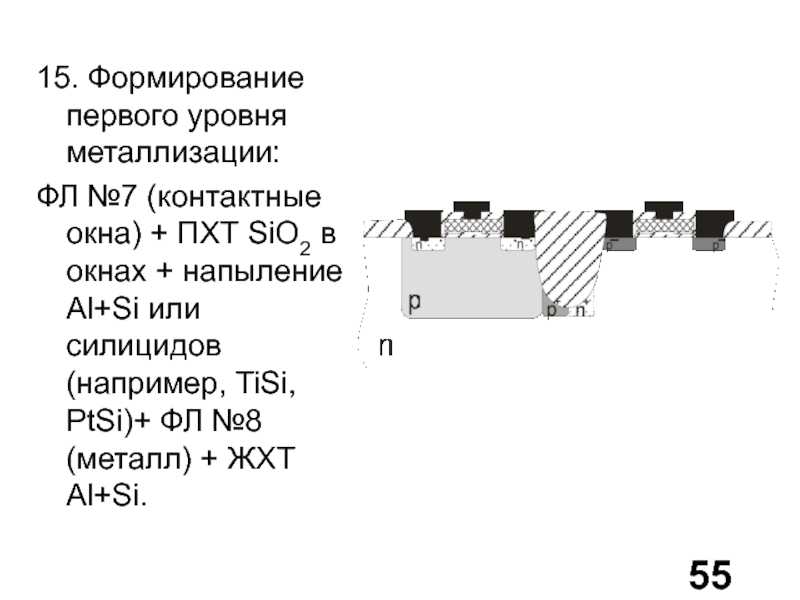

Слайд 5515. Формирование первого уровня металлизации:

ФЛ №7 (контактные окна) + ПХТ

SiO2 в окнах + напыление Al+Si или силицидов (например, TiSi,

PtSi)+ ФЛ №8 (металл) + ЖХТ Al+Si.

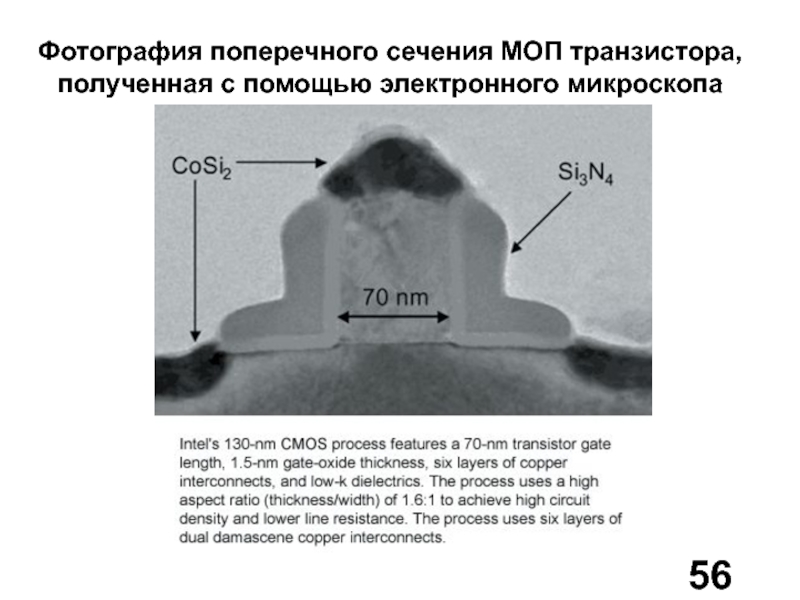

Слайд 56Фотография поперечного сечения МОП транзистора, полученная с помощью электронного микроскопа

Слайд 57Список использованных и рекомендуемых источников

Технология, конструкции и методы моделирования кремниевых

интегральных микросхем: в 2 ч. / Королев М.А., Крупкина Т.Ю.,

Ревелева М.А., под общей ред. Чаплыгина Ю.А. – М.: БИНОМ. Лаборатория знаний. – 2007. Ч. 1: Технологические процессы изготовления кремниевых интегральных схем и их моделирование. – 397 с.

Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч. / Королев М.А., Крупкина Т.Ю., Путря М.Г., Шевяков В.И., под общей ред. члена-корр. РАН профессора Чаплыгина Ю.А. – М.: БИНОМ. Лаборатория знаний. – 2009. Ч. 2: Элементы и маршруты изготовления кремниевых ИС и методы их математического моделирования. – 422 с.

Коледов Л.А. Технология и конструкции микросхем, микропрорцессоров и микросборок: Учебник для вузов / М.: Радио и связь, 1989. – 400 с.

Технология СБИС: В 2-х кн. Кн. 2 / Пер. с англ. Под ред. Зи С. – М.: Мир, 1986. – 453 с.

Малышева И.А. Технология производства интегральных микросхем: Учебник для техникумов / М.: Радио и связь, 1991. – 344 с.

Программа для дистанционного обучения по курсу «Технология СБИС» / http://sbis.karelia.ru/ [Электронный ресурс]. – 2009.

Киреев В.Ю. «Введение в технологии микроэлектроники и нанотехнологии». ГНЦ РФ «ЦНИИХМ», 2008 г.