n-разрядных двоичных чисел и выполнения преобразований над ними.

Элементарной ячейкой

электронной памяти является триггер, способный сохранять 1 бит записанной в нем информации. Каждый разряд двоичного числа записывается в своем триггере, поэтому число триггеров в регистре определяет разрядность записываемого числа.Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове.

Регистр предназначен для записи, хранения и выдачи информации.

С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое достаточно сложное цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых схем.

Регистры классифицируются по следующим видам:

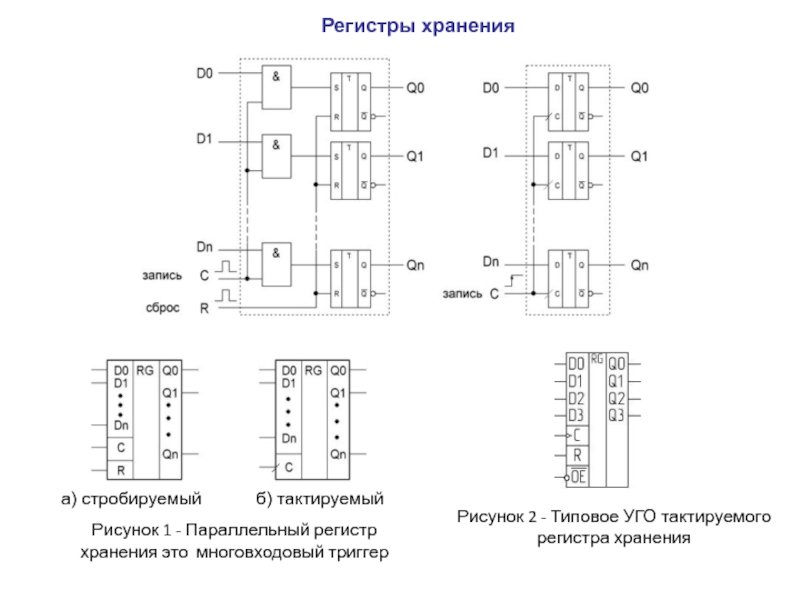

1. Регистры хранения (параллельные или накопительные);

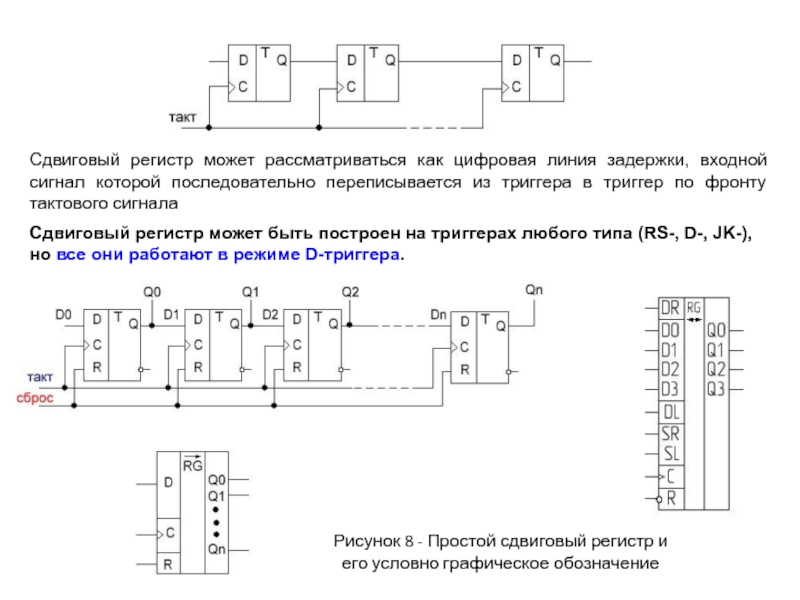

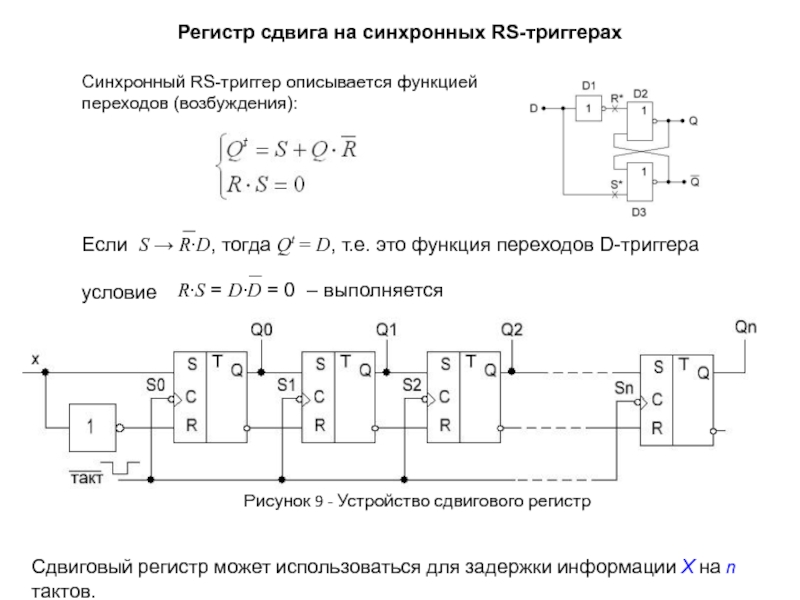

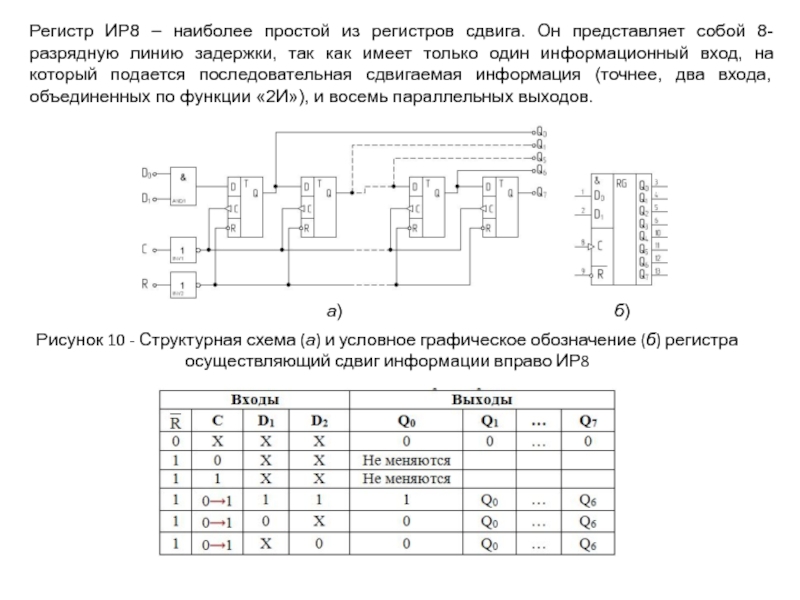

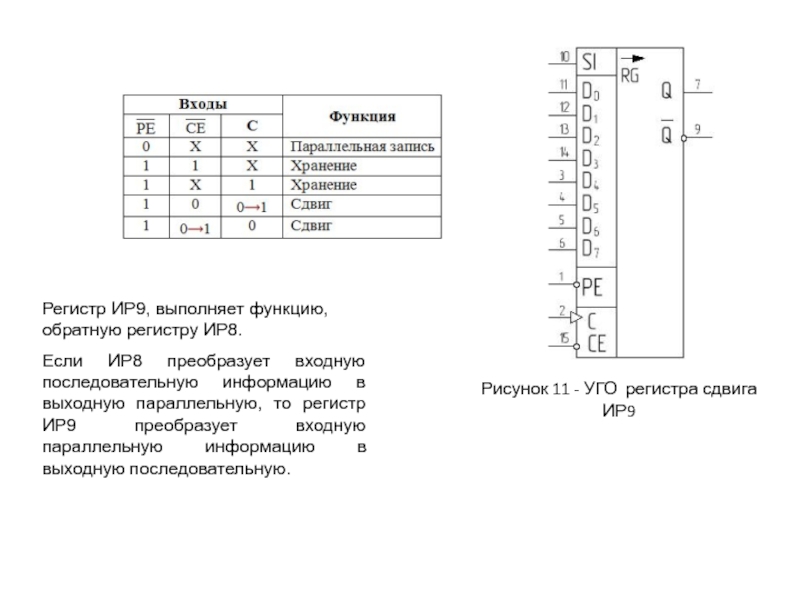

2. Регистры сдвига (последовательные).