Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

SCH-T-3.ppt

Содержание

- 1. SCH-T-3.ppt

- 2. ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИБАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ n-МОПЭЛЕКТРОННЫЙ КЛЮЧ

- 3. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ n-МОП В последнее время

- 4. В большинстве схем подложка электрически соединяется с

- 5. Металлический затвор изолирован от канала тонкой изоляционной

- 6. При увеличении входного напряжения выше U' сопротив-ление

- 7. Точка пересечения передаточной характеристики с биссектрисой первого

- 8. Электронный ключ КМОП Значительно лучшими параметрами обладают

- 9. Передаточная характеристика КМОП ключа При нулевом входном

- 10. При увеличении входного напряжения выше U' (точка

- 11. Таким образом, при входном напряжении ниже U'

- 12. Переходные процессы в КМОП ключах определяются временем

- 13. У элемента Шеффера транзисторы VT1, VT2 с

- 14. Если на одном из входов присутствует низкий

- 15. Любые более сложные логические схемы могут быть

- 16. Если на управляющий вход «#» подано напряжение

- 17. СХЕМОТЕХНИКА ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ ЛОГИЧЕСКИЕ КОМБИНАЦИОННЫЕ СХЕМЫ

- 18. Алгоритм преобразования ЛКС может быть задан тремя

- 19. Мажоритарный элемент может быть реализован на элементах

- 20. Схема МАЖОРИТАРНОГО ЭЛЕМЕНТАY3&&&&1ABCABC Однако, прежде чем создавать принципиальную

- 21. В частности, можно, используя алгебраические преобразования исходного

- 22. Операциям склеивания соответствуют на карте Карно объединения

- 23. Минимизированная функция для мажоритарного элемента имеет вид: Принципиальная

- 24. СУММАТОРЫ СУММАТОР – это ЛКС, формирующая сигналы

- 25. Логический элемент "И-ИЛИ-НЕ" имеется в наборе любой

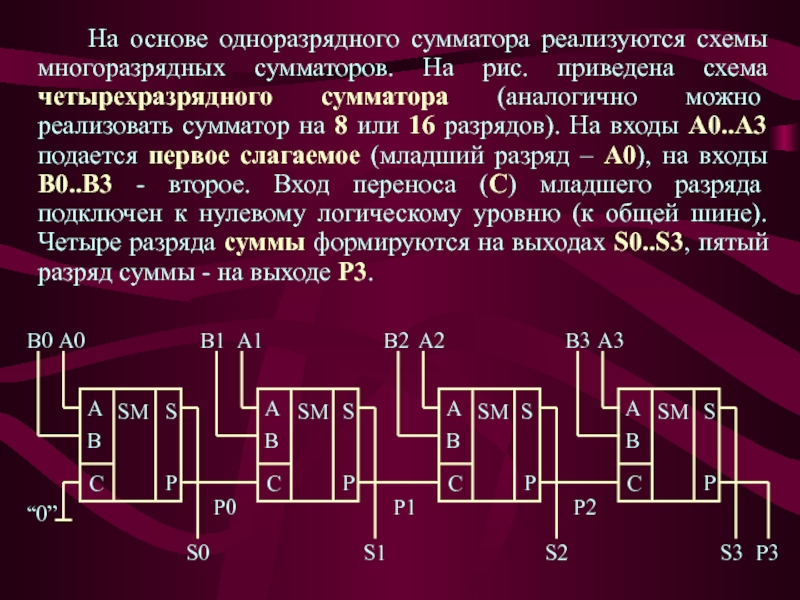

- 26. На основе одноразрядного сумматора реализуются схемы многоразрядных

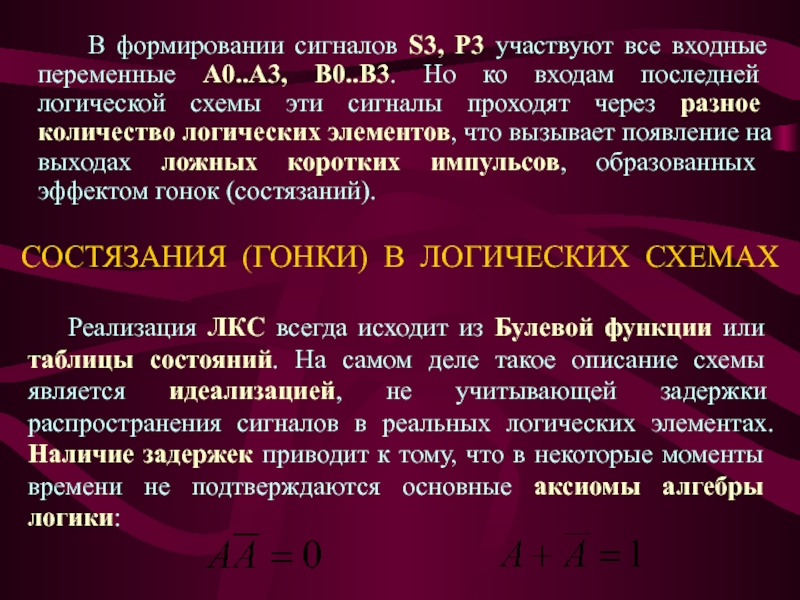

- 27. В формировании сигналов S3, P3 участвуют все

- 28. Наличие задержки распространения сигнала в инверторе приводит

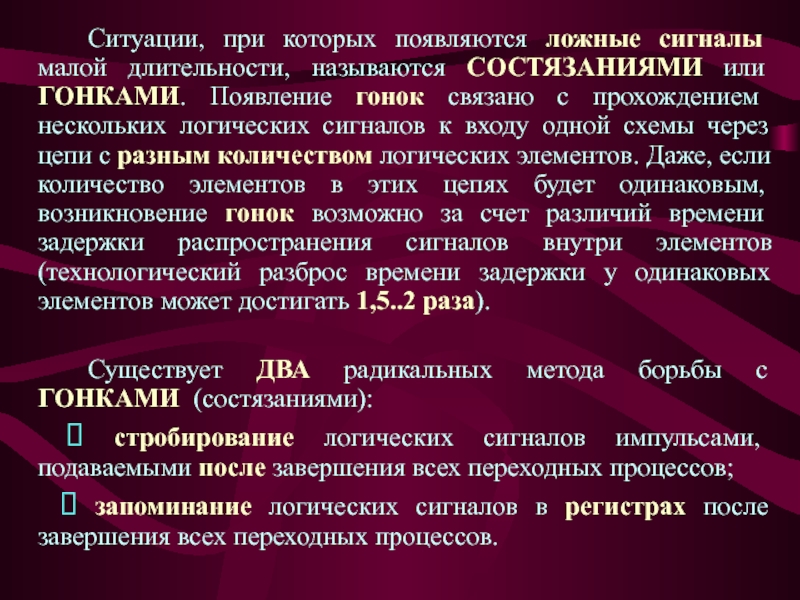

- 29. Ситуации, при которых появляются ложные сигналы малой

- 30. ПРЕОБРАЗОВАТЕЛИ КОДОВ, ДЕШИФРАТОРЫ ПРЕОБРАЗОВАТЕЛИ КОДОВ предназначены для

- 31. Преобразователи двоичного кода в код «1 из

- 32. X0X1X2Y0Y1Y2…………………………………………………………………………………………………………X2Y7

- 33. Дешифратор «1 из 8» может быть реализован

- 34. Дополнительные входы разрешения могут быть использованы для

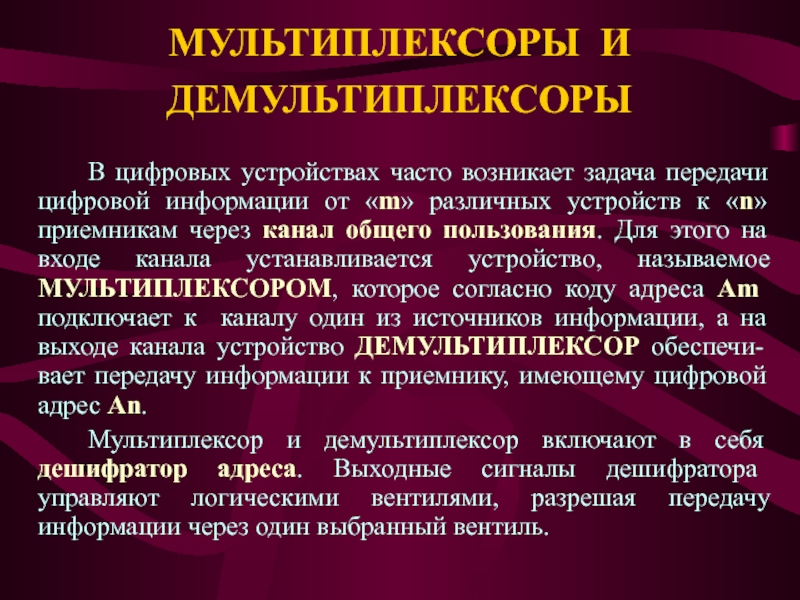

- 35. МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ В цифровых устройствах часто

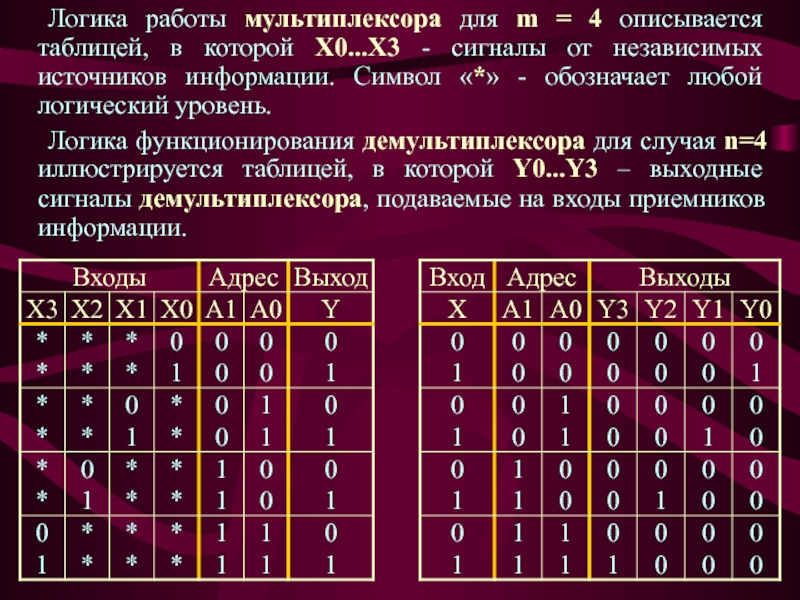

- 36. Логика работы мультиплексора для m = 4

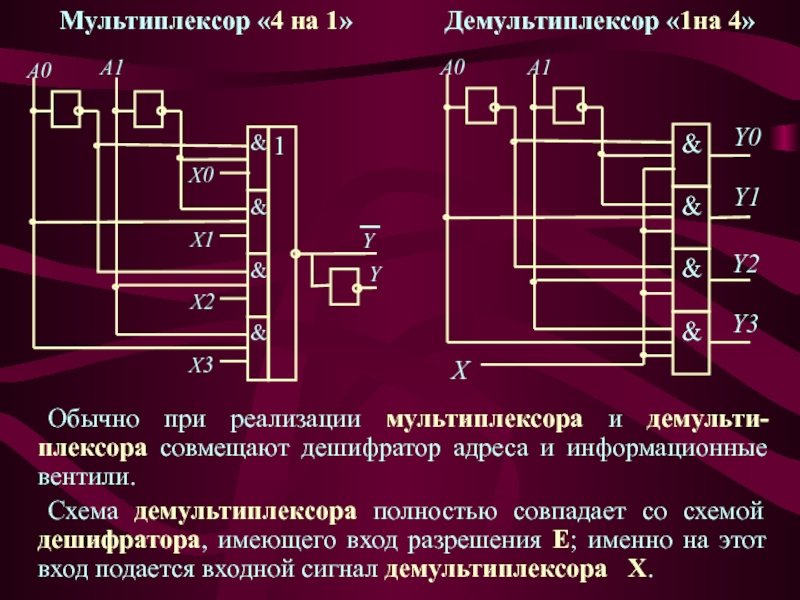

- 37. Обычно при реализации мультиплексора и демульти-плексора совмещают

- 38. Вопросы для экспресс-контроля1. Назовите методы описания (задания) логических

- 39. Вопросы для экспресс-контроля7. Зачем дешифраторам необходим вход ОЕ – разрешение выхода?8. Назначение мультиплексоров и демульти-плексоров.

- 40. ЛЕКЦИЯ ОКОНЧЕНАСПАСИБО ЗА ВНИМАНИЕ

- 41. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ

БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ n-МОП

ЭЛЕКТРОННЫЙ КЛЮЧ КМОП

ЛОГИЧЕСКИЕ КОМБИНАЦИОННЫЕ СХЕМЫ

СУММАТОРЫ

СОСТЯЗАНИЯ

(ГОНКИ) В ЛОГИЧЕСКИХ СХЕМАХ

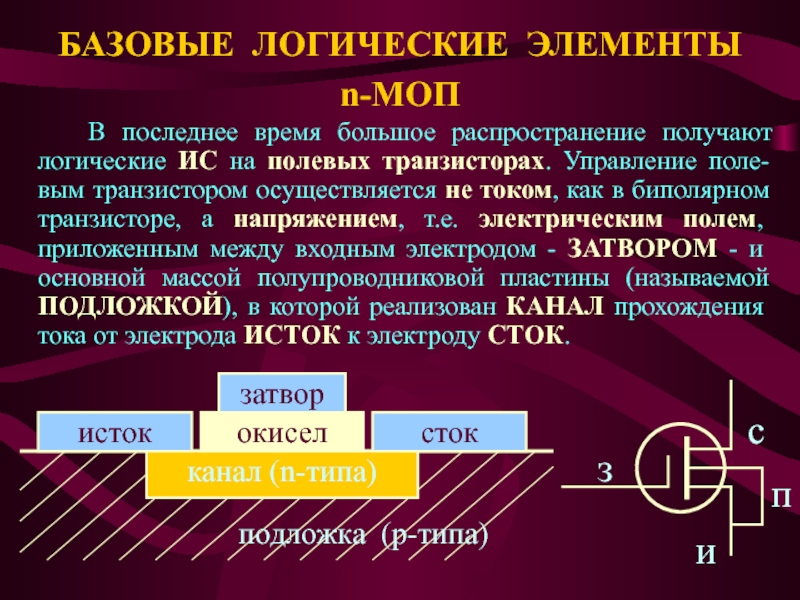

Слайд 3БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ n-МОП

В последнее время большое распространение получают

логические ИС на полевых транзисторах. Управление поле-вым транзистором осуществляется не

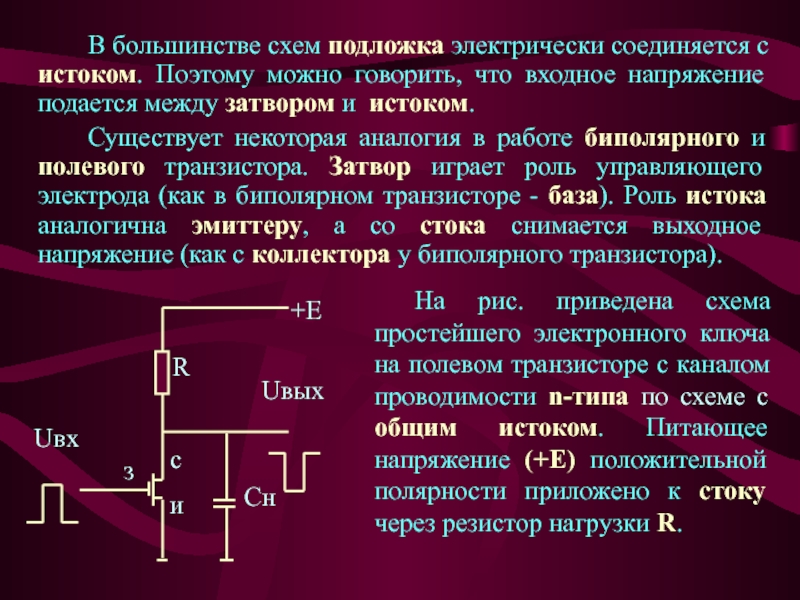

током, как в биполярном транзисторе, а напряжением, т.е. электрическим полем, приложенным между входным электродом - ЗАТВОРОМ - и основной массой полупроводниковой пластины (называемой ПОДЛОЖКОЙ), в которой реализован КАНАЛ прохождения тока от электрода ИСТОК к электроду СТОК.Слайд 4 В большинстве схем подложка электрически соединяется с истоком. Поэтому можно

говорить, что входное напряжение подается между затвором и истоком.

Существует

некоторая аналогия в работе биполярного и полевого транзистора. Затвор играет роль управляющего электрода (как в биполярном транзисторе - база). Роль истока аналогична эмиттеру, а со стока снимается выходное напряжение (как с коллектора у биполярного транзистора). На рис. приведена схема простейшего электронного ключа на полевом транзисторе с каналом проводимости n-типа по схеме с общим истоком. Питающее напряжение (+Е) положительной полярности приложено к стоку через резистор нагрузки R.

+Е

Uвых

Uвх

R

з

с

и

Сн

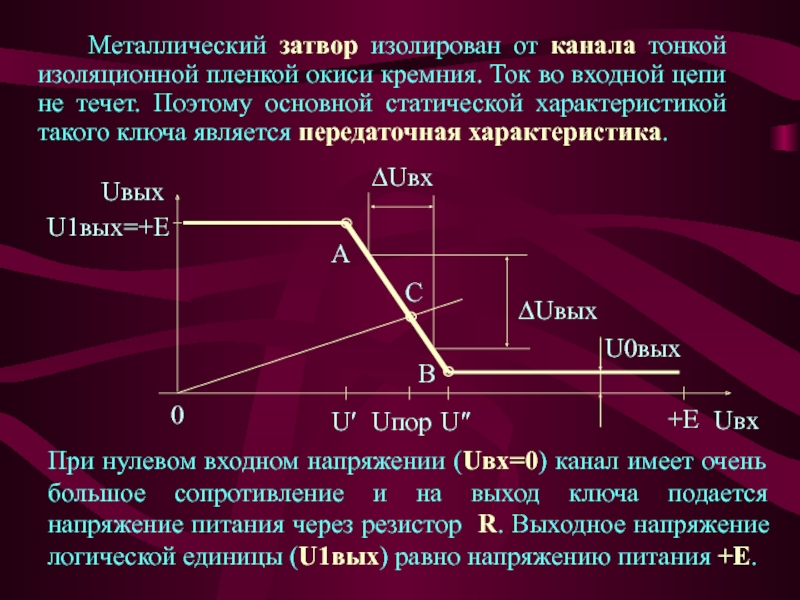

Слайд 5 Металлический затвор изолирован от канала тонкой изоляционной пленкой окиси кремния.

Ток во входной цепи не течет. Поэтому основной статической характеристикой

такого ключа является передаточная характеристика.При нулевом входном напряжении (Uвх=0) канал имеет очень большое сопротивление и на выход ключа подается напряжение питания через резистор R. Выходное напряжение логической единицы (U1вых) равно напряжению питания +Е.

Слайд 6 При увеличении входного напряжения выше U' сопротив-ление канала постепенно уменьшается

и на выход подается часть напряжения источника питания с делителя,

образован-ного сопротивлением канала и резистором R (участок А-В). Сопротивление канала не может уменьшиться до нуля. При входном напряжении выше U" сопротивление канала достигает минимальной величины, и дальнейшее увеличение входного напряжения не влияет на сопротивление канала.Величины U', U" и Rкмин определяются технологиче-скими параметрами: степенью легирования канала, степенью шероховатости поверхности канала, геометрическими размерами канала; а также напряжением питания электрон-ного ключа.

На участке А-В, т.е. при входном напряжении от U' до U" электронный ключ работает как аналоговый усилитель с коэффициентом усиления

Ku=∆Uвых/∆Uвх.

Слайд 7 Точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С)

определяет пороговое напряжение Uпор электронного ключа.

Переходные процессы в электронных ключах

на полевых транзисторах определяются временем перезаряда паразитного конденсатора нагрузки Сн через сопротивление открытого канала Rкмин или через резистор R (который на порядок больше) при закрытом канале.Поэтому быстродействие таких логических схем относительно невелико при средних уровнях потребляемой мощности на один ключ.

Единственное преимущество логических ключей на n-МОП структурах - минимальные габариты. При ограниченной площади кремниевой пластины на ее поверхности можно разместить максимальное количество таких логических элементов.

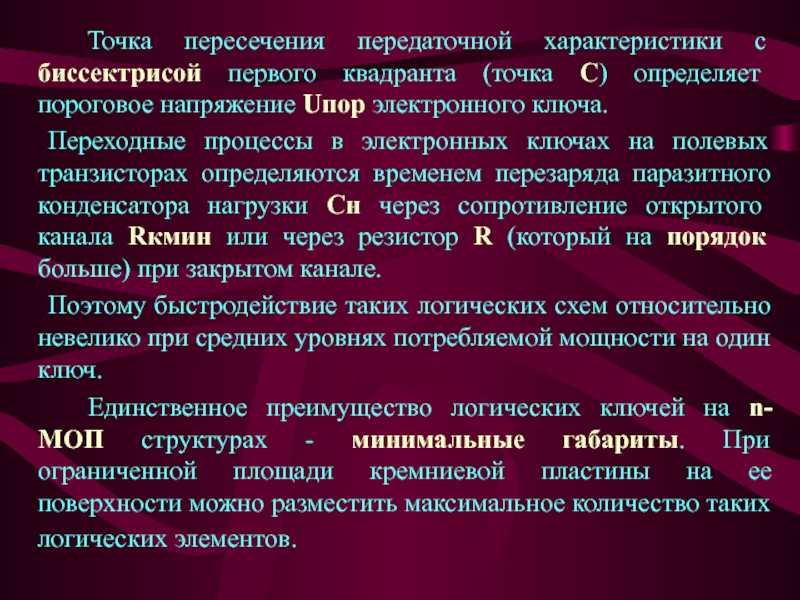

Слайд 8Электронный ключ КМОП

Значительно лучшими параметрами обладают электронные ключи, выполненные

на полевых транзисторах с взаимно дополняющей проводимостью n- и p-типа.

Этим объясняется название ключей - КМОП (буква К - от слова комплиментарный, дополнительный).+Е

Uвых

Uвх

VT1

з

с

и

Сн

з

с

и

VT2

Электронный ключ на полевом транзисторе с каналом n-типа VT1 в качестве нагрузки имеет полевой транзистор VT2 с каналом p-типа. Поскольку схема симметричная, то можно говорить, что ключ на транзис-торе p-типа VT2 в качестве нагрузки имеет полевой тран-зистор с каналом n-типа VT1.

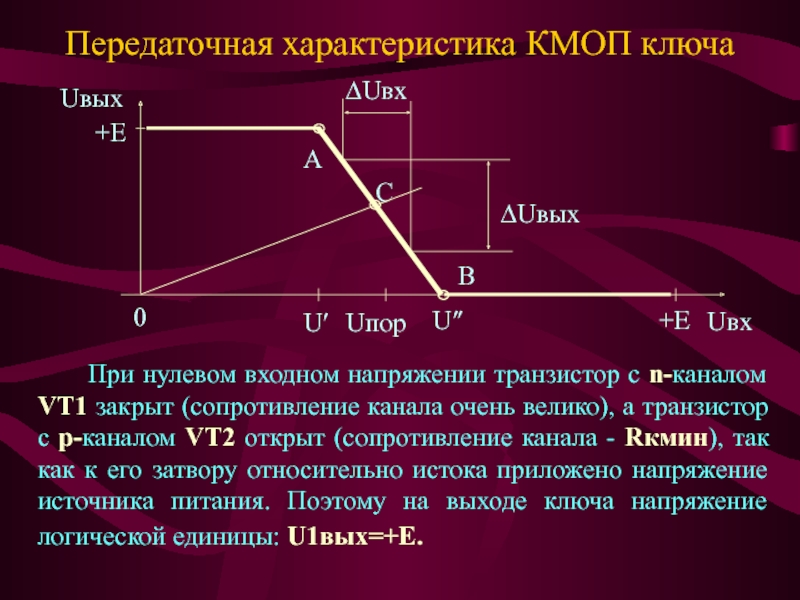

Слайд 9Передаточная характеристика КМОП ключа

При нулевом входном напряжении транзистор с

n-каналом VT1 закрыт (сопротивление канала очень велико), а транзистор с

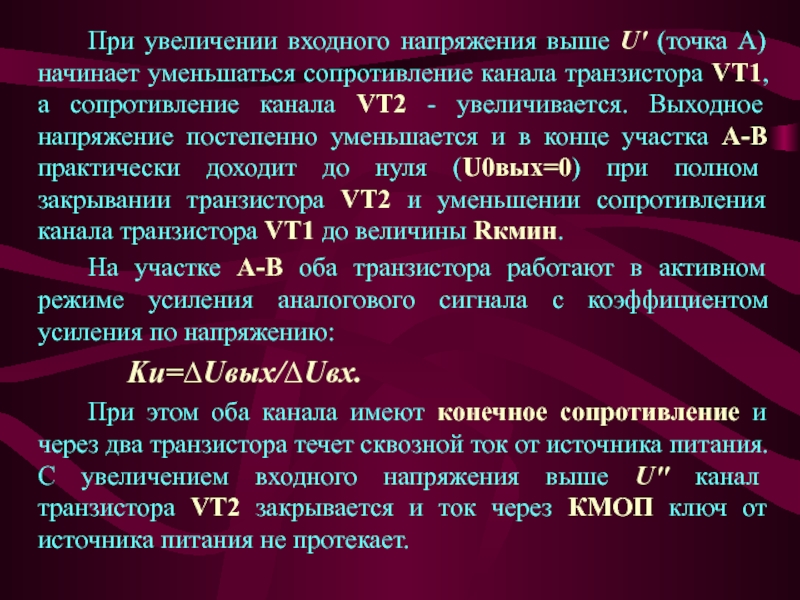

р-каналом VT2 открыт (сопротивление канала - Rкмин), так как к его затвору относительно истока приложено напряжение источника питания. Поэтому на выходе ключа напряжение логической единицы: U1вых=+Е.Слайд 10 При увеличении входного напряжения выше U' (точка А) начинает уменьшаться

сопротивление канала транзистора VT1, а сопротивление канала VT2 - увеличивается.

Выходное напряжение постепенно уменьшается и в конце участка А-В практически доходит до нуля (U0вых=0) при полном закрывании транзистора VT2 и уменьшении сопротивления канала транзистора VT1 до величины Rкмин.На участке А-В оба транзистора работают в активном режиме усиления аналогового сигнала с коэффициентом усиления по напряжению:

Ku=∆Uвых/∆Uвх.

При этом оба канала имеют конечное сопротивление и через два транзистора течет сквозной ток от источника питания. С увеличением входного напряжения выше U" канал транзистора VT2 закрывается и ток через КМОП ключ от источника питания не протекает.

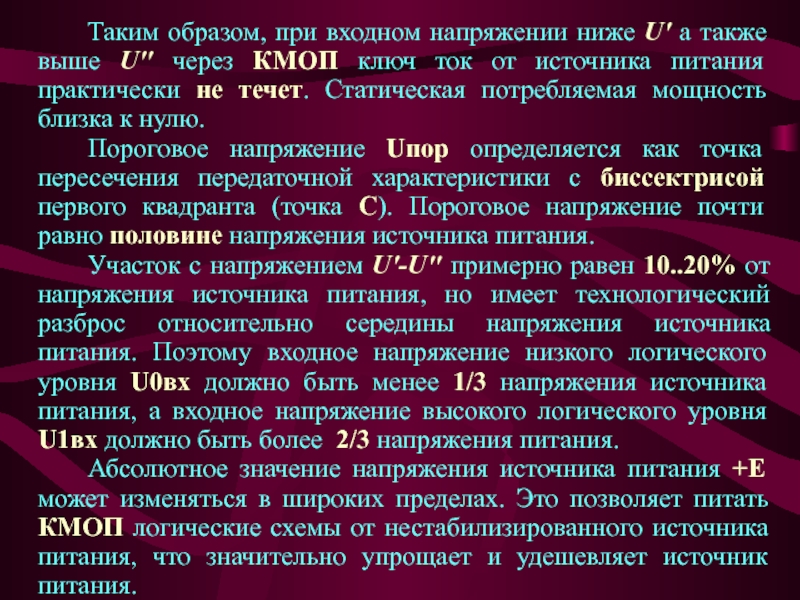

Слайд 11 Таким образом, при входном напряжении ниже U' а также выше

U" через КМОП ключ ток от источника питания практически не

течет. Статическая потребляемая мощность близка к нулю.Пороговое напряжение Uпор определяется как точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С). Пороговое напряжение почти равно половине напряжения источника питания.

Участок с напряжением U'-U" примерно равен 10..20% от напряжения источника питания, но имеет технологический разброс относительно середины напряжения источника питания. Поэтому входное напряжение низкого логического уровня U0вх должно быть менее 1/3 напряжения источника питания, а входное напряжение высокого логического уровня U1вх должно быть более 2/3 напряжения питания.

Абсолютное значение напряжения источника питания +Е может изменяться в широких пределах. Это позволяет питать КМОП логические схемы от нестабилизированного источника питания, что значительно упрощает и удешевляет источник питания.

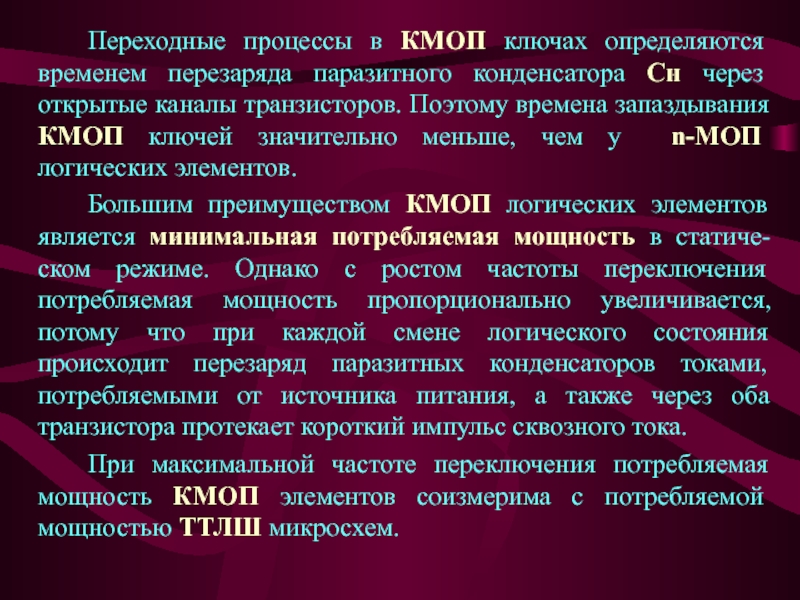

Слайд 12 Переходные процессы в КМОП ключах определяются временем перезаряда паразитного конденсатора

Сн через открытые каналы транзисторов. Поэтому времена запаздывания КМОП ключей

значительно меньше, чем у n-МОП логических элементов.Большим преимуществом КМОП логических элементов является минимальная потребляемая мощность в статиче-ском режиме. Однако с ростом частоты переключения потребляемая мощность пропорционально увеличивается, потому что при каждой смене логического состояния происходит перезаряд паразитных конденсаторов токами, потребляемыми от источника питания, а также через оба транзистора протекает короткий импульс сквозного тока.

При максимальной частоте переключения потребляемая мощность КМОП элементов соизмерима с потребляемой мощностью ТТЛШ микросхем.

Слайд 13 У элемента Шеффера транзисторы VT1, VT2 с р-каналом соединены параллельно,

а транзисторы VT3, VT4 с n-каналом - последовательно. При подаче

высокого логического уровня на оба входа Х1, Х2 закрываются транзисторы VT1, VT2 и открываются транзисторы VT3, VT4. На выход подается низкий логический уровень U0вых.Элемент Шеффера

″И-НЕ″

VT1

з

+Е

x1

VT3

с

и

з

и

с

з

и

с

VT2

з

VT4

с

и

x2

y

VT4

з

+Е

x1

VT1

и

с

з

с

и

з

с

и

VT3

з

VT2

и

с

x2

y

Элемент Пирса

″ИЛИ-НЕ″

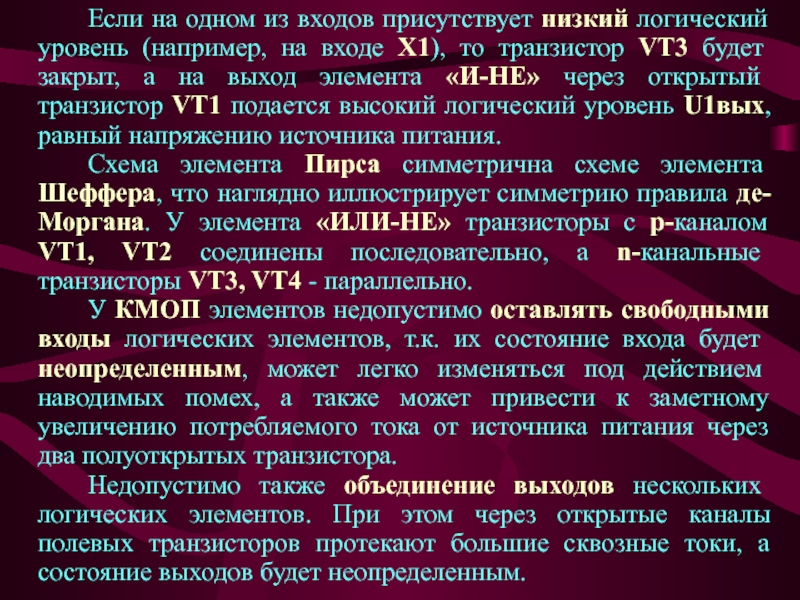

Слайд 14 Если на одном из входов присутствует низкий логический уровень (например,

на входе Х1), то транзистор VT3 будет закрыт, а на

выход элемента «И-НЕ» через открытый транзистор VT1 подается высокий логический уровень U1вых, равный напряжению источника питания.Схема элемента Пирса симметрична схеме элемента Шеффера, что наглядно иллюстрирует симметрию правила де-Моргана. У элемента «ИЛИ-НЕ» транзисторы с р-каналом VT1, VT2 соединены последовательно, а n-канальные транзисторы VT3, VT4 - параллельно.

У КМОП элементов недопустимо оставлять свободными входы логических элементов, т.к. их состояние входа будет неопределенным, может легко изменяться под действием наводимых помех, а также может привести к заметному увеличению потребляемого тока от источника питания через два полуоткрытых транзистора.

Недопустимо также объединение выходов нескольких логических элементов. При этом через открытые каналы полевых транзисторов протекают большие сквозные токи, а состояние выходов будет неопределенным.

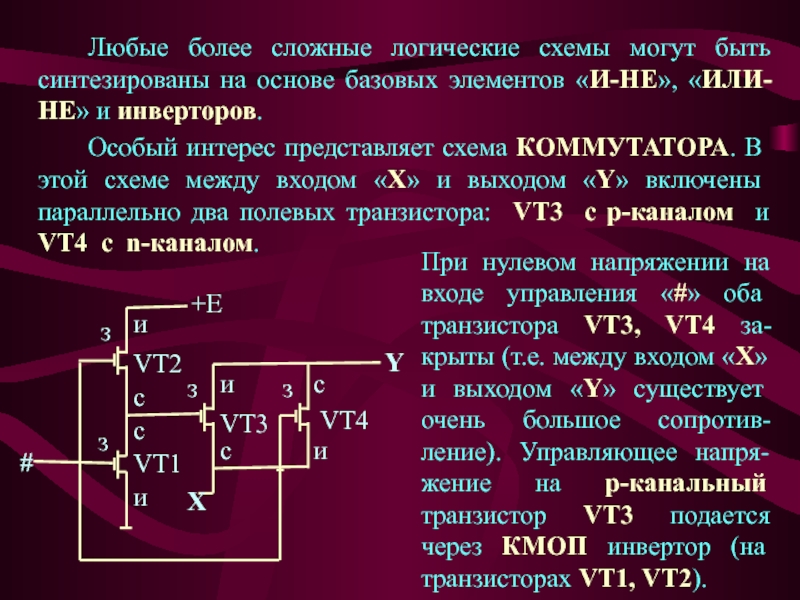

Слайд 15 Любые более сложные логические схемы могут быть синтезированы на основе

базовых элементов «И-НЕ», «ИЛИ-НЕ» и инверторов.

Особый интерес представляет схема КОММУТАТОРА.

В этой схеме между входом «Х» и выходом «Y» включены параллельно два полевых транзистора: VT3 с р-каналом и VT4 с n-каналом. VT2

VT1

з

+Е

#

VT3

с

и

з

и

с

з

и

с

Y

VT4

з

c

и

Х

При нулевом напряжении на входе управления «#» оба транзистора VT3, VT4 за-крыты (т.е. между входом «X» и выходом «Y» существует очень большое сопротив-ление). Управляющее напря-жение на р-канальный транзистор VT3 подается через КМОП инвертор (на транзисторах VT1, VT2).

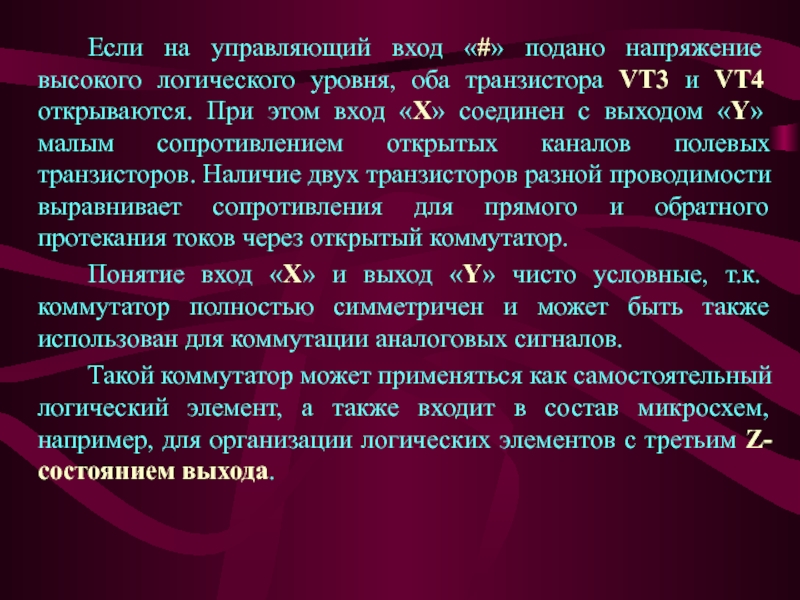

Слайд 16 Если на управляющий вход «#» подано напряжение высокого логического уровня,

оба транзистора VT3 и VT4 открываются. При этом вход «Х»

соединен с выходом «Y» малым сопротивлением открытых каналов полевых транзисторов. Наличие двух транзисторов разной проводимости выравнивает сопротивления для прямого и обратного протекания токов через открытый коммутатор.Понятие вход «Х» и выход «Y» чисто условные, т.к. коммутатор полностью симметричен и может быть также использован для коммутации аналоговых сигналов.

Такой коммутатор может применяться как самостоятельный логический элемент, а также входит в состав микросхем, например, для организации логических элементов с третьим Z-состоянием выхода.

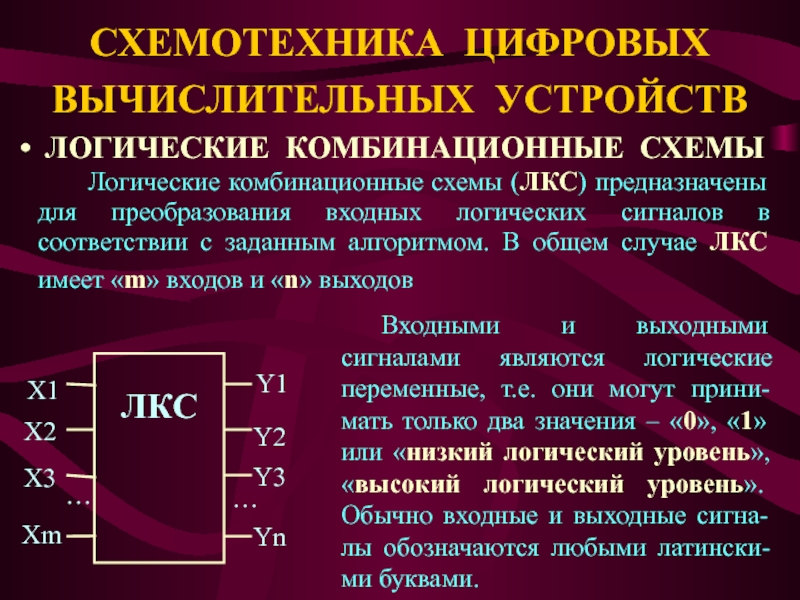

Слайд 17СХЕМОТЕХНИКА ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ

ЛОГИЧЕСКИЕ КОМБИНАЦИОННЫЕ СХЕМЫ

Логические комбинационные схемы

(ЛКС) предназначены для преобразования входных логических сигналов в соответствии с

заданным алгоритмом. В общем случае ЛКС имеет «m» входов и «n» выходовX1

X2

X3

Xm

…

…

ЛКС

Y1

Y2

Y3

Yn

Входными и выходными сигналами являются логические переменные, т.е. они могут прини-мать только два значения – «0», «1» или «низкий логический уровень», «высокий логический уровень». Обычно входные и выходные сигна-лы обозначаются любыми латински-ми буквами.

Слайд 18 Алгоритм преобразования ЛКС может быть задан тремя способами:

⮚ Булевыми

выражениями:

⮚ Таблицей состояний, в которой количество строк равно количеству возможных

комбинаций входных переменных (для логических переменных с двумя состояниями количество комбинаций - 2m); первые два столбца выходных сигналов - Y1, Y2 - соответствуют приведенным логическим функциям;⮚ Словесное описание (задание алгоритма на вербальном уровне), например: ЛКС мажоритарного элемента имеет 3 входа и 1 выход; сигнал на выходе равен «1», если не менее двух входных сигналов равны «1».

Слайд 19 Мажоритарный элемент может быть реализован на элементах любой функционально полной

системы логических элементов, например, на элементах "НЕ", "И", "ИЛИ"

ТАБЛИЦА

СОСТОЯНИЙ для трех входных переменных Между всеми тремя способами существует одно-значная взаимосвязь. Так, мажоритарный элемент может быть задан в виде таблицы состояний (см. выходные сигналы для функции Y3), или в виде Булевой функции:

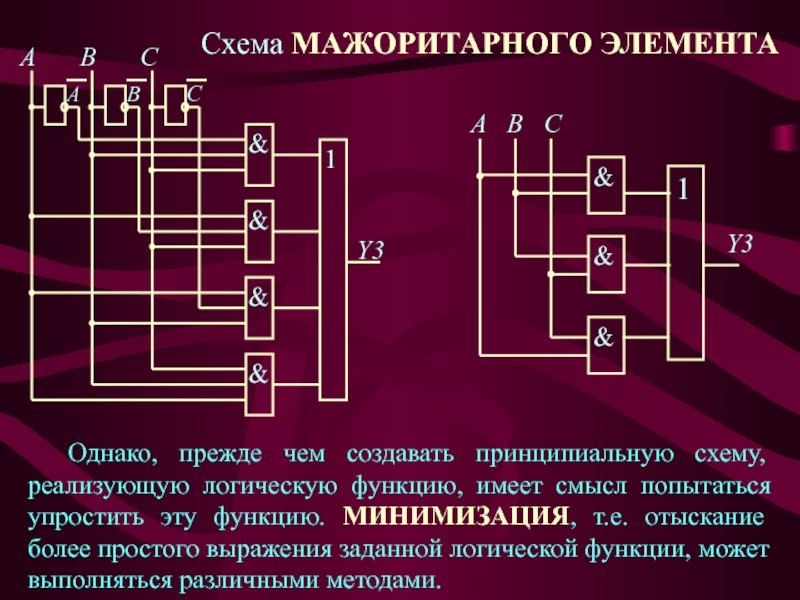

Слайд 20

Схема МАЖОРИТАРНОГО ЭЛЕМЕНТА

Y3

&

&

&

&

1

A

B

C

A

B

C

Однако, прежде чем создавать принципиальную схему, реализующую логическую

функцию, имеет смысл попытаться упростить эту функцию. МИНИМИЗАЦИЯ, т.е. отыскание

более простого выражения заданной логической функции, может выполняться различными методами.A

Y3

&

&

&

1

В

С

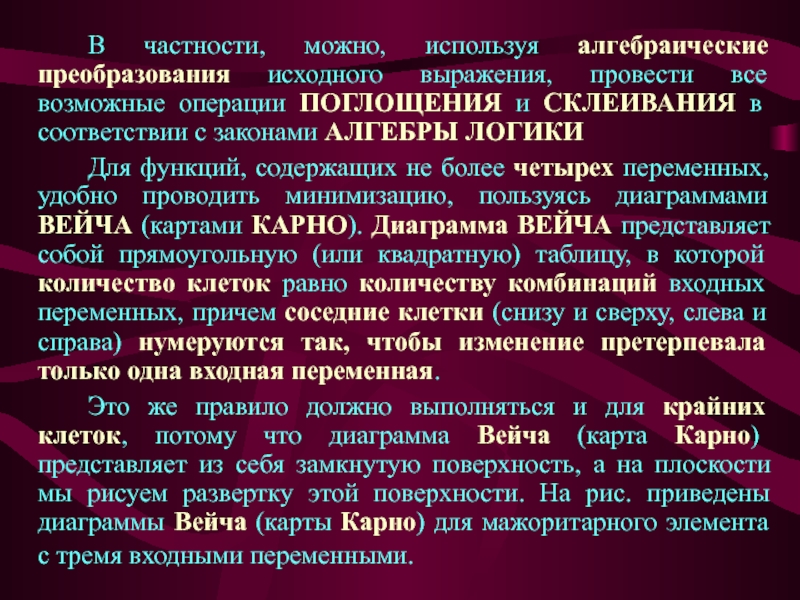

Слайд 21 В частности, можно, используя алгебраические преобразования исходного выражения, провести все

возможные операции ПОГЛОЩЕНИЯ и СКЛЕИВАНИЯ в соответствии с законами АЛГЕБРЫ

ЛОГИКИДля функций, содержащих не более четырех переменных, удобно проводить минимизацию, пользуясь диаграммами ВЕЙЧА (картами КАРНО). Диаграмма ВЕЙЧА представляет собой прямоугольную (или квадратную) таблицу, в которой количество клеток равно количеству комбинаций входных переменных, причем соседние клетки (снизу и сверху, слева и справа) нумеруются так, чтобы изменение претерпевала только одна входная переменная.

Это же правило должно выполняться и для крайних клеток, потому что диаграмма Вейча (карта Карно) представляет из себя замкнутую поверхность, а на плоскости мы рисуем развертку этой поверхности. На рис. приведены диаграммы Вейча (карты Карно) для мажоритарного элемента с тремя входными переменными.

Слайд 22 Операциям склеивания соответствуют на карте Карно объединения соседних единиц в

прямоугольники (или квадраты) с числом клеток, кратных 2k (2, 4,

8, 16...). Конечной целью минимизации является: ОБЪЕДИНЕНИЕ ВСЕХ ЕДИНИЦ В ПРЯМОУГОЛЬНИКИ С МАКСИМАЛЬ-НЫМИ РАЗМЕРАМИ. При этом необходимо учитывать, что в карте Карно левые и правые боковые грани соединены (т.е. диаграмма свернута в цилиндр) и возможно склеивание крайних правых клеток с крайними левыми.Операция склеивания : ab V ab = a (b V b) = a

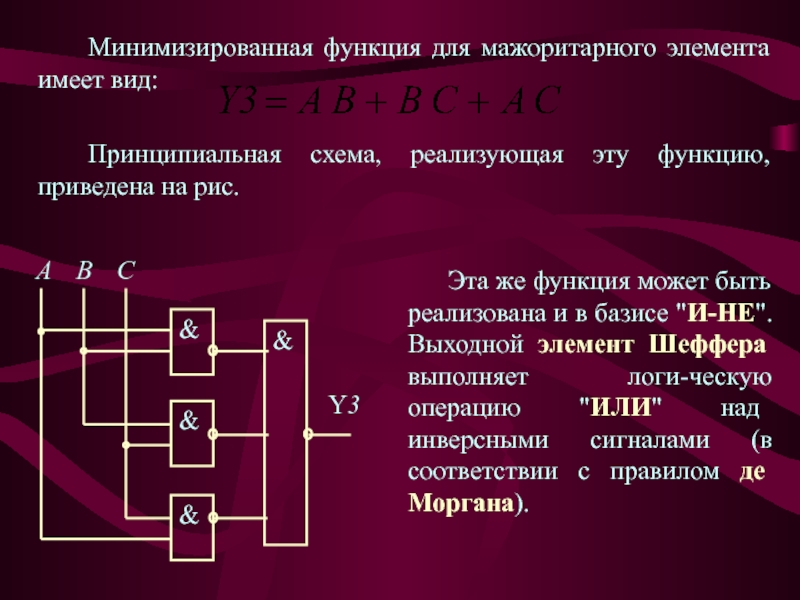

Слайд 23 Минимизированная функция для мажоритарного элемента имеет вид:

Принципиальная схема, реализующая эту

функцию, приведена на рис.

A

B

C

Y3

&

&

&

&

Эта же функция может быть реализована

и в базисе "И-НЕ". Выходной элемент Шеффера выполняет логи-ческую операцию "ИЛИ" над инверсными сигналами (в соответствии с правилом де Моргана).Слайд 24СУММАТОРЫ

СУММАТОР – это ЛКС, формирующая сигналы суммы (S) и

переноса (Р) при сложении двух двоичных чисел (А, В) и

сигнала переноса соседнего младшего разряда (С) по правилам двоичной арифметики.C

A

B

SM

S

P

Слайд 25 Логический элемент "И-ИЛИ-НЕ" имеется в наборе любой серии ТТЛ и

ТТЛШ.

Для КМОП элементов эти схемы сумматоров легко реализуются в

базисе "И-НЕ". Одноразрядный сумматор на элементах "И-ИЛИ-НЕ"

A

B

C

S

P

A

B

C

B

S

P

Слайд 26 На основе одноразрядного сумматора реализуются схемы многоразрядных сумматоров. На рис.

приведена схема четырехразрядного сумматора (аналогично можно реализовать сумматор на 8

или 16 разрядов). На входы А0..А3 подается первое слагаемое (младший разряд – А0), на входы В0..В3 - второе. Вход переноса (С) младшего разряда подключен к нулевому логическому уровню (к общей шине). Четыре разряда суммы формируются на выходах S0..S3, пятый разряд суммы - на выходе Р3.A0

B0

C

A

B

SM

S

P

S0

P0

A1

B1

S1

P1

C

A

B

SM

S

P

A2

B2

S2

P2

C

A

B

SM

S

P

A3

B3

S3

P3

C

A

B

SM

S

P

“0”

Слайд 27 В формировании сигналов S3, P3 участвуют все входные переменные А0..А3,

В0..В3. Но ко входам последней логической схемы эти сигналы проходят

через разное количество логических элементов, что вызывает появление на выходах ложных коротких импульсов, образованных эффектом гонок (состязаний).СОСТЯЗАНИЯ (ГОНКИ) В ЛОГИЧЕСКИХ СХЕМАХ

Реализация ЛКС всегда исходит из Булевой функции или таблицы состояний. На самом деле такое описание схемы является идеализацией, не учитывающей задержки распространения сигналов в реальных логических элементах. Наличие задержек приводит к тому, что в некоторые моменты времени не подтверждаются основные аксиомы алгебры логики:

Слайд 28 Наличие задержки распространения сигнала в инверторе приводит к появлению ложных

сигналов на выходах F1 и F2 с длительностью tз, определяемой

величиной задержки в инверторе.&

A

F1

t1

t2

t3

tз

F1

tз

t

A

t

t

F2

1

t1

t2

t3

tз

tз

t

A

t

t

A

F2

Слайд 29 Ситуации, при которых появляются ложные сигналы малой длительности, называются СОСТЯЗАНИЯМИ

или ГОНКАМИ. Появление гонок связано с прохождением нескольких логических сигналов

к входу одной схемы через цепи с разным количеством логических элементов. Даже, если количество элементов в этих цепях будет одинаковым, возникновение гонок возможно за счет различий времени задержки распространения сигналов внутри элементов (технологический разброс времени задержки у одинаковых элементов может достигать 1,5..2 раза).Существует ДВА радикальных метода борьбы с ГОНКАМИ (состязаниями):

⮚ стробирование логических сигналов импульсами, подаваемыми после завершения всех переходных процессов;

⮚ запоминание логических сигналов в регистрах после завершения всех переходных процессов.

Слайд 30ПРЕОБРАЗОВАТЕЛИ КОДОВ, ДЕШИФРАТОРЫ

ПРЕОБРАЗОВАТЕЛИ КОДОВ предназначены для перевода чисел из

одной формы представления в другую. Например, при вводе информации в

ЭВМ необходимо преобразовать десятичные числа в двоичные, а при выводе информации на индикаторы или печатающее устройство - двоичные или двоично-десятичные коды преобразовываются в коды управления знакогенератором, светодиодными или жидкокристаллическими индикаторами, механизмом печати.Отправным пунктом для построения ПРЕОБРАЗОВА-ТЕЛЯ КОДОВ является таблица состояний, в которой записываются полный набор входных и соответствующий набор выходных слов. Синтез ЛКС преобразователей кодов осуществляется известными алгоритмами, например, при помощи карт Карно.

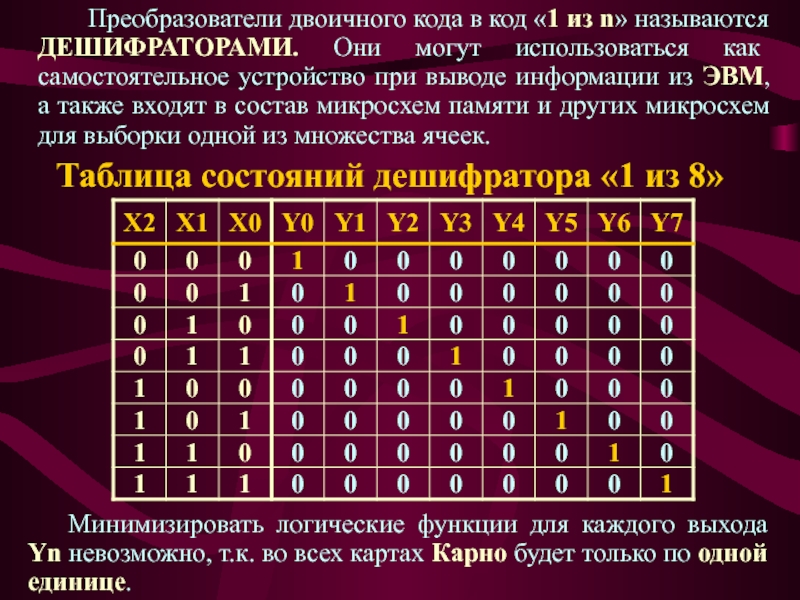

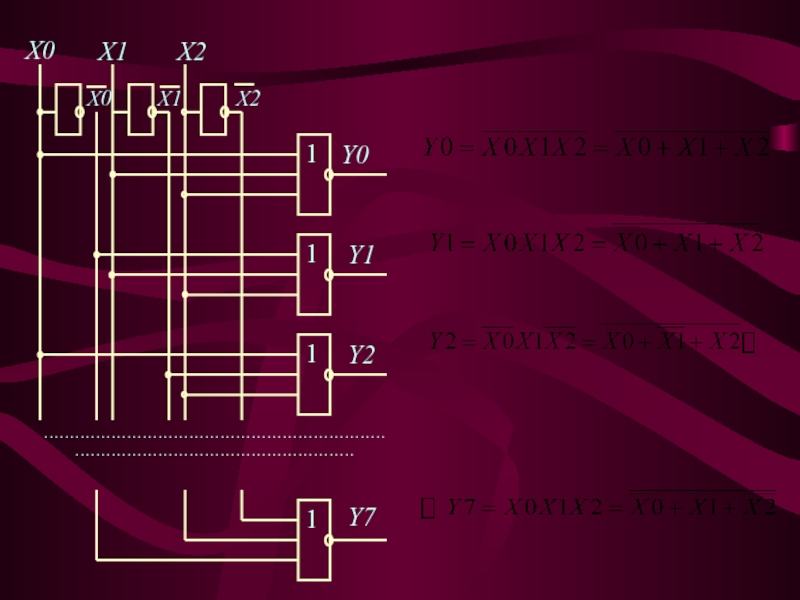

Слайд 31 Преобразователи двоичного кода в код «1 из n» называются ДЕШИФРАТОРАМИ.

Они могут использоваться как самостоятельное устройство при выводе информации из

ЭВМ, а также входят в состав микросхем памяти и других микросхем для выборки одной из множества ячеек.Таблица состояний дешифратора «1 из 8»

Минимизировать логические функции для каждого выхода Yn невозможно, т.к. во всех картах Карно будет только по одной единице.

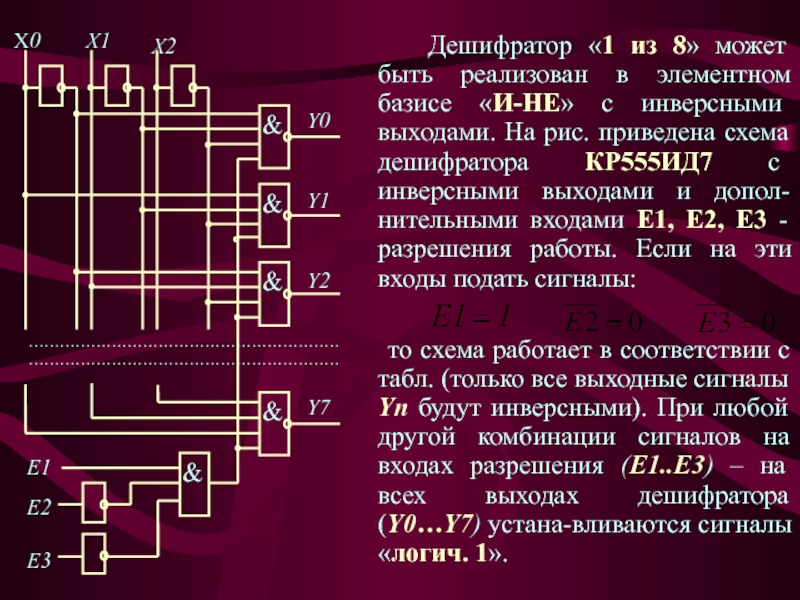

Слайд 33 Дешифратор «1 из 8» может быть реализован в элементном базисе

«И-НЕ» с инверсными выходами. На рис. приведена схема дешифратора КР555ИД7

с инверсными выходами и допол-нительными входами Е1, Е2, Е3 - разрешения работы. Если на эти входы подать сигналы:то схема работает в соответствии с табл. (только все выходные сигналы Yn будут инверсными). При любой другой комбинации сигналов на входах разрешения (E1..E3) – на всех выходах дешифратора (Y0…Y7) устана-вливаются сигналы «логич. 1».

X0

X1

X2

…………………………………………………………………………………………………………

&

E1

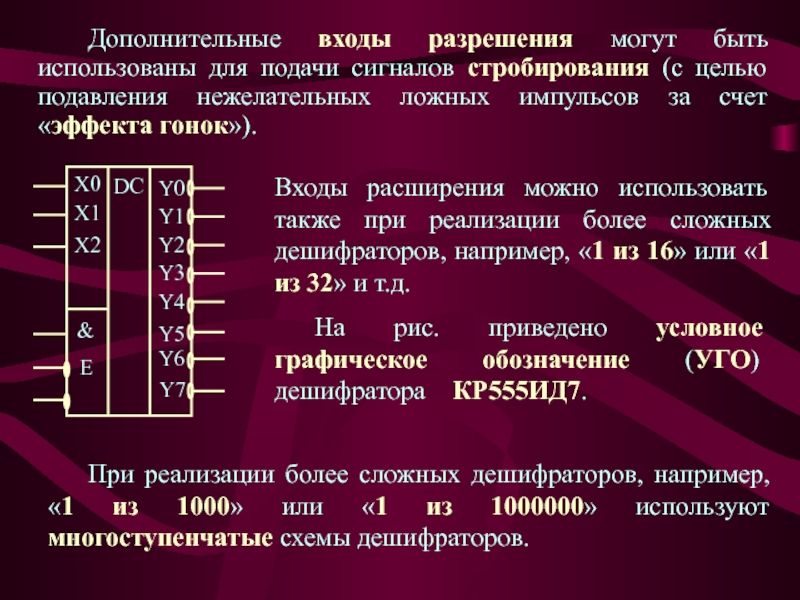

Слайд 34 Дополнительные входы разрешения могут быть использованы для подачи сигналов стробирования

(с целью подавления нежелательных ложных импульсов за счет «эффекта гонок»).

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X0

X1

X2

&

E

DC

Входы расширения можно использовать также при реализации более сложных дешифраторов, например, «1 из 16» или «1 из 32» и т.д.

На рис. приведено условное графическое обозначение (УГО) дешифратора КР555ИД7.

При реализации более сложных дешифраторов, например, «1 из 1000» или «1 из 1000000» используют многоступенчатые схемы дешифраторов.

Слайд 35МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

В цифровых устройствах часто возникает задача передачи

цифровой информации от «m» различных устройств к «n» приемникам через

канал общего пользования. Для этого на входе канала устанавливается устройство, называемое МУЛЬТИПЛЕКСОРОМ, которое согласно коду адреса Am подключает к каналу один из источников информации, а на выходе канала устройство ДЕМУЛЬТИПЛЕКСОР обеспечи-вает передачу информации к приемнику, имеющему цифровой адрес An.Мультиплексор и демультиплексор включают в себя дешифратор адреса. Выходные сигналы дешифратора управляют логическими вентилями, разрешая передачу информации через один выбранный вентиль.

Слайд 36 Логика работы мультиплексора для m = 4 описывается таблицей, в

которой X0...X3 - сигналы от независимых источников информации. Символ «*»

- обозначает любой логический уровень.Логика функционирования демультиплексора для случая n=4 иллюстрируется таблицей, в которой Y0...Y3 – выходные сигналы демультиплексора, подаваемые на входы приемников информации.

Слайд 37 Обычно при реализации мультиплексора и демульти-плексора совмещают дешифратор адреса и

информационные вентили.

Схема демультиплексора полностью совпадает со схемой дешифратора, имеющего вход

разрешения Е; именно на этот вход подается входной сигнал демультиплексора Х.X

A0

A1

Y0

&

&

&

&

Y1

Y2

Y3

Мультиплексор «4 на 1»

Демультиплексор «1на 4»

X0

X1

X2

X3

A0

A1

Y

&

1

&

&

&

Y

Слайд 38Вопросы для экспресс-контроля

1. Назовите методы описания (задания) логических комбинационных схем (ЛКС).

2. Объясните

необходимость минимизации ЛКС. Назовите методы минимизации ЛКС.

3. Назначение сумматоров. Реализация многораз-рядных

сумматоров.4. Что такое состязания (гонки) в логических элементах?

5. Методы борьбы с гонками (состязаниями).

6. Что такое дешифраторы? Области применения дешифраторов. Реализация дешифраторов.