Слайд 4Восьмиразрядные микропроцессоры

Слайд 5

Процессор - основной блок ЭВМ, осуществляющий обработку данных.

В настоящее

время основным типом процессоров являются

цифровые программно управляемые процессоры,

построенные

на базе цифровых электронных схем и

использующих для обработки данных методы Булевой алгебры и двоичной арифметики, реализующие произвольные алгоритмы, описанный в ограниченном базисе некоторой системы команд

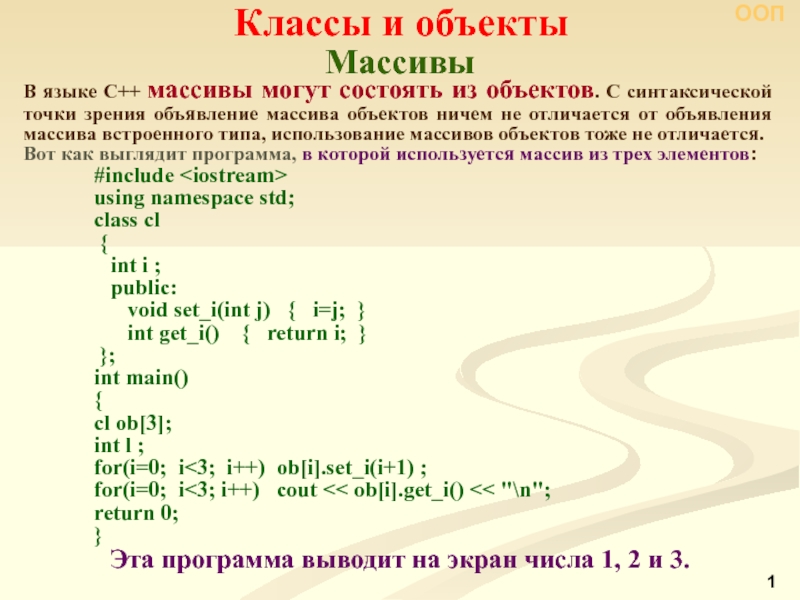

Слайд 6

Микропроцессор является программируемой универсальной БИС, способной выполнять функции центрального процессора

ЭВМ,

т. е. микропроцессор может считывать информацию из внешних устройств,

памяти

производить над ней арифметические и логические операции,

анализировать результаты вычислений и записывать данные в память и внешние устройства,

функционируя при этом под управлением команд

Слайд 7

Универсальный процессор - процессор, имеющий архитектуру, набор структурных блоков, систем

команд и конструктивно-технологическое исполнение, позволяющее одинаково эффективно применять его для

решения достаточно широкого круга разнотипных задач и использовать в различных условиях.

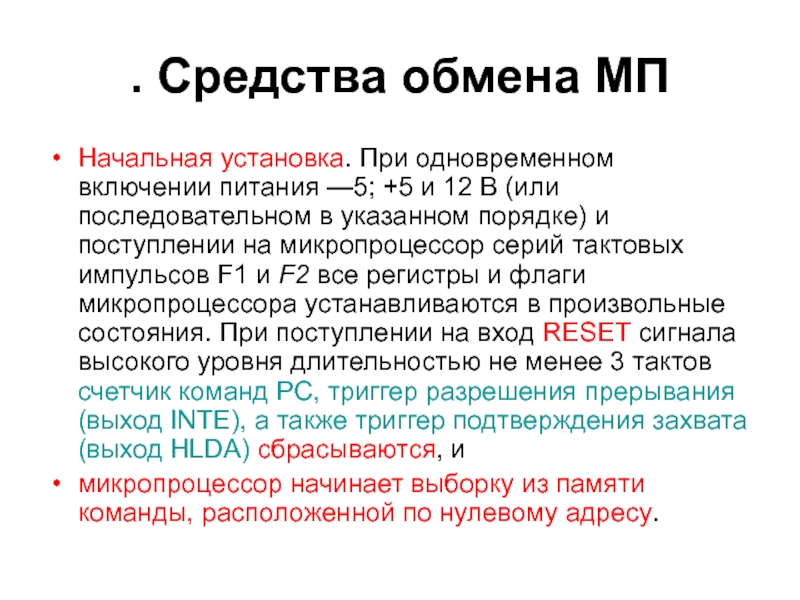

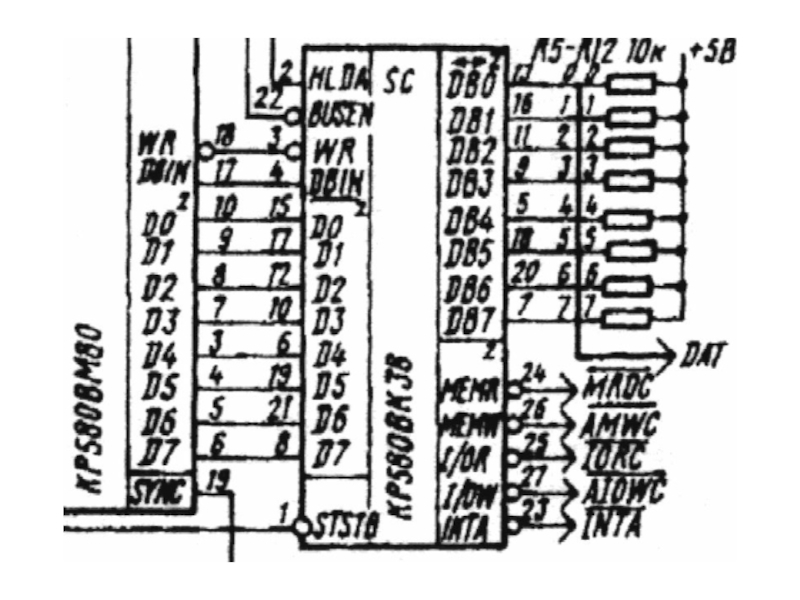

Слайд 12. Средства обмена МП

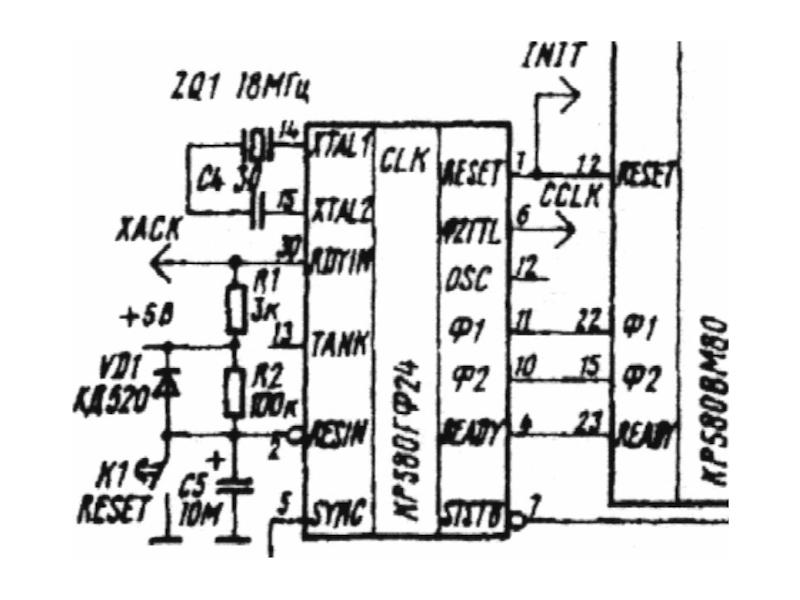

Начальная установка. При одновременном включении питания

—5; +5 и 12 В (или последовательном в указанном порядке)

и поступлении на микропроцессор серий тактовых импульсов F1 и F2 все регистры и флаги микропроцессора устанавливаются в произвольные состояния. При поступлении на вход RESET сигнала высокого уровня длительностью не менее 3 тактов счетчик команд PC, триггер разрешения прерывания (выход INTE), а также триггер подтверждения захвата (выход HLDA) сбрасываются, и

микропроцессор начинает выборку из памяти команды, расположенной по нулевому адресу.

Слайд 13

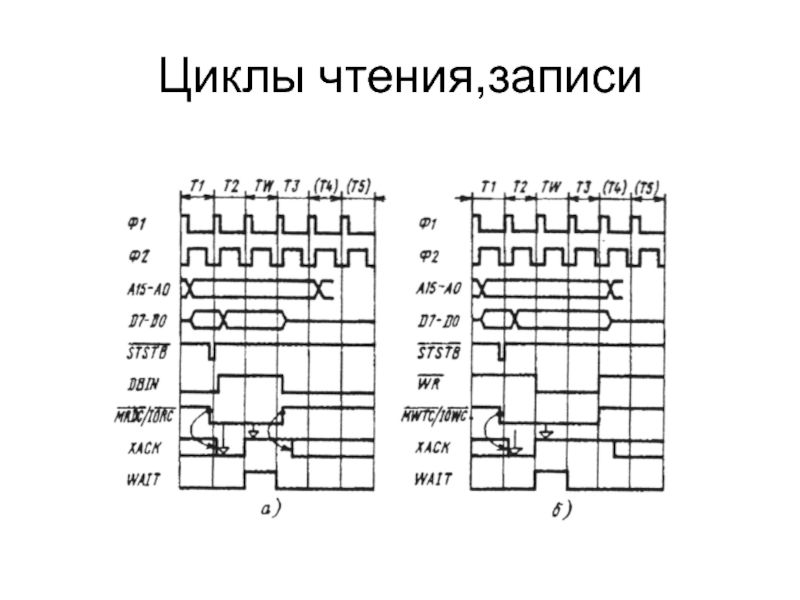

Микропроцессор выполняет различные команды за различное время в течение от

1 до 5 машинных циклов (Ml—М5) Первый цикл обычно состоит

из 4—5 машинных тактов,

последующие — из 3

Слайд 14Особые состояния МП

1.Пуск

2.Ожидание

3.Захват

4.Останов

5.Прерывания

Слайд 15Состояние «ожидание»

предназначено для согласования работы микропроцессора с медленнодействующими памятью или

внешними устройствами, которые не успевают выставить данные па входы микропроцессора

DO—D7 во время действия сигнала DBIN и циклах чтения или принять их

переход в состояние при сигнале на входе READY=0

во время состоянии ожидания микропроцессор на выходе WAIT выставляет сигнал высокого уровня, а на остальных выходах сигналы не изменяются

Слайд 16Состояние «захват».

По сигналу высокого уровня, поступающего от внешних устройств

или пульта оператора на вход HOLD, микропроцессор переходит, в состояние

«захват».

Состояние «захват» предназначено для того, чтобы внешнее устройство могло считывать или записывать информацию непосредственно в память системы, минуя микропроцессор,

Слайд 17Состояние «останов»

похоже на состояние «ожидание», только оно происходит

в результате выполнения команды HLT,

выйти из состояния «останов» можно,

только осуществив начальную установку путем отключения и включения питания или подачей сигнала RESET с пульта управления

Слайд 18. Режим прерывания

. Режим прерывания может наступить при подаче

на вход INT сигнала высокого уровня

запрос па прерывание может

быть обслужен, если триггер прерывания микропроцессора (выход INTE) установлен в «1». Обычно этот триггер по сигналу RESET сбрасывается в «О» и запрещает прерывание. Разрешить прерывание можно программным путем по команде

Слайд 19Интерфейс ввода-вывода микропроцессора

Первый метод предполагает обращение к внешним устройствам

как к ячейкам памяти Таким образом, адресное пространство, отводимое для

этих устройств, полностью входит в 64 К адресов памяти.

При втором методе организации обращения к внешним устройствам осуществляется раздельное управление памятью и внешними устройствами. Обмен с внешними устройствами выполняется с помощью команд IN и OUT.

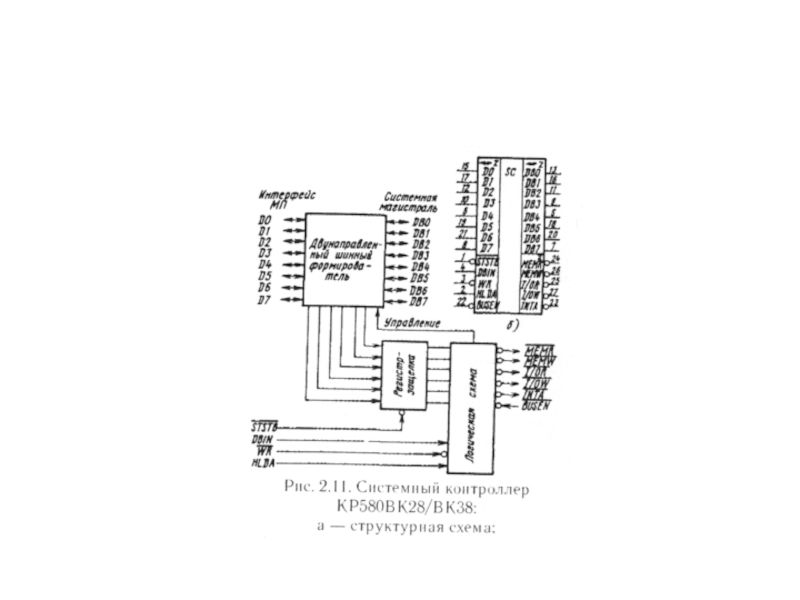

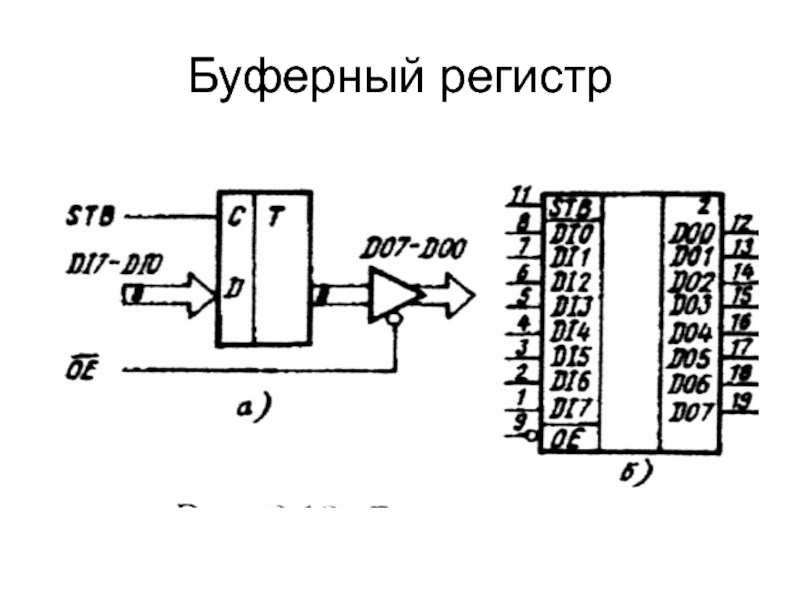

Слайд 30

Основой схемы является 8-разрядный регистр-защелка со статическим синхро-входом STB (Strobe).

Запись данных в регистр разрешена при STB = 1

. В

противном случае регистр находится в режиме хранения. На выходе регистра имеется трехстабильный буфер, управляемый сигналом ОЕ (Output Enable). Буфер обеспечивает выходной ток до 32 мА и емкость нагрузки до 300 пФ. Если управляющий сигнал ОЕ активен, то данные регистра передаются на выход микросхемы. При ОЕ=1 выходной буфер закрыт и находится в высокоомном состоянии.

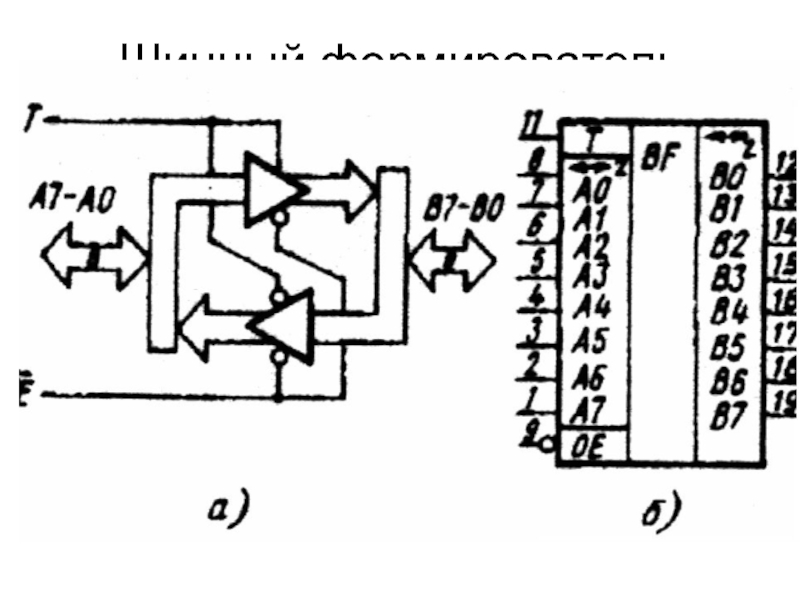

Слайд 32

Трехстабильные буферные схемы выбираются только при низком уровне напряжения на

линии ОЕ. При этом, если на входе Т (Transmitter) высокий

уровень напряжения, то открывается буфер для передачи из канала А в В. В противном случае осуществляется передача в обратном направлении.

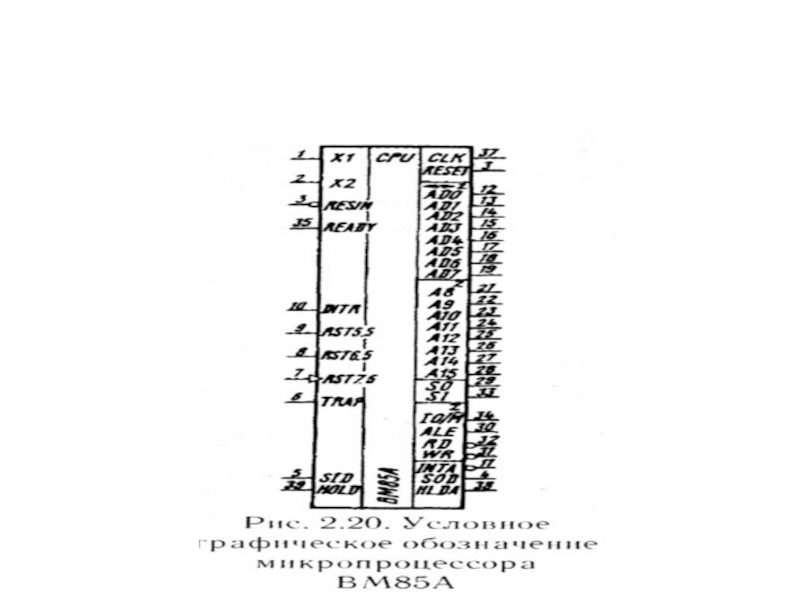

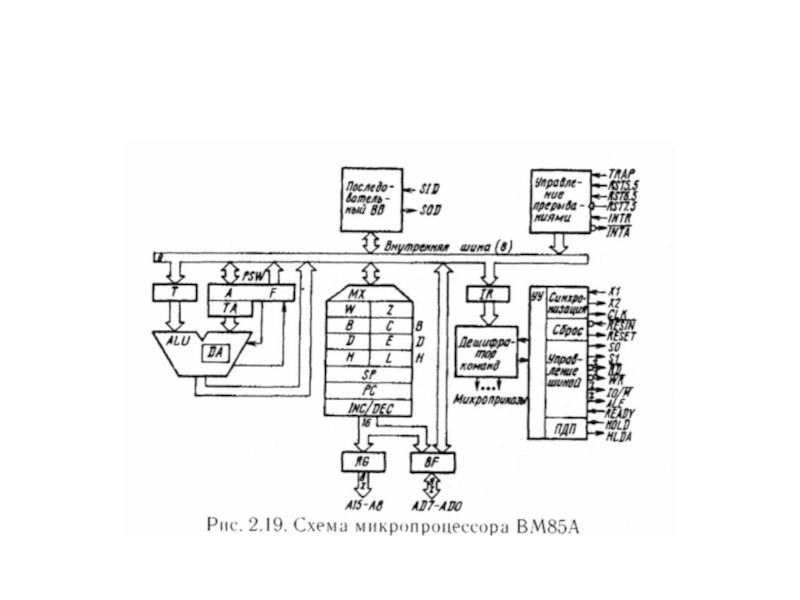

Слайд 34Процессор с мультиплексируемой шиной