Разделы презентаций

- Разное

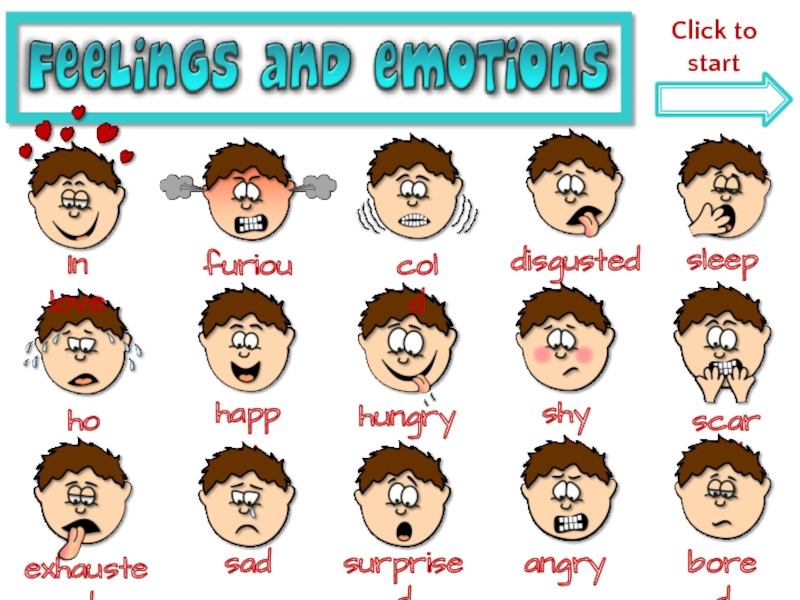

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Интегральные микросхемы

Содержание

- 1. Интегральные микросхемы

- 2. Интегральная микросхема, чип, микрочип — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле и помещённая в неразборный корпус

- 3. Степень интеграциималая интегральная схема (МИС) — до 100

- 4. Базовые логические элементы Схема И Схема реализует

- 5. Условное обозначение элемента "И"

- 6. Схема ИЛИ Схема ИЛИ реализует дизъюнкцию (логическое сложение)

- 7. Условное обозначение элемента "ИЛИ"

- 8. Схема НЕ. Схема НЕ (инвертор) реализует операцию отрицание двух или более логических значений. Условное обозначение элемента "НЕ"

- 9. Схема И-НЕСхема И-НЕ (штрих Шеффера) состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.Условное обозначение элемента "И-НЕ"

- 10. Схема ИЛИ-НЕ Схема ИЛИ-НЕ (стрелка Пирса) состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Условное обозначение элемента "ИЛИ-НЕ"

- 11. ТриггерТриггер - электронное устройство, которое может находиться

- 12. RS-триггер асинхронныйRS-триггер — триггер, который сохраняет своё предыдущее

- 13. D-триггерD-триггер (D delay — задержка)— запоминает состояние входа и выдаёт его на выход.

- 14. T-триггерСинхронный Т-триггер, при единице на входе Т, по каждому

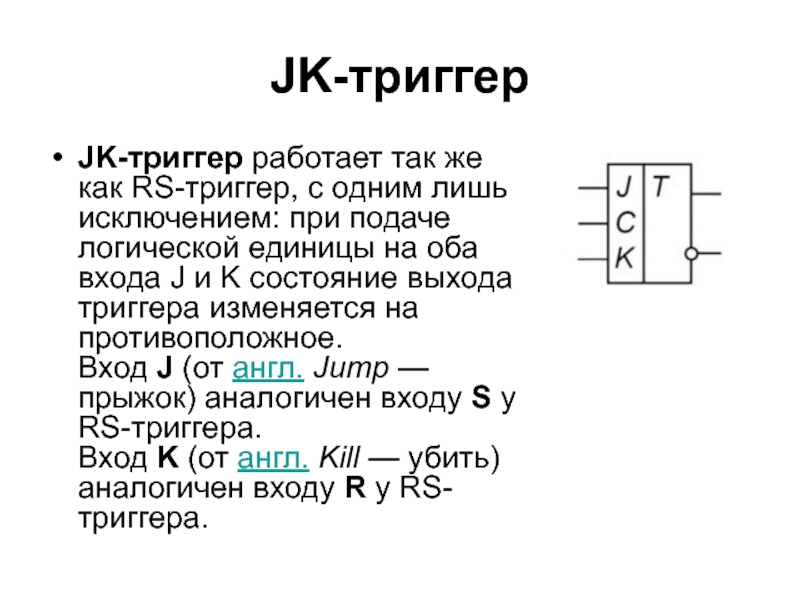

- 15. JK-триггерJK-триггер работает так же как RS-триггер, с одним

- 16. Скачать презентанцию

Интегральная микросхема, чип, микрочип — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле и помещённая в неразборный корпус

Слайды и текст этой презентации

Слайд 1Основы Микроэлектроники

Лекция 3 Интегральные микросхемы

Рахмеев Р.Г.

Башкирский государственный педагогический университет им.М.Акмуллы

Слайд 2

Интегральная микросхема, чип, микрочип — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле

и помещённая в неразборный корпус

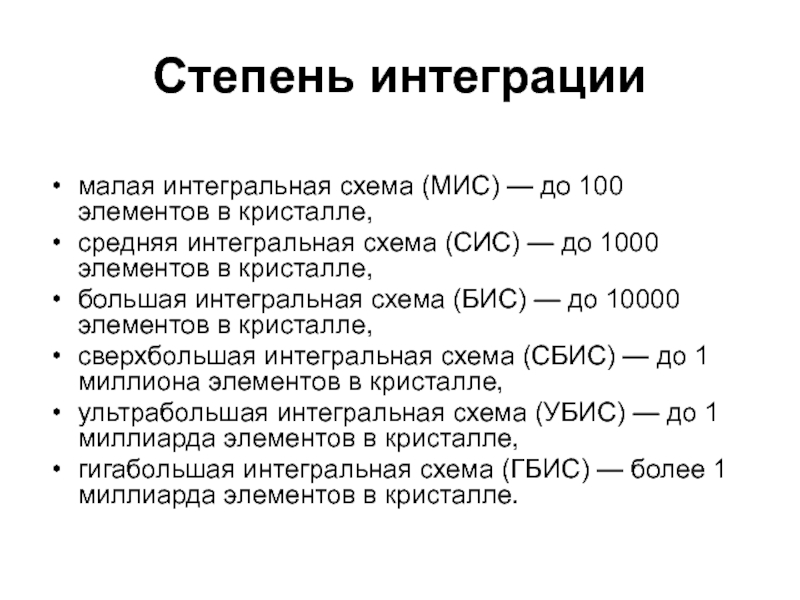

Слайд 3Степень интеграции

малая интегральная схема (МИС) — до 100 элементов в кристалле,

средняя

интегральная схема (СИС) — до 1000 элементов в кристалле,

большая интегральная схема

(БИС) — до 10000 элементов в кристалле,сверхбольшая интегральная схема (СБИС) — до 1 миллиона элементов в кристалле,

ультрабольшая интегральная схема (УБИС) — до 1 миллиарда элементов в кристалле,

гигабольшая интегральная схема (ГБИС) — более 1 миллиарда элементов в кристалле.

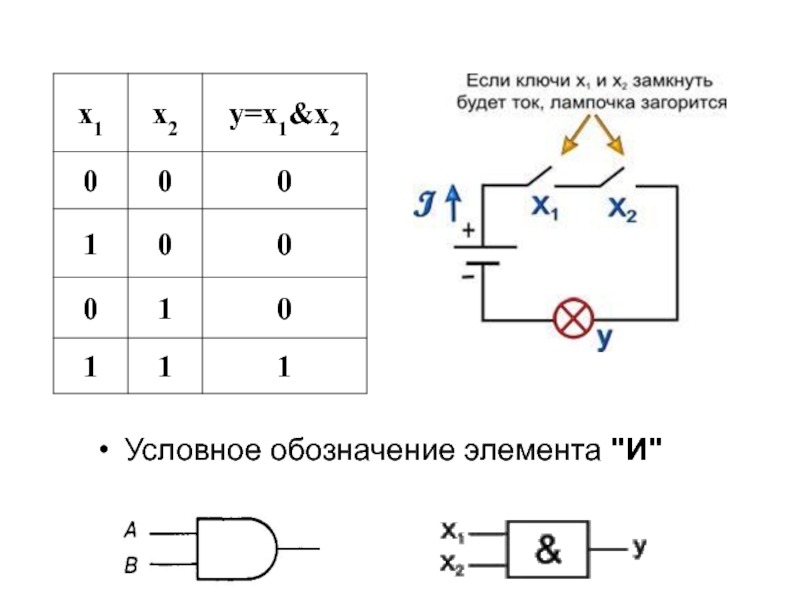

Слайд 4Базовые логические элементы

Схема И

Схема реализует конъюнкцию (логическое умножение)

двух или более логических значений

Единица на выходе схемы И будет

тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль. Слайд 6Схема ИЛИ

Схема ИЛИ реализует дизъюнкцию (логическое сложение) двух или более

логических значений

Когда хотя бы на одном входе схемы ИЛИ будет

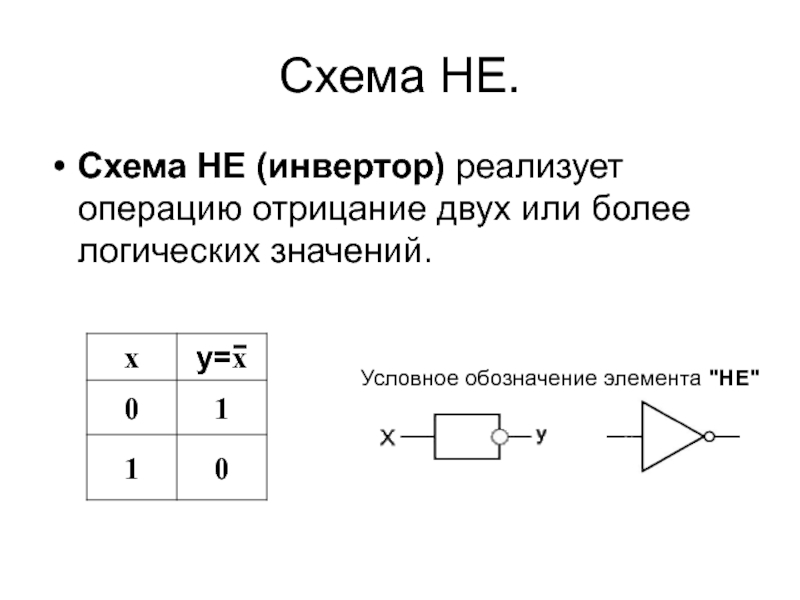

единица, на её выходе также будет единица. Слайд 8Схема НЕ.

Схема НЕ (инвертор) реализует операцию отрицание двух или более логических значений.

Условное обозначение

элемента "НЕ"

Слайд 9Схема И-НЕ

Схема И-НЕ (штрих Шеффера) состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Условное обозначение

элемента "И-НЕ"

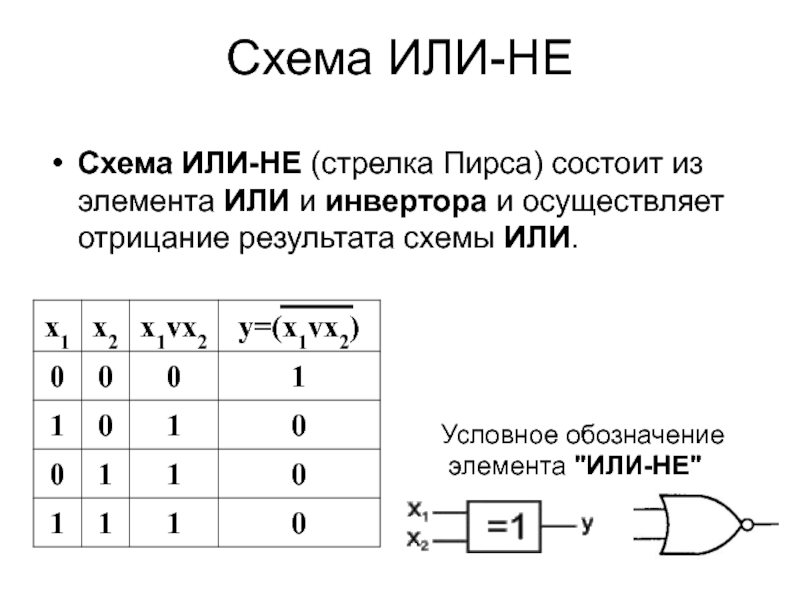

Слайд 10Схема ИЛИ-НЕ

Схема ИЛИ-НЕ (стрелка Пирса) состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата

схемы ИЛИ.

Условное обозначение

элемента "ИЛИ-НЕ"

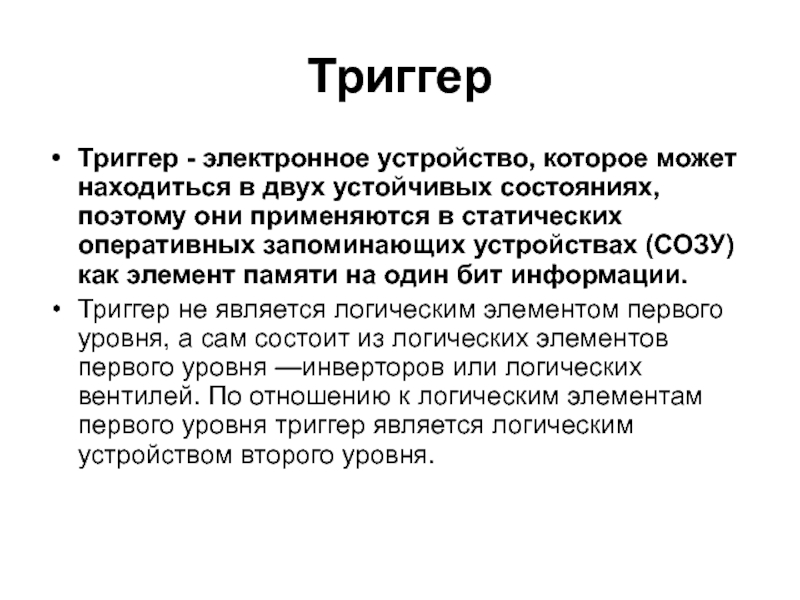

Слайд 11Триггер

Триггер - электронное устройство, которое может находиться в двух устойчивых

состояниях, поэтому они применяются в статических оперативных запоминающих устройствах (СОЗУ)

как элемент памяти на один бит информации.Триггер не является логическим элементом первого уровня, а сам состоит из логических элементов первого уровня —инверторов или логических вентилей. По отношению к логическим элементам первого уровня триггер является логическим устройством второго уровня.

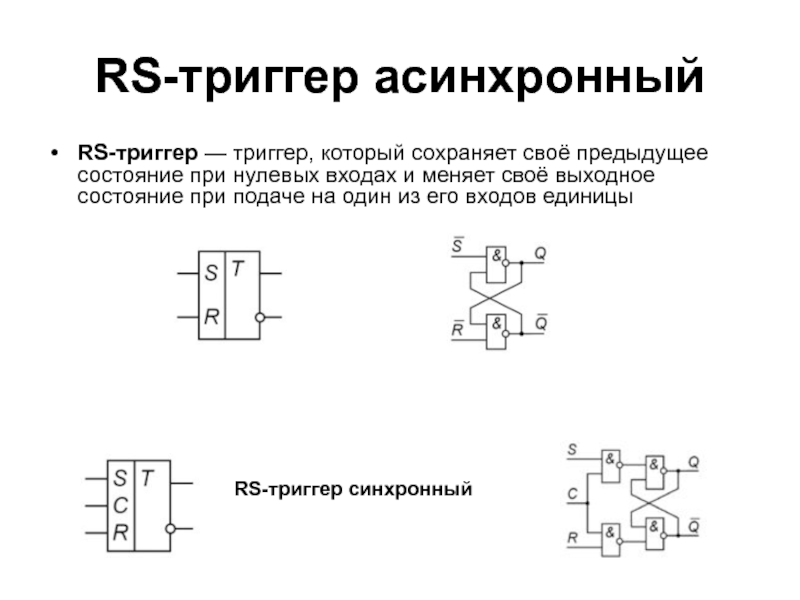

Слайд 12RS-триггер асинхронный

RS-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых

входах и меняет своё выходное состояние при подаче на один

из его входов единицыRS-триггер синхронный