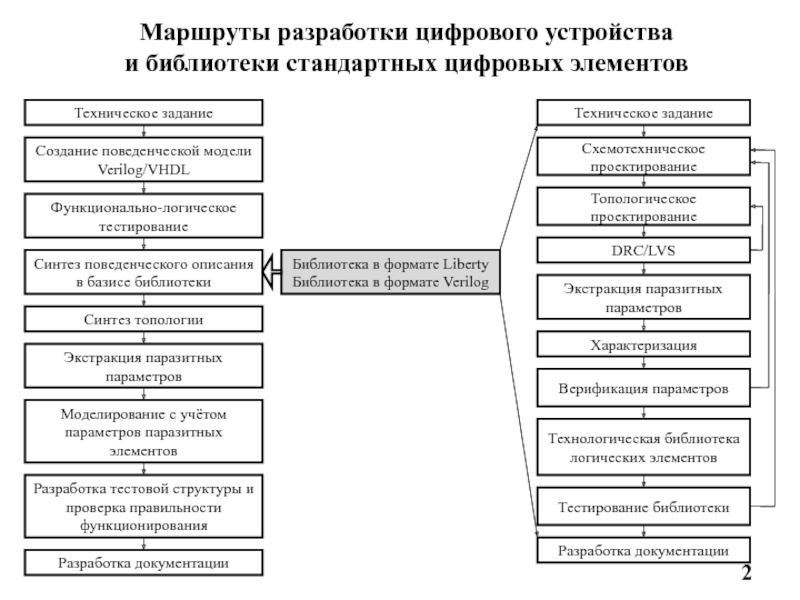

Слайд 2Маршруты разработки цифрового устройства

и библиотеки стандартных цифровых элементов

Техническое задание

Создание

поведенческой модели

Verilog/VHDL

Функционально-логическое тестирование

Синтез поведенческого описания в базисе библиотеки

Синтез топологии

Моделирование

с учётом параметров паразитных элементов

Разработка тестовой структуры и проверка правильности функционирования

Разработка документации

Экстракция паразитных параметров

Библиотека в формате Liberty

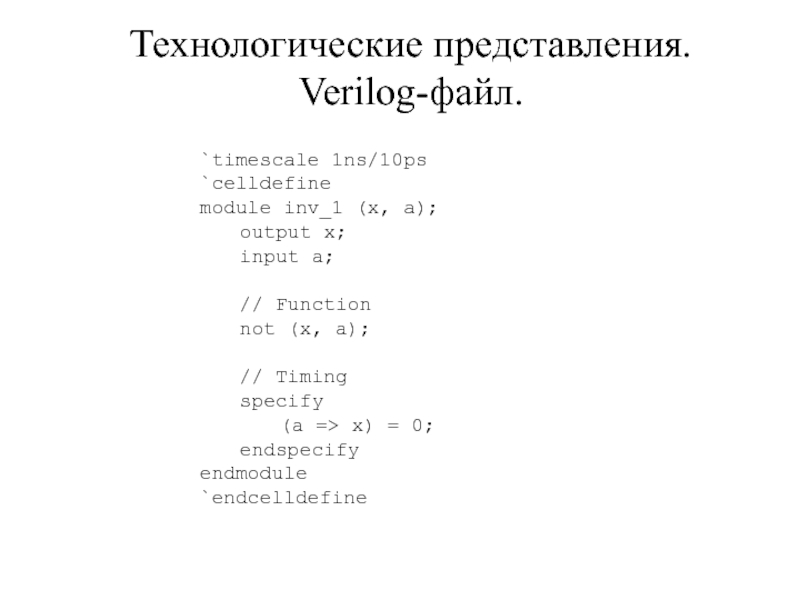

Библиотека в формате Verilog

Техническое задание

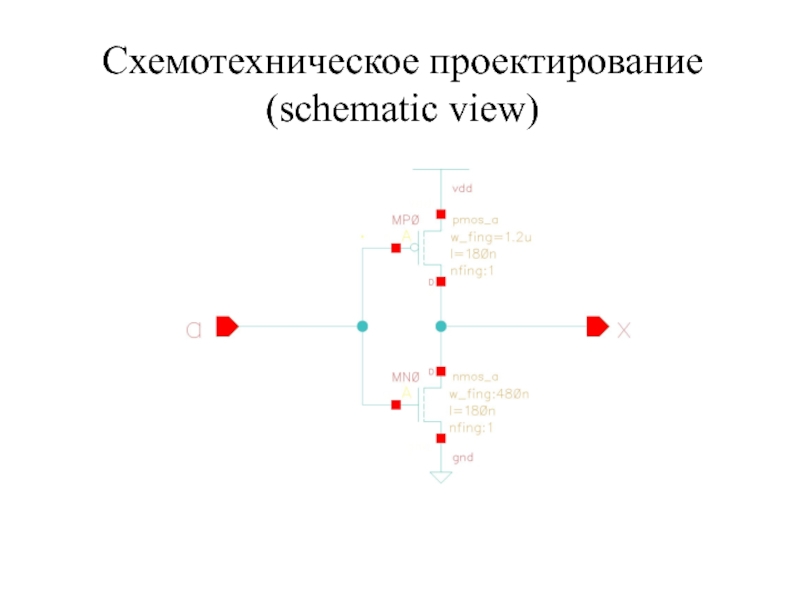

Схемотехническое проектирование

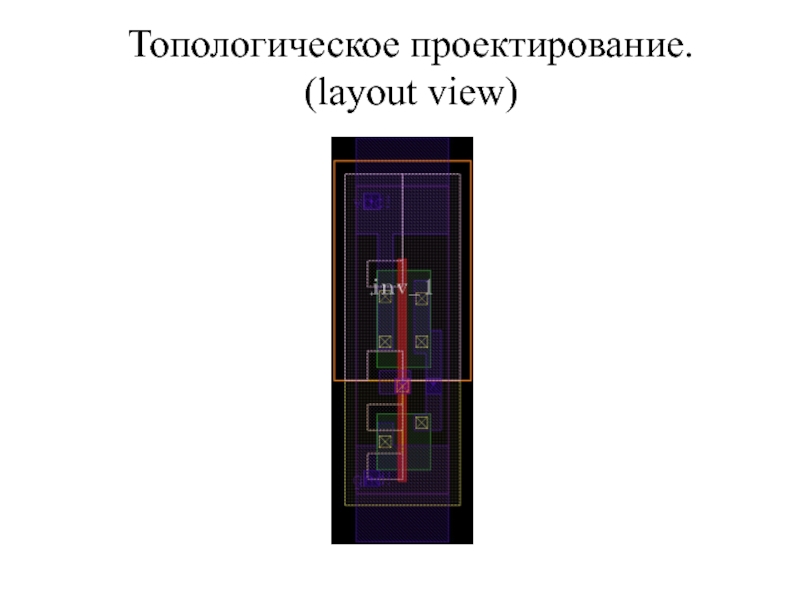

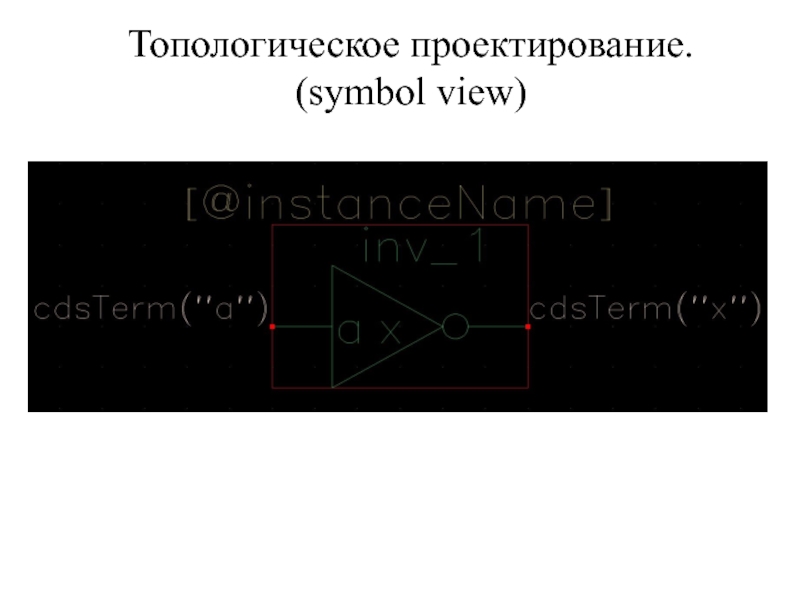

Топологическое проектирование

DRC/LVS

Экстракция паразитных параметров

Характеризация

Верификация параметров

Технологическая библиотека логических элементов

Тестирование библиотеки

Разработка документации

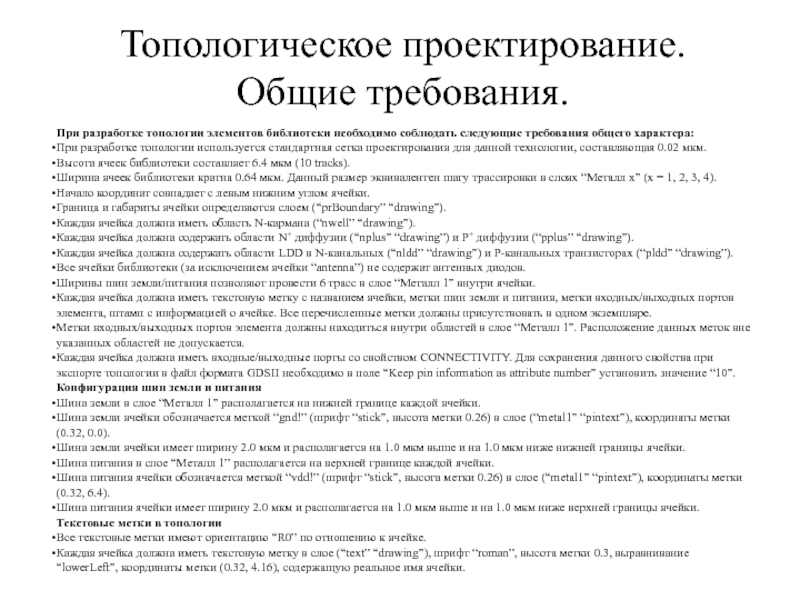

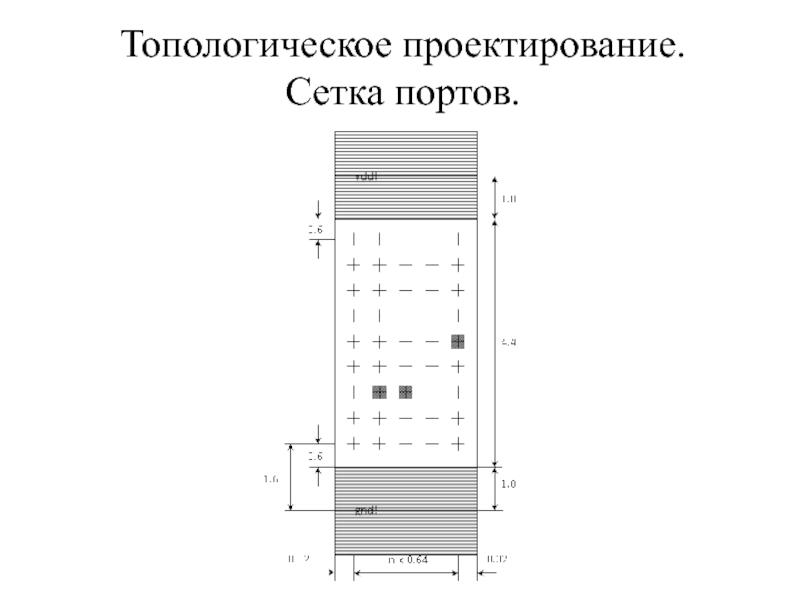

Слайд 5Топологическое проектирование.

Общие требования.

При разработке топологии элементов библиотеки необходимо соблюдать следующие

требования общего характера:

При разработке топологии используется стандартная сетка проектирования для

данной технологии, составляющая 0.02 мкм.

Высота ячеек библиотеки составляет 6.4 мкм (10 tracks).

Ширина ячеек библиотеки кратна 0.64 мкм. Данный размер эквивалентен шагу трассировки в слоях “Металл x” (x = 1, 2, 3, 4).

Начало координат совпадает с левым нижним углом ячейки.

Граница и габариты ячейки определяются слоем (“prBoundary” “drawing”).

Каждая ячейка должна иметь область N-кармана (“nwell” “drawing”).

Каждая ячейка должна содержать области N+ диффузии (“nplus” “drawing”) и P+ диффузии (“pplus” “drawing”).

Каждая ячейка должна содержать области LDD в N-канальных (“nldd” “drawing”) и P-канальных транзисторах (“pldd” “drawing”).

Все ячейки библиотеки (за исключением ячейки “antenna”) не содержат антенных диодов.

Ширины шин земли/питания позволяют провести 6 трасс в слое “Металл 1” внутри ячейки.

Каждая ячейка должна иметь текстовую метку с названием ячейки, метки шин земли и питания, метки входных/выходных портов элемента, штамп с информацией о ячейке. Все перечисленные метки должны присутствовать в одном экземпляре.

Метки входных/выходных портов элемента должны находиться внутри областей в слое “Металл 1”. Расположение данных меток вне указанных областей не допускается.

Каждая ячейка должна иметь входные/выходные порты со свойством CONNECTIVITY. Для сохранения данного свойства при экспорте топологии в файл формата GDSII необходимо в поле “Keep pin information as attribute number” установить значение “10”.

Конфигурация шин земли и питания

Шина земли в слое “Металл 1” располагается на нижней границе каждой ячейки.

Шина земли ячейки обозначается меткой “gnd!” (шрифт “stick”, высота метки 0.26) в слое (“metal1” “pintext”), координаты метки (0.32, 0.0).

Шина земли ячейки имеет ширину 2.0 мкм и располагается на 1.0 мкм выше и на 1.0 мкм ниже нижней границы ячейки.

Шина питания в слое “Металл 1” располагается на верхней границе каждой ячейки.

Шина питания ячейки обозначается меткой “vdd!” (шрифт “stick”, высота метки 0.26) в слое (“metal1” “pintext”), координаты метки (0.32, 6.4).

Шина питания ячейки имеет ширину 2.0 мкм и располагается на 1.0 мкм выше и на 1.0 мкм ниже верхней границы ячейки.

Текстовые метки в топологии

Все текстовые метки имеют ориентацию “R0” по отношению к ячейке.

Каждая ячейка должна иметь текстовую метку в слое (“text” “drawing”), шрифт “roman”, высота метки 0.3, выравнивание “lowerLeft”, координаты метки (0.32, 4.16), содержащую реальное имя ячейки.

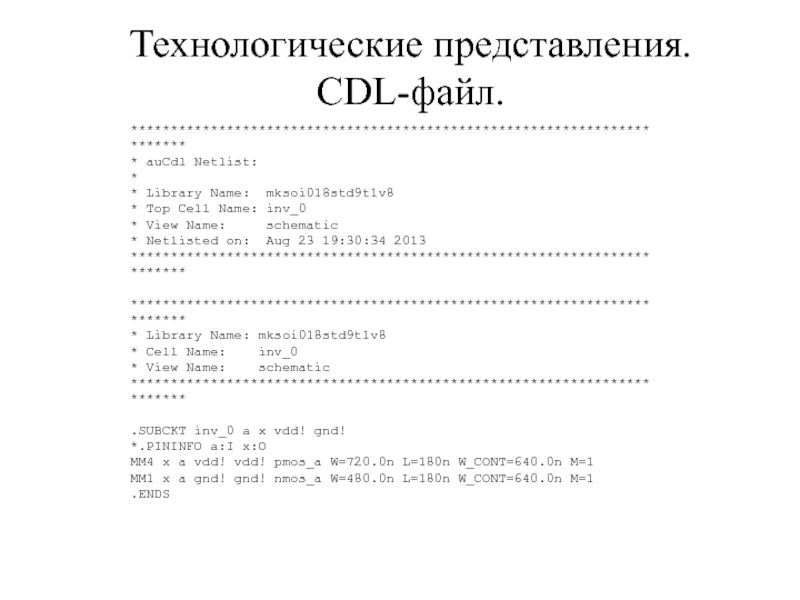

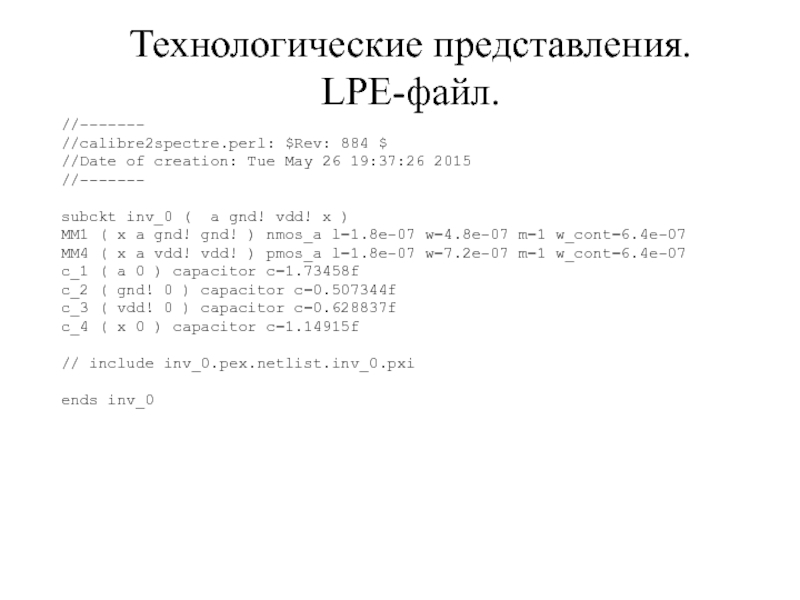

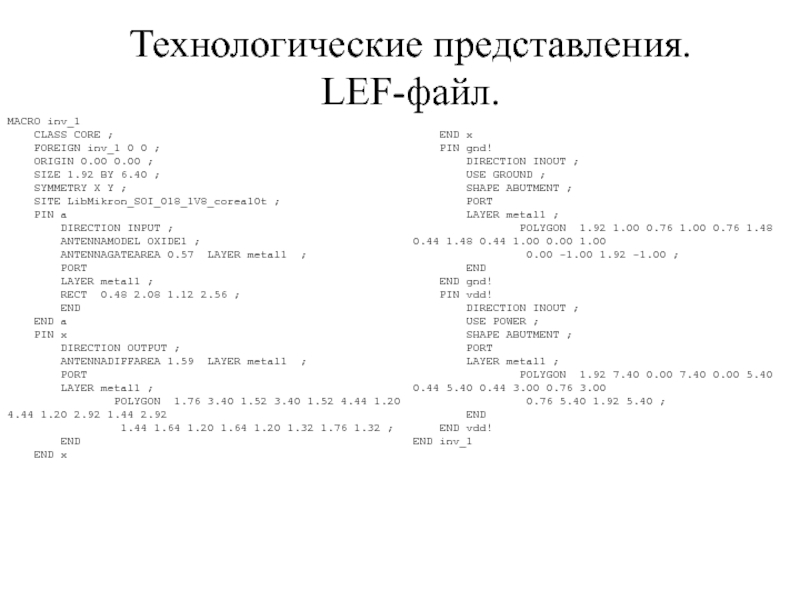

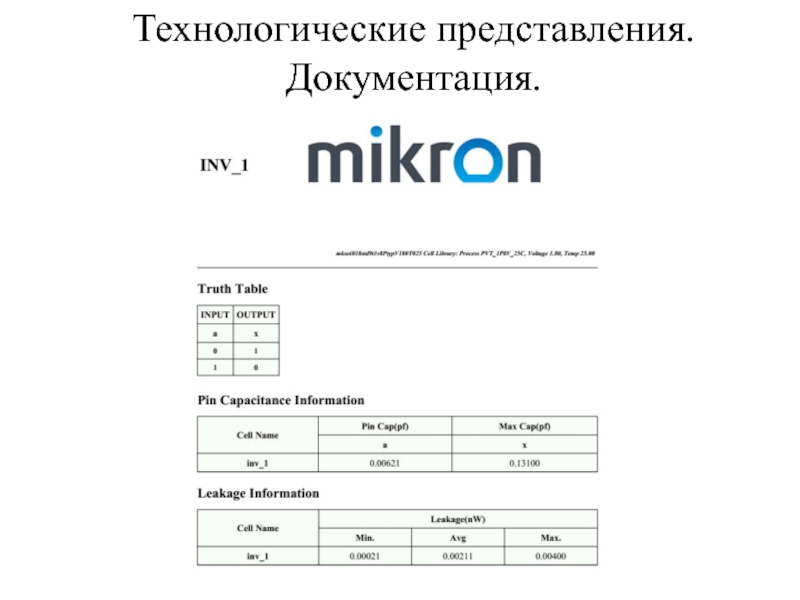

Слайд 13Технологические представления.

LEF-файл.

MACRO inv_1

CLASS CORE ;

FOREIGN inv_1

0 0 ;

ORIGIN 0.00 0.00 ;

SIZE

1.92 BY 6.40 ;

SYMMETRY X Y ;

SITE LibMikron_SOI_018_1V8_corea10t ;

PIN a

DIRECTION INPUT ;

ANTENNAMODEL OXIDE1 ;

ANTENNAGATEAREA 0.57 LAYER metal1 ;

PORT

LAYER metal1 ;

RECT 0.48 2.08 1.12 2.56 ;

END

END a

PIN x

DIRECTION OUTPUT ;

ANTENNADIFFAREA 1.59 LAYER metal1 ;

PORT

LAYER metal1 ;

POLYGON 1.76 3.40 1.52 3.40 1.52 4.44 1.20 4.44 1.20 2.92 1.44 2.92

1.44 1.64 1.20 1.64 1.20 1.32 1.76 1.32 ;

END

END x

END x

PIN gnd!

DIRECTION INOUT ;

USE GROUND ;

SHAPE ABUTMENT ;

PORT

LAYER metal1 ;

POLYGON 1.92 1.00 0.76 1.00 0.76 1.48 0.44 1.48 0.44 1.00 0.00 1.00

0.00 -1.00 1.92 -1.00 ;

END

END gnd!

PIN vdd!

DIRECTION INOUT ;

USE POWER ;

SHAPE ABUTMENT ;

PORT

LAYER metal1 ;

POLYGON 1.92 7.40 0.00 7.40 0.00 5.40 0.44 5.40 0.44 3.00 0.76 3.00

0.76 5.40 1.92 5.40 ;

END

END vdd!

END inv_1

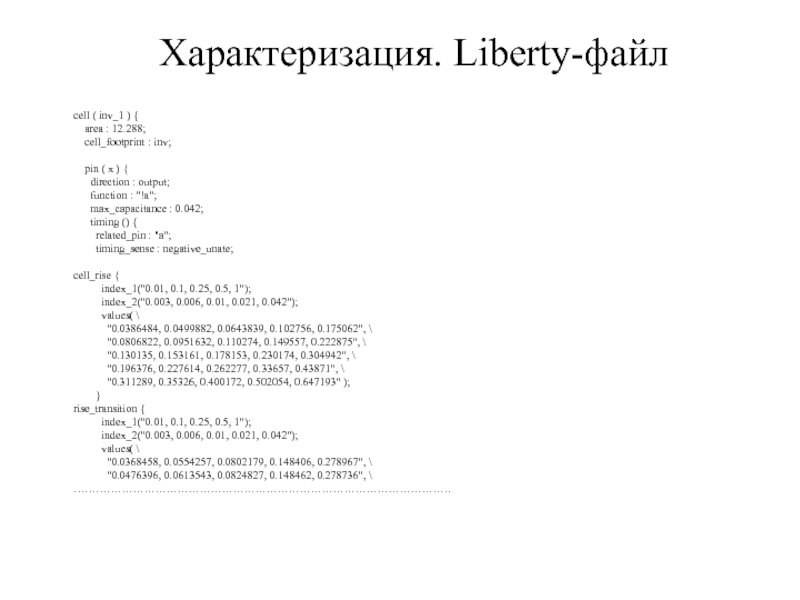

Слайд 15Характеризация. Liberty-файл

cell ( inv_1 ) {

area : 12.288;

cell_footprint : inv;

pin ( x ) {

direction : output;

function : "!a";

max_capacitance : 0.042;

timing () {

related_pin : "a";

timing_sense : negative_unate;

cell_rise {

index_1("0.01, 0.1, 0.25, 0.5, 1");

index_2("0.003, 0.006, 0.01, 0.021, 0.042");

values( \

"0.0386484, 0.0499882, 0.0643839, 0.102756, 0.175062", \

"0.0806822, 0.0951632, 0.110274, 0.149557, 0.222875", \

"0.130135, 0.153161, 0.178153, 0.230174, 0.304942", \

"0.196376, 0.227614, 0.262277, 0.33657, 0.43871", \

"0.311289, 0.35326, 0.400172, 0.502054, 0.647193" );

}

rise_transition {

index_1("0.01, 0.1, 0.25, 0.5, 1");

index_2("0.003, 0.006, 0.01, 0.021, 0.042");

values( \

"0.0368458, 0.0554257, 0.0802179, 0.148406, 0.278967", \

"0.0476396, 0.0613543, 0.0824827, 0.148462, 0.278736", \

…………………………………………………………………………………………