Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Организация системы ввода вывода

Содержание

- 1. Организация системы ввода вывода

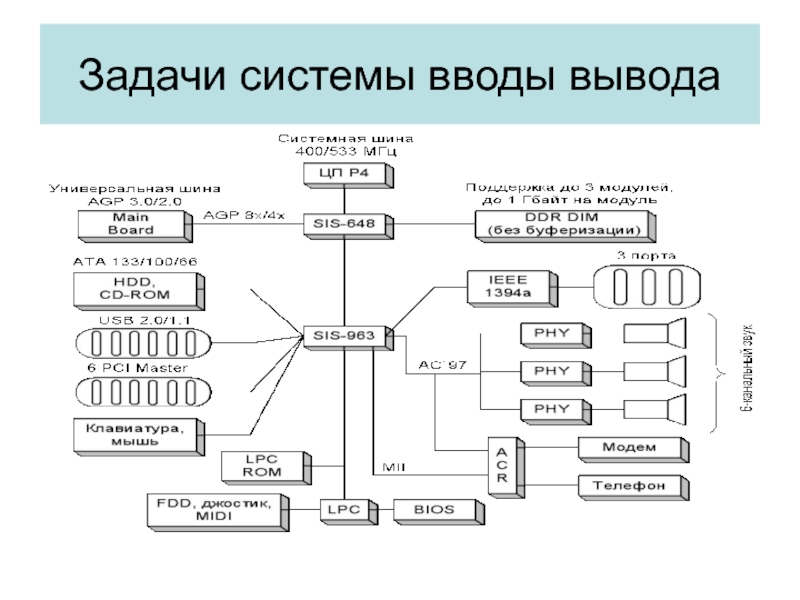

- 2. Задачи системы вводы вывода

- 3. Глобальные задачи СВВОбеспечение максимальной производительности вычислительной системы.Возможность

- 4. Элементы системы ввода -выводаКаналыПортыИнтерфейсыКонтроллерыДрайверыСпособы обменаПрограммныйПрямой доступК памятиЧерез системупрерыванийФизическаяорганизацияКонструктивыЛогическаяорганизацияBIOS

- 5. Типы ввода – вывода процессораИзолированный ввод-вывод.

- 6. Уровни обслуживания ввода-выводаПрограмма БлокуправленияСистемная таблицаБуфер данныхДрайвер1Драйвер NКонтроллер 1Контроллер NПУ 1ПУ NСистема ввода-выводаЛогическийуровеньФизическийуровеньАппаратураСВВПортПортилиилиУровень ОС

- 7. Функции драйверовПроверка готовности контроллера и ПУ к

- 8. Способы организации СВВПрограммный.На основе системы прерываний.Прямой доступ

- 9. Алгоритм программного ввода-вывода под управлением процессора1. Сформировать

- 10. Система прерыванийОбработка прерывания.Организация системы приоритетов через систему арбитража.

- 11. Диаграмма прерывания

- 12. Процедура обработки прерыванияИдентификация уровня запроса прерывания и

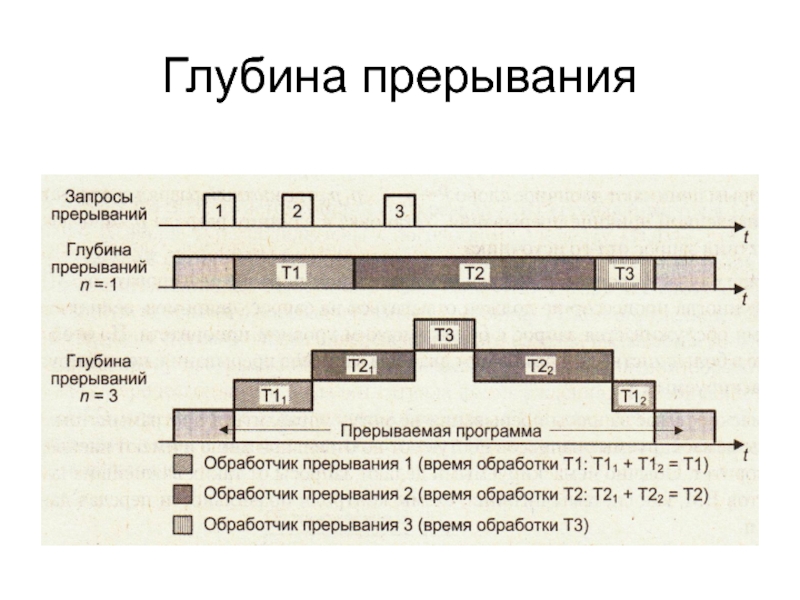

- 13. Характеристики систем прерыванияВремя реакции Тр.Время на переключение программ Тп=Тз+Тв.Эффективность прерывания.Глубина прерываний.

- 14. Глубина прерывания

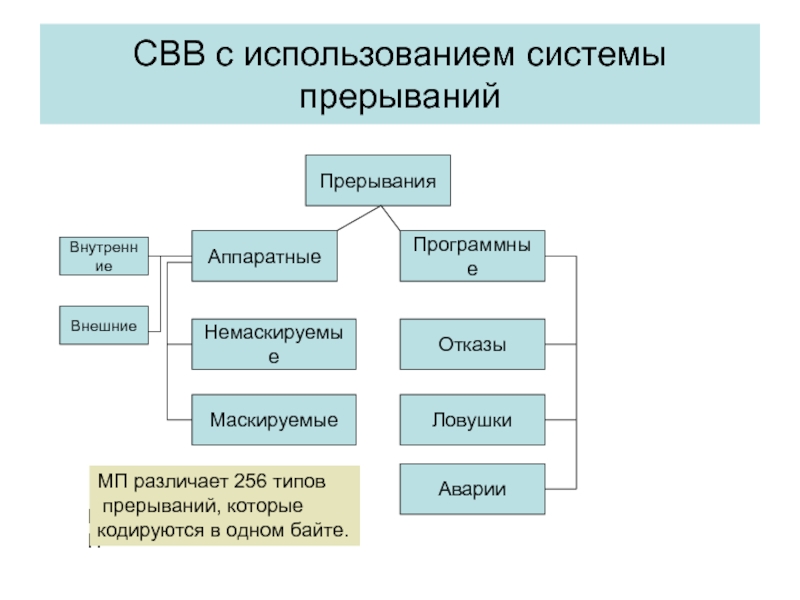

- 15. СВВ с использованием системы прерыванийПрерыванияАппаратныеПрограммныеНемаскируемыеМаскируемыеОтказыЛовушкиАварииМПМП различает 256 типов прерываний, которые кодируются в одном байте.ВнутренниеВнешние

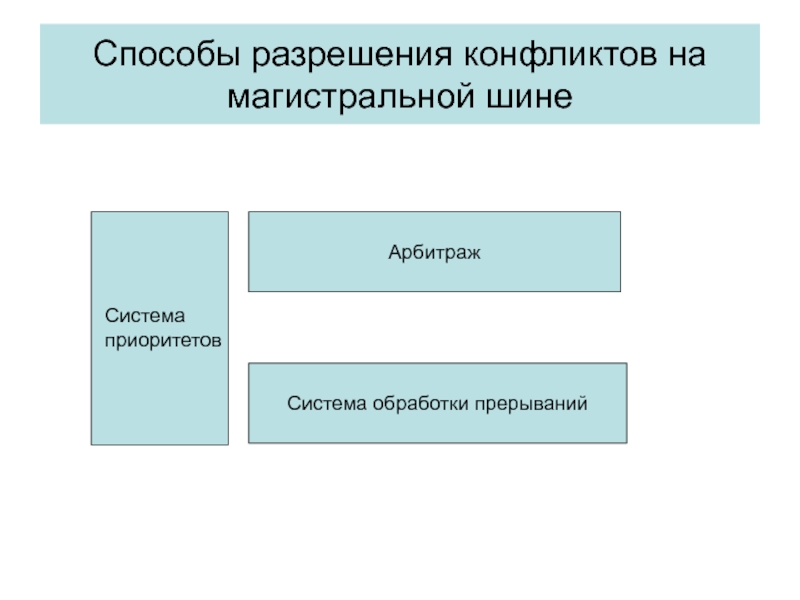

- 16. Способы разрешения конфликтов на магистральной шинеАрбитражСистема обработки прерыванийСистемаприоритетов

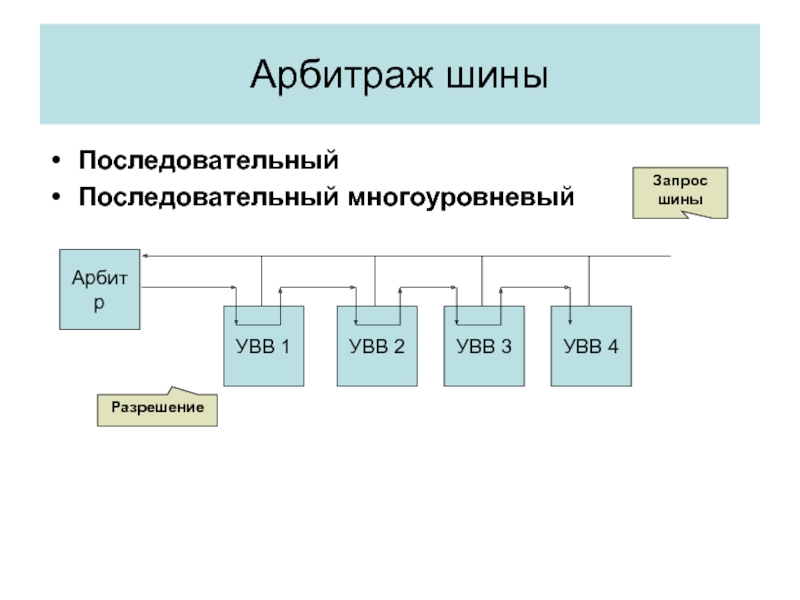

- 17. Арбитраж шиныПоследовательныйПоследовательный многоуровневыйАрбитрУВВ 1УВВ 2УВВ 3УВВ 4ЗапросшиныРазрешение

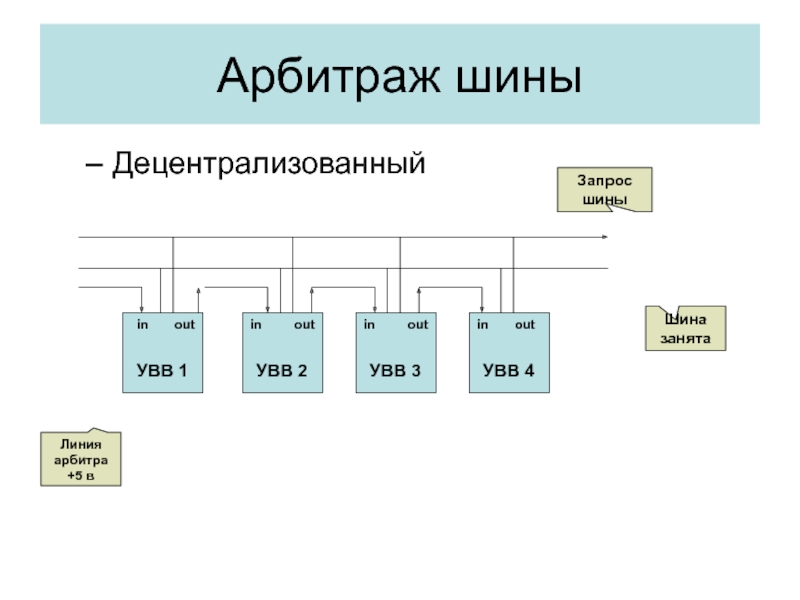

- 18. ДецентрализованныйАрбитраж шиныinoutinininoutoutoutЛиния арбитра +5 вУВВ 1УВВ 2УВВ 3УВВ 4ЗапросшиныШиназанята

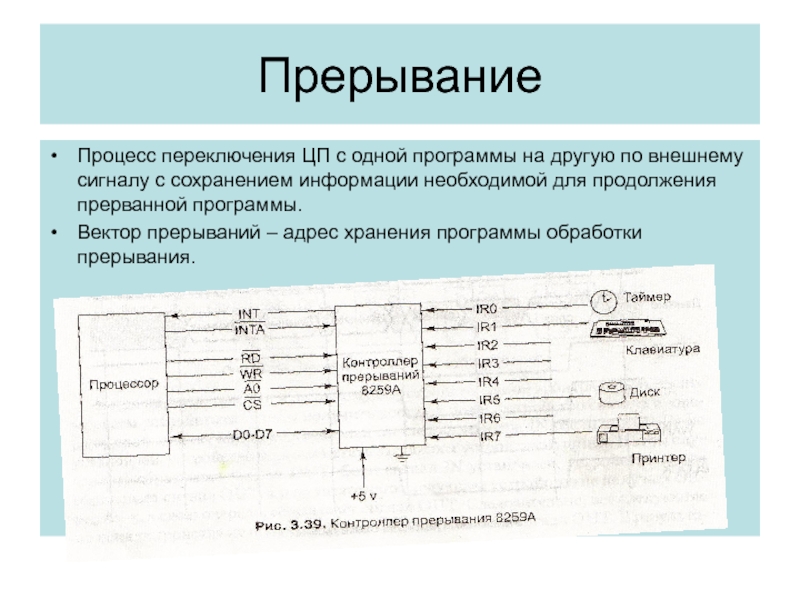

- 19. ПрерываниеПроцесс переключения ЦП с одной программы на

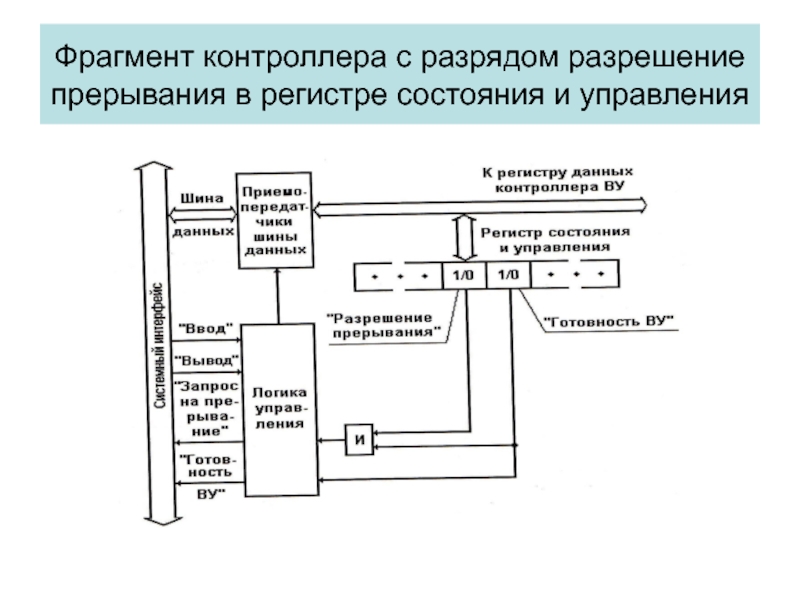

- 20. Фрагмент контроллера с разрядом разрешение прерывания в регистре состояния и управления

- 21. Вектор прерываний

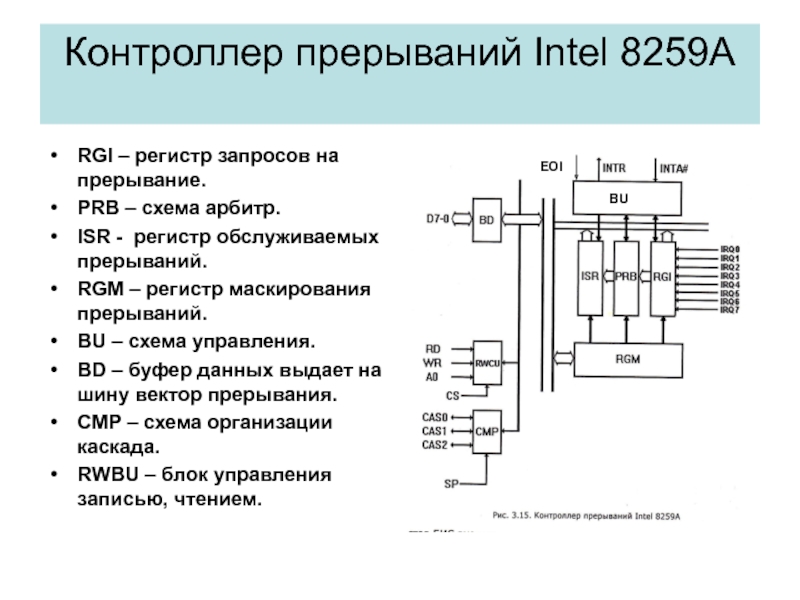

- 22. Контроллер прерываний Intel 8259ARGI – регистр запросов

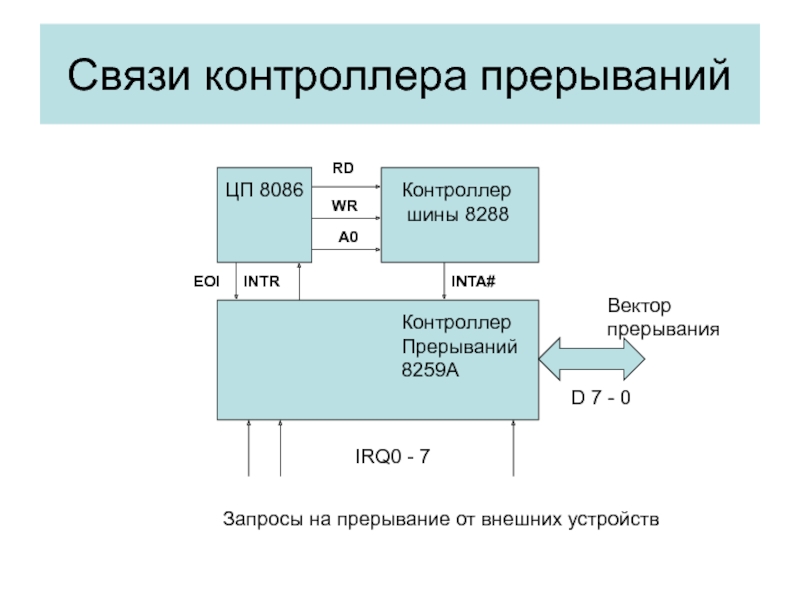

- 23. Связи контроллера прерыванийЦП 8086Контроллер шины 8288RDWRA0EOIINTRINTA#Контроллер Прерываний8259АD

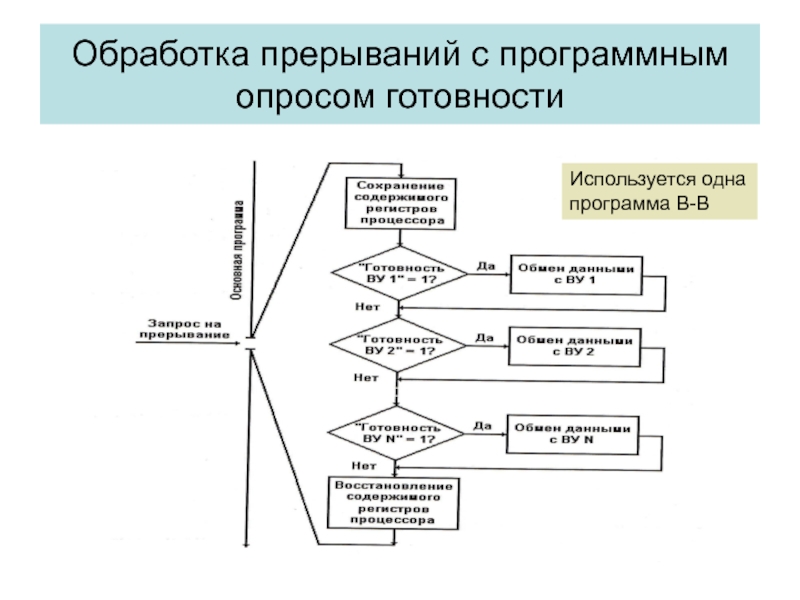

- 24. Обработка прерываний с программным опросом готовностиИспользуется однапрограмма В-В

- 25. Обобщенная схема контроллера

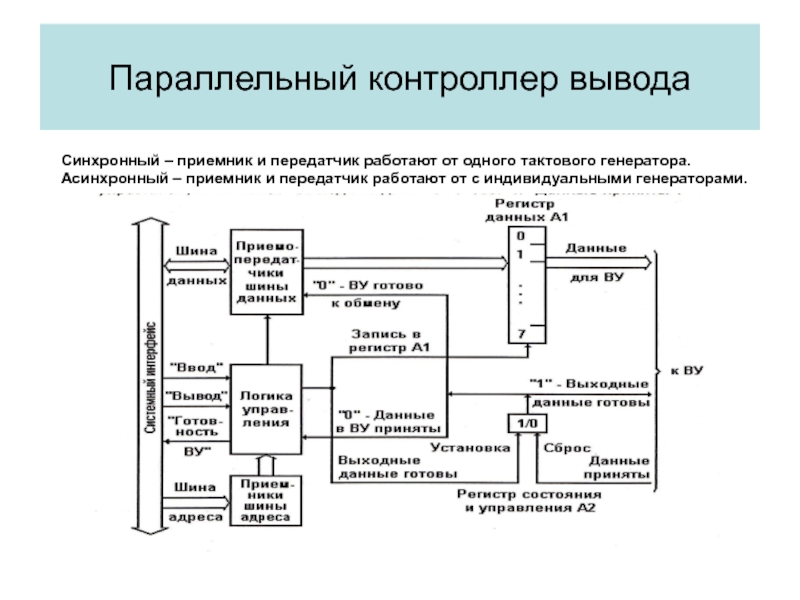

- 26. Параллельный контроллер выводаСинхронный – приемник и передатчик

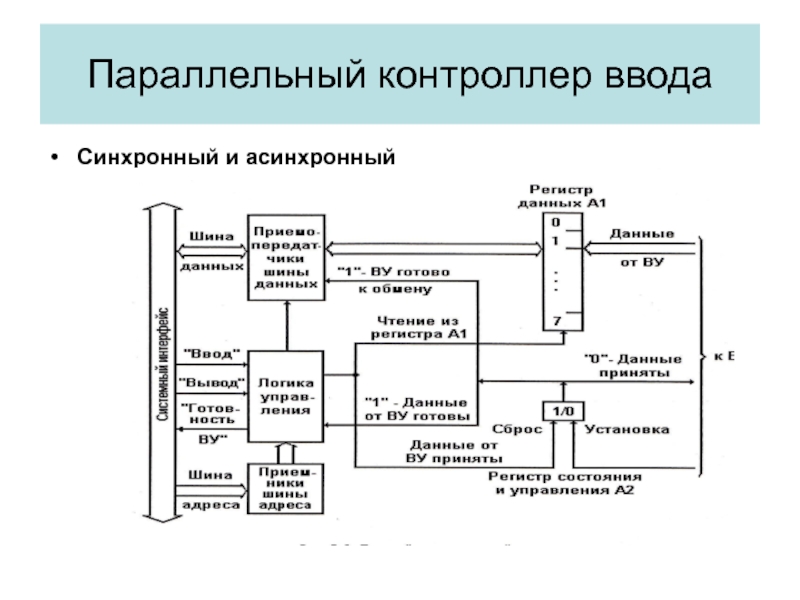

- 27. Синхронный и асинхронныйПараллельный контроллер ввода

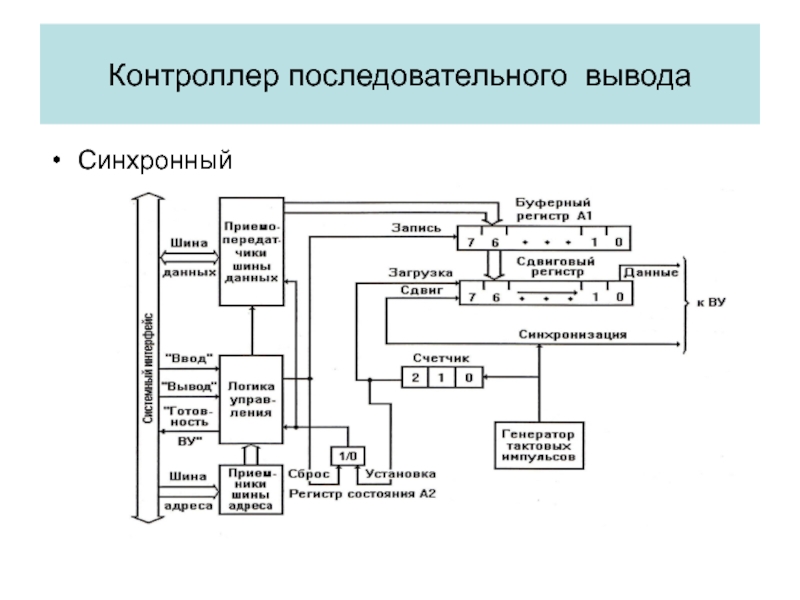

- 28. Контроллер последовательного выводаСинхронный

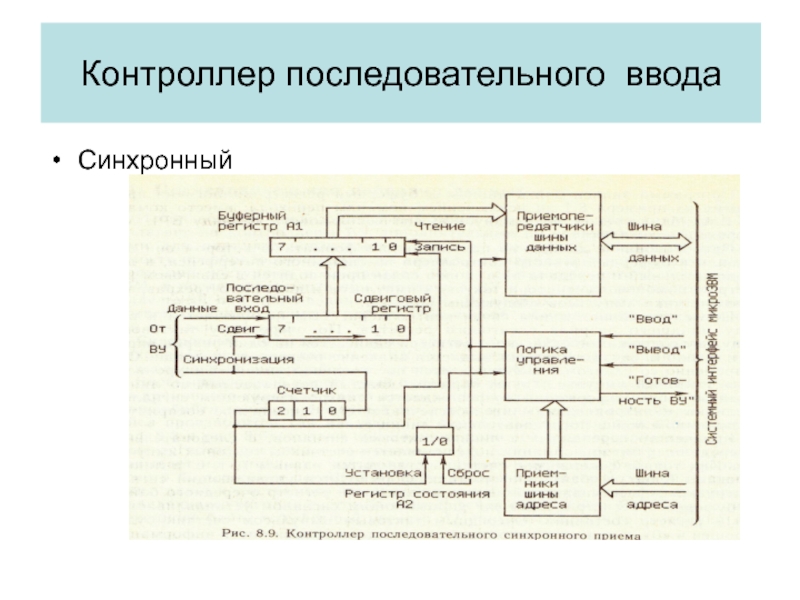

- 29. СинхронныйКонтроллер последовательного ввода

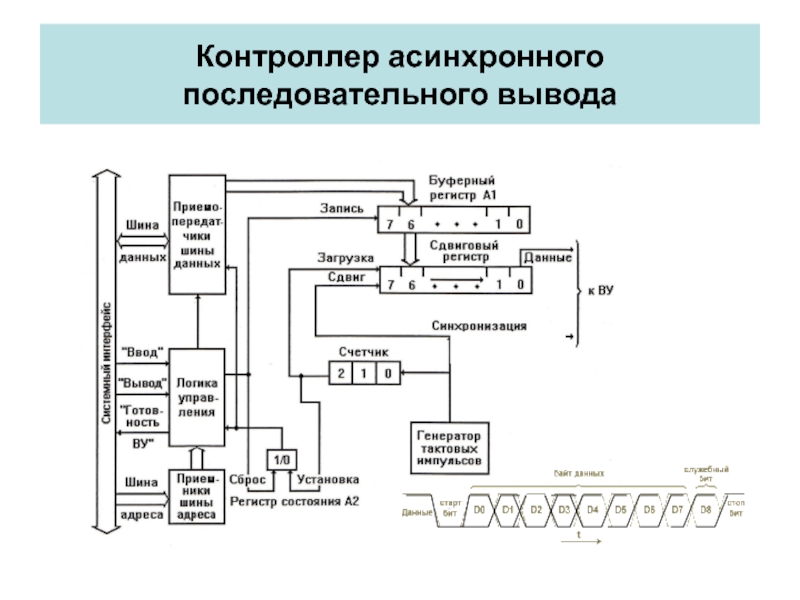

- 30. Контроллер асинхронного последовательного вывода

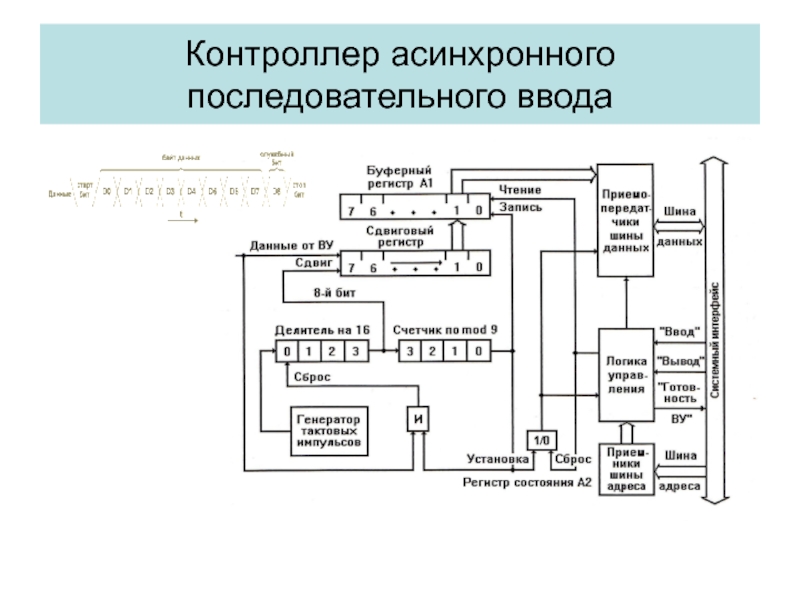

- 31. Контроллер асинхронного последовательного ввода

- 32. Контроллер ПДП может быть реализован как отдельное

- 33. Структура МПС с контроллером ПДПМПОЗУКонтроллерПДПВУШАШДШУHRQHRQ – запрос

- 34. Последовательность ПДП1. Принять запрос на ПДП от

- 35. Контроллер прямого доступа к памяти блок схема

- 36. Назначение блоков контроллера ПДПMR – регистр режима

- 37. Фрагмент контроллера прямого доступа к памяти

- 38. PIO- parallel Input-OutputМикросхема Intel 8255A8255AПорт А 8 разрядовПорт В 8 разрядовПорт С 8 разрядовD0-D7RESETRDWRA0-1CS2р8р

- 39. Программная модель UART(Universal Asynchronous Receiver Transmitter) МП

- 40. Программная модель UART микропроцессоров AVR фирмы ATMEL

- 41. Слайд 41

- 42. Организация программ для передачи данных UART AVRПрограммаMovsBufПрограмма

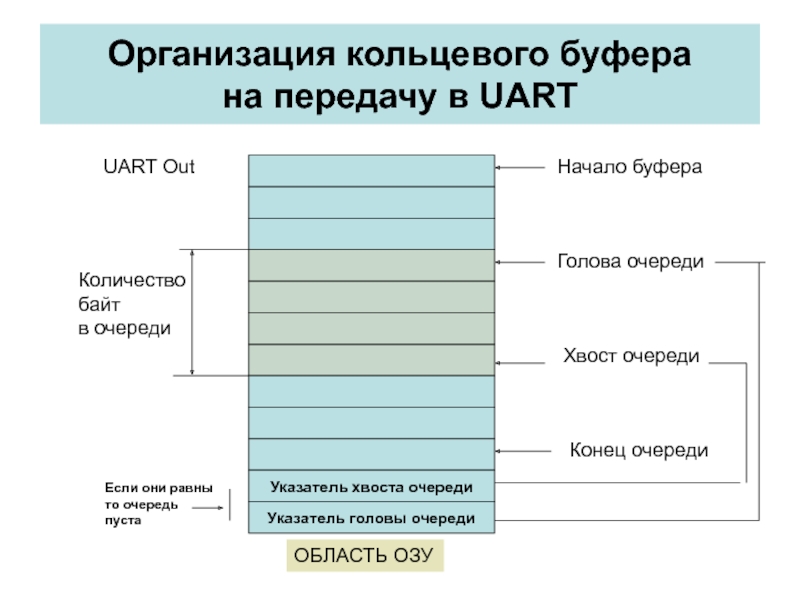

- 43. Организация кольцевого буфера на передачу в UARTУказатель

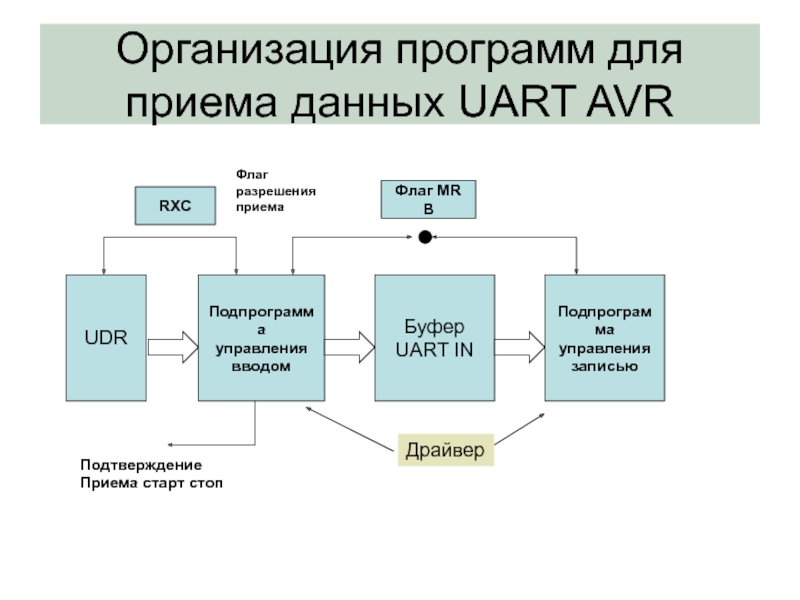

- 44. Организация программ для приема данных UART AVRПодпрограммауправлениявводомБуферUART INПодпрограммауправлениязаписьюUDRФлаг MR BПодтверждениеПриема старт стопRXCФлагразрешенияприемаДрайвер

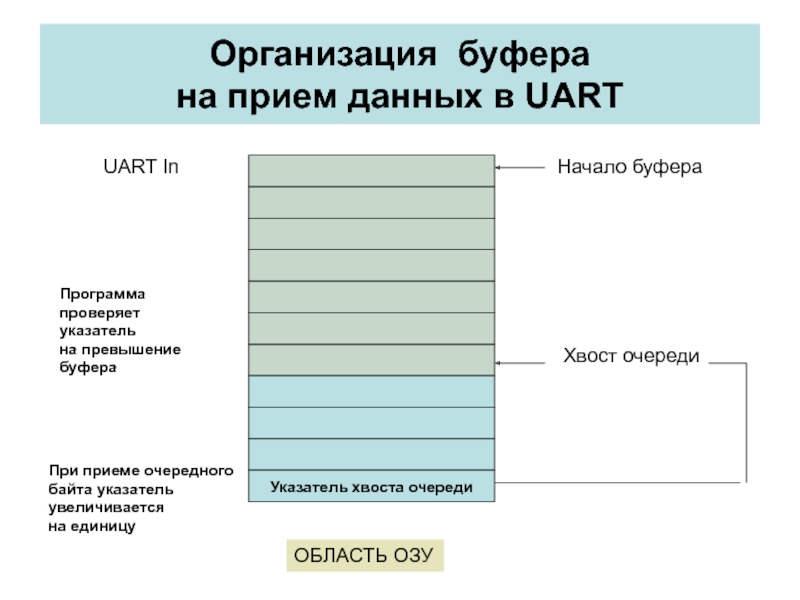

- 45. Организация буфера на прием данных в UARTУказатель

- 46. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Организация системы ввода вывода

Логическая организация СВВ, аппаратная организация СВВ, контроллеры:

параллельного В-В, последовательного В-В, ПДП. Микросхемы UART, PIO.

Слайд 3Глобальные задачи СВВ

Обеспечение максимальной производительности вычислительной системы.

Возможность изменения конфигурации периферийных

устройств (ПУ).

Возможность модифицировать ПУ , не изменяя ядро системы.

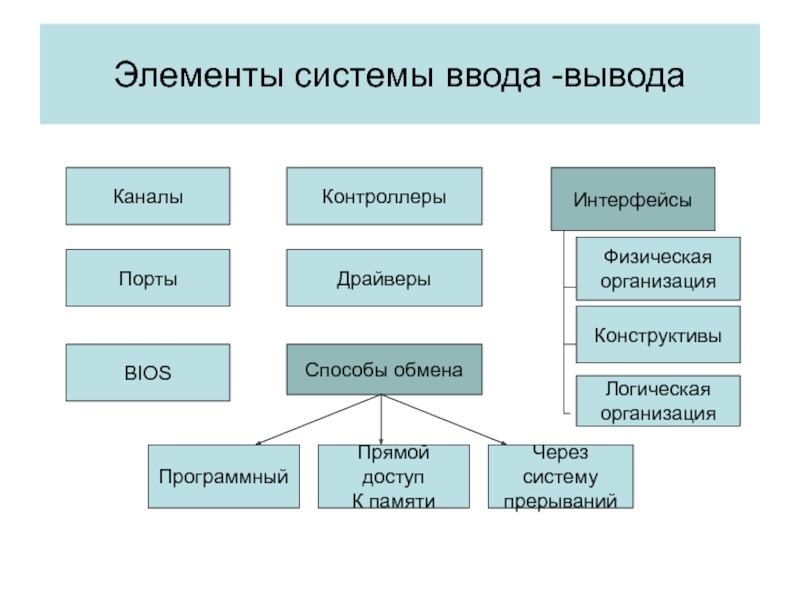

Слайд 4Элементы системы ввода -вывода

Каналы

Порты

Интерфейсы

Контроллеры

Драйверы

Способы обмена

Программный

Прямой доступ

К памяти

Через систему

прерываний

Физическая

организация

Конструктивы

Логическая

организация

BIOS

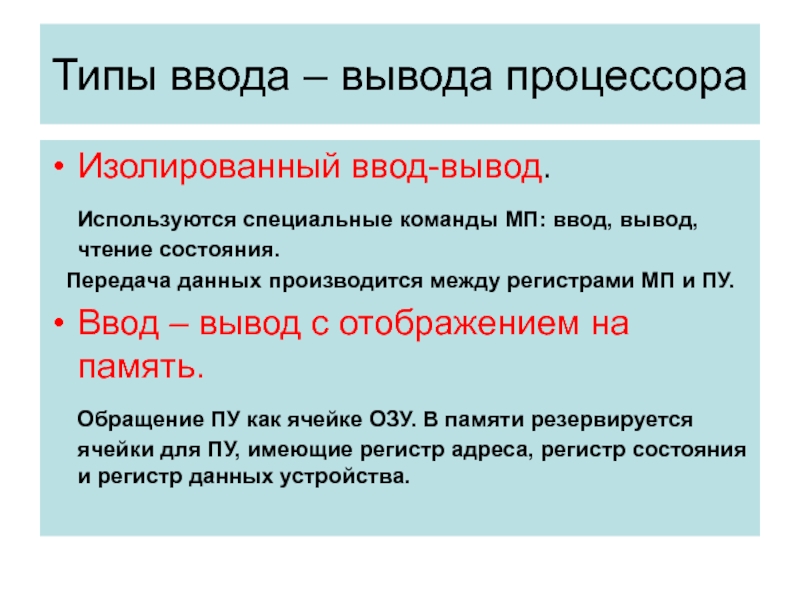

Слайд 5Типы ввода – вывода процессора

Изолированный ввод-вывод.

Используются специальные команды

МП: ввод, вывод, чтение состояния.

Передача данных производится между

регистрами МП и ПУ.Ввод – вывод с отображением на память.

Обращение ПУ как ячейке ОЗУ. В памяти резервируется ячейки для ПУ, имеющие регистр адреса, регистр состояния и регистр данных устройства.

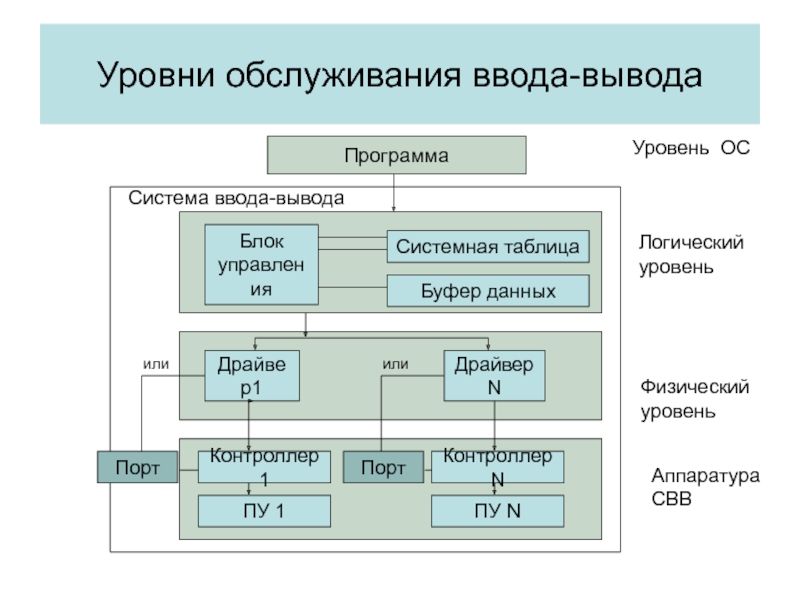

Слайд 6Уровни обслуживания ввода-вывода

Программа

Блок

управления

Системная таблица

Буфер данных

Драйвер1

Драйвер N

Контроллер 1

Контроллер N

ПУ 1

ПУ

N

Система ввода-вывода

Логический

уровень

Физический

уровень

Аппаратура

СВВ

Порт

Порт

или

или

Уровень ОС

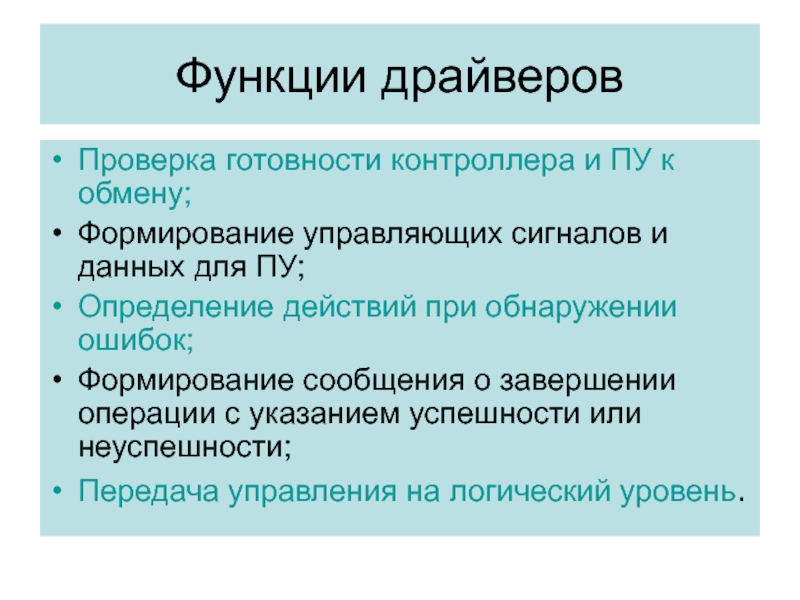

Слайд 7Функции драйверов

Проверка готовности контроллера и ПУ к обмену;

Формирование управляющих сигналов

и данных для ПУ;

Определение действий при обнаружении ошибок;

Формирование сообщения о

завершении операции с указанием успешности или неуспешности;Передача управления на логический уровень.

Слайд 8Способы организации СВВ

Программный.

На основе системы прерываний.

Прямой доступ к памяти.

Коммутаторный.

Без адресный

«точка –точка».

Они могут комбинироваться при конкретной реализации системы.

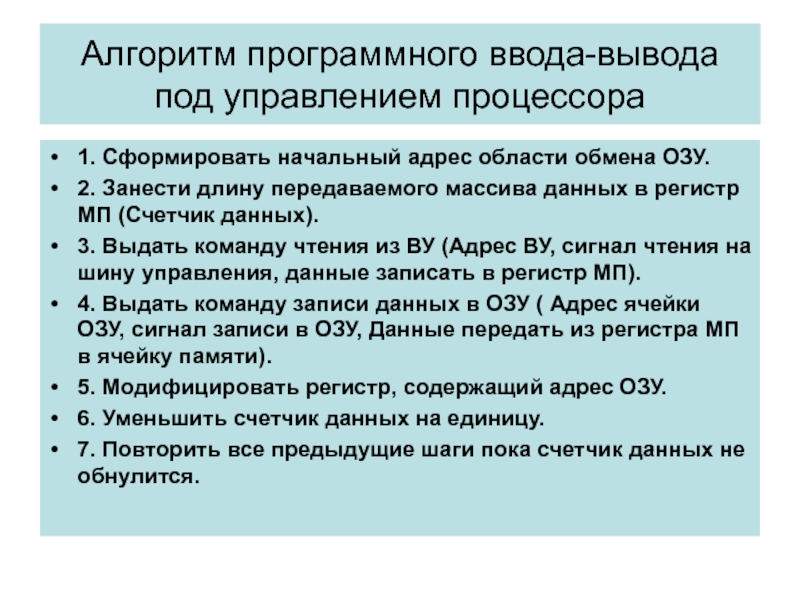

Слайд 9Алгоритм программного ввода-вывода под управлением процессора

1. Сформировать начальный адрес области

обмена ОЗУ.

2. Занести длину передаваемого массива данных в регистр МП

(Счетчик данных).3. Выдать команду чтения из ВУ (Адрес ВУ, сигнал чтения на шину управления, данные записать в регистр МП).

4. Выдать команду записи данных в ОЗУ ( Адрес ячейки ОЗУ, сигнал записи в ОЗУ, Данные передать из регистра МП в ячейку памяти).

5. Модифицировать регистр, содержащий адрес ОЗУ.

6. Уменьшить счетчик данных на единицу.

7. Повторить все предыдущие шаги пока счетчик данных не обнулится.

Слайд 10Система прерываний

Обработка прерывания.

Организация системы приоритетов через систему арбитража.

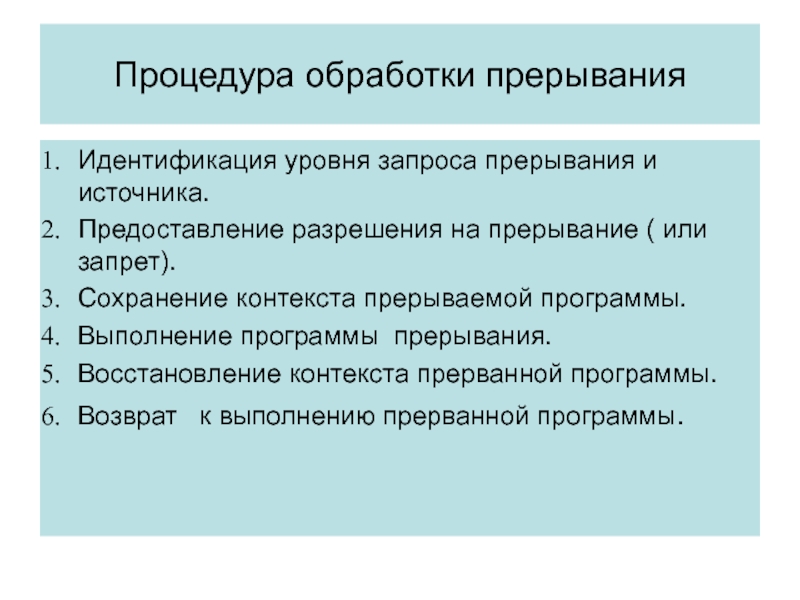

Слайд 12Процедура обработки прерывания

Идентификация уровня запроса прерывания и источника.

Предоставление разрешения на

прерывание ( или запрет).

Сохранение контекста прерываемой программы.

Выполнение программы прерывания.

Восстановление контекста

прерванной программы.Возврат к выполнению прерванной программы.

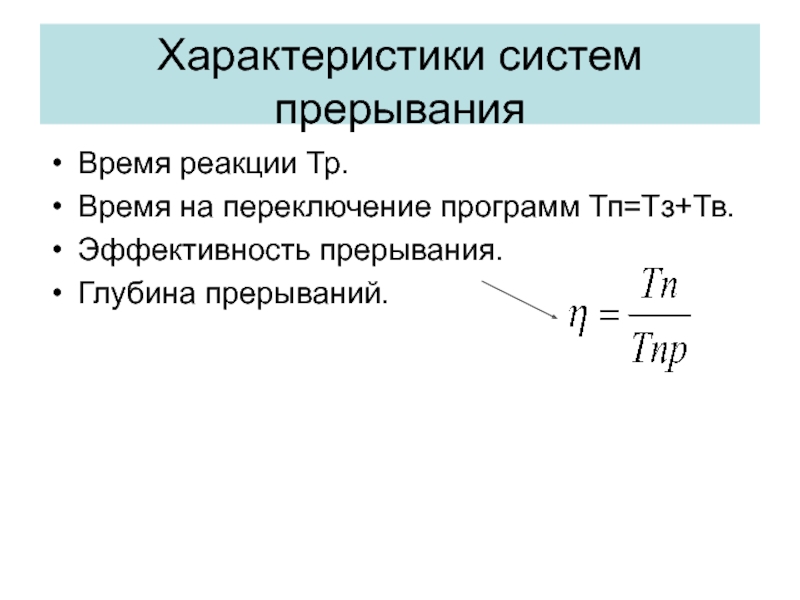

Слайд 13Характеристики систем прерывания

Время реакции Тр.

Время на переключение программ Тп=Тз+Тв.

Эффективность прерывания.

Глубина

прерываний.

Слайд 15СВВ с использованием системы прерываний

Прерывания

Аппаратные

Программные

Немаскируемые

Маскируемые

Отказы

Ловушки

Аварии

МП

МП различает 256 типов

прерываний, которые

кодируются в одном байте.

Внутренние

Внешние

Слайд 16Способы разрешения конфликтов на магистральной шине

Арбитраж

Система обработки прерываний

Система

приоритетов

Слайд 17Арбитраж шины

Последовательный

Последовательный многоуровневый

Арбитр

УВВ 1

УВВ 2

УВВ 3

УВВ 4

Запрос

шины

Разрешение

Слайд 18Децентрализованный

Арбитраж шины

in

out

in

in

in

out

out

out

Линия арбитра +5 в

УВВ 1

УВВ 2

УВВ 3

УВВ 4

Запрос

шины

Шина

занята

Слайд 19Прерывание

Процесс переключения ЦП с одной программы на другую по внешнему

сигналу с сохранением информации необходимой для продолжения прерванной программы.

Вектор прерываний

– адрес хранения программы обработки прерывания.Слайд 22Контроллер прерываний Intel 8259A

RGI – регистр запросов на прерывание.

PRB –

схема арбитр.

ISR - регистр обслуживаемых прерываний.

RGM – регистр маскирования прерываний.

BU

– схема управления.BD – буфер данных выдает на шину вектор прерывания.

CMP – схема организации каскада.

RWBU – блок управления записью, чтением.

BU

EOI

Слайд 23Связи контроллера прерываний

ЦП 8086

Контроллер

шины 8288

RD

WR

A0

EOI

INTR

INTA#

Контроллер

Прерываний

8259А

D 7 - 0

IRQ0

- 7

Запросы на прерывание от внешних устройств

Вектор

прерывания

Слайд 26Параллельный контроллер вывода

Синхронный – приемник и передатчик работают от одного

тактового генератора.

Асинхронный – приемник и передатчик работают от с индивидуальными

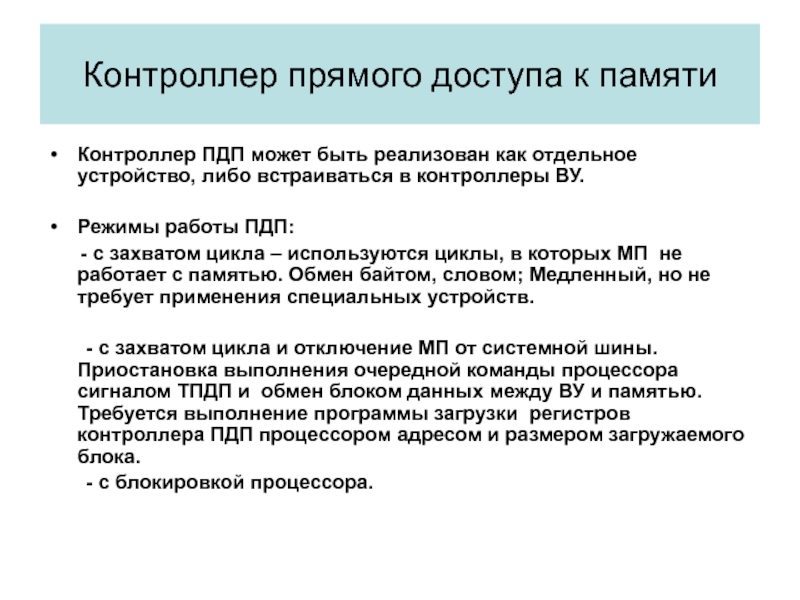

генераторами.Слайд 32Контроллер ПДП может быть реализован как отдельное устройство, либо встраиваться

в контроллеры ВУ.

Режимы работы ПДП:

- с захватом

цикла – используются циклы, в которых МП не работает с памятью. Обмен байтом, словом; Медленный, но не требует применения специальных устройств.- с захватом цикла и отключение МП от системной шины. Приостановка выполнения очередной команды процессора сигналом ТПДП и обмен блоком данных между ВУ и памятью. Требуется выполнение программы загрузки регистров контроллера ПДП процессором адресом и размером загружаемого блока.

- с блокировкой процессора.

Контроллер прямого доступа к памяти

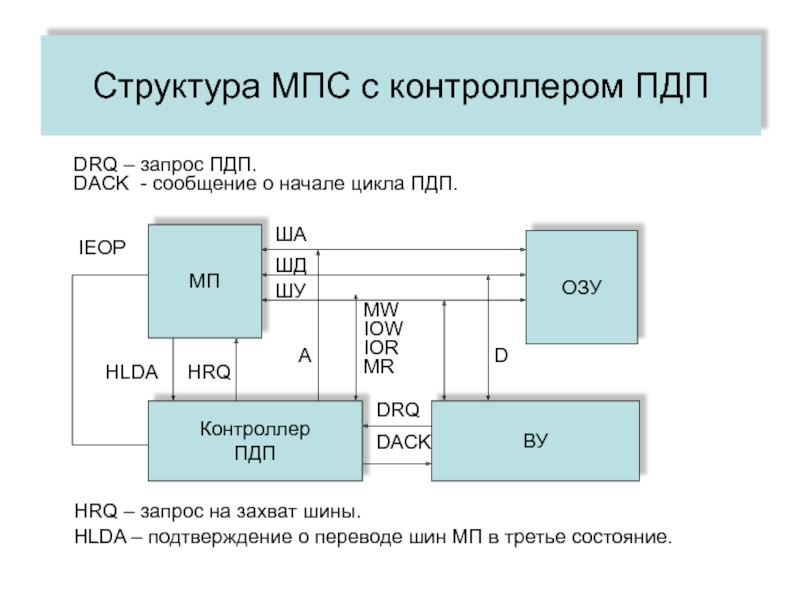

Слайд 33Структура МПС с контроллером ПДП

МП

ОЗУ

Контроллер

ПДП

ВУ

ША

ШД

ШУ

HRQ

HRQ – запрос на захват шины.

HLDA

HLDA

– подтверждение о переводе шин МП в третье состояние.

DRQ

DACK

DRQ –

запрос ПДП.DACK - сообщение о начале цикла ПДП.

MR

IOW

IOR

A

D

MW

IEOP

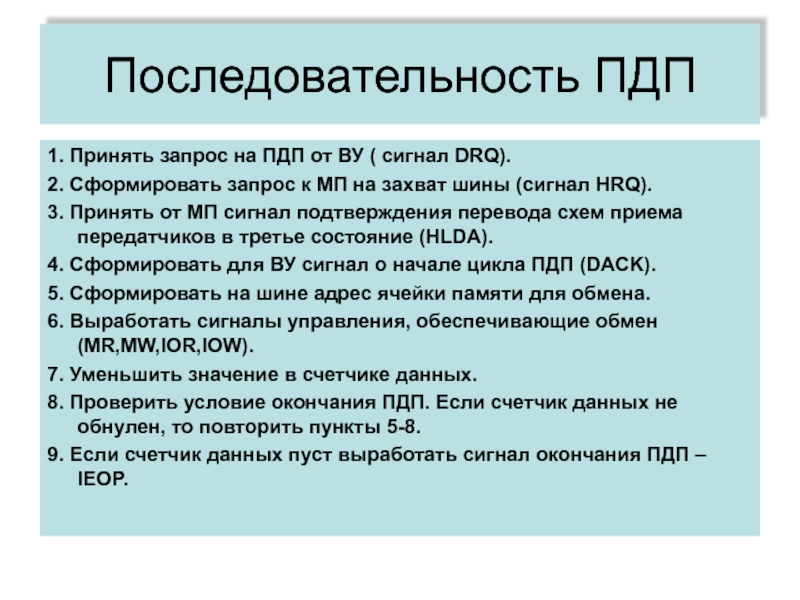

Слайд 34Последовательность ПДП

1. Принять запрос на ПДП от ВУ ( сигнал

DRQ).

2. Сформировать запрос к МП на захват шины (сигнал HRQ).

3.

Принять от МП сигнал подтверждения перевода схем приема передатчиков в третье состояние (HLDA).4. Сформировать для ВУ сигнал о начале цикла ПДП (DACK).

5. Сформировать на шине адрес ячейки памяти для обмена.

6. Выработать сигналы управления, обеспечивающие обмен (MR,MW,IOR,IOW).

7. Уменьшить значение в счетчике данных.

8. Проверить условие окончания ПДП. Если счетчик данных не обнулен, то повторить пункты 5-8.

9. Если счетчик данных пуст выработать сигнал окончания ПДП – IEOP.

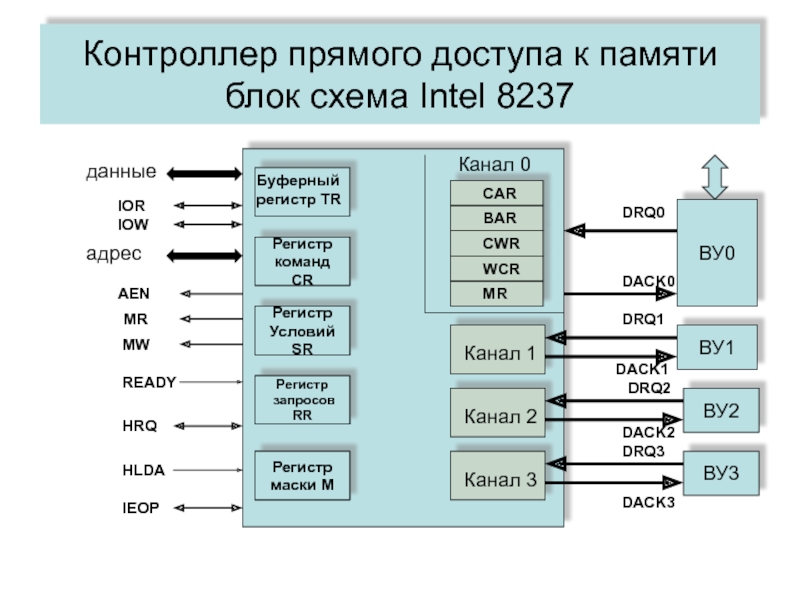

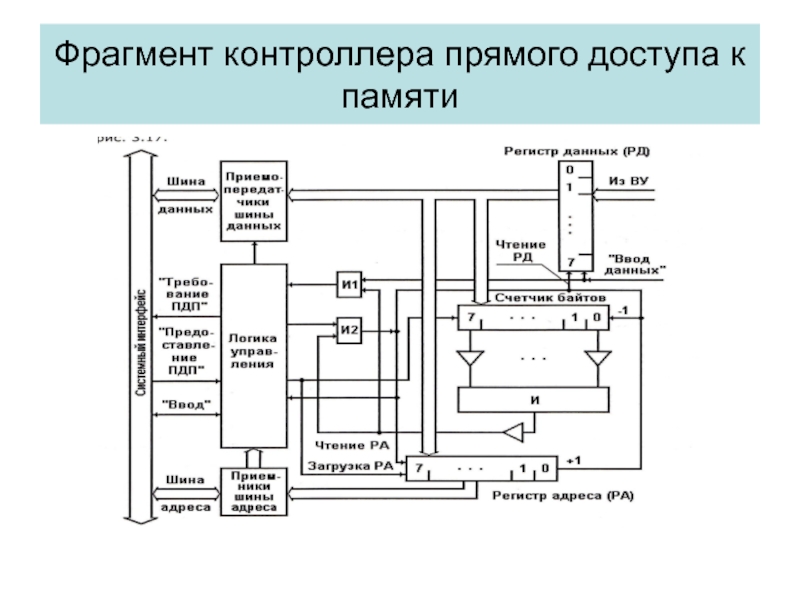

Слайд 35Контроллер прямого доступа к памяти

блок схема Intel 8237

CAR

BAR

CWR

WCR

MR

Канал 0

Канал 1

Канал

2

Канал 3

DRQ0

DRQ1

DRQ2

DRQ3

DACK0

DACK1

DACK2

DACK3

Буферный

регистр TR

Регистр

команд CR

Регистр

Условий SR

Регистр

запросов RR

Регистр

маски M

данные

адрес

IOR

IOW

AEN

MR

MW

READY

HRQ

HLDA

IEOP

ВУ0

ВУ1

ВУ2

ВУ3

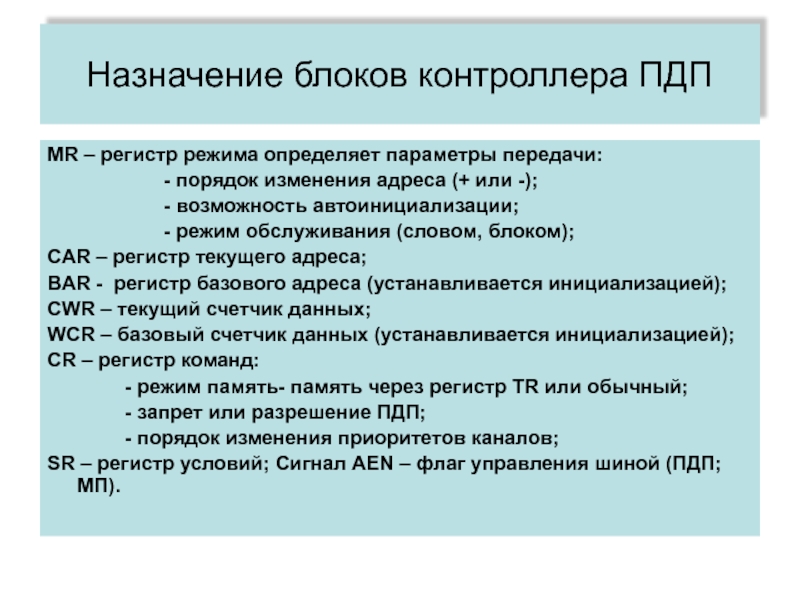

Слайд 36Назначение блоков контроллера ПДП

MR – регистр режима определяет параметры передачи:

- порядок изменения адреса (+ или -);

- возможность автоинициализации;

- режим обслуживания (словом, блоком);

CAR – регистр текущего адреса;

BAR - регистр базового адреса (устанавливается инициализацией);

CWR – текущий счетчик данных;

WCR – базовый счетчик данных (устанавливается инициализацией);

CR – регистр команд:

- режим память- память через регистр TR или обычный;

- запрет или разрешение ПДП;

- порядок изменения приоритетов каналов;

SR – регистр условий; Сигнал AEN – флаг управления шиной (ПДП;МП).

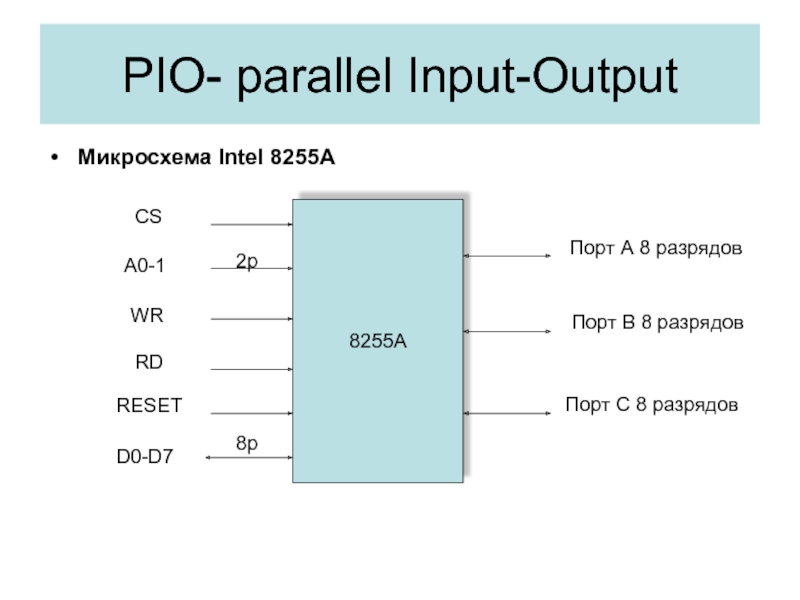

Слайд 38PIO- parallel Input-Output

Микросхема Intel 8255A

8255A

Порт А 8 разрядов

Порт В 8

разрядов

Порт С 8 разрядов

D0-D7

RESET

RD

WR

A0-1

CS

2р

8р

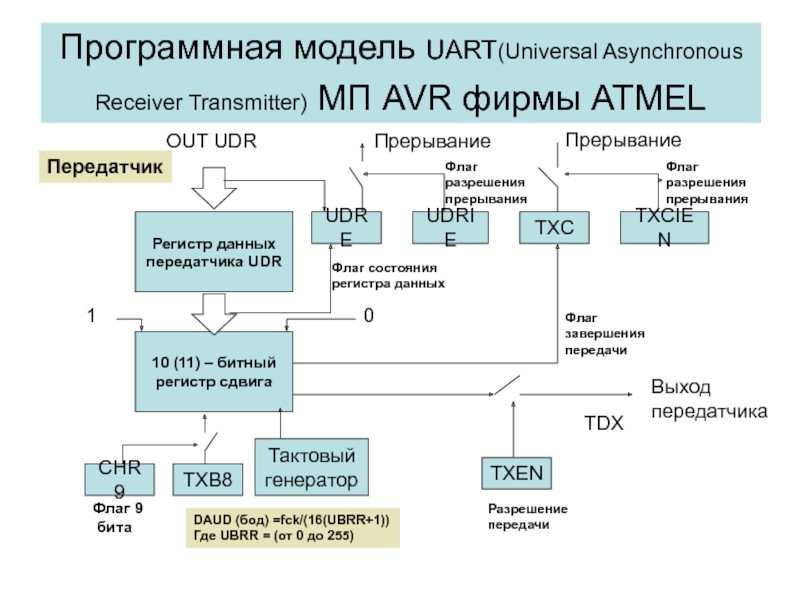

Слайд 39Программная модель UART(Universal Asynchronous Receiver Transmitter) МП AVR фирмы ATMEL

Регистр данных

передатчика UDR

10 (11) – битный

регистр сдвига

Тактовый

генератор

UDRIE

UDRE

TXCIEN

TXC

TXB8

CHR9

TXEN

OUT UDR

Флаг 9

бита

TDX

Разрешение

передачи

Прерывание

Прерывание

1

0

Флаг

состояниярегистра данных

Флаг

завершения

передачи

Флаг

разрешения

прерывания

Флаг

разрешения

прерывания

Выход

передатчика

Передатчик

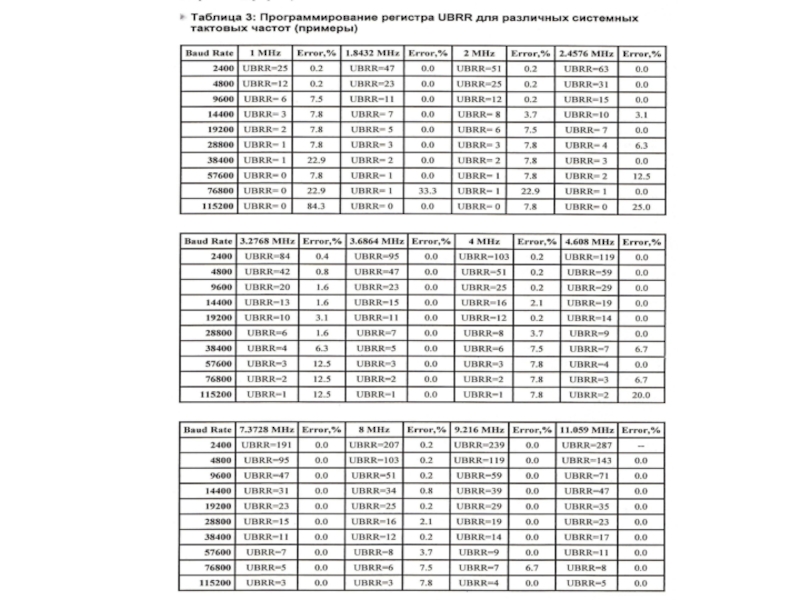

DAUD (бод) =fck/(16(UBRR+1))

Где UBRR = (от 0 до 255)

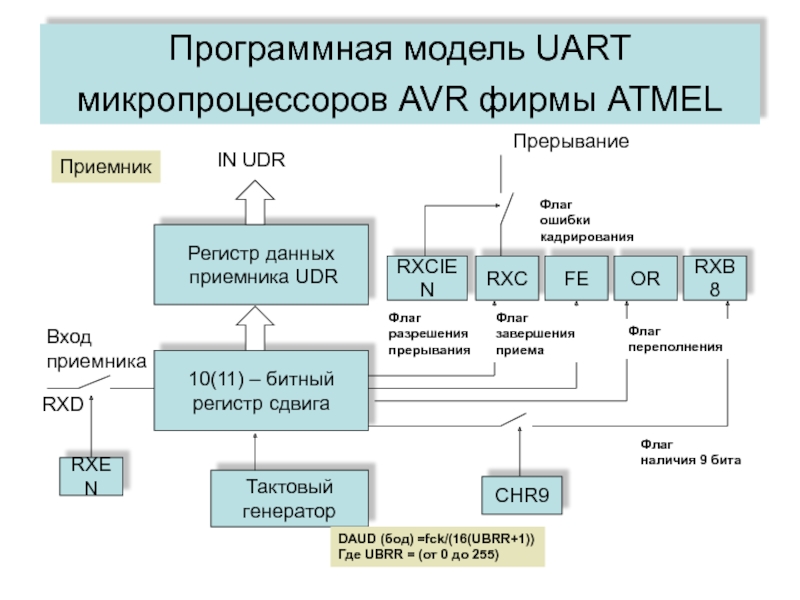

Слайд 40Программная модель UART микропроцессоров AVR фирмы ATMEL

Регистр данных

приемника

UDR

10(11) – битный

регистр сдвига

Тактовый

генератор

RXCIEN

RXC

FE

OR

RXB8

RXEN

RXD

Вход

приемника

CHR9

Прерывание

IN UDR

Флаг

завершения

приема

Флаг

разрешения

прерывания

Флаг

ошибки

кадрирования

Флаг

переполнения

Флаг

наличия 9 бита

Приемник

DAUD (бод)

=fck/(16(UBRR+1))Где UBRR = (от 0 до 255)

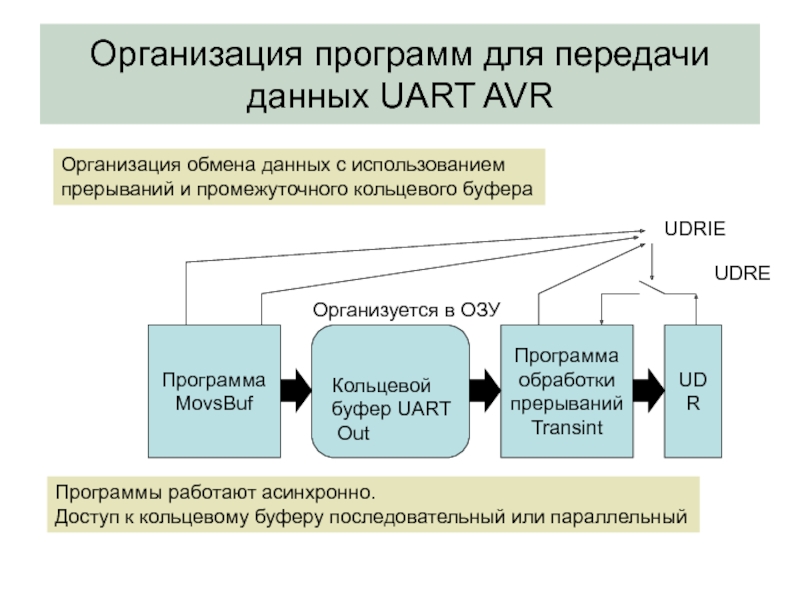

Слайд 42Организация программ для передачи данных UART AVR

Программа

MovsBuf

Программа

обработки

прерываний

Transint

UDR

Организация обмена данных

с использованием

прерываний и промежуточного кольцевого буфера

Кольцевой

буфер UART

Out

UDRIE

UDRE

Программы

работают асинхронно.Доступ к кольцевому буферу последовательный или параллельный

Организуется в ОЗУ