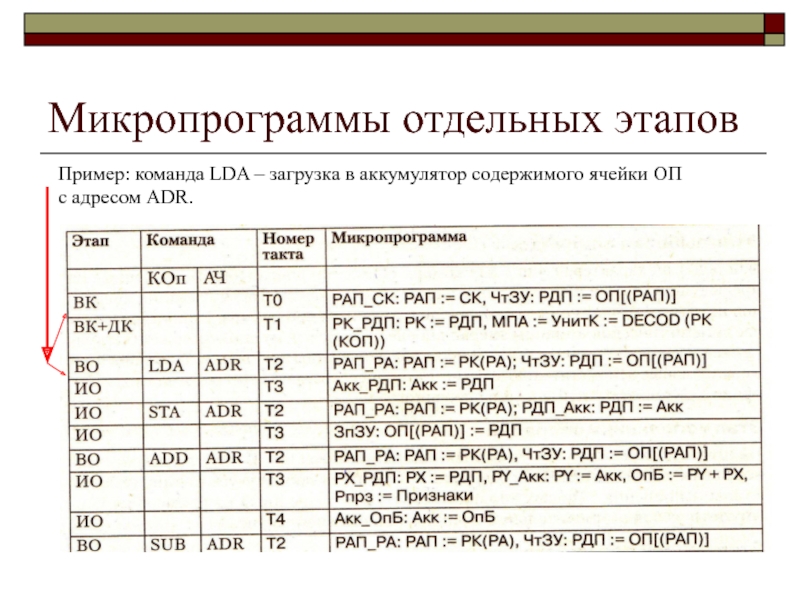

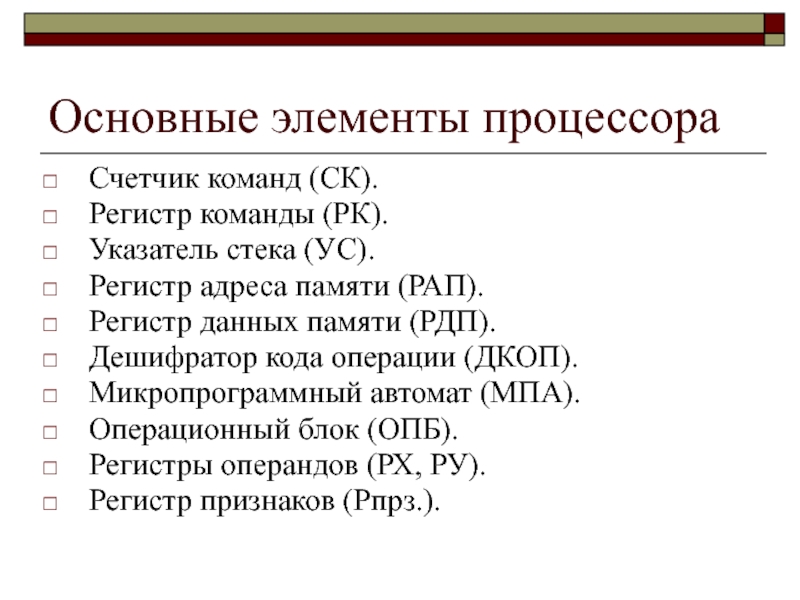

памяти (РАП).

Регистр данных памяти (РДП).

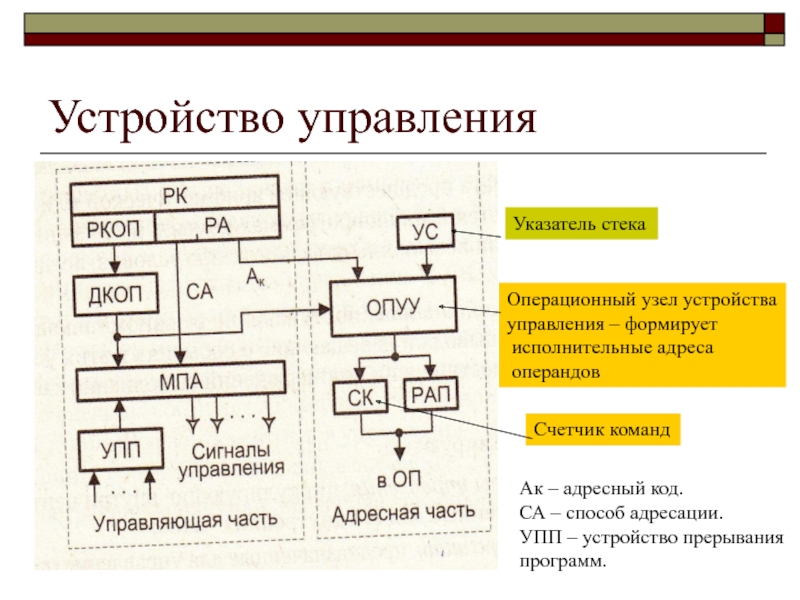

Дешифратор кода операции (ДКОП).

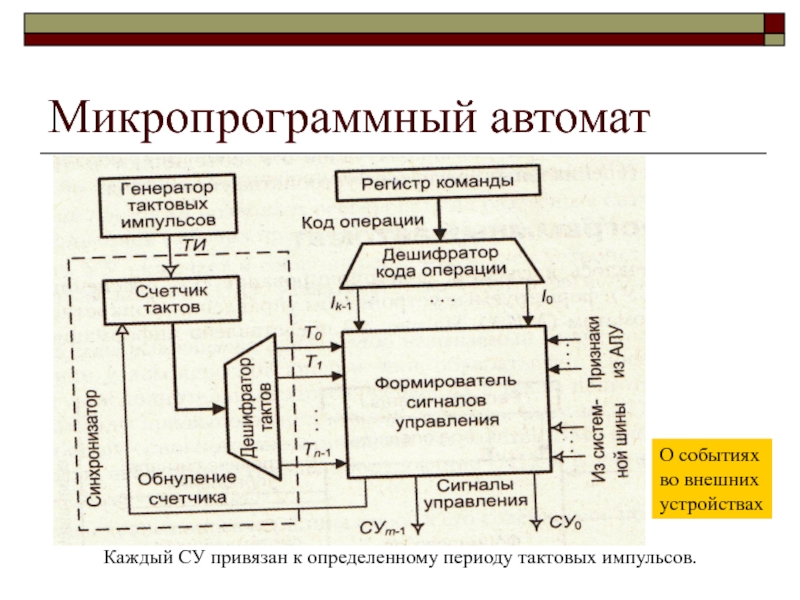

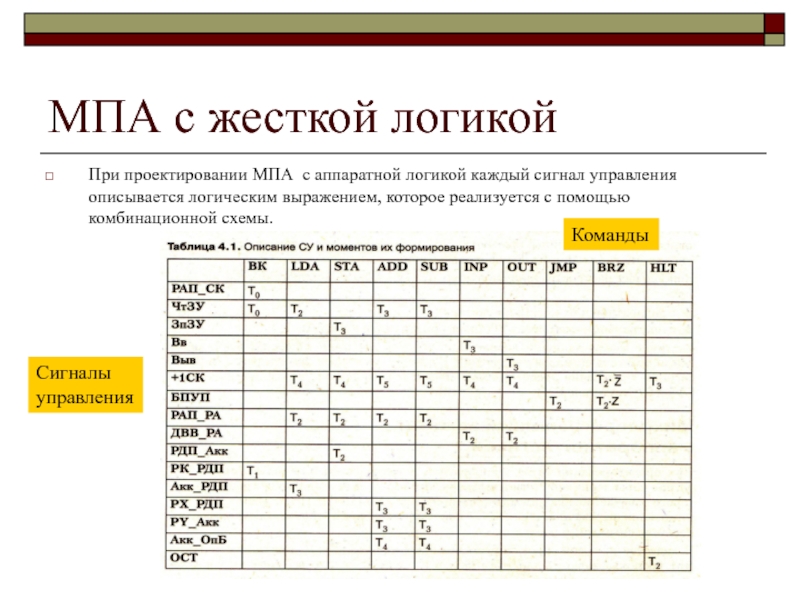

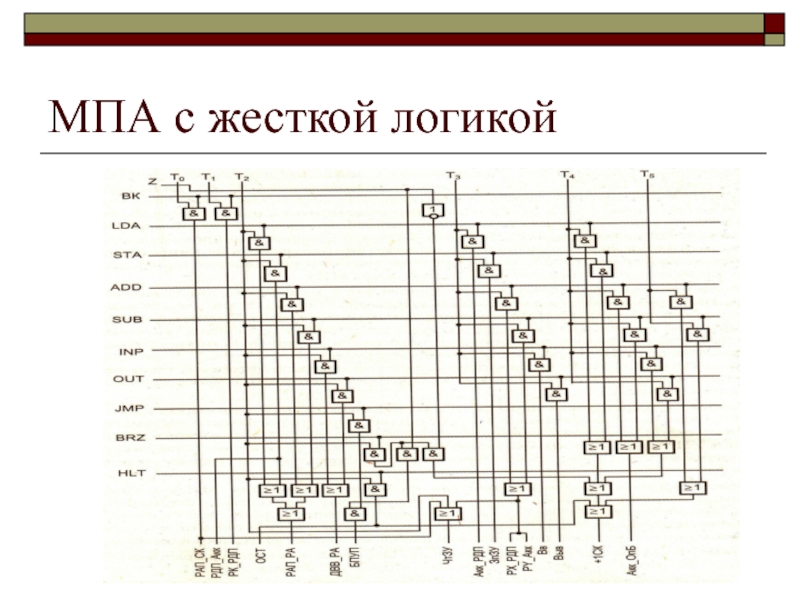

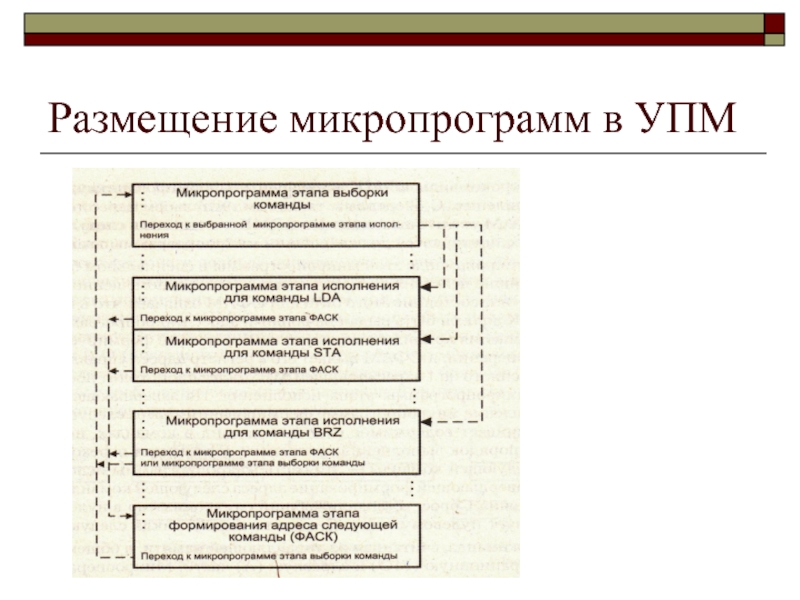

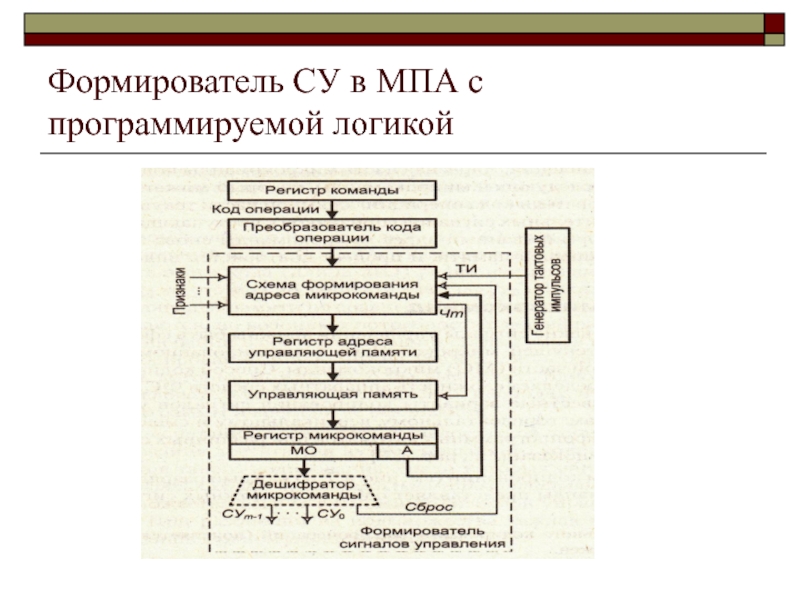

Микропрограммный автомат (МПА).

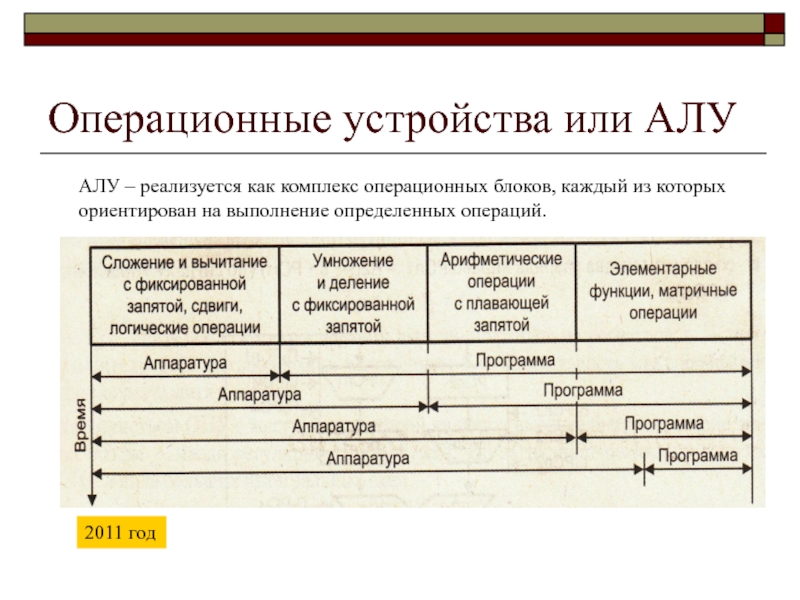

Операционный

блок (ОПБ).Регистры операндов (РХ, РУ).

Регистр признаков (Рпрз.).

![Процессор. Функциональная организация Стандартный цикл процессораВыборка команды РК=ОП[(CК)].(ВК).Декодирование команды (ДК): Определяются следующие действия. Стандартный цикл процессораВыборка команды РК=ОП[(CК)].(ВК).Декодирование команды (ДК): Определяются следующие действия. Откуда](/img/thumbs/1f4f0d169fa4059274067668852a2e89-800x.jpg)