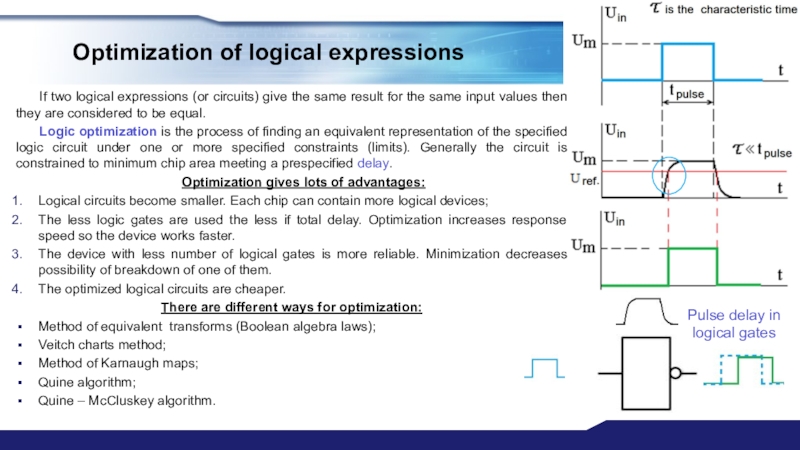

the same result for the same input values then they

are considered to be equal.

Logic optimization is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints (limits). Generally the circuit is constrained to minimum chip area meeting a prespecified delay.

Optimization gives lots of advantages:

Logical circuits become smaller. Each chip can contain more logical devices;

The less logic gates are used the less if total delay. Optimization increases response speed so the device works faster.

The device with less number of logical gates is more reliable. Minimization decreases possibility of breakdown of one of them.

The optimized logical circuits are cheaper.

There are different ways for optimization:

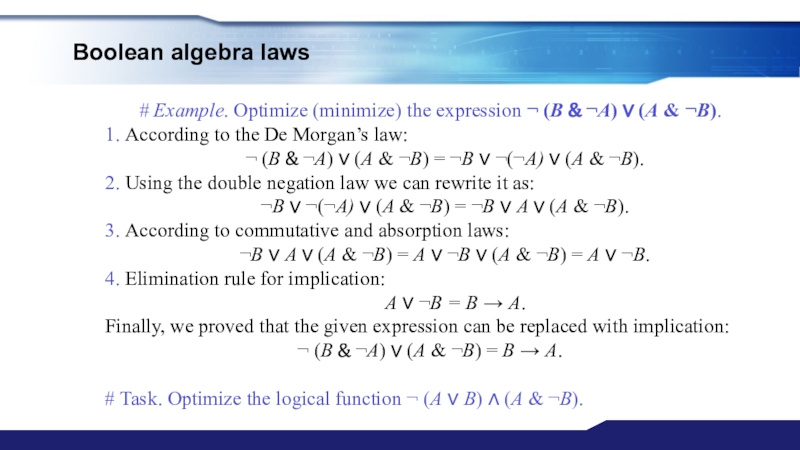

Method of equivalent transforms (Boolean algebra laws);

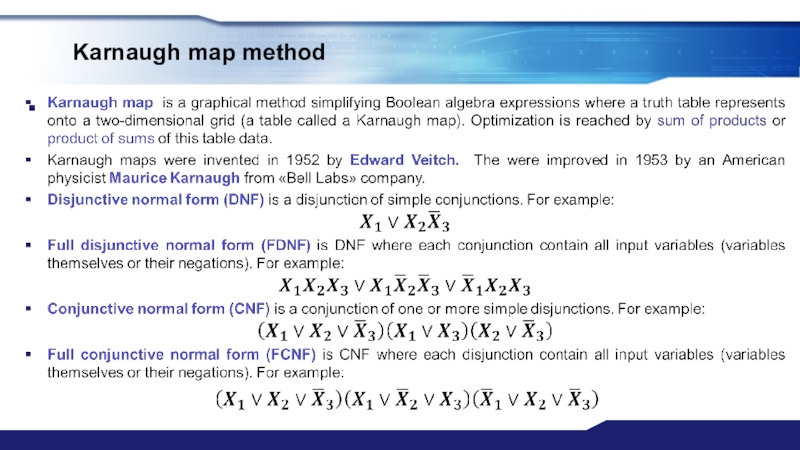

Veitch charts method;

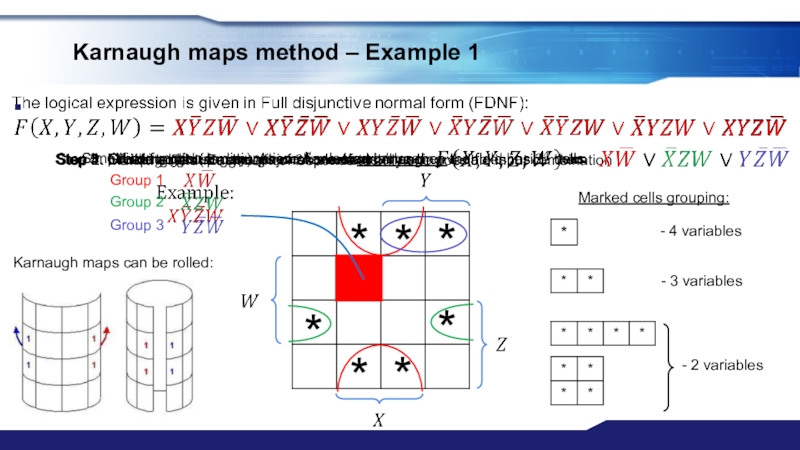

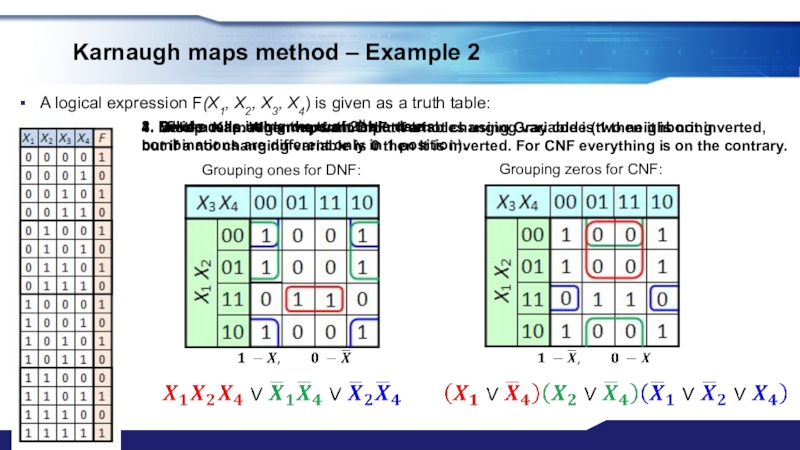

Method of Karnaugh maps;

Quine algorithm;

Quine – McCluskey algorithm.

Pulse delay in logical gates