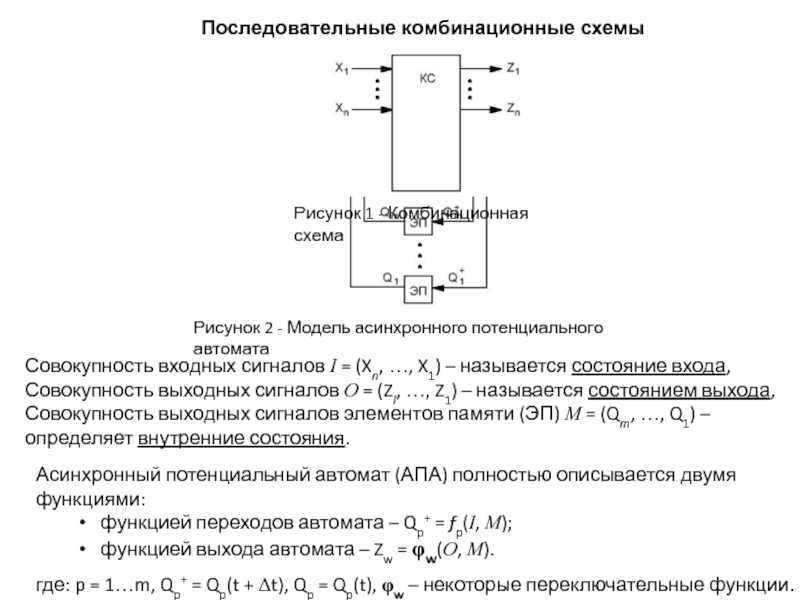

сигналов I = (Xn, …, X1) – называется состояние входа,

Совокупность

выходных сигналов O = (Zl, …, Z1) – называется состоянием выхода,Рисунок 1 - Комбинационная схема

Совокупность выходных сигналов элементов памяти (ЭП) M = (Qm, …, Q1) – определяет внутренние состояния.

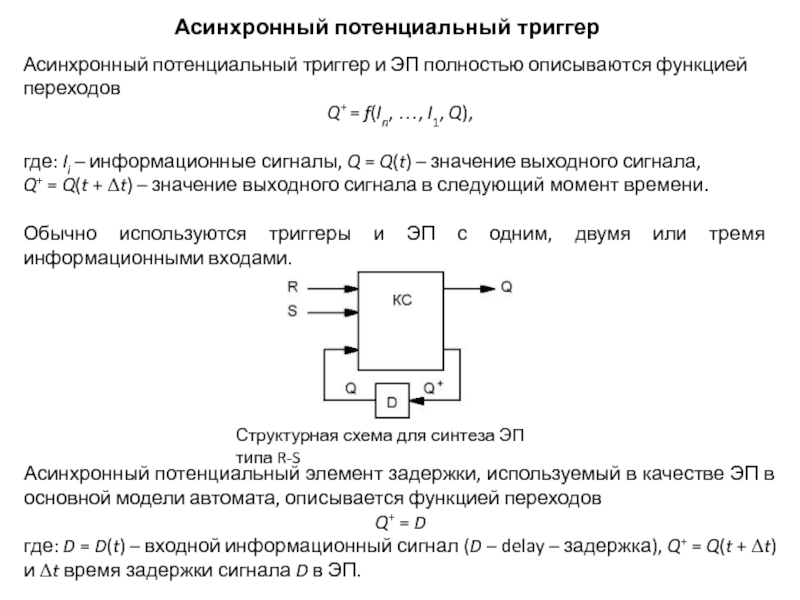

Асинхронный потенциальный автомат (АПА) полностью описывается двумя функциями:

функцией переходов автомата – Qp+ = fp(I, M);

функцией выхода автомата – Zw = fw(O, M).

где: p = 1…m, Qp+ = Qp(t + Dt), Qp = Qp(t), fw – некоторые переключательные функции.