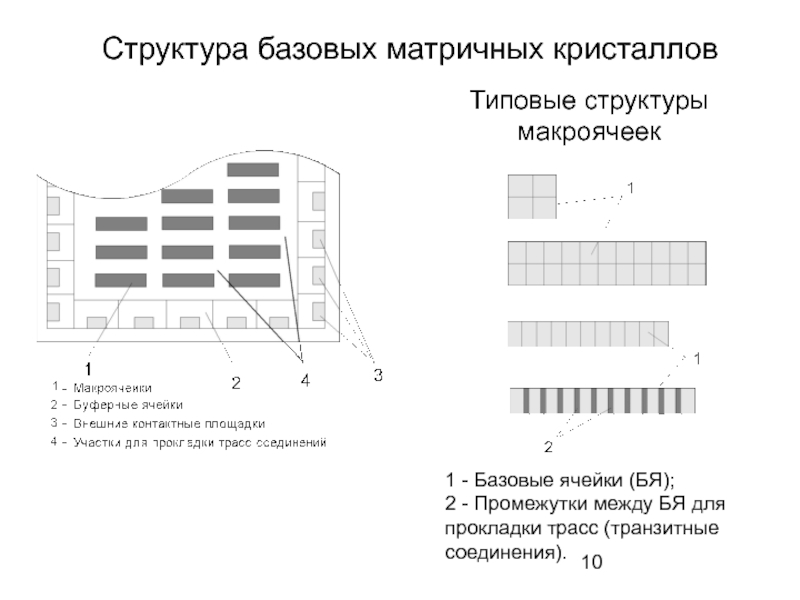

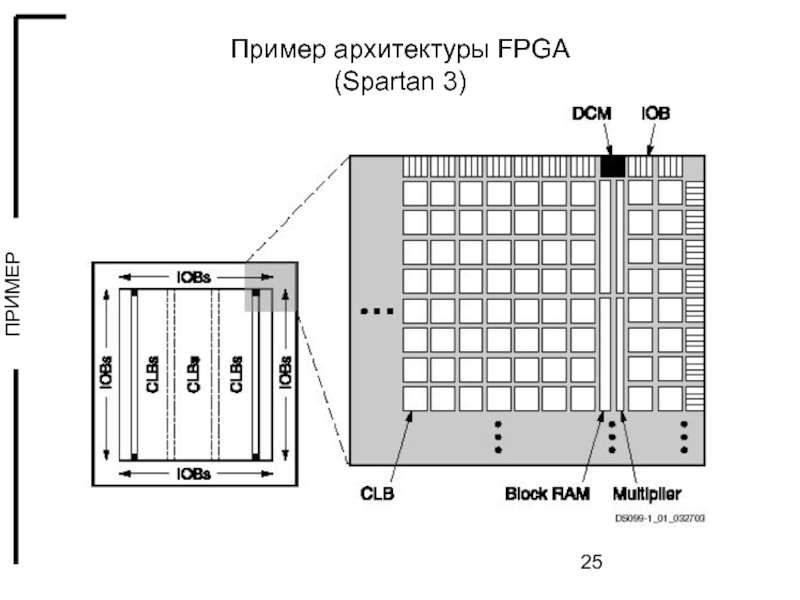

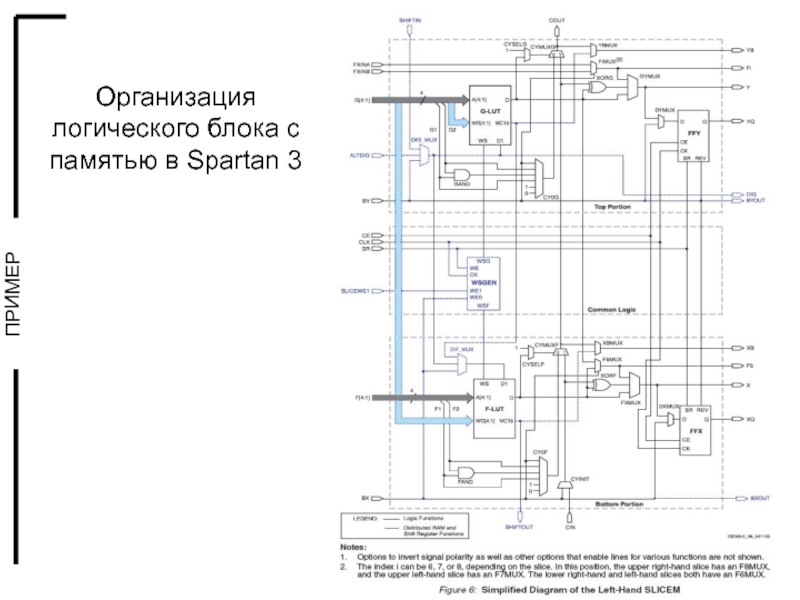

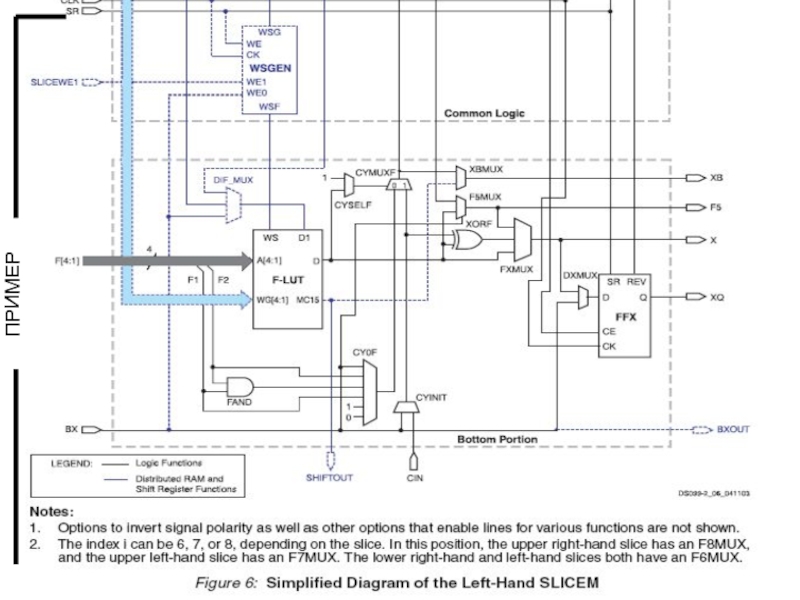

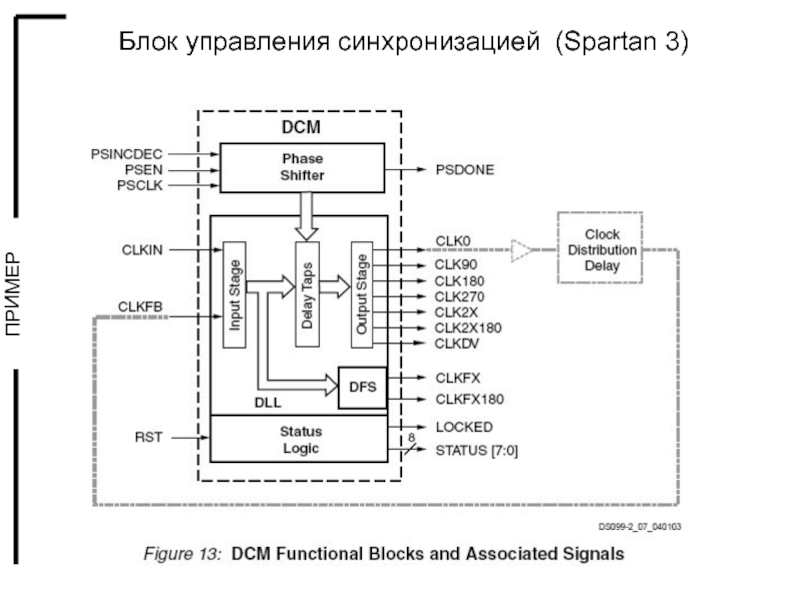

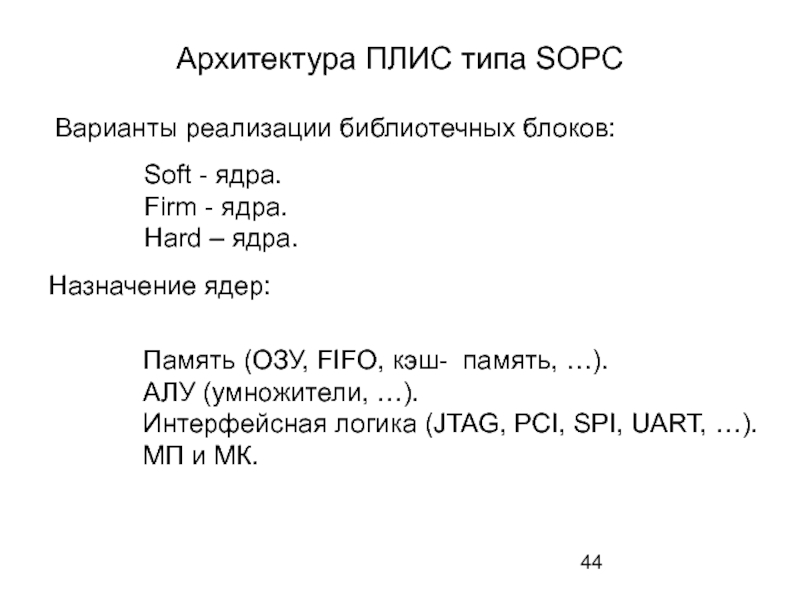

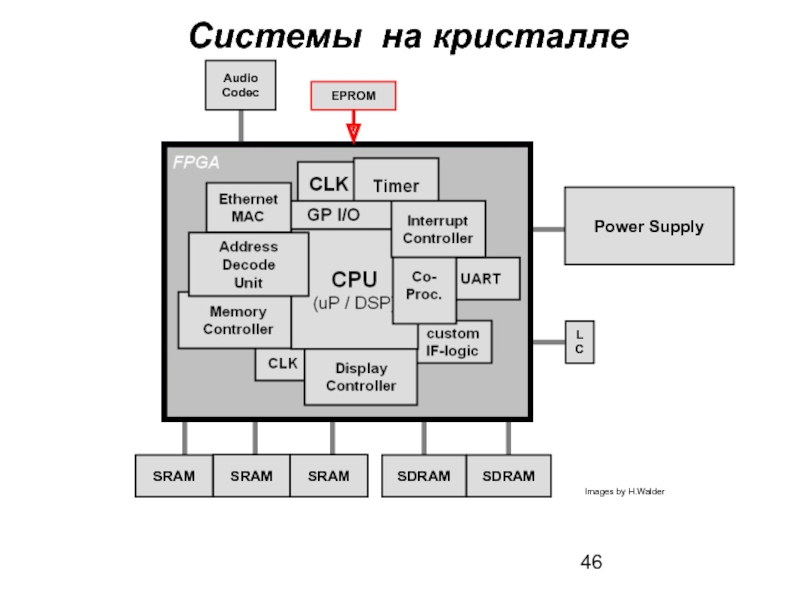

Архитектура интегральных схем с программируемой структурой (ПЛИС).

Основы языка VHDL

и Verilog. Процесс проектирования цифровых устройств с использованием ПЛИС.