Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

АДРЕСНОЕ ПРОСТРАНСТВО МПС И МЕТОДЫ ДЕШИФРАЦИИ

Содержание

- 1. АДРЕСНОЕ ПРОСТРАНСТВО МПС И МЕТОДЫ ДЕШИФРАЦИИ

- 2. План лекции 1.Адресное пространство МПС 2.

- 3. Адресное пространство МПС Адресное пространство представляет собой

- 4. Слайд 4

- 5. Слайд 5

- 6. Адресное пространство определяет число возможных отличимых друг

- 7. Понятие адресного пространства позволяет наглядно представлять размещение в нем различных программно-доступных объектов.

- 8. Слайд 8

- 9. А- зона 16К (0000-3FFF), отведенная для адресов

- 10. Методы дешифрации адресов. Принцип полной дешифрацииДля решения

- 11. Слайд 11

- 12. Принцип частичной дешифрацииДля правильной работы такой микроЭВМ

- 13. Слайд 13

- 14. Слайд 14

- 15. Слайд 15

- 16. Если адресная шина содержит :три сигнальные линии,

- 17. . Методы дешифрации адресов Старший двоичный разряд

- 18. Слайд 18

- 19. При 16-ти разрядной шине адресаадресное пространство при

- 20. Таблица адресов0000-03FFh 1K0400-07FFh 1K 0000-07FFh

- 21. Схемы адресных дешифраторов

- 22. Выделение восьми блоков по 2K ячеек

- 23. выделять восемь блоков по 256 ячеек

- 24. ПЗУ в качестве адресного дешифратора .Пусть требуется

- 25. решениенаименьший блок имеет размер 2К ячеек, то

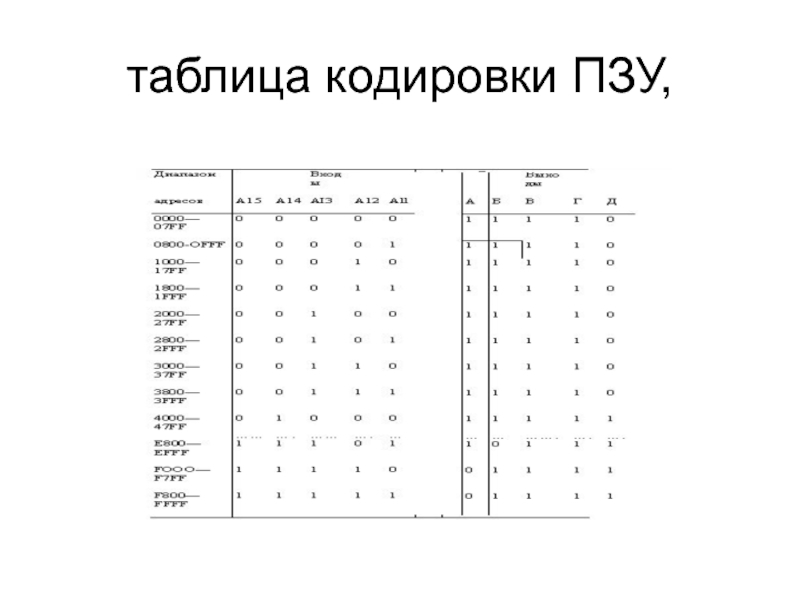

- 26. дешифраторВыбираем за основу ПЗУ с пятью адресными

- 27. . Микросхема ПЗУ

- 28. таблица кодировки ПЗУ,

- 29. Скачать презентанцию

План лекции 1.Адресное пространство МПС 2. Методы дешифрации адресов. 3. Схемы адресных дешифраторов 4.Использование ПЗУ в качестве адресного дешифратора.

Слайды и текст этой презентации

Слайд 2План лекции

1.Адресное пространство МПС

2. Методы дешифрации адресов.

3. Схемы адресных дешифраторов

адресного дешифратора.Слайд 3Адресное пространство МПС

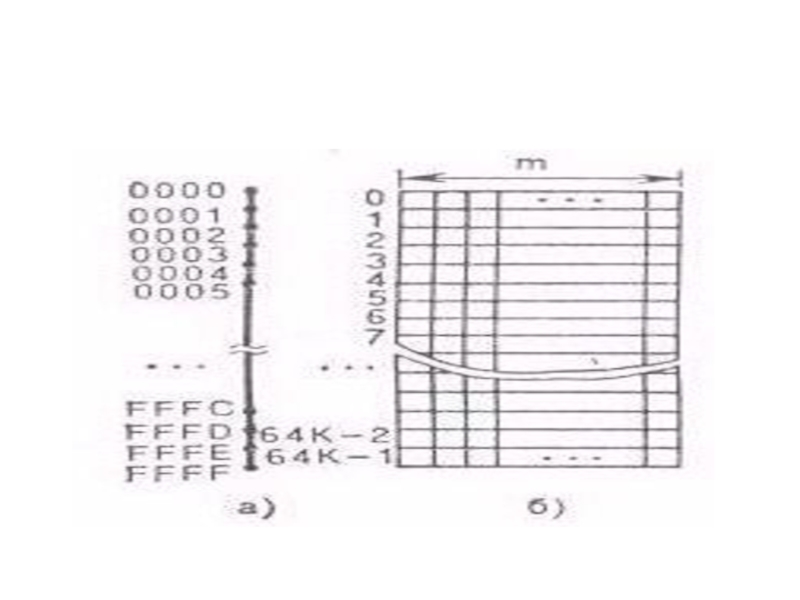

Адресное пространство представляет собой упорядоченное множество кодов

0, 1, 2,., (2*n—1); где n—число адресных линий.

Это множество

для наглядности представляют в виде отрезка числовой оси либо в виде таблицы)

Нумерация точек, или «ячеек», адресного пространства при его графическом представлении производится снизу вверх или сверху вниз (что удобнее) в десятичной, восьмеричной или шестнадцатеричной форме

Слайд 6

Адресное пространство определяет число возможных отличимых друг от друга кодовых

комбинаций (адресов), которые может выдать на адресную шину активное устройство

.

Адресное пространство определяет лишь потенциальные возможности системы—максимальное число программно-доступных элементов, которые могут присутствовать в ней. Поэтому адресное пространство можно сравнить с пустым или частично заполненным помещением библиотеки, в котором можно разместить, например, не более 64К книгСлайд 7

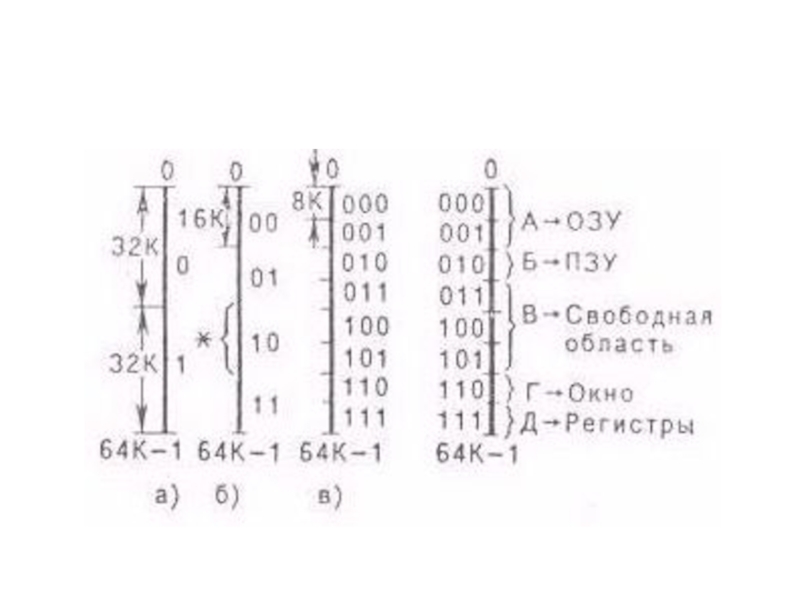

Понятие адресного пространства позволяет наглядно представлять размещение в нем различных

программно-доступных объектов.

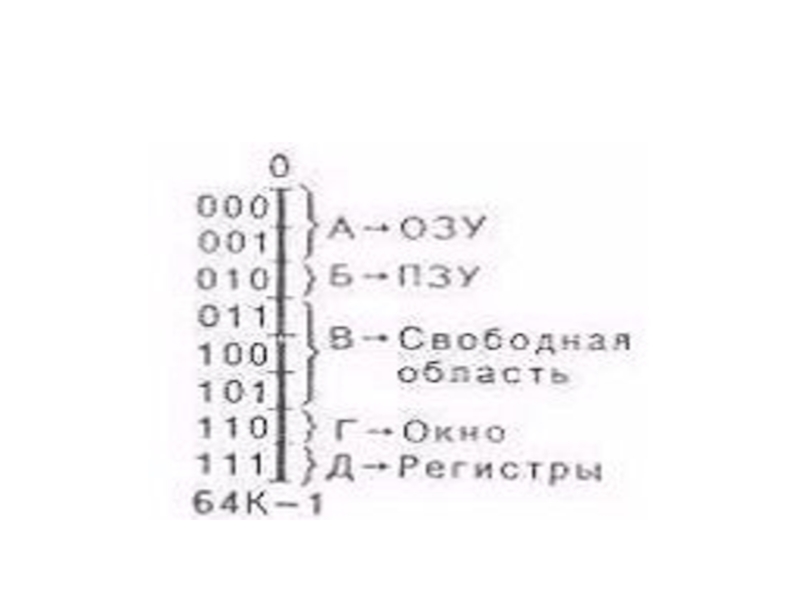

Слайд 9

А- зона 16К (0000-3FFF), отведенная для адресов ОЗУ;

Б- зона

8К (4000-5FFF) отведенная для

адресов ПЗУ;В- свободная зона 24К (6000-BFFF),

Г- «окно» размером 8К (C000-DFFF)

Д- зона 8К (E000-FFFF)

Слайд 10Методы дешифрации адресов.

Принцип полной дешифрации

Для решения задачи подключения триггера

нужно,

во-первых, определить, его «положение» в адресном пространстве

во-вторых, предусмотреть схему адресного дешифратора, который срабатывает при обращении процессора к схеме. Положение адреса в адресном пространстве микроЭВМ можно выбрать в любой свободной области, т. е.

либо в оставшейся незанятой части зоны ЕООО—FFFF,

либо в области 6000—BFFF.

Остановимся, например, на последней: 6000—BFFF.

Структура дешифратора зависит от используемой элементной базы и, что особенно важно, от выбранного метода дешифрации

Слайд 12

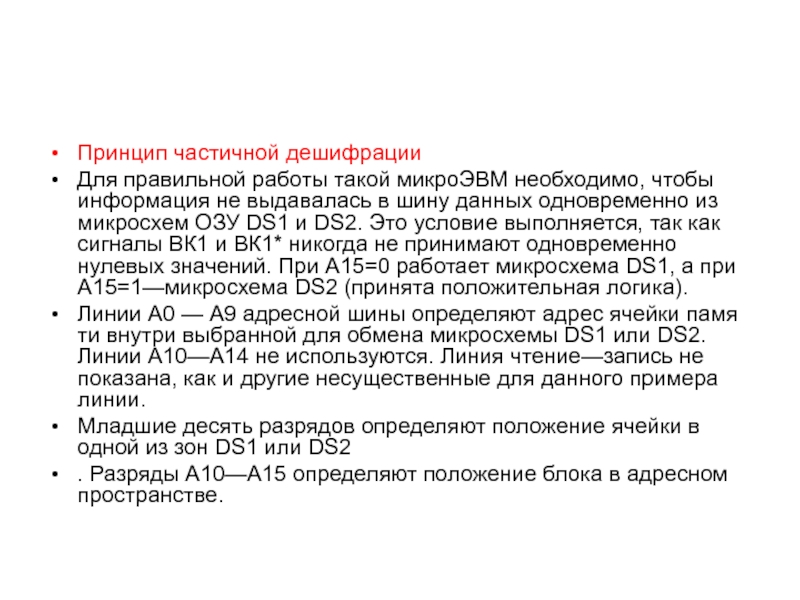

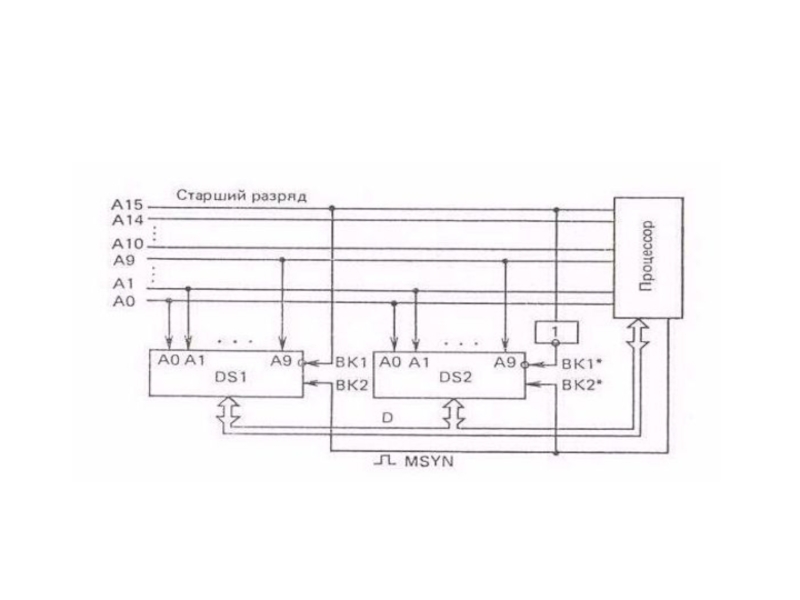

Принцип частичной дешифрации

Для правильной работы такой микроЭВМ необходимо, чтобы информация

не выдавалась в шину данных одновременно из микросхем ОЗУ DS1

и DS2. Это условие выполняется, так как сигналы ВК1 и ВК1* никогда не принимают одновременно нулевых значений. При А15=0 работает микросхема DS1, а при А15=1—микросхема DS2 (принята положительная логика).Линии А0 — А9 адресной шины определяют адрес ячейки памяти внутри выбранной для обмена микросхемы DS1 или DS2. Линии А10—А14 не используются. Линия чтение—запись не показана, как и другие несущественные для данного примера линии.

Младшие десять разрядов определяют положение ячейки в одной из зон DS1 или DS2

. Разряды А10—А15 определяют положение блока в адресном пространстве.

Слайд 16

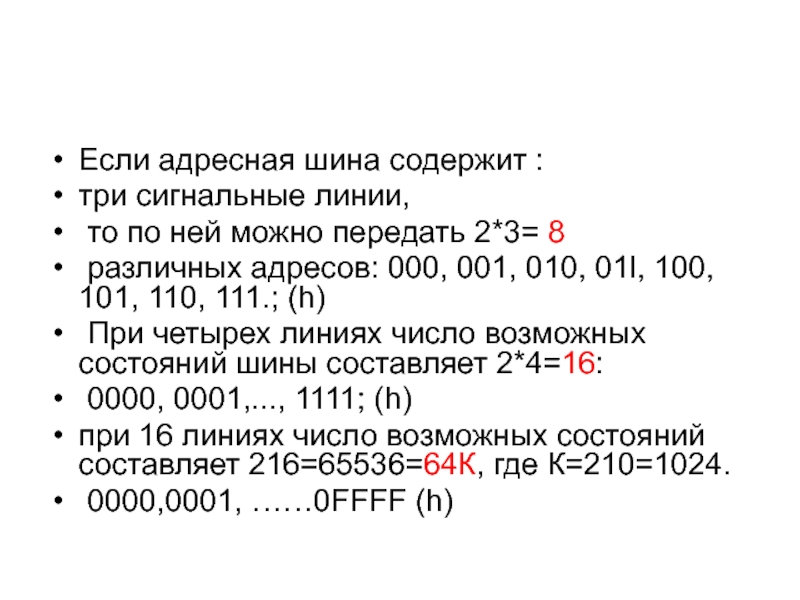

Если адресная шина содержит :

три сигнальные линии,

то по ней

можно передать 2*3= 8

различных адресов: 000, 001, 010, 01l,

100, 101, 110, 111.; (h) При четырех линиях число возможных состояний шины составляет 2*4=16:

0000, 0001,..., 1111; (h)

при 16 линиях число возможных состояний составляет 216=65536=64К, где К=210=1024.

0000,0001, ……0FFFF (h)

Слайд 17. Методы дешифрации адресов

Старший двоичный разряд адреса делит адресное

пространство на две равные части

два старших разряда делят его

на четыре равные части(три старших разряда—на восемь равных частей.

Шестнадцать разрядов адреса делят адресное пространство емкостью 64К на 64К частей по одной ячейке

.

Слайд 19

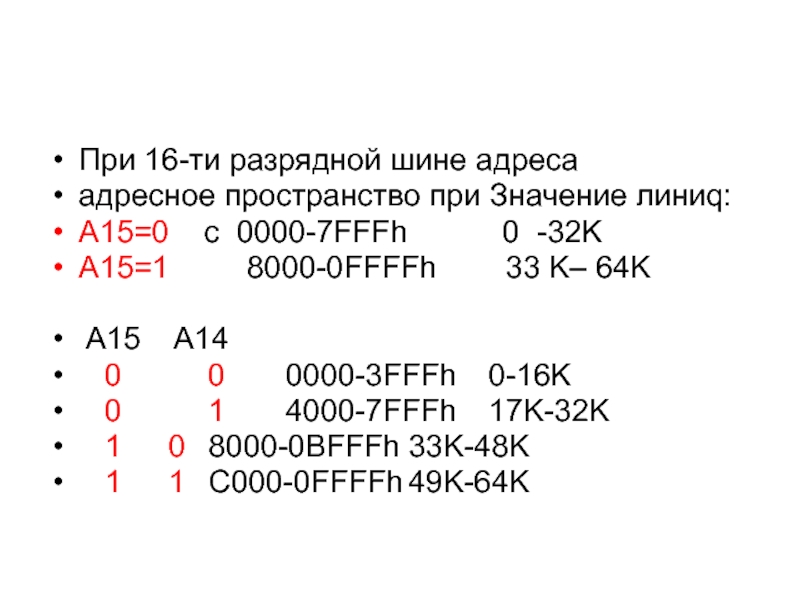

При 16-ти разрядной шине адреса

адресное пространство при Значение линиq:

А15=0

с 0000-7FFFh 0 -32K

A15=1

8000-0FFFFh 33 K– 64K A15 A14

0 0 0000-3FFFh 0-16K

0 1 4000-7FFFh 17K-32K

1 0 8000-0BFFFh 33K-48K

1 1 C000-0FFFFh 49K-64K

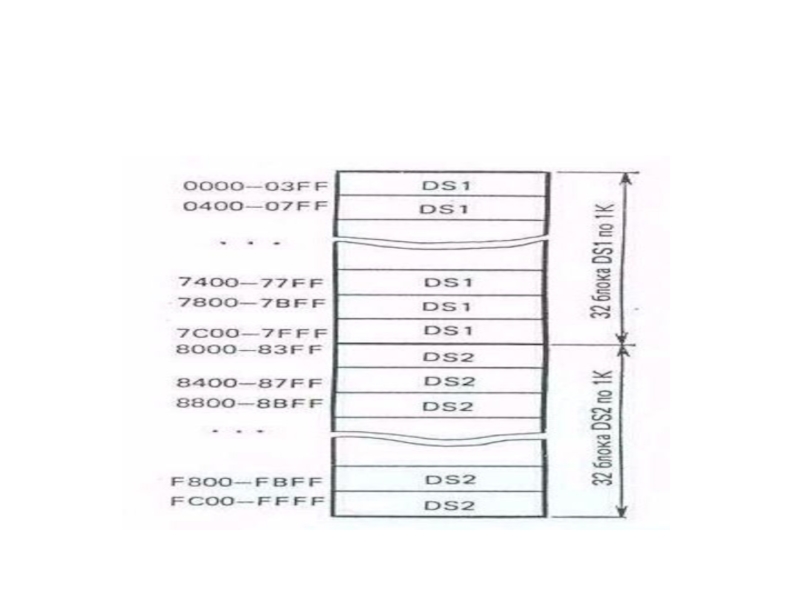

Слайд 20Таблица адресов

0000-03FFh 1K

0400-07FFh 1K 0000-07FFh 2K

0800-0BFFh

1K

0C00-0FFFh 1K 0000-0FFFh 4K

1000-13FFh 1K

1400-17FFh 1K

1800-1BFFh 1K

1C00-1FFFh

1K 0000h-1FFFh 8K0000-3FFFh 16K

0000-7FFFh 32K

0000-0BFFh 48K

0000-0FFFFh 64G

Слайд 24ПЗУ в качестве адресного дешифратора

.Пусть требуется выделить зоны адресного

пространства для размещения в них адресов следующих устройств, каждое из

которых представляет собой одну микросхему:,а) ПЗУ1 зону F000—FFFF, 4K ячеек;

б) ПЗУ2 зону E000—EFFF, 4K ячеек;

в) ОЗУ1 зону A000—A7FF, 2K ячеек;

г) УВВ зону 8000—87FF, 2K ячеек;

д) ОЗУ2 зону 0000—3FFF, 16К ячеек.

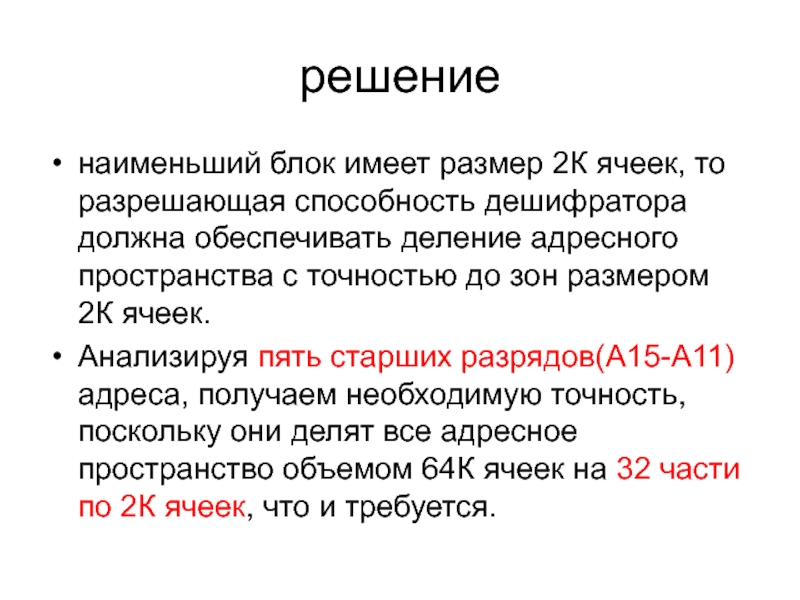

Слайд 25решение

наименьший блок имеет размер 2К ячеек, то разрешающая способность дешифратора

должна обеспечивать деление адресного пространства с точностью до зон размером

2К ячеек.Анализируя пять старших разрядов(А15-А11) адреса, получаем необходимую точность, поскольку они делят все адресное пространство объемом 64К ячеек на 32 части по 2К ячеек, что и требуется.