Physics Faculty, Electronic Devices & Systems, 7th semester,2010

Dr. Mokhovikov

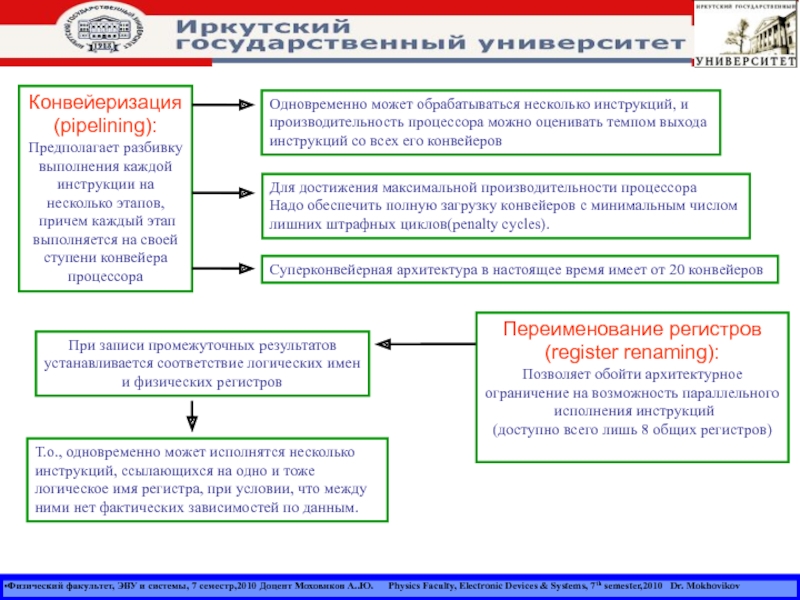

Конвейеризация

(pipelining):

Предполагает разбивку выполнения каждой инструкции на несколько этапов,

причем каждый этап выполняется на своей ступени конвейера процессора

Одновременно может обрабатываться несколько инструкций, и

производительность процессора можно оценивать темпом выхода

инструкций со всех его конвейеров

Для достижения максимальной производительности процессора

Надо обеспечить полную загрузку конвейеров с минимальным числом

лишних штрафных циклов(penalty cycles).

Суперконвейерная архитектура в настоящее время имеет от 20 конвейеров

Переименование регистров

(register renaming):

Позволяет обойти архитектурное

ограничение на возможность параллельного

исполнения инструкций

(доступно всего лишь 8 общих регистров)

При записи промежуточных результатов

устанавливается соответствие логических имен

и физических регистров

Т.о., одновременно может исполнятся несколько

инструкций, ссылающихся на одно и тоже

логическое имя регистра, при условии, что между

ними нет фактических зависимостей по данным.