Разделы презентаций

- Разное

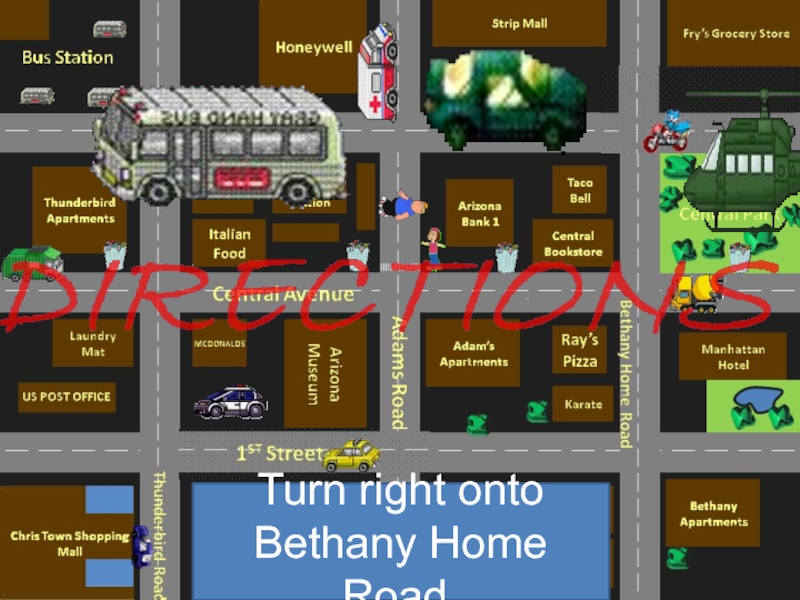

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Хранение информации Министерство образования и науки Российской

Содержание

- 1. Хранение информации Министерство образования и науки Российской

- 2. 5. Хранение информации в компьютерной технике.Регистровая память,

- 3. 5. Хранение информации в компьютерной технике.5.1. Классификация запоминающих устройствРис. 5.1. Классификация запоминающих устройств.

- 4. 5. Хранение информации в компьютерной технике.5.2. Характеристики

- 5. 5. Хранение информации в компьютерной технике5.3. Конфигурация

- 6. 5. Хранение информации в компьютерной технике5.4. Запоминающие

- 7. 5. Хранение информации в компьютерной технике5.4. Запоминающие

- 8. 5. Хранение информации в компьютерной технике5.5. Основные

- 9. Рис. 5.9 Вид модулей, вверху – модуль

- 10. Таблица 1 Основные параметры перечисленных в спецификации

- 11. Рис. 5.13. Модули DDR3 1333 8 ГБРис.

- 12. 5. Хранение информации в компьютерной технике5.5. Основные

- 13. 5. Хранение информации в компьютерной технике5.5. Основные

- 14. 5. Хранение информации в компьютерной технике5.6. Организация

- 15. 5. Хранение информации в компьютерной технике5.6. Организация

- 16. 5. Хранение информации в компьютерной технике5.6. Организация

- 17. 5. Хранение информации в компьютерной технике5.6. Организация

- 18. 5. Хранение информации в компьютерной технике5.6. Организация

- 19. 5. Хранение информации в компьютерной технике5.6. Организация

- 20. 5. Хранение информации в компьютерной технике5.6. Организация

- 21. 5. Хранение информации в компьютерной технике5.6. Организация

- 22. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Хранение информации

Курс лекций часть 1

Масловский Владимир Михайлович, к.т.н., доцент кафедра

ИУ-10

Слайд 25. Хранение информации в компьютерной технике.

Регистровая память, имеющаяся в составе

процессора или других устройств ЭВМ, предназначенная для кратковременного хранения небольшого

объема информации, непосредственно участвующей в вычислениях или операциях обмена (ввода-вывода).Основная память предназначена для оперативного хранения и обмена данными, непосредственно участвующими в процессе обработки. Конструктивно она исполняется в виде интегральных схем (ИС) и подразделяется на два вида:

- постоянное запоминающее устройство (ПЗУ);

- оперативное запоминающее устройство.

Кэш-память служит для хранения копий информации, используемой в текущих операциях обмена.

Внешняя память используется для долговременного хранения больших объемов информации. В современных компьютерных системах в качестве устройств внешней памяти наиболее часто применяются:

- накопители на жестких магнитных дисках (НЖМД);

- накопители на гибких магнитных дисках (НГМД);

- накопители на оптических дисках;

- магнитооптические носители информации;

- ленточные накопители (стримеры).

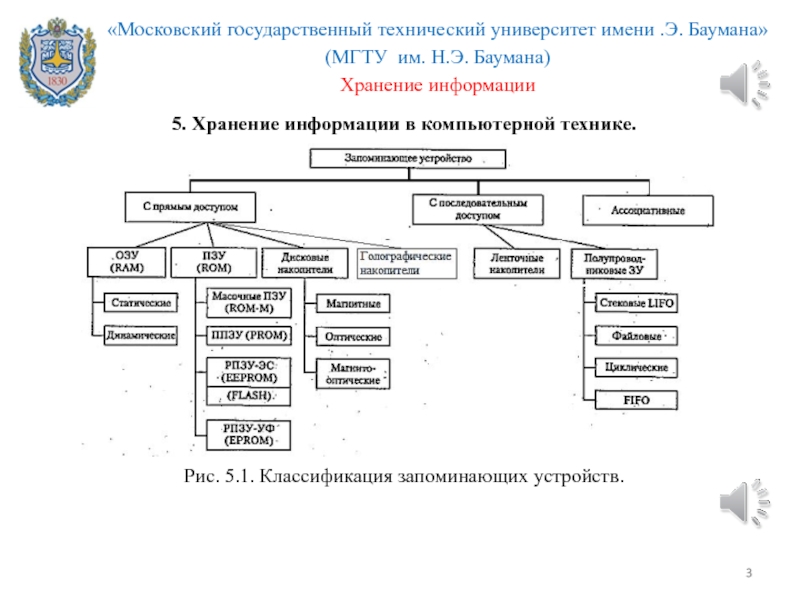

Слайд 35. Хранение информации в компьютерной технике.

5.1. Классификация запоминающих устройств

Рис. 5.1.

Классификация запоминающих устройств.

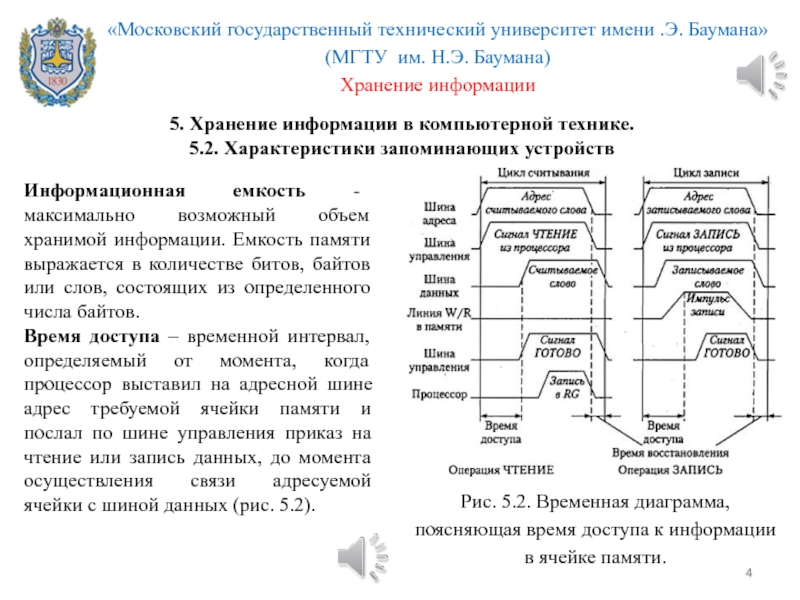

Слайд 45. Хранение информации в компьютерной технике.

5.2. Характеристики запоминающих устройств

Рис. 5.2.

Временная диаграмма, поясняющая время доступа к информации в ячейке памяти.

Информационная

емкость - максимально возможный объем хранимой информации. Емкость памяти выражается в количестве битов, байтов или слов, состоящих из определенного числа байтов.Время доступа – временной интервал, определяемый от момента, когда процессор выставил на адресной шине адрес требуемой ячейки памяти и послал по шине управления приказ на чтение или запись данных, до момента осуществления связи адресуемой ячейки с шиной данных (рис. 5.2).

Слайд 55. Хранение информации в компьютерной технике

5.3. Конфигурация запоминающих устройств с

прямым доступом

Рис. 5.3. ПЗУ 256х8 с одномерной адресацией

Рис. 5.4. ПЗУ

256х1 с двумерной адресацией 1-битовых слов- DIP (Dual IN Line Package – корпус с двумя рядами выводов) – классические микросхемы, применявшиеся в ранних моделях ЭВМ, сейчас применяются в блоках кэш памяти;

- SIP (Single In Line Package –корпус с одним рядом выводов) – микросхема с одним рядом выводов, устанавливаемая вертикально.

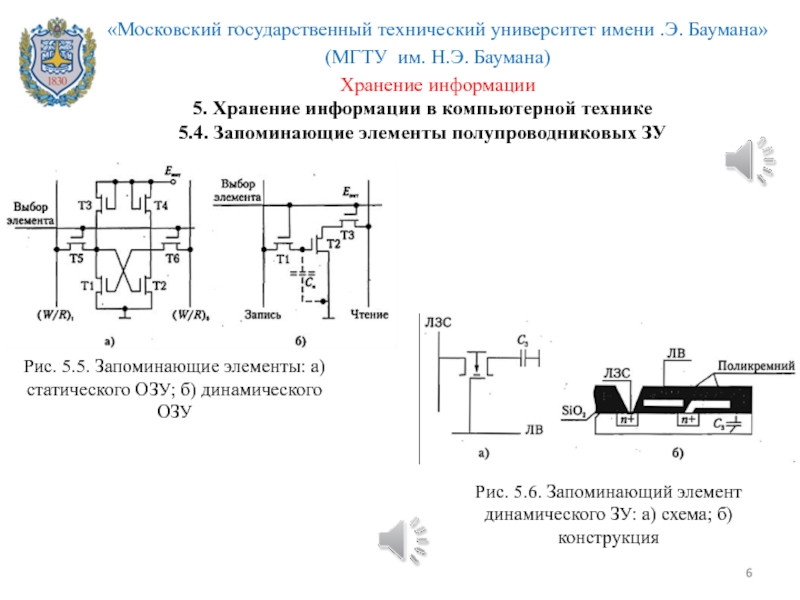

Слайд 65. Хранение информации в компьютерной технике

5.4. Запоминающие элементы полупроводниковых ЗУ

Рис.

5.5. Запоминающие элементы: а) статического ОЗУ; б) динамического ОЗУ

Рис. 5.6.

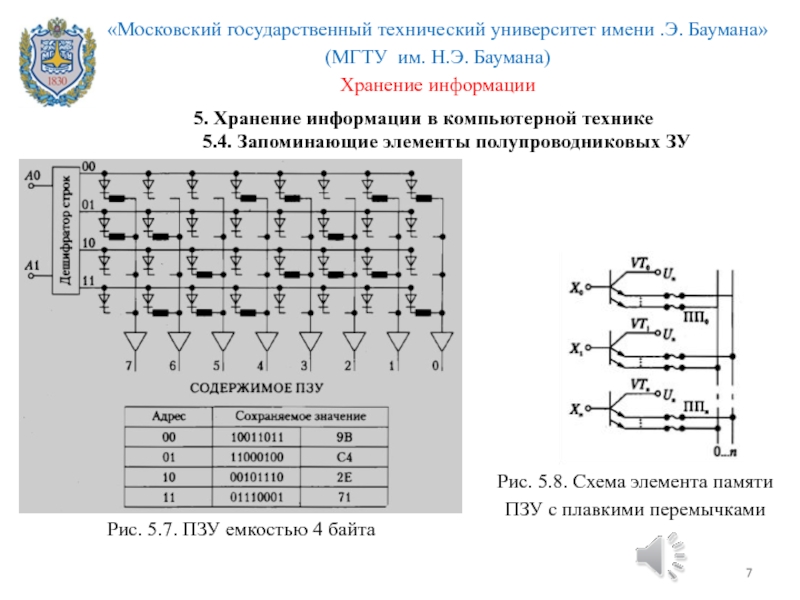

Запоминающий элемент динамического ЗУ: а) схема; б) конструкцияСлайд 75. Хранение информации в компьютерной технике

5.4. Запоминающие элементы полупроводниковых ЗУ

Рис.

5.7. ПЗУ емкостью 4 байта

Рис. 5.8. Схема элемента памяти ПЗУ

с плавкими перемычкамиСлайд 85. Хранение информации в компьютерной технике

5.5. Основные типы памяти современных

ПЭВМ

5.5.1. Оперативные запоминающие устройства.

Как было отмечено выше, в современных микропроцессорных

системах в качестве ОЗУ чаще всего используются динамические ЗУ с запоминающим конденсатором. FPM DRAM - Fast Page Mode DRAM – динамическая память с быстрым страничным доступом.

EDO - Extended Data Out – расширенное время удержания данных на выходе.

BEDO - Burst EDO – EDO с блочным доступом – память на основе EDO, работающая не одиночными, а пакетными циклами чтение/записи.

SDRAM – Synchronjus DRAM – синхронная динамическая память – память с синхронным доступом, работающая быстрее обычной асинхронной (FPM/EDO/BEDO).

VCM 133 -Virtufl Channel Memory – виртуальный канал памяти.

RDRAM. Память типа RDRAM - Rambus DRAM, разработанная Rambus Inc, построенная на базе специального интерфейса Rambus Interface, которым снабжается как контроллер памяти, так и каждая микросхема.

DDR SDRAM - DDR, Double Data Rate –удвоенная скорость передачи данных.

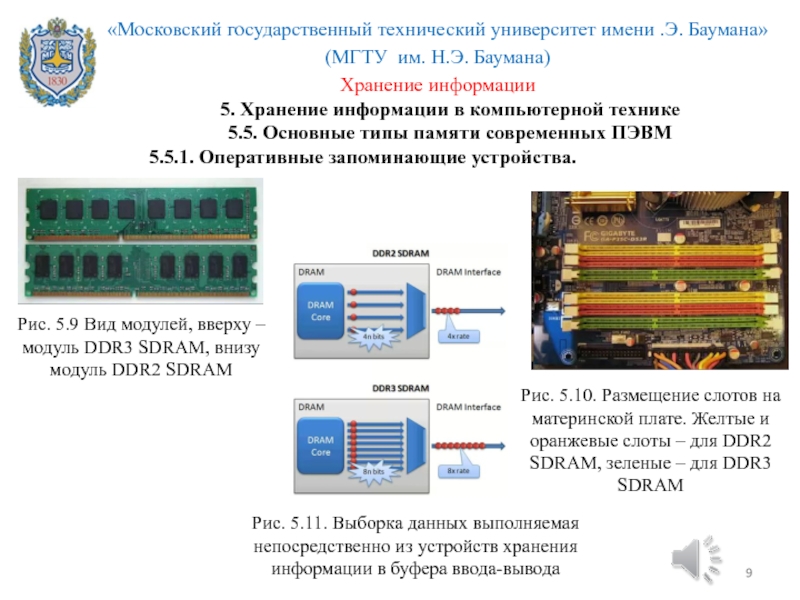

Слайд 9Рис. 5.9 Вид модулей, вверху – модуль DDR3 SDRAM, внизу

модуль DDR2 SDRAM

Рис. 5.10. Размещение слотов на материнской плате. Желтые

и оранжевые слоты – для DDR2 SDRAM, зеленые – для DDR3 SDRAMРис. 5.11. Выборка данных выполняемая непосредственно из устройств хранения информации в буфера ввода-вывода

5. Хранение информации в компьютерной технике

5.5. Основные типы памяти современных ПЭВМ

5.5.1. Оперативные запоминающие устройства.

Слайд 10Таблица 1 Основные параметры перечисленных в спецификации вариантов

Рис. 5.12. упаковка

BGA (Ball Grid Array — массив шариков)

5. Хранение информации в

компьютерной технике5.5. Основные типы памяти современных ПЭВМ

5.5.1. Оперативные запоминающие устройства.

Слайд 11Рис. 5.13. Модули DDR3 1333 8 ГБ

Рис. 5.14. Модуль памяти

Kingston HyperX Blu PC3-12800 DIMM DDR3 1600MHz - KIT 2x2Gb

KHX1600C9AD3B1K2/4G CL9Тайминги - временные задержки сигнала. Тайминги измеряют в наносекундах (нс). Мера таймингов – такт. В описании оперативной памяти они указываются в виде последовательности чисел (CL5-5-4-12 или просто 9-9-9-24), где по порядку указываются следующие параметры:

- CAS Latency – задержка между командой чтения и доступностью к чтению первого слова.

- RAS to CAS Delay (RCD) - задержка между сигналами RAS (Row Address Strobe) и CAS (Column Address Strobe), этот параметр указывает интервал между доступами на шину контроллером памяти сигналов RAS3 и CAS3.

- RAS Precharge Time (RP) – время повторной выдачи (период накопления заряда) сигнала RAS3 – через какое время контроллер памяти будет способен снова выдать сигнал инициализации адреса строки.

- DRAM Cycle Time Tras/Trc – суммарный показатель быстродействия модуля памяти.

5. Хранение информации в компьютерной технике

5.5. Основные типы памяти современных ПЭВМ

5.5.1. Оперативные запоминающие устройства.

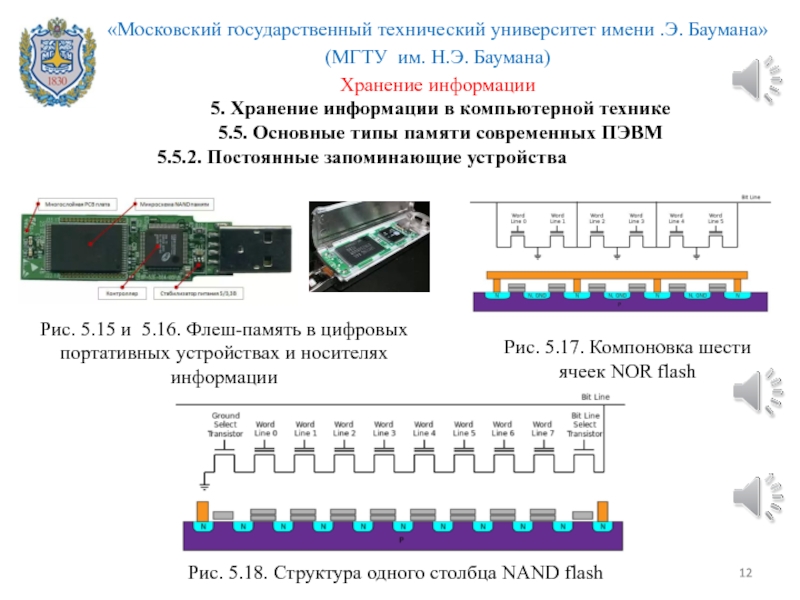

Слайд 125. Хранение информации в компьютерной технике

5.5. Основные типы памяти современных

ПЭВМ

5.5.2. Постоянные запоминающие устройства

Рис. 5.15 и 5.16. Флеш-память в цифровых

портативных устройствах и носителях информации Рис. 5.17. Компоновка шести ячеек NOR flash

Рис. 5.18. Структура одного столбца NAND flash

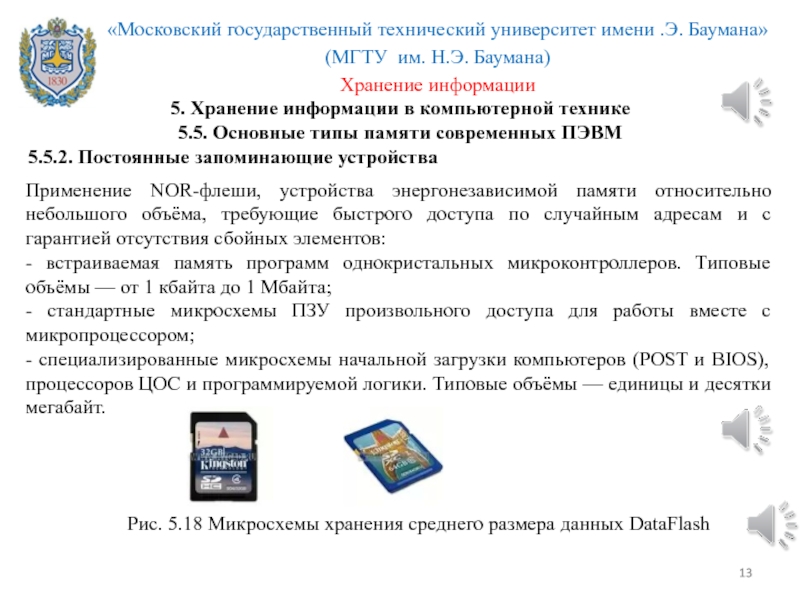

Слайд 135. Хранение информации в компьютерной технике

5.5. Основные типы памяти современных

ПЭВМ

5.5.2. Постоянные запоминающие устройства

Применение NOR-флеши, устройства энергонезависимой памяти относительно небольшого

объёма, требующие быстрого доступа по случайным адресам и с гарантией отсутствия сбойных элементов:- встраиваемая память программ однокристальных микроконтроллеров. Типовые объёмы — от 1 кбайта до 1 Мбайта;

- стандартные микросхемы ПЗУ произвольного доступа для работы вместе с микропроцессором;

- специализированные микросхемы начальной загрузки компьютеров (POST и BIOS), процессоров ЦОС и программируемой логики. Типовые объёмы — единицы и десятки мегабайт.

Рис. 5.18 Микросхемы хранения среднего размера данных DataFlash

Слайд 145. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.1. Основные понятия о типах и структурах данных

К целому типу

относится конечное множество целых чисел, причем наибольшее по модулю целое число определяется конкретной вычислительной системой. К вещественному типу относится конечное множество вещественных чисел, содержащих в общем случае целую и дробную части.

К символьному типу относится конечное множество символов, в которое могут входить буквы, десятичные цифры, математические и специальные знаки и разделители.

Логический тип представляет одно из двух логических значений – истина или ложь. Над логическими данными можно выполнять основные логические операции конъюнкции (И), дизъюнкции (ИЛИ) и отрицания (НЕ), а также более сложные операции эквивалентности, импликации, исключающего ИЛИ и др.

Указательный тип представляет множество переменных (указателей), значения которых содержат адреса байтов памяти. Присваивая указателю то или иное допустимое значение, можно обеспечить доступ к желаемым данным через этот указатель.

Слайд 155. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

Под организацией данных

понимают совокупность методов и средств представления информации в ЭВМ. Различают логическую и физическую (машинную) организации данных.Физическая организация (структура) данных отражает способы представления данных в памяти ЭВМ и методы доступа к ним.

Логическая организация данных является абстрактным способом представления данных, не связанным с физической средой их размещения.

Единица поименованных данных (объект) – элемент данных (поле). Он является наименьшей (неделимой) единицей информации, имеющей смысловое значение.

Массив – упорядоченная совокупность однотипных элементов, адресуемых с помощью некоторого индекса. Массив может быть одномерным и многомерным.

Слайд 165. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

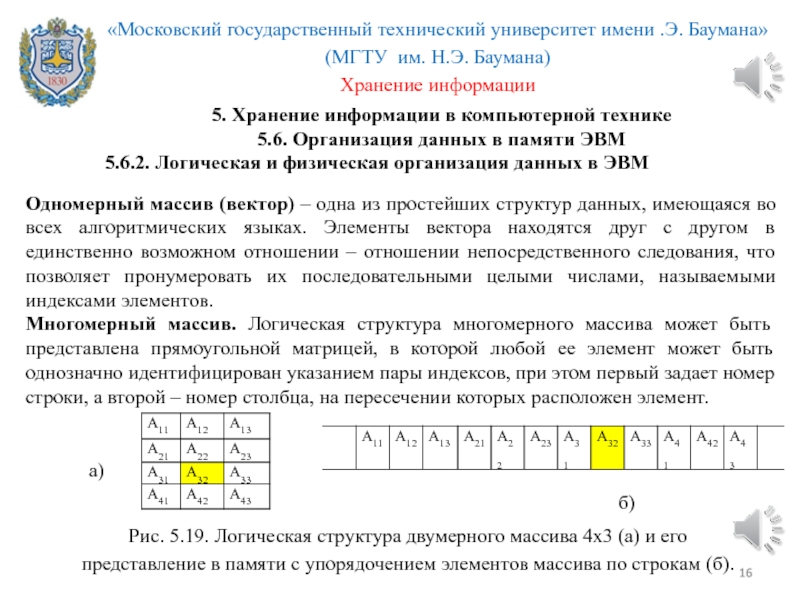

Одномерный массив (вектор)

– одна из простейших структур данных, имеющаяся во всех алгоритмических языках. Элементы вектора находятся друг с другом в единственно возможном отношении – отношении непосредственного следования, что позволяет пронумеровать их последовательными целыми числами, называемыми индексами элементов. Многомерный массив. Логическая структура многомерного массива может быть представлена прямоугольной матрицей, в которой любой ее элемент может быть однозначно идентифицирован указанием пары индексов, при этом первый задает номер строки, а второй – номер столбца, на пересечении которых расположен элемент.

Рис. 5.19. Логическая структура двумерного массива 4х3 (а) и его представление в памяти с упорядочением элементов массива по строкам (б).

а)

б)

Слайд 175. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

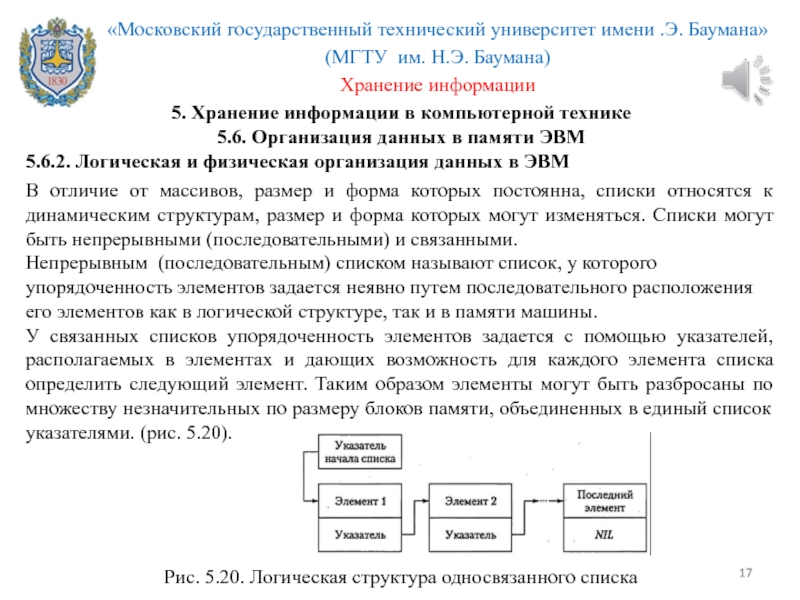

В отличие от

массивов, размер и форма которых постоянна, списки относятся к динамическим структурам, размер и форма которых могут изменяться. Списки могут быть непрерывными (последовательными) и связанными.Непрерывным (последовательным) списком называют список, у которого упорядоченность элементов задается неявно путем последовательного расположения его элементов как в логической структуре, так и в памяти машины.

У связанных списков упорядоченность элементов задается с помощью указателей, располагаемых в элементах и дающих возможность для каждого элемента списка определить следующий элемент. Таким образом элементы могут быть разбросаны по множеству незначительных по размеру блоков памяти, объединенных в единый список указателями. (рис. 5.20).

Рис. 5.20. Логическая структура односвязанного списка

Слайд 185. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

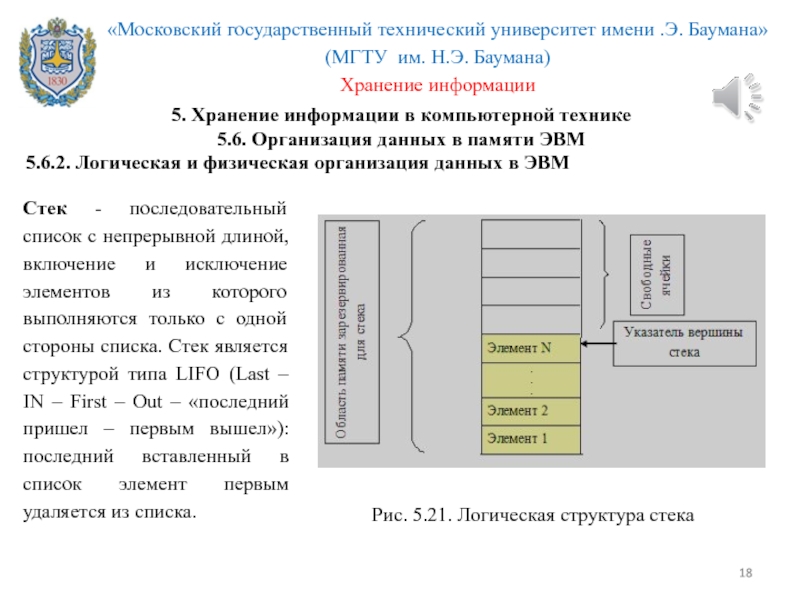

Стек - последовательный

список с непрерывной длиной, включение и исключение элементов из которого выполняются только с одной стороны списка. Стек является структурой типа LIFO (Last – IN – First – Out – «последний пришел – первым вышел»): последний вставленный в список элемент первым удаляется из списка.Рис. 5.21. Логическая структура стека

Слайд 195. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

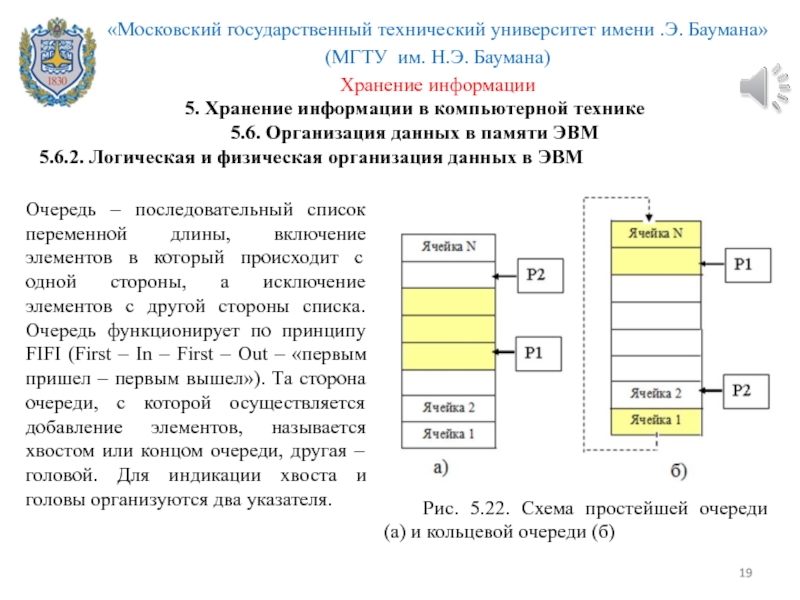

Очередь – последовательный

список переменной длины, включение элементов в который происходит с одной стороны, а исключение элементов с другой стороны списка. Очередь функционирует по принципу FIFI (First – In – First – Out – «первым пришел – первым вышел»). Та сторона очереди, с которой осуществляется добавление элементов, называется хвостом или концом очереди, другая – головой. Для индикации хвоста и головы организуются два указателя.Рис. 5.22. Схема простейшей очереди (а) и кольцевой очереди (б)

Слайд 205. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

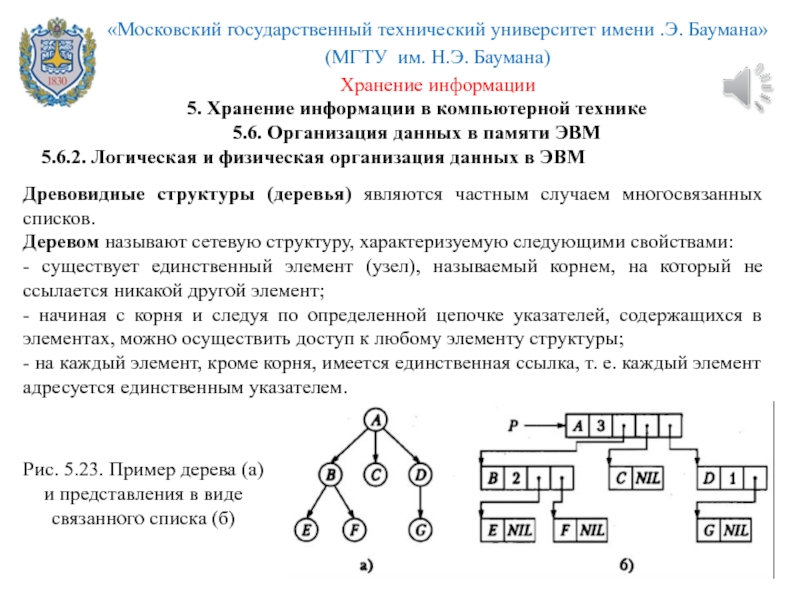

Древовидные структуры (деревья)

являются частным случаем многосвязанных списков.Деревом называют сетевую структуру, характеризуемую следующими свойствами:

- существует единственный элемент (узел), называемый корнем, на который не ссылается никакой другой элемент;

- начиная с корня и следуя по определенной цепочке указателей, содержащихся в элементах, можно осуществить доступ к любому элементу структуры;

- на каждый элемент, кроме корня, имеется единственная ссылка, т. е. каждый элемент адресуется единственным указателем.

Рис. 5.23. Пример дерева (а) и представления в виде связанного списка (б)

Слайд 215. Хранение информации в компьютерной технике

5.6. Организация данных в памяти

ЭВМ

5.6.2. Логическая и физическая организация данных в ЭВМ

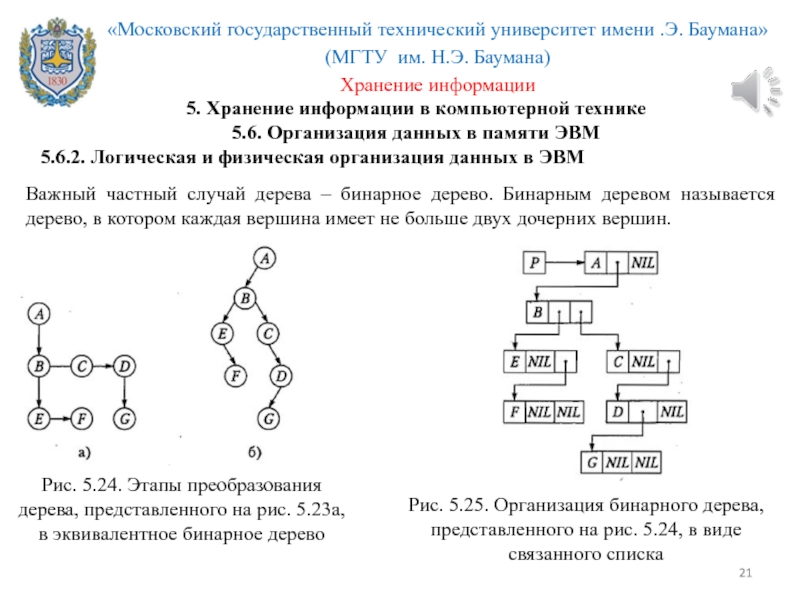

Важный частный случай

дерева – бинарное дерево. Бинарным деревом называется дерево, в котором каждая вершина имеет не больше двух дочерних вершин.Рис. 5.24. Этапы преобразования дерева, представленного на рис. 5.23а, в эквивалентное бинарное дерево

Рис. 5.25. Организация бинарного дерева, представленного на рис. 5.24, в виде связанного списка