Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

(кафедра ИИС и ТП, ауд. 1306) КОТОВ Юрий Терентьевич Электротехника и

Содержание

- 1. (кафедра ИИС и ТП, ауд. 1306) КОТОВ Юрий Терентьевич Электротехника и

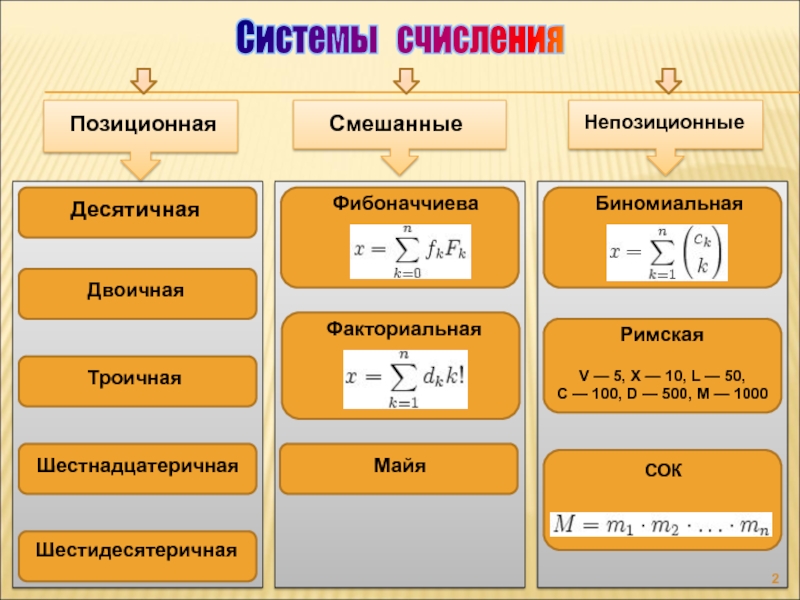

- 2. Системы счисленияПозиционнаяСмешанныеНепозиционныеФакториальная МайяБиномиальнаяРимскаяСОКДесятичнаяДвоичнаяШестнадцатеричнаяШестидесятеричнаяФибоначчиеваV — 5, X

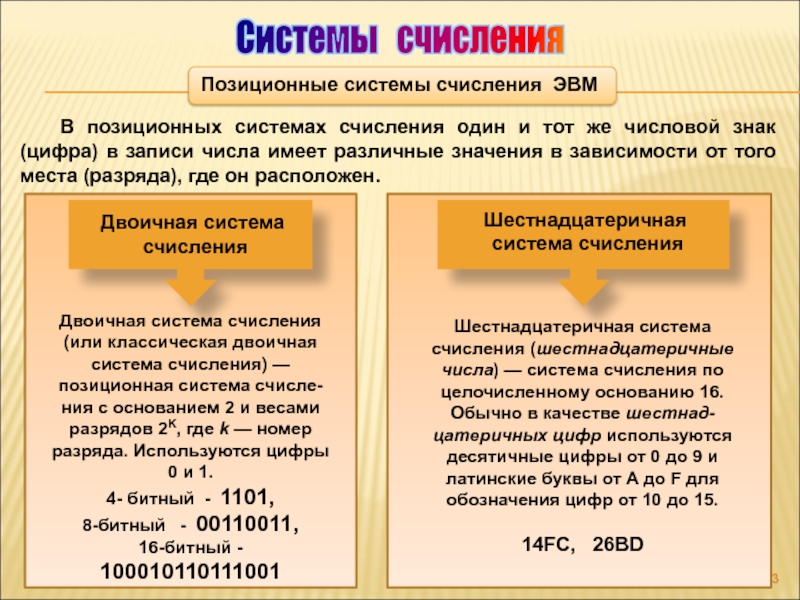

- 3. Системы счисленияПозиционные системы счисления ЭВМ В позиционных

- 4. Системы счисления Двоичная система используется в цифровых

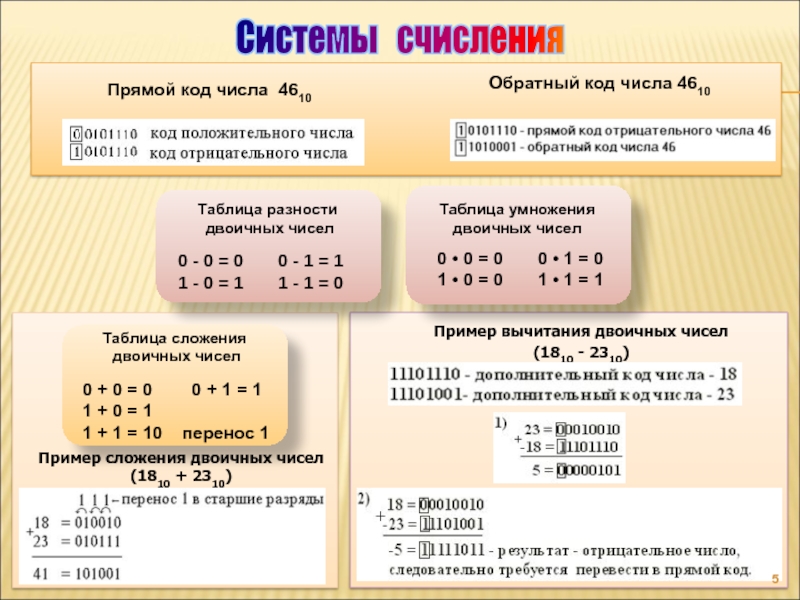

- 5. Системы счисленияПрямой код числа 4610 Обратный

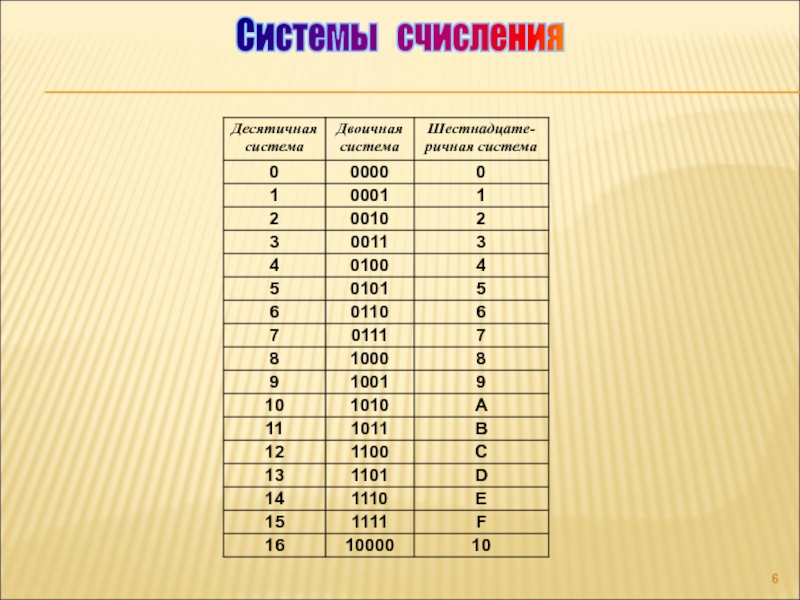

- 6. Системы счисления

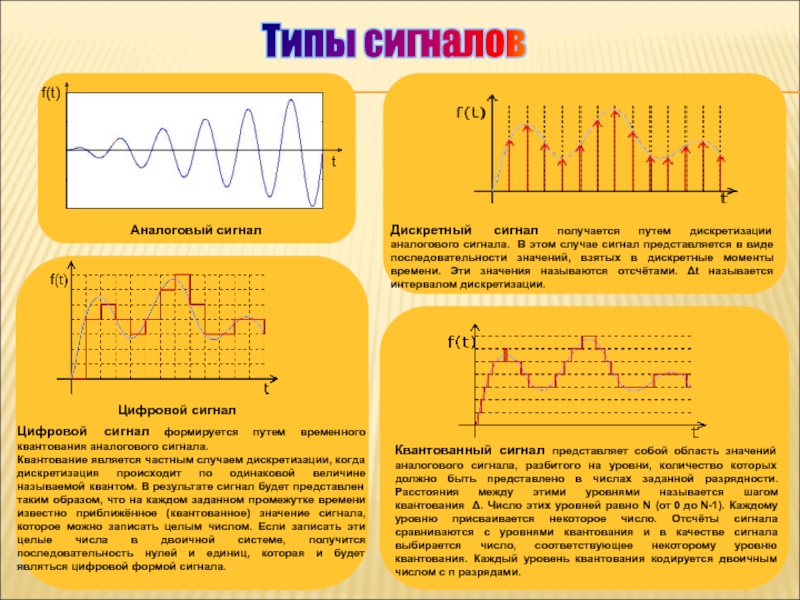

- 7. Типы сигналовДискретный сигнал получается путем дискретизации аналогового

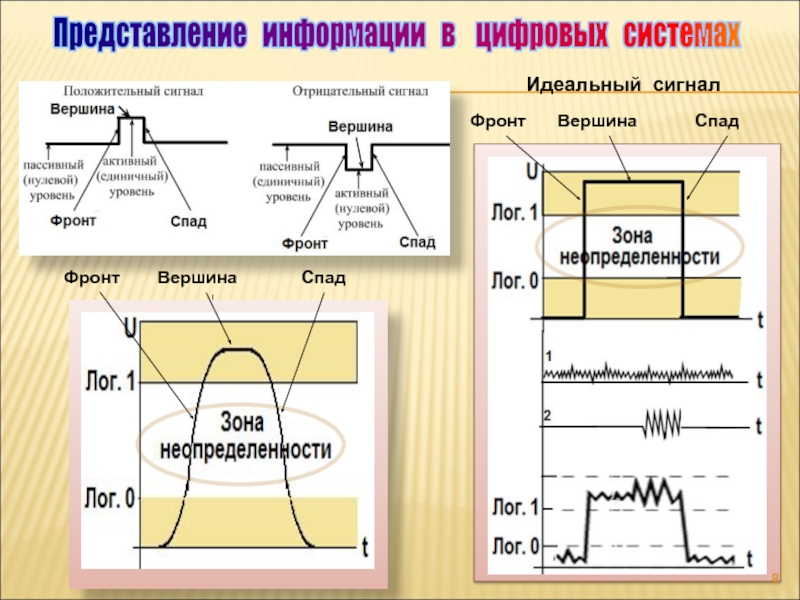

- 8. Представление информации в цифровых системахФронтВершинаСпадФронтСпадВершинаФронтСпадРеальный сигналИдеальный сигнал

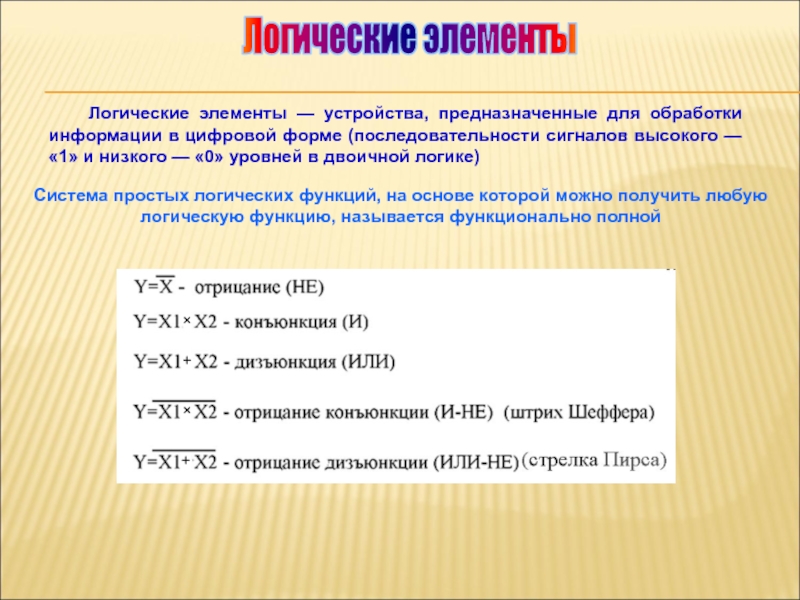

- 9. Система простых логических функций, на основе которой

- 10. Логические элементы(Отрицание) инверсия, НЕДизьюнкция (сложение), ИЛИГрафическоепредставлениеТаблицаистинностиВременныедиаграммыработы

- 11. Логические элементыКоньюнкция (умножение), ИУмножение с инверсией (штрих Шеффера), И-НЕ

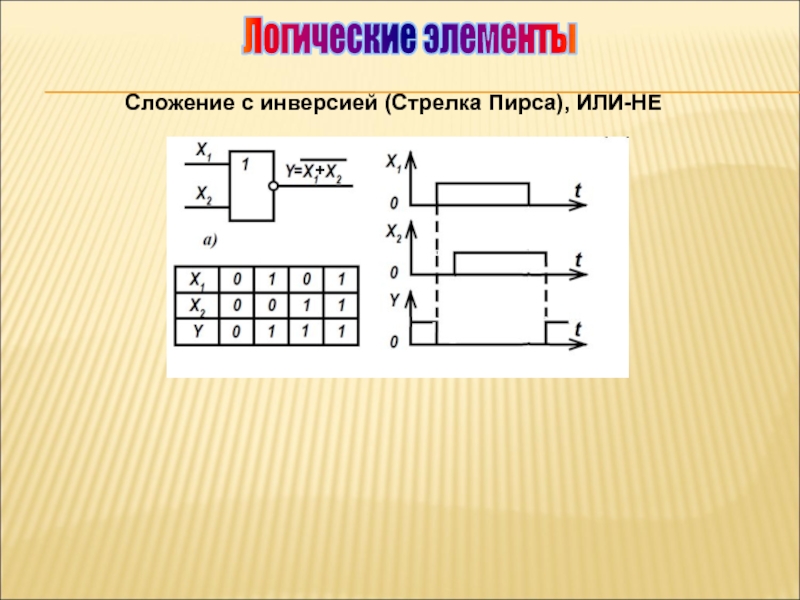

- 12. Логические элементыЛогические элементыСложение с инверсией (Стрелка Пирса), ИЛИ-НЕ

- 13. Логические элементыРеализация основных функций на элементах И-НЕ

- 14. Рассмотрим порядок составления функциональной

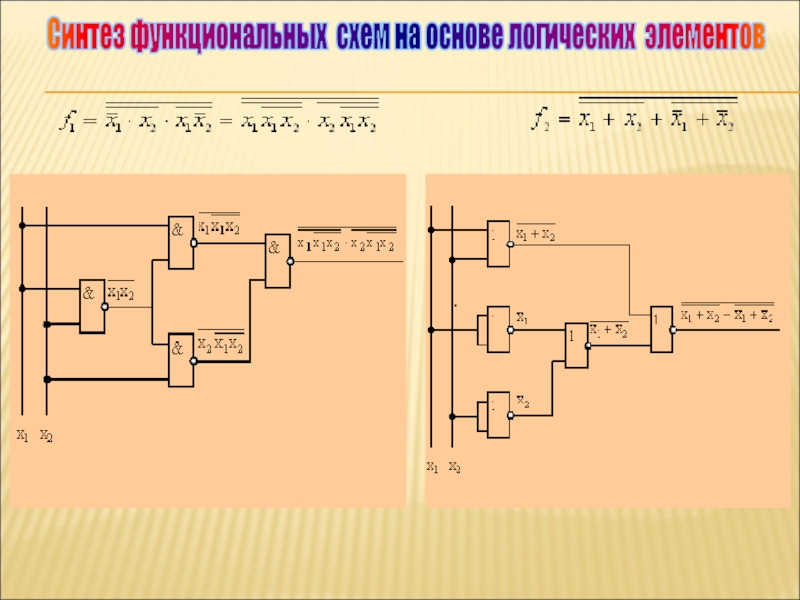

- 15. . Синтез функциональных схем на основе логических элементов

- 16. Синтез функциональных схем на основе логических элементов . . (практическое задание)

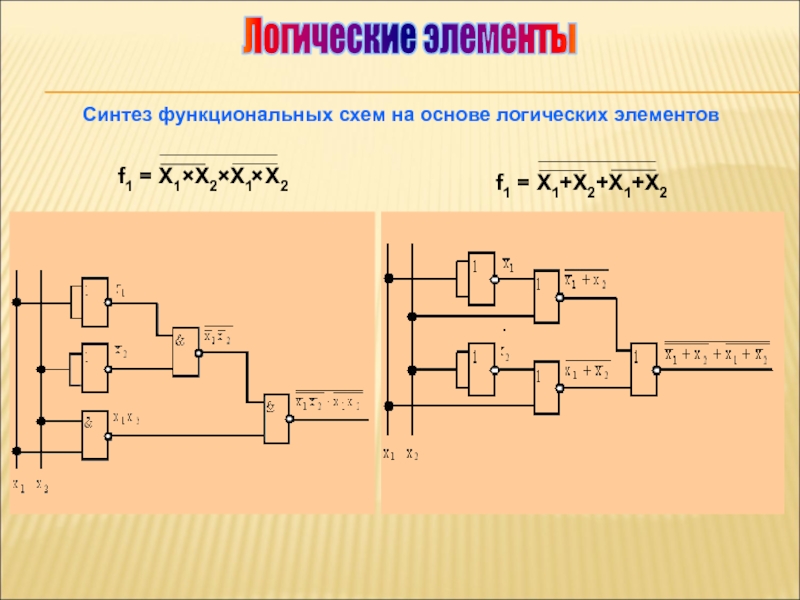

- 17. Логические элементы . . Синтез функциональных схем на основе логических элементов

- 18. Исследование работы логических элементов(практическое задание)

- 19. Сложность логической функции, а отсюда сложность и

- 20. Карта Карно для трёх переменных Карта Карно

- 21. Карты КарноАлгоритм и способы объединения (склейки) минтермов

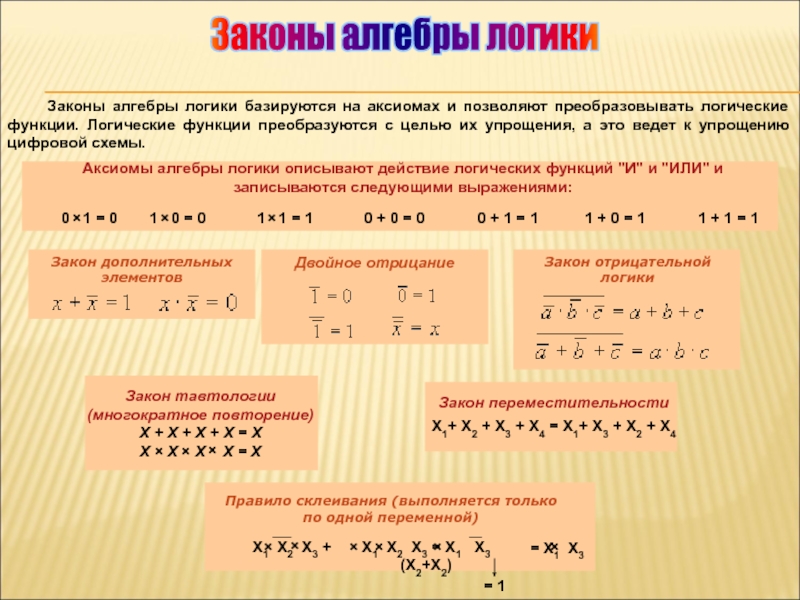

- 22. Законы алгебры логики Законы алгебры логики базируются на

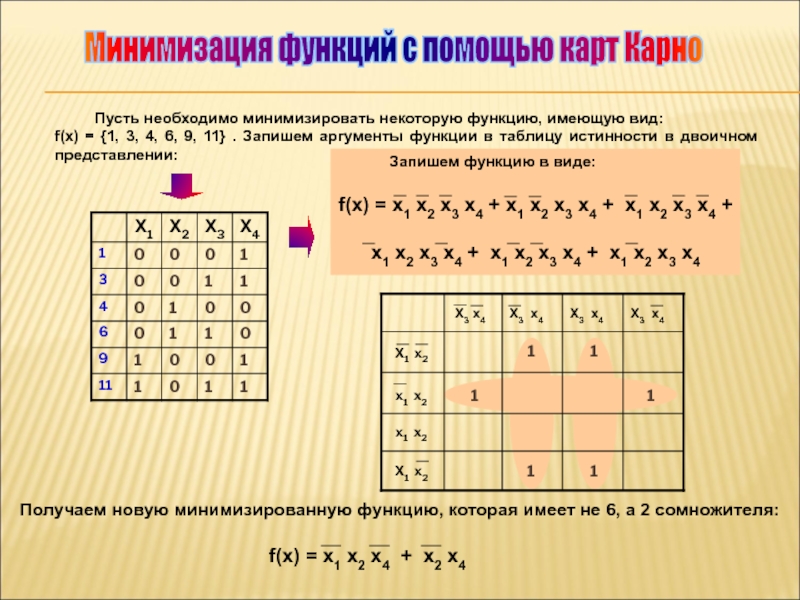

- 23. Минимизация функций с помощью карт Карно Пусть необходимо

- 24. Минимизация функций с помощью карт Карно Пусть необходимо

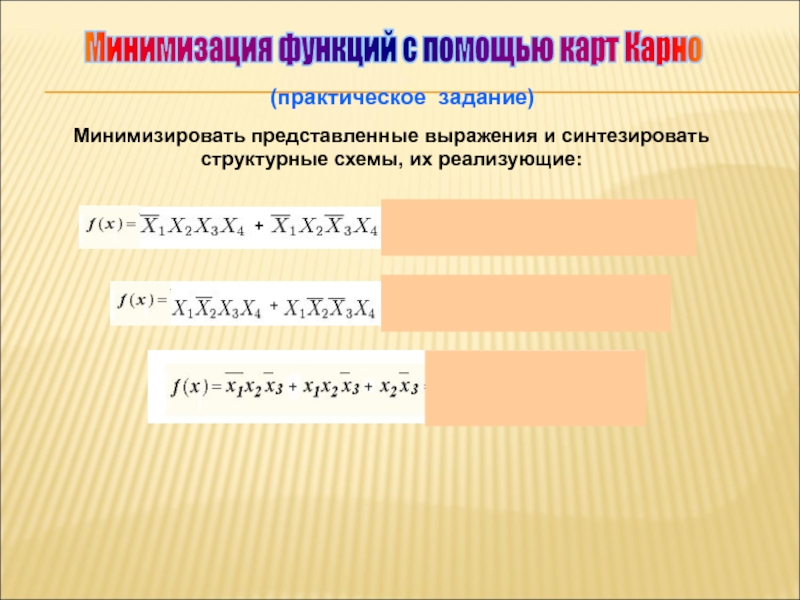

- 25. Минимизация функций с помощью карт Карно(практическое задание)Минимизировать представленные выражения и синтезироватьструктурные схемы, их реализующие:

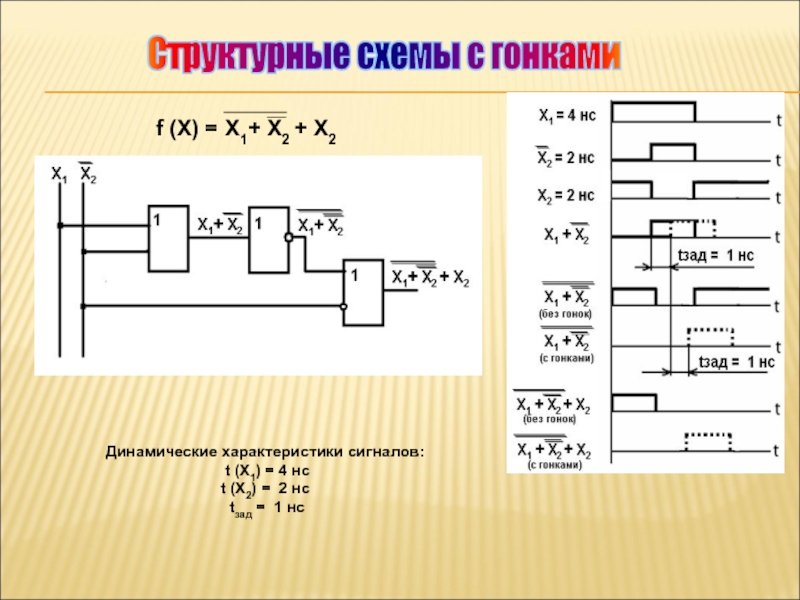

- 26. Структурные схемы с гонкамиДинамические характеристики сигналов: t

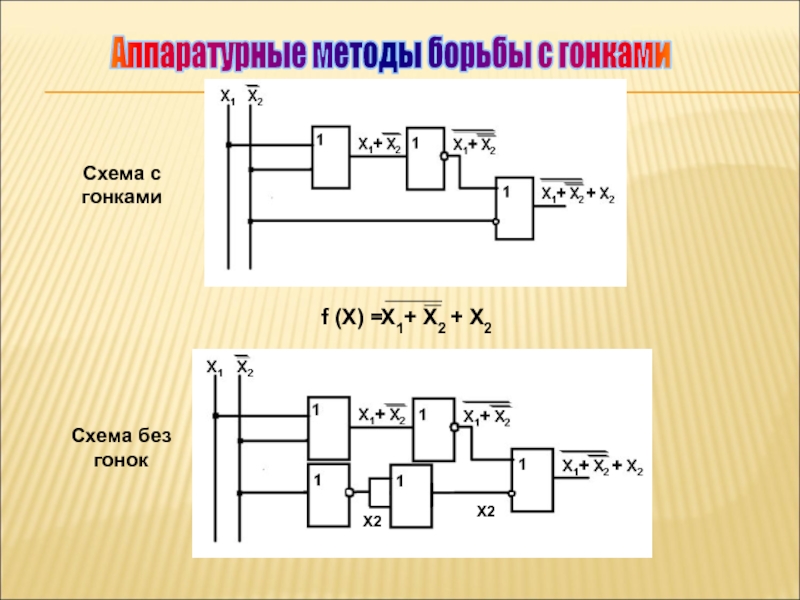

- 27. Аппаратурные методы борьбы с гонкамиСхема с гонкамиСхема без гонок

- 28. Классификация интегральных микросхем по технологии изготовленияРТЛ — резисторно-транзисторная

- 29. Обозначение логических микросхем на структурных схемах

- 30. Одновибраторы(ждущие мультивибраторы)Одновибраторы предназначены для формирования импульсов определенной

- 31. Принципы построенияодновибраторовФормирователи импульса после окончания действия запускающего сигнала

- 32. Мультивибраторы Схема имеет два динамических состояния. В первом

- 33. Формирователи импульсов Для устройств автоматики, дистанционного управления или

- 34. Генераторы синусоидальныхколебанийПроцесс установления колебаний в генераторе Трехзвенные

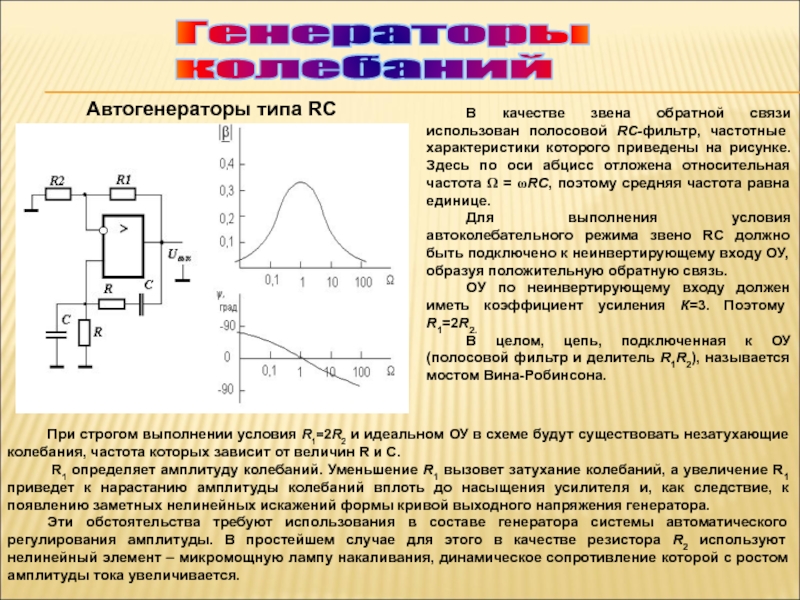

- 35. Генераторы синусоидальныхколебаний В качестве звена обратной связи использован

- 36. Генераторы синусоидальныхколебаний Основным элементом генератора является микросхема К155ЛАЗ.

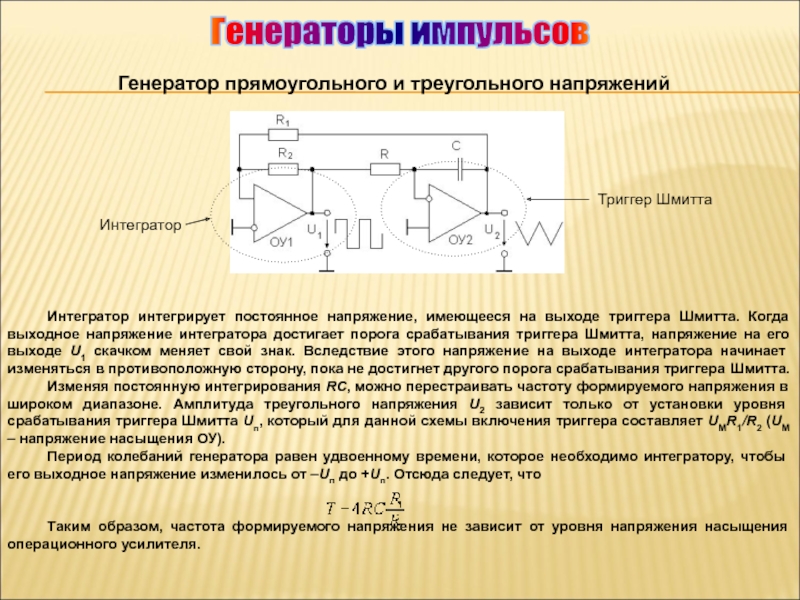

- 37. Генераторы импульсовГенератор прямоугольного и треугольного напряжений Интегратор интегрирует

- 38. Генераторы импульсовна логических элементах

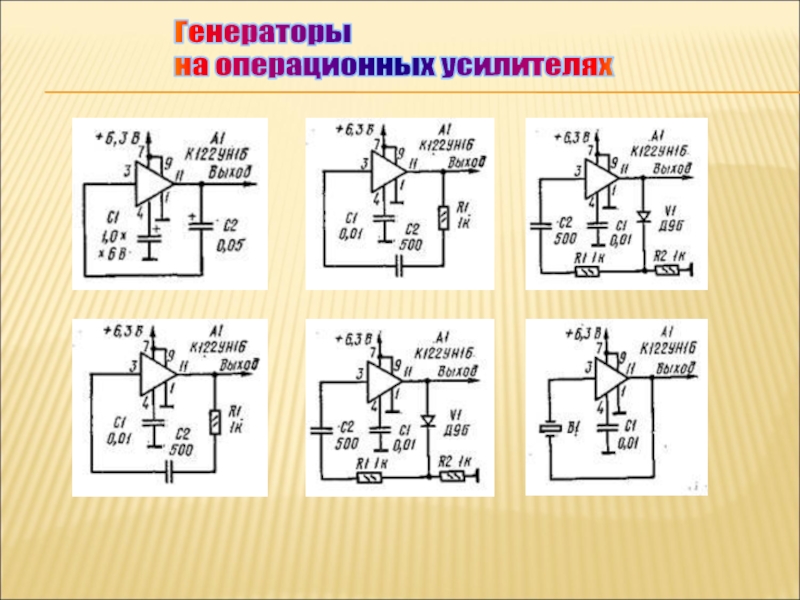

- 39. Генераторы импульсовна операционных усилителях

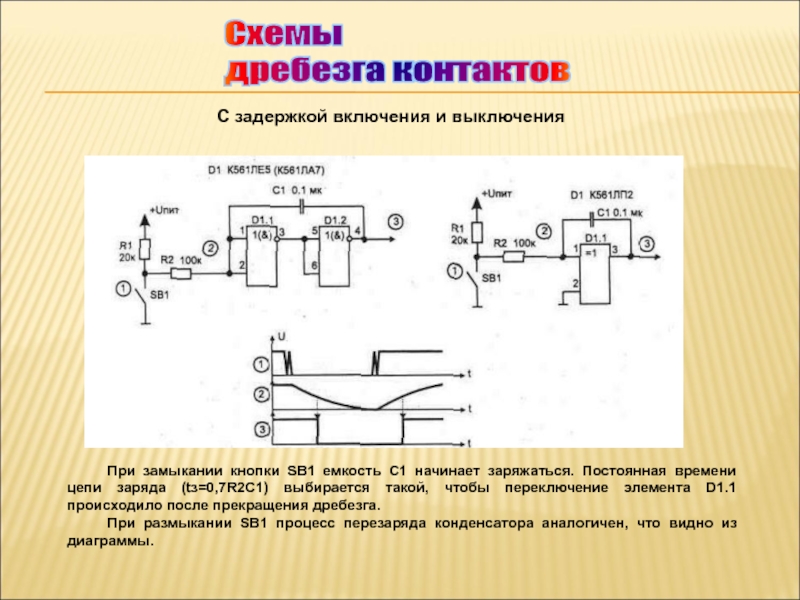

- 40. Схемы устранения дребезга контактовС задержкой включения и

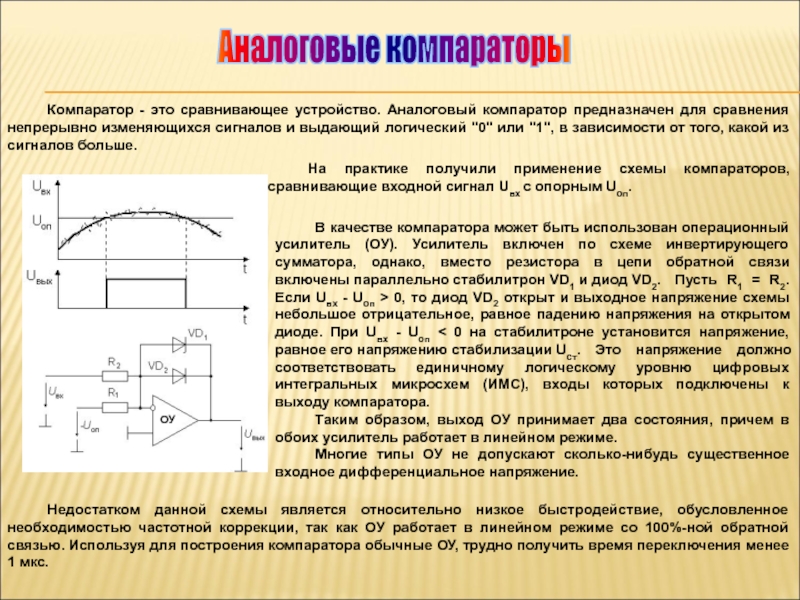

- 41. Компаратор - это сравнивающее устройство. Аналоговый компаратор

- 42. Двухпороговые аналоговые компараторыОсобенности компараторов: - Несмотря на то,

- 43. Комбинационные схемыЦИФРОВЫЕ КОМПАРАТОРЫТаблица истинности компаратора Цифровые компараторы выполняют

- 44. Комбинационные схемыЦИФРОВЫЕ МНОГОРАЗРЯДНЫЕ КОМПАРАТОРЫКомбинированный способ наращивания разрядности компаратораОрганизация N-разрядного компаратора

- 45. Комбинационные схемыСтруктурная схема сравнения 16-разрядных кодов

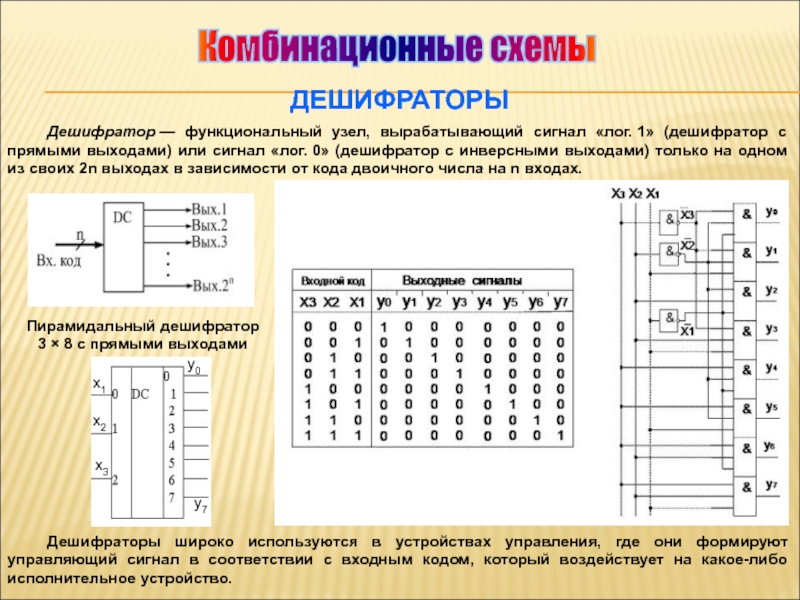

- 46. Комбинационные схемыДЕШИФРАТОРЫ Дешифратор — функциональный узел, вырабатывающий сигнал «лог. 1»

- 47. Комбинационные схемы Микросхема К155ИД3 имеет четыре информационных входа

- 48. Комбинационные схемыПаразитные импульсы в дешифраторах Как и для

- 49. Комбинационные схемыПерекоммутация входного сигнала по разным выходам

- 50. Комбинационные схемыПозиционная индикация на дешифраторе Дешифраторы, имеющие

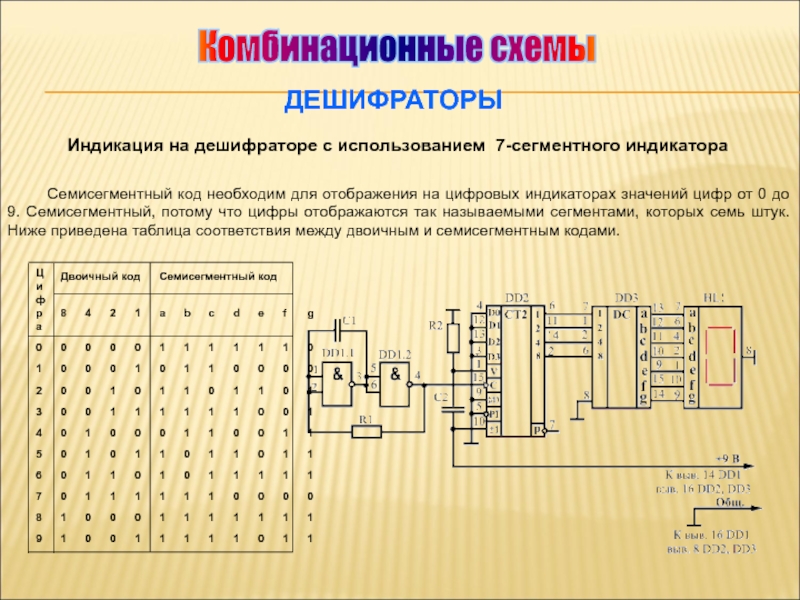

- 51. Комбинационные схемыИндикация на дешифраторе с использованием 7-сегментного

- 52. Комбинационные схемыДЕШИФРАТОРЫУвеличение разрядности дешифратора на 32 выхода

- 53. Комбинационные схемыДЕШИФРАТОРЫУвеличение разрядности дешифратора на 64 выхода

- 54. Комбинационные схемыДЕШИФРАТОРЫУвеличение разрядности дешифратора на 256 выходов

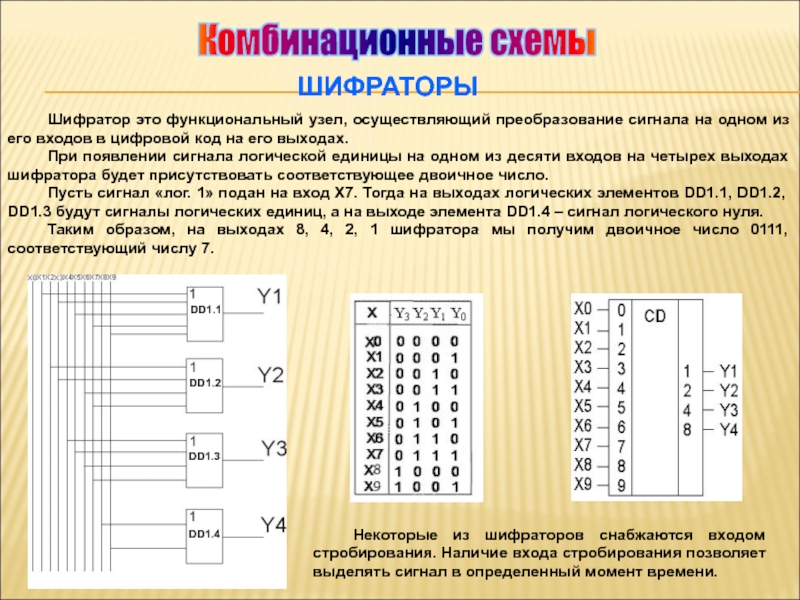

- 55. Комбинационные схемыШИФРАТОРЫ Шифратор это функциональный узел, осуществляющий преобразование

- 56. Комбинационные схемыШИФРАТОРЫ Наличие у шифраторов входов EI и

- 57. Комбинационные схемыШИФРАТОРЫПрименение шифратора для уменьшения числа передающих

- 58. Комбинационные схемыМУЛЬТИПЛЕКСОРЫ Мультиплексор - это функциональный узел, осуществляющий

- 59. Комбинационные схемыМУЛЬТИПЛЕКСОРЫ

- 60. Комбинационные схемыМУЛЬТИПЛЕКСОРЫДиаграмма сигналов

- 61. Комбинационные схемыМУЛЬТИПЛЕКСОРЫ Мультиплексор обозначается – MS. A1-A3 - адресные

- 62. Комбинационные схемыМУЛЬТИПЛЕКСОРЫ Число информационных входов реально выпускаемых промышленностью

- 63. Комбинационные схемыДЕМУЛЬТИПЛЕКСОРЫ Демультиплексорами называются устройства, которые позволяют подключать

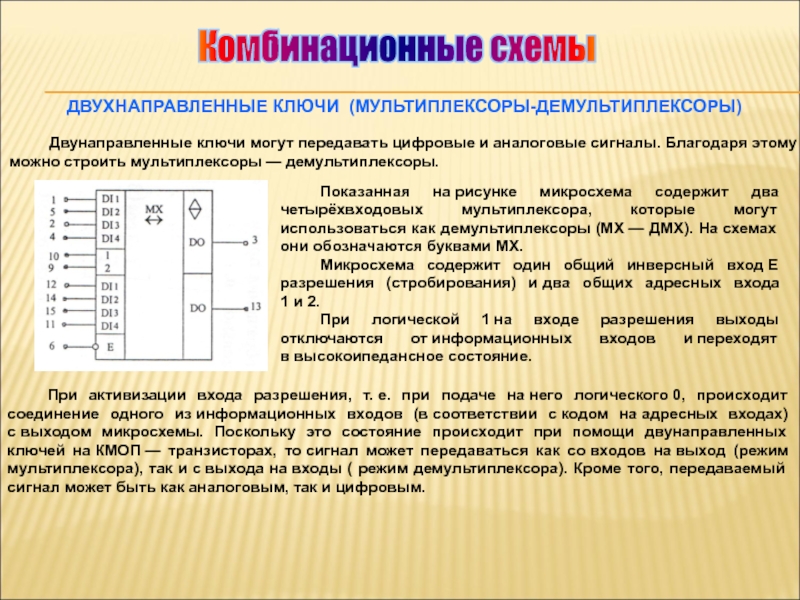

- 64. Комбинационные схемыДВУХНАПРАВЛЕННЫЕ КЛЮЧИ (МУЛЬТИПЛЕКСОРЫ-ДЕМУЛЬТИПЛЕКСОРЫ) Двунаправленные ключи могут передавать

- 65. Комбинационные схемыПреобразователи кодов Преобразователи кодов служат для преобразования

- 66. Комбинационные схемыСУММАТОРЫ Сумматоры предназначены для выполнения арифметических действий

- 67. Комбинационные схемыПолный одноразрядный сумматор на три входа

- 68. Комбинационные схемыСУММАТОРЫПараллельный n-разрядный сумматорПолный сумматор, синтезированный из двух полусумматоровОрганизация 12 - разрядного сумматораС – вход расширения

- 69. Комбинационные схемыПараллельные сумматоры с последовательным переносом При параллельном

- 70. Цифро-аналоговые преобразователи Цифро-аналоговые преобразователи предназначены для создания выходной

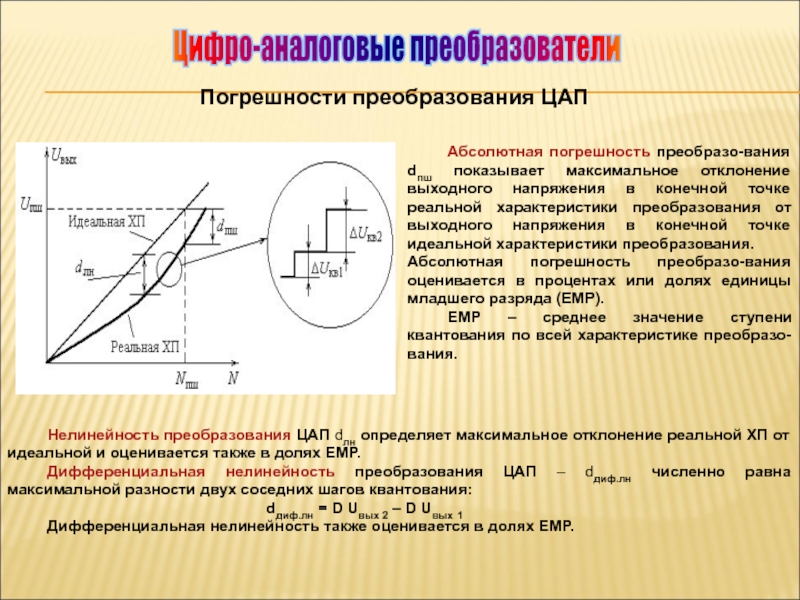

- 71. Цифро-аналоговые преобразователиПогрешности преобразования ЦАП Абсолютная погрешность преобразо-вания dпш

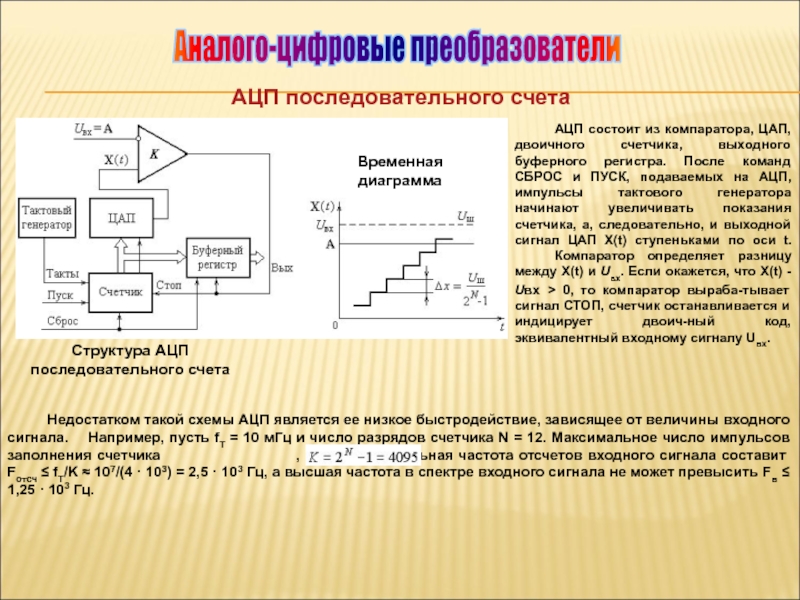

- 72. Аналого-цифровые преобразователиАЦП последовательного счета Недостатком такой схемы АЦП

- 73. Аналого-цифровые преобразователиАЦП последовательного приближения Если окажется, что Uвх

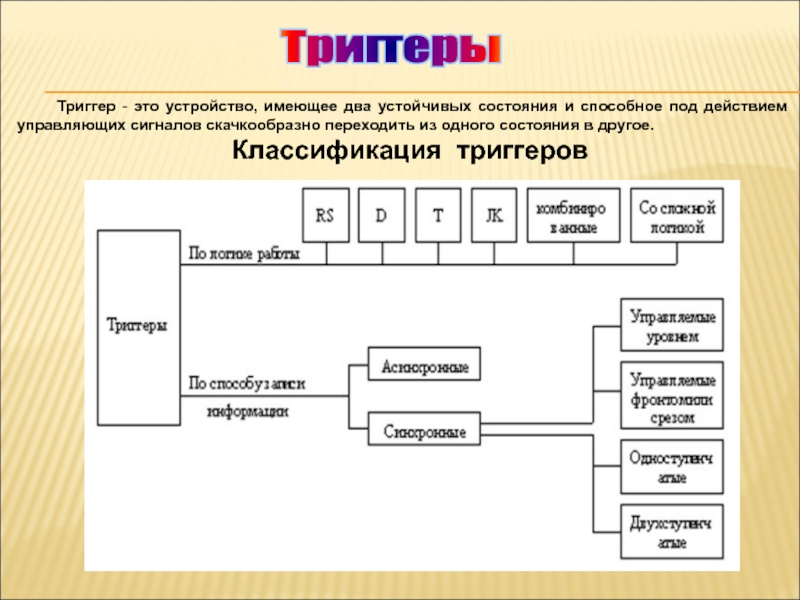

- 74. ТриггерыКлассификация триггеров Триггер - это устройство, имеющее два

- 75. При подаче единицы на вход R (от

- 76. Синхронный RS-триггер Известно, что из-за задержек переключения логических

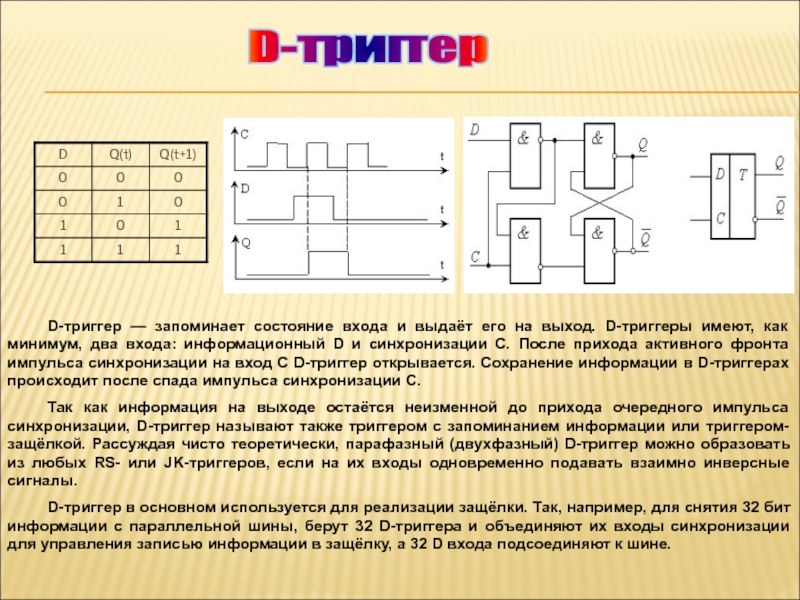

- 77. D-триггер D-триггер — запоминает состояние входа и выдаёт

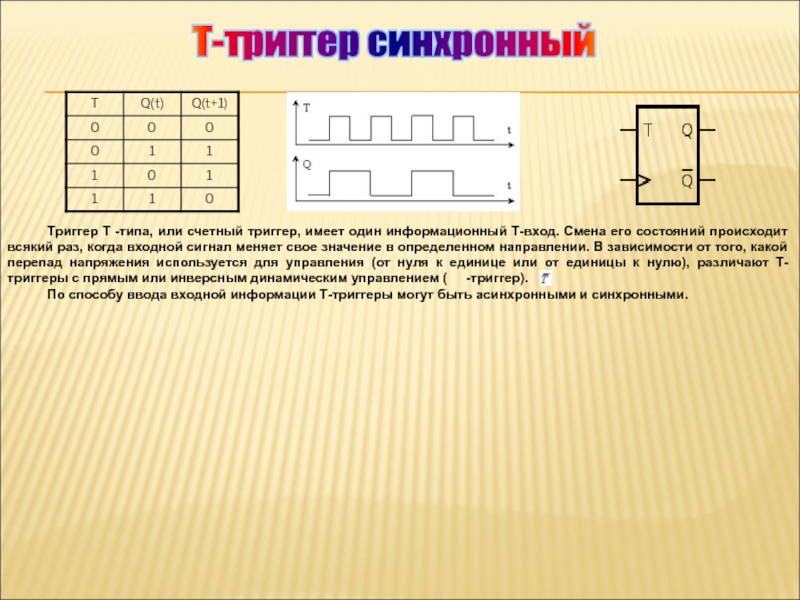

- 78. T-триггер синхронный Триггер Т -типа, или счетный триггер,

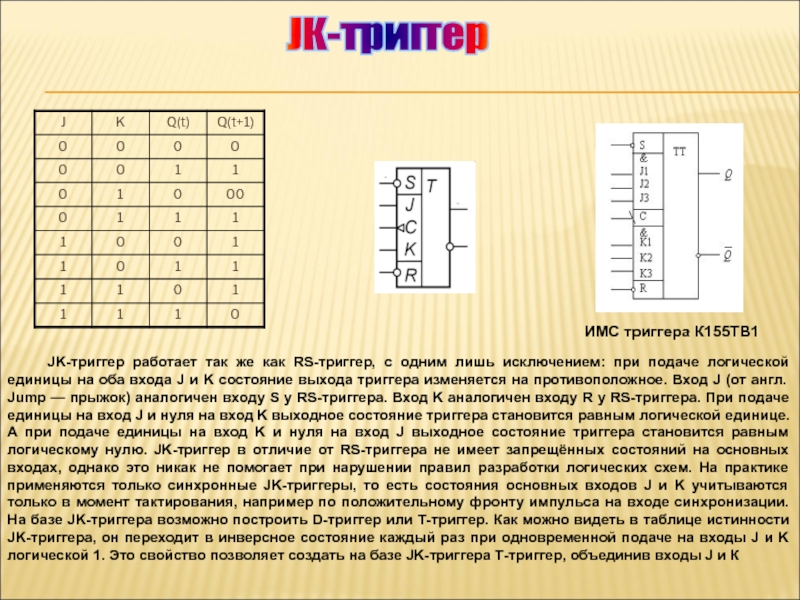

- 79. JK-триггер JK-триггер работает так же как RS-триггер, с

- 80. JK-триггерИспользование JK-триггера в качестве: D-триггераасинхронного T-триггерасинхронного T-триггера

- 81. Счетчики Счетчиком называется устройство, предназначенное для подсчета числа

- 82. СчетчикиПоследовательные счетчики Счетчик может работать как суммирующий, так

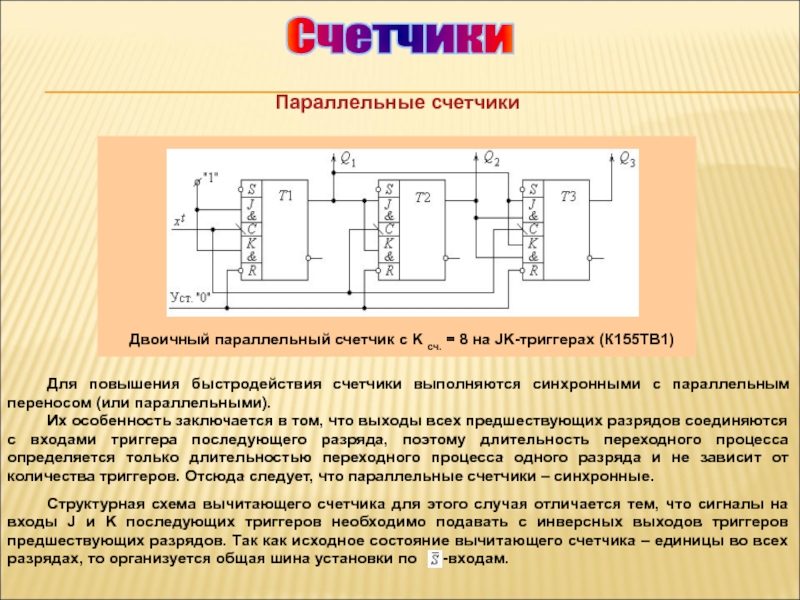

- 83. СчетчикиПараллельные счетчики Для повышения быстродействия счетчики выполняются синхронными

- 84. СчетчикиРеверсивные счетчики Реверсивный счетчик должен, в зависимости от

- 85. Регистры Цифровые регистры - это устройства, предназначенные для

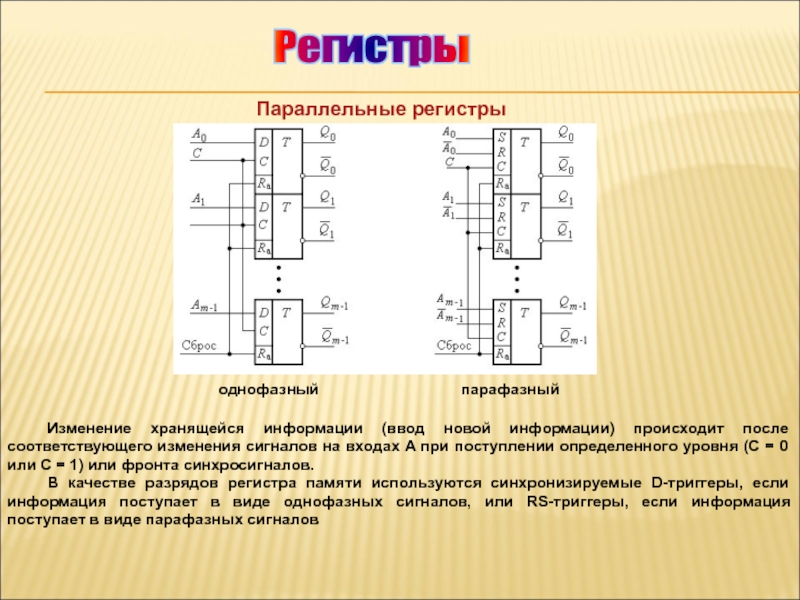

- 86. РегистрыПараллельные регистрыоднофазный

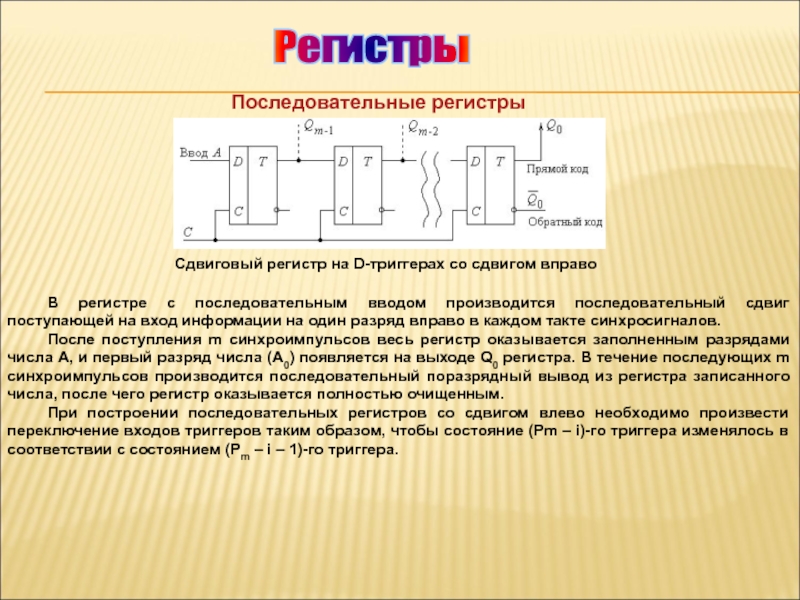

- 87. РегистрыПоследовательные регистрыСдвиговый регистр на D-триггерах со сдвигом

- 88. РегистрыРеверсивные регистры Для построения реверсивного сдвигового регистра необходимо

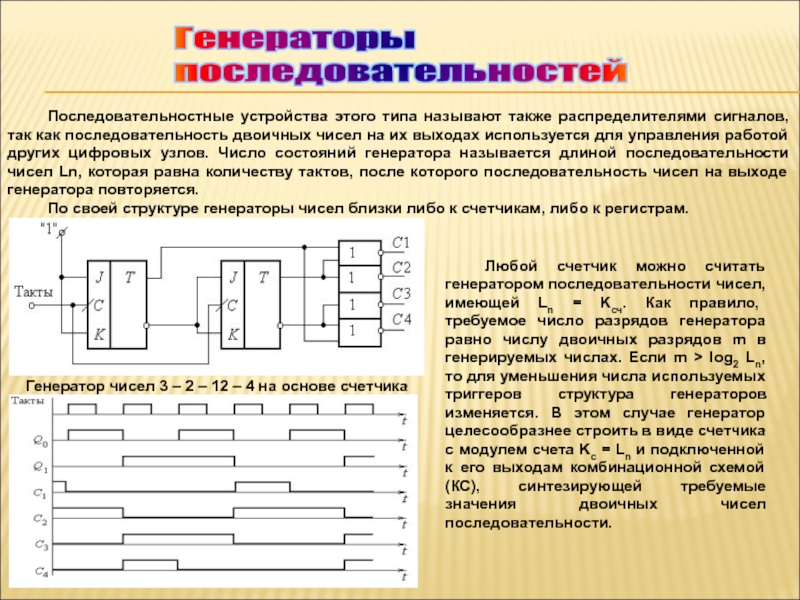

- 89. Генераторы числовых последовательностей Последовательностные устройства этого типа называют

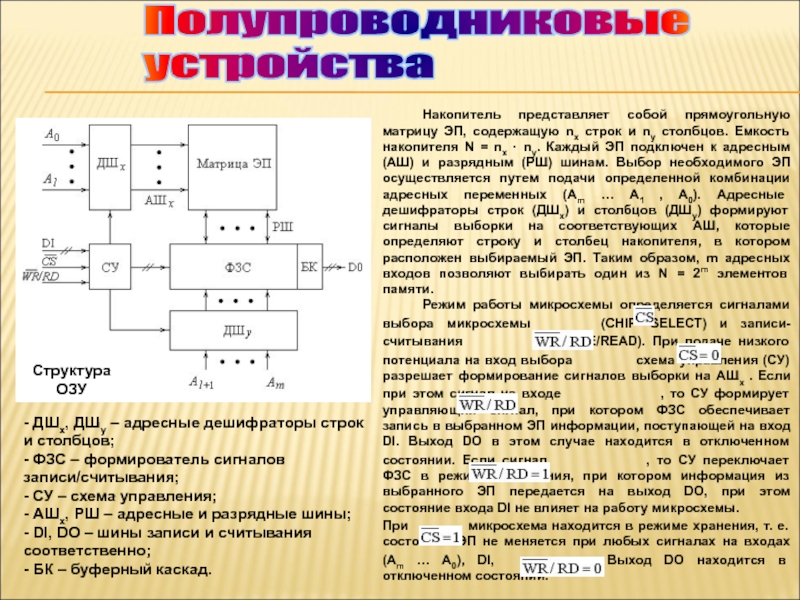

- 90. Полупроводниковые запоминающиеустройстваСтруктура ОЗУ- ДШх, ДШу – адресные

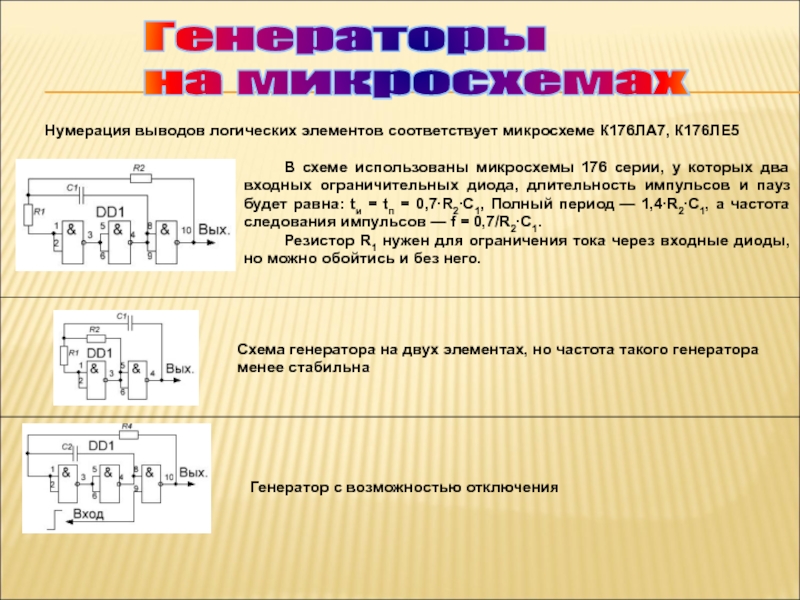

- 91. Генераторы импульсных сигналов на микросхемах В схеме

- 92. Генераторы импульсных сигналов на микросхемах Схема с

- 93. Схема подключения двух индикаторов с общим анодомСхема подключения семисегментныхиндикаторов

- 94. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2Системы счисления

Позиционная

Смешанные

Непозиционные

Факториальная

Майя

Биномиальная

Римская

СОК

Десятичная

Двоичная

Шестнадцатеричная

Шестидесятеричная

Фибоначчиева

V — 5, X — 10, L

— 50,

C — 100, D — 500, M — 1000

Троичная

Слайд 3Системы счисления

Позиционные системы счисления ЭВМ

В позиционных системах счисления один

и тот же числовой знак (цифра) в записи числа имеет

различные значения в зависимости от того места (разряда), где он расположен.Двоичная система счисления (или классическая двоичная система счисления) — позиционная система счисле-ния с основанием 2 и весами разрядов 2K, где k — номер разряда. Используются цифры 0 и 1.

4- битный - 1101,

8-битный - 00110011,

16-битный - 100010110111001

Шестнадцатеричная система счисления (шестнадцатеричные числа) — система счисления по целочисленному основанию 16.

Обычно в качестве шестнад-цатеричных цифр используются десятичные цифры от 0 до 9 и латинские буквы от A до F для обозначения цифр от 10 до 15.

14FC, 26BD

Двоичная система

счисления

Шестнадцатеричная

система счисления

Слайд 4Системы счисления

Двоичная система используется в цифровых системах, поскольку является

наиболее простой и удовлетворяет требованиям:

- чем меньше значений существует в

системе, тем проще изготовить отдельные элементы, оперирующие этими значениями. В частности, две цифры двоичной системы счисления могут быть легко представлены многими физическими явлениями: есть ток — нет тока, индукция магнитного поля больше пороговой величины или нет и т. д. - чем меньше количество состояний у элемента, тем выше помехоустойчивость и тем быстрее он может работать. Например, чтобы закодировать три состояния через величину индукции магнитного поля, потребуется ввести два пороговых значения, что не будет способствовать помехоустойчивости и надёжности хранения информации.

- двоичная арифметика является довольно простой. Простыми являются таблицы сложения и умножения — основных действий над числами.

- возможно применение аппарата алгебры логики для выполнения логических и побитовых операций над числами (сложение, вычитание, умножение, отрицание, ограничение, обощение, деление).

Двоичная система счисления

Четырехразрядный

формат чисел

1101101 (0…255)

2n, где n – 1…8

1000101110110101 (0…65535)

2n, где n – 1…16

Шестнадцатиразрядный

формат чисел

Восьмиразрядный

формат чисел

1101 (0…15)

2n, где n - 1….4

Слайд 5Системы счисления

Прямой код числа 4610

Обратный код числа 4610

Пример

сложения двоичных чисел (1810 + 2310)

Пример вычитания двоичных чисел

(1810 - 2310)

0 + 0 = 0 0 + 1 = 1

1 + 0 = 1

1 + 1 = 10 перенос 1

Таблица сложения

двоичных чисел

Таблица разности

двоичных чисел

0 - 0 = 0 0 - 1 = 1

1 - 0 = 1 1 - 1 = 0

Таблица умножения

двоичных чисел

0 • 0 = 0 0 • 1 = 0

1 • 0 = 0 1 • 1 = 1

Слайд 7Типы сигналов

Дискретный сигнал получается путем дискретизации аналогового сигнала. В этом

случае сигнал представляется в виде последовательности значений, взятых в дискретные

моменты времени. Эти значения называются отсчётами. Δt называется интервалом дискретизации.Цифровой сигнал формируется путем временного квантования аналогового сигнала.

Квантование является частным случаем дискретизации, когда дискретизация происходит по одинаковой величине называемой квантом. В результате сигнал будет представлен таким образом, что на каждом заданном промежутке времени известно приближённое (квантованное) значение сигнала, которое можно записать целым числом. Если записать эти целые числа в двоичной системе, получится последовательность нулей и единиц, которая и будет являться цифровой формой сигнала.

Цифровой сигнал

Квантованный сигнал представляет собой область значений аналогового сигнала, разбитого на уровни, количество которых должно быть представлено в числах заданной разрядности. Расстояния между этими уровнями называется шагом квантования Δ. Число этих уровней равно N (от 0 до N-1). Каждому уровню присваивается некоторое число. Отсчёты сигнала сравниваются с уровнями квантования и в качестве сигнала выбирается число, соответствующее некоторому уровню квантования. Каждый уровень квантования кодируется двоичным числом с n разрядами.

Аналоговый сигнал

f(t)

t

Слайд 8Представление информации в цифровых системах

Фронт

Вершина

Спад

Фронт

Спад

Вершина

Фронт

Спад

Реальный сигнал

Идеальный

сигнал

Слайд 9Система простых логических функций, на основе которой можно получить любую

логическую функцию, называется функционально полной

Логические элементы

Логические элементы — устройства, предназначенные

для обработки информации в цифровой форме (последовательности сигналов высокого — «1» и низкого — «0» уровней в двоичной логике)Слайд 10Логические элементы

(Отрицание) инверсия, НЕ

Дизьюнкция (сложение), ИЛИ

Графическое

представление

Таблица

истинности

Временные

диаграммы

работы

Слайд 14 Рассмотрим порядок составления функциональной схемы по заданной

логической функции

1-й этап - получить отрицание от переменных х1, х2, х3.2-й этап - получить дизъюнкцию , конъюнкции и .

3-й этап - получить конъюнкцию х1( ).

Функциональная схема

Синтез функциональных схем на основе логических элементов

Слайд 19 Сложность логической функции, а отсюда сложность и стоимость реализующей ее

КС, пропорциональны числу логических операций и числу вхождений переменных или

их отрицаний. В принципе любая функция может быть упрощена непосредственно с помощью аксиом и теорем логики, но, как правило, такие преобразования требуют громоздких выкладок.Наиболее часто применяемым методом упрощения (минимизации) ПФ является метод карт Карно.

Карты Карно — графический способ минимизации линейных функций, обеспечивающий относительную простоту работы с большими выражениями и устранение потенциальных гонок. Минимизация необходима для построения комбинационных схем цифровых автоматов минимальной сложности. Она представляет собой операции попарного неполного склеивания и элементарного поглощения. Карты Карно рассматриваются как перестроенная соответствующим образом таблица истинности функции.

Карты Карно были изобретены в 1952 Эдвардом В. Вейчем и усовершенствованы в 1953 Морисом Карно, физиком из «Bell Labs», и были призваны помочь упростить цифровые электронные схемы.

Карты Карно

Исходной информацией для работы с картой Карно является таблица истинности минимизируемой функции. Таблица истинности содержит полную информацию о логической функции, задавая её значения на всех возможных 2N наборах входных переменных X1 ... XN. Карта Карно также содержит 2N клеток, каждая из которых ассоциируется с уникальным набором входных переменных X1 ... XN. Таким образом, между таблицей истинности и картой Карно имеется взаимно однозначное соответствие, и карту Карно можно считать соответствующим образом отформатированной таблицей истинности.

Карта Карно может быть составлена для любого количества переменных, однако удобно работать при количестве переменных не более пяти. По сути Карта Карно — это таблица истинности составленная в 2-х мерном виде.

Слайд 20Карта Карно для трёх переменных

Карта Карно для двух переменных

0

1

X1

1

0

X1

X2

X2

X1 x2

x1 x2

1

x1 x2

1

X1 x2

X3 x4

X3 x4

X3 x4

x3 x4

1

1

1

1

1

Карта Карно

для четырех переменных Если функция имеет запрещённые наборы входных переменных, при которых функция может иметь произвольное значение (0 либо 1), то такая функция называется неопределённой. Для удобства минимизации её следует доопределить, то есть неопре-делённые значения карты Карно произволь-ным образом заменить «1» либо «0».

Карты Карно

Слайд 21Карты Карно

Алгоритм и способы объединения (склейки) минтермов карт Карно

-объединяются смежные

клетки, содержащие единицы в область, так чтобы одна область содержала

2n (где n - целое число) клеток (крайние строки и столбцы являются соседними между собой), в области не должно находиться клеток содержащих нули;-область должна располагаться симметрично оси(ей);

-не смежные области, расположенные симметрично оси(ей) могут объединяться в одну;

-область должна быть как можно больше, а количество областей как можно меньше;

-области могут пересекаться;

-возможно несколько вариантов накрытия.

При склейке должно быть минимум числа объединений единиц и максимум единиц, составляющих каждое объединение.

Слайд 22Законы алгебры логики

Законы алгебры логики базируются на аксиомах и позволяют

преобразовывать логические функции. Логические функции преобразуются с целью их упрощения,

а это ведет к упрощению цифровой схемы.Закон тавтологии

(многократное повторение)

X + X + X + X = X

X × X X X = X

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 1

Аксиомы алгебры логики описывают действие логических функций "И" и "ИЛИ" и записываются следующими выражениями:

= 1

×

×

Слайд 23Минимизация функций с помощью карт Карно

Пусть необходимо минимизировать функцию, имеющую

вид: f(x) = {1, 2, 6, 12, 13}.

Составляем таблицу

истинности путем записи аргументов функции в нее в двоичном представлении:Данные из таблицы истинности запишем в виде:

f(x) = x1 x2 x3 x4 + x1 x2 x3 x4 + x1 x2 x3 x4 + x1 x2 x3 x4 + x1 x2 x3 x4

Вставляем в карту Карно минтермы «1» («0» не записываем)

и объединяем их в карте Карно, имеющей 4 строки и 4 столбца:

Получаем новую минимизированную функцию, которая имеет не 5, а 3 сомножителя:

x1 x2 x3 x4

f(x) = x1 x2 x3 x4 + x1 x3 x4 + x1 x2 x3

x1x3 x4

(Х2 и Х2 сокращаются)

(Х4 и Х4 сокращаются)

Слайд 24Минимизация функций с помощью карт Карно

Пусть необходимо минимизировать некоторую функцию,

имеющую вид:

f(x) = {1, 3, 4, 6, 9, 11} .

Запишем аргументы функции в таблицу истинности в двоичном представлении:f(x) = x1 x2 x3 x4 + x1 x2 x3 x4 + x1 x2 x3 x4 +

x1 x2 x3 x4 + x1 x2 x3 x4 + x1 x2 x3 x4

Получаем новую минимизированную функцию, которая имеет не 6, а 2 сомножителя:

Запишем функцию в виде:

X1 x2

x1 x2

1

x1 x2

1

X1 x2

X3 x4

X3 x4

X3 x4

X3 x4

1

1

1

1

f(x) = x1 x2 x4 + х2 x4

Слайд 25Минимизация функций с помощью карт Карно

(практическое задание)

Минимизировать представленные выражения и

синтезировать

структурные схемы, их реализующие:

Слайд 26Структурные схемы с гонками

Динамические характеристики сигналов:

t (X1) = 4

нс

t (X2) = 2 нс

tзад = 1 нс

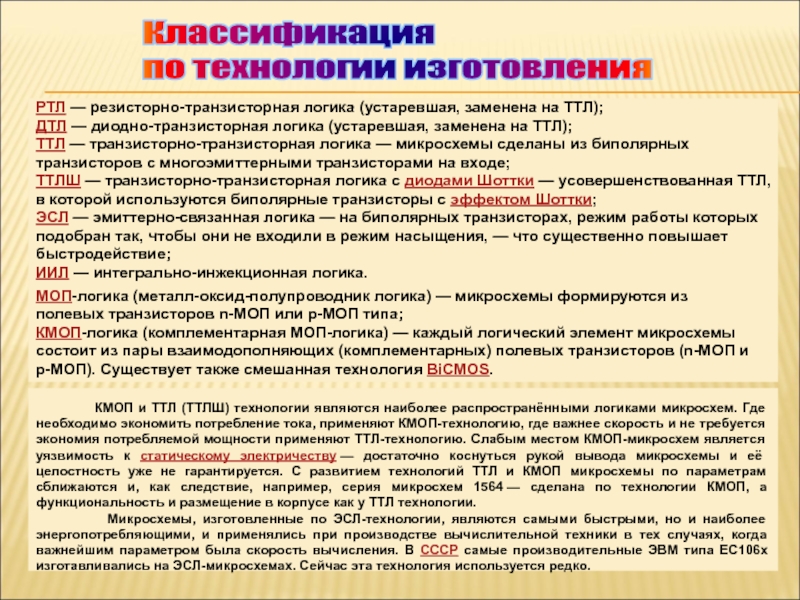

Слайд 28Классификация интегральных микросхем

по технологии изготовления

РТЛ — резисторно-транзисторная логика (устаревшая, заменена

на ТТЛ);

ДТЛ — диодно-транзисторная логика (устаревшая, заменена на ТТЛ);

ТТЛ —

транзисторно-транзисторная логика — микросхемы сделаны из биполярных транзисторов с многоэмиттерными транзисторами на входе; ТТЛШ — транзисторно-транзисторная логика с диодами Шоттки — усовершенствованная ТТЛ, в которой используются биполярные транзисторы с эффектом Шоттки;

ЭСЛ — эмиттерно-связанная логика — на биполярных транзисторах, режим работы которых подобран так, чтобы они не входили в режим насыщения, — что существенно повышает быстродействие;

ИИЛ — интегрально-инжекционная логика.

МОП-логика (металл-оксид-полупроводник логика) — микросхемы формируются из полевых транзисторов n-МОП или p-МОП типа;

КМОП-логика (комплементарная МОП-логика) — каждый логический элемент микросхемы состоит из пары взаимодополняющих (комплементарных) полевых транзисторов (n-МОП и p-МОП). Существует также смешанная технология BiCMOS.

КМОП и ТТЛ (ТТЛШ) технологии являются наиболее распространёнными логиками микросхем. Где необходимо экономить потребление тока, применяют КМОП-технологию, где важнее скорость и не требуется экономия потребляемой мощности применяют ТТЛ-технологию. Слабым местом КМОП-микросхем является уязвимость к статическому электричеству — достаточно коснуться рукой вывода микросхемы и её целостность уже не гарантируется. С развитием технологий ТТЛ и КМОП микросхемы по параметрам сближаются и, как следствие, например, серия микросхем 1564 — сделана по технологии КМОП, а функциональность и размещение в корпусе как у ТТЛ технологии.

Микросхемы, изготовленные по ЭСЛ-технологии, являются самыми быстрыми, но и наиболее энергопотребляющими, и применялись при производстве вычислительной техники в тех случаях, когда важнейшим параметром была скорость вычисления. В СССР самые производительные ЭВМ типа ЕС106х изготавливались на ЭСЛ-микросхемах. Сейчас эта технология используется редко.

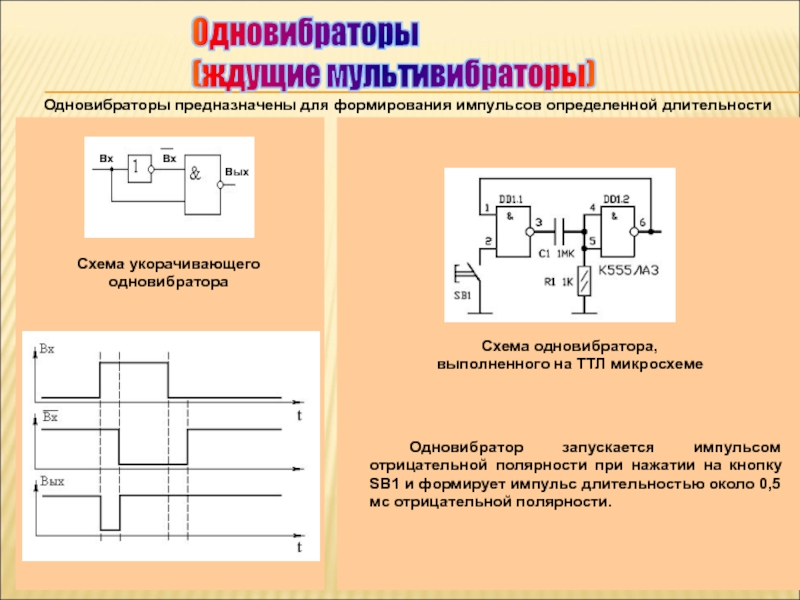

Слайд 30Одновибраторы

(ждущие мультивибраторы)

Одновибраторы предназначены для формирования импульсов определенной длительности

Схема укорачивающего

одновибратора

Схема одновибратора,

выполненного на ТТЛ микросхеме

Одновибратор запускается импульсом отрицательной

полярности при нажатии на кнопку SB1 и формирует импульс длительностью около 0,5 мс отрицательной полярности. Слайд 31Принципы построения

одновибраторов

Формирователи импульса после окончания действия

запускающего сигнала

Слайд 32Мультивибраторы

Схема имеет два динамических состояния. В первом из них, когда

на выходе D1.1 состояние лог. "1" (выход D1.2 лог. "0"),

конденсатор С1 заряжается. В процессе заряда напряжение на входе инвертора D1.1 возрастает, и при достижении значения Uпор=0,5Uпит происходит скачкообразный переход во второе динамическое состояние, в котором на выходах D1.1 лог. "О", D1.2 - "1". В этом состоянии происходит перезаряд емкости (разряд) током обратного направления. При достижении напряжения на С1 Unop происходит возврат схемы в первое динамическое состояние.Диаграмма напряжений поясняет работу. Резистор R2 является ограничительным, и его сопротивление не должно быть меньше 1 кОм, а чтобы он не влиял на расчетную частоту, номинал резистора R1 выбираем значительно больше R2 (R2<0,01R1). Ограничительный резистор (R2) иногда устанавливают последовательно с конденсатором.

Мультивибратор — релаксационный генератор сигналов электрических прямоу-гольных колебаний с короткими фронтами.

Существуют три типа схем мультивибратора в зависимости от режима работы:

- нестабильный, или автоколебательный: схема самопроизвольно переходит из одного состояния в другое.

- моностабильный: одно из состояний является стабильным, но другое состояния неустойчиво (переходное). Мультивибратор на некоторое время, определяемое параметрами его компонентов переходит в неустойчивое состояние под действием запускающего импульса. Затем возвращается в устойчивое состояния до прихода очередного запускающего импульса.

Такие мультивибраторы используются для формирования импульса с фиксированной длительностью, не зависящей от длительности запускающего импульса.

Такой тип мультивибраторов иногда, в литературе, называют одновибраторы или ждущие мультивибраторы.

- бистабильный: схема устойчива в любом состоянии. Схема может быть переключена из одного состояния в другое с помощью внешних импульсов.

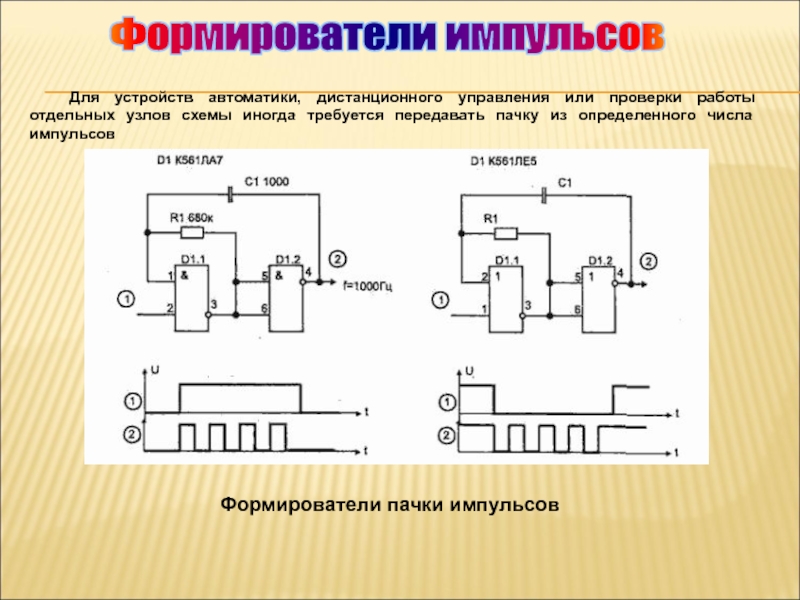

Слайд 33Формирователи импульсов

Для устройств автоматики, дистанционного управления или проверки работы отдельных

узлов схемы иногда требуется передавать пачку из определенного числа импульсов

Формирователи пачки импульсов

Слайд 34Генераторы синусоидальных

колебаний

Процесс установления

колебаний в генераторе

Трехзвенные фазосдвигающие

RС цепи

(а,б) и схема моста Вина (в)

Слайд 35Генераторы синусоидальных

колебаний

В качестве звена обратной связи использован полосовой RC-фильтр, частотные

характеристики которого приведены на рисунке. Здесь по оси абцисс отложена

относительная частота W = wRC, поэтому средняя частота равна единице.Для выполнения условия автоколебательного режима звено RC должно быть подключено к неинвертирующему входу ОУ, образуя положительную обратную связь.

ОУ по неинвертирующему входу должен иметь коэффициент усиления К=3. Поэтому R1=2R2.

В целом, цепь, подключенная к ОУ (полосовой фильтр и делитель R1R2), называется мостом Вина-Робинсона.

При строгом выполнении условия R1=2R2 и идеальном ОУ в схеме будут существовать незатухающие колебания, частота которых зависит от величин R и C.

R1 определяет амплитуду колебаний. Уменьшение R1 вызовет затухание колебаний, а увеличение R1 приведет к нарастанию амплитуды колебаний вплоть до насыщения усилителя и, как следствие, к появлению заметных нелинейных искажений формы кривой выходного напряжения генератора.

Эти обстоятельства требуют использования в составе генератора системы автоматического регулирования амплитуды. В простейшем случае для этого в качестве резистора R2 используют нелинейный элемент – микромощную лампу накаливания, динамическое сопротивление которой с ростом амплитуды тока увеличивается.

Автогенераторы типа RC

Слайд 36Генераторы синусоидальных

колебаний

Основным элементом генератора является микросхема К155ЛАЗ. Кольцевое соединение трёх

инверторов DD1.1...DD1.3 представляет собой неустойчивую структуру, склонную к возбуждению на

максимальной рабочей частоте.Резистор R1 задаёт рабочую точку микросхемы вблизи порога переключения. Благодаря наличию у ТТЛ-схем "мёртвой зоны" (диапазона напряжений между порогами логического "0" и логической "1") ИМС переходит в активный режим.

Контур L1-C1 создаёт условия для возбуждения на собственной резонансной частоте.

Добротность контура большого значения не имеет, схема уверенно запускается и с низкодобротными контурами.

RC-генератор на ОУ с упрощенным мостом Вина и простейшей схемой стабилизации амплитуды.

Мост Вина

Слайд 37Генераторы импульсов

Генератор прямоугольного и треугольного напряжений

Интегратор интегрирует постоянное напряжение, имеющееся

на выходе триггера Шмитта. Когда выходное напряжение интегратора достигает порога

срабатывания триггера Шмитта, напряжение на его выходе U1 скачком меняет свой знак. Вследствие этого напряжение на выходе интегратора начинает изменяться в противоположную сторону, пока не достигнет другого порога срабатывания триггера Шмитта.Изменяя постоянную интегрирования RC, можно перестраивать частоту формируемого напряжения в широком диапазоне. Амплитуда треугольного напряжения U2 зависит только от установки уровня срабатывания триггера Шмитта Uп, который для данной схемы включения триггера составляет UМR1/R2 (UМ – напряжение насыщения ОУ).

Период колебаний генератора равен удвоенному времени, которое необходимо интегратору, чтобы его выходное напряжение изменилось от –Uп до +Uп. Отсюда следует, что

Таким образом, частота формируемого напряжения не зависит от уровня напряжения насыщения операционного усилителя.

Интегратор

Триггер Шмитта

Слайд 40Схемы устранения

дребезга контактов

С задержкой включения и выключения

При замыкании кнопки

SB1 емкость С1 начинает заряжаться. Постоянная времени цепи заряда (tз=0,7R2С1)

выбирается такой, чтобы переключение элемента D1.1 происходило после прекращения дребезга.При размыкании SB1 процесс перезаряда конденсатора аналогичен, что видно из диаграммы.

Слайд 41 Компаратор - это сравнивающее устройство. Аналоговый компаратор предназначен для сравнения

непрерывно изменяющихся сигналов и выдающий логический "0" или "1", в

зависимости от того, какой из сигналов больше.Аналоговые компараторы

В качестве компаратора может быть использован операционный усилитель (ОУ). Усилитель включен по схеме инвертирующего сумматора, однако, вместо резистора в цепи обратной связи включены параллельно стабилитрон VD1 и диод VD2. Пусть R1 = R2. Если Uвх - Uоп > 0, то диод VD2 открыт и выходное напряжение схемы небольшое отрицательное, равное падению напряжения на открытом диоде. При Uвх - Uоп < 0 на стабилитроне установится напряжение, равное его напряжению стабилизации Uст. Это напряжение должно соответствовать единичному логическому уровню цифровых интегральных микросхем (ИМС), входы которых подключены к выходу компаратора.

Таким образом, выход ОУ принимает два состояния, причем в обоих усилитель работает в линейном режиме.

Многие типы ОУ не допускают сколько-нибудь существенное входное дифференциальное напряжение.

Недостатком данной схемы является относительно низкое быстродействие, обусловленное необходимостью частотной коррекции, так как ОУ работает в линейном режиме со 100%-ной обратной связью. Используя для построения компаратора обычные ОУ, трудно получить время переключения менее 1 мкс.

На практике получили применение схемы компараторов, сравнивающие входной сигнал Uвх с опорным Uоп.

ОУ

Слайд 42Двухпороговые аналоговые компараторы

Особенности компараторов:

- Несмотря на то, что компараторы очень

похожи на операционные усилители, в них почти никогда не используют

отрицательную обратную связь, так как в этом случае весьма вероятно (а при наличии внутреннего гистерезиса - гарантировано) самовозбуждение компараторов.- В связи с тем, что в схеме нет отрицательной обратной связи, напряжения на входах компаратора неодинаковы.

- Из-за отсутствия отрицательной обратной связи входное сопротивление компаратора относительно низко и может меняться при изменении входных сигналов.

- Выходное сопротивление компараторов значительно и различно для разной полярности выходного напряжения.

Слайд 43Комбинационные схемы

ЦИФРОВЫЕ КОМПАРАТОРЫ

Таблица истинности

компаратора

Цифровые компараторы выполняют сравнение двух чисел,

представленных в двоичном коде.

Число входов компаратора определяется разрядностью сравниваемых

двоичных кодов чисел «а» и «b». Цифровой компаратор имеет три выхода, на которых формируются сигналы в условиях a = b, a > b и a < b. Структурная схема одноразрядного

цифрового компаратора

Схема одноразрядного

компаратора

Слайд 44Комбинационные схемы

ЦИФРОВЫЕ МНОГОРАЗРЯДНЫЕ КОМПАРАТОРЫ

Комбинированный способ

наращивания разрядности компаратора

Организация N-разрядного компаратора

Слайд 46Комбинационные схемы

ДЕШИФРАТОРЫ

Дешифратор — функциональный узел, вырабатывающий сигнал «лог. 1» (дешифратор с прямыми

выходами) или сигнал «лог. 0» (дешифратор с инверсными выходами) только на

одном из своих 2n выходах в зависимости от кода двоичного числа на n входах. Дешифраторы широко используются в устройствах управления, где они формируют управляющий сигнал в соответствии с входным кодом, который воздействует на какое-либо исполнительное устройство.

Пирамидальный дешифратор

3 × 8 с прямыми выходами

Слайд 47Комбинационные схемы

Микросхема К155ИД3 имеет четыре информационных входа Х0, Х1, Х2

и Х3, два инверсных входа стробирования V, объединённых по И,

и 16 инверсных выходов 0–15. Если на входах V1, V2 «лог. 0», то на выходе одной из схем DD1, номер которой соответствует десятичному эквиваленту входного кода, будет «лог. 0».Если хотя бы на одном из входов V «лог. 1», то независимо от состояния входов на всех выходах микросхемы формируется «лог. 1».

Дешифратор на ИМС К155ИД3 на 4 ×16

ДЕШИФРАТОРЫ

Слайд 48Комбинационные схемы

Паразитные импульсы в дешифраторах

Как и для любых других цифровых

микросхем, для дешифраторов критична ситуация одновременного или почти одновременного изменения

входных сигналов. Например, если стробы С постоянно разрешают работу дешифратора, то в момент изменения входного кода на любом выходе дешифратора могут появиться паразитные отрицательные короткие импульсы. Это может быть связано как с неодновременным выставлением разрядов кода (из-за несовершенства микросхем источников кода или из-за разных задержек распространения по линиям связи), так и с внутренними задержками самих микросхем дешифраторов.Если такие паразитные импульсы нужно исключить, то можно применять синхронизацию с помощью стробирующих сигналов. Используемый для этого сигнал С должен начинаться после текущего изменения кода, а заканчиваться до следующего изменения кода, то есть должен быть реализован вложенный цикл. На рисунке показано, как будет выглядеть выходной сигнал дешифратора без стробирования и со стробированием.

ДЕШИФРАТОРЫ

Слайд 49Комбинационные схемы

Перекоммутация входного сигнала по разным выходам

(демультиплексирование сигнала).

Дешифратор в

данном случае выступает в качестве демультиплексора входных сигналов, который позволяет

разделить входные сигналы, приходящие в разные моменты времени на вход С2, на одну выходную линию (мультиплексированные сигналы). При этом входы 1, 2, 4 дешифратора используются в качестве управляющих, определяющих, на какой выход переслать пришедший в данный момент входной сигнал. Вход С2 выступает в роли входного сигнала, который пересылается на заданный выход 0, 1, 2,… или 7.Если у микросхемы имеется несколько стробирующих входов С, то оставшиеся входы С можно использовать в качестве разрешающих работу дешифратора (например, вход С1).

ДЕШИФРАТОРЫ

Слайд 50Комбинационные схемы

Позиционная индикация на дешифраторе

Дешифраторы, имеющие выходы 0 –

3 с открытым коллектором, удобно применять в схемах позиционной индикации

на светодиодах. На рисунке приведен пример такой индикации на микросхеме, которая представляет собой два дешифратора 2 x 4 с объединенными входами для подачи кода и стробами С1 и С2, позволяющими строить дешифратор 3 x 8. При этом старший разряд кода выбирает один из дешифраторов 2 x 4 (нуль соответствует верхнему по схеме дешифратору, а единица—нижнему). То есть в данном случае номер горящего светодиода равен входному коду дешифратора.Такая индикация называется позиционной.

ДЕШИФРАТОРЫ

Слайд 51Комбинационные схемы

Индикация на дешифраторе с использованием 7-сегментного индикатора

ДЕШИФРАТОРЫ

Семисегментный код

необходим для отображения на цифровых индикаторах значений цифр от 0

до 9. Семисегментный, потому что цифры отображаются так называемыми сегментами, которых семь штук. Ниже приведена таблица соответствия между двоичным и семисегментным кодами.Слайд 55Комбинационные схемы

ШИФРАТОРЫ

Шифратор это функциональный узел, осуществляющий преобразование сигнала на одном

из его входов в цифровой код на его выходах.

При

появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число. Пусть сигнал «лог. 1» подан на вход Х7. Тогда на выходах логических элементов DD1.1, DD1.2, DD1.3 будут сигналы логических единиц, а на выходе элемента DD1.4 – сигнал логического нуля.

Таким образом, на выходах 8, 4, 2, 1 шифратора мы получим двоичное число 0111, соответствующий числу 7.

Некоторые из шифраторов снабжаются входом стробирования. Наличие входа стробирования позволяет выделять сигнал в определенный момент времени.

Слайд 56Комбинационные схемы

ШИФРАТОРЫ

Наличие у шифраторов входов EI и EO позволяет увеличивать

количество входов и разрядов шифратора с помощью дополнительных элементов на

выходе.Структурная схема шифратора 16 х 4

на двух микросхемах шифраторов

ИВ1 и трех элементах 2И-НЕ

Одновременное или почти одновременное изменение сигналов на входе шифратора приводит к появлению периодов неопределенности на выходах. Выходной код может на короткое время принимать значение, не соответствующее ни одному из входных сигналов. Поэтому в тех случаях, когда входные сигналы могут приходить одновременно, необходима синхронизация выходного кода, например, с помощью разрешающего сигнала EI, который должен приходить только тогда, когда состояние неопределенности уже закончилось.

Увеличение числа входов шифратора

Слайд 57Комбинационные схемы

ШИФРАТОРЫ

Применение шифратора для уменьшения числа передающих линий

Стандартное применение шифраторов

состоит в сокращении количества сигналов. Например, в случае шифратора ИВ1

информация о восьми входных сигналах сворачивается в три выходных сигнала. Это очень удобно, например, при передаче сигналов на большие расстояния. Правда, входные сигналы не должны приходить одновременно. На нижнем рисунке показаны стандартная схема включения шифратора и временные диаграммы его работы Инверсия выходного кода приводит к тому, что при приходе нулевого входного сигнала на выходе формируется не нулевой код, а код 111, то есть 7. Точно так же при приходе, например, третьего входного сигнала на выходе образуется код 100, то есть4, а при приходе пятого выходного сигнала — код 010, то есть 2.Слайд 58Комбинационные схемы

МУЛЬТИПЛЕКСОРЫ

Мультиплексор - это функциональный узел, осуществляющий подключение (коммутацию) одного

из нескольких информационных входов (Х0 - Х2) на выход (Y).

Входы

А0 – А2 являются управляющими и предназначены для выбора одного из информационных входов, подключаемых к выходу У. Реализация мультиплексора

На ИМС 3-2И-ИЛИ

Одновременная подача двух и более сигналов на управляющие входы недопустимо, т.к. в этих случаях состояние выхода ИМС 3-2И-ИЛИ будет непред-сказуемо.

Для устранения подобных случаев управление работой мультиплексора осуществляется дешифратором DC.

Слайд 61Комбинационные схемы

МУЛЬТИПЛЕКСОРЫ

Мультиплексор обозначается – MS.

A1-A3 - адресные входы. На них

подается двоичный код, указывающий номер подсоединяемого к выходу входа из

набора D0-D7.D0-D7 информационные входы.

E- разрешающий вход. Подача лог. «1» на вход Е переводит выход «У» в высокоимпедансное состояние.

Слайд 62Комбинационные схемы

МУЛЬТИПЛЕКСОРЫ

Число информационных входов реально выпускаемых промышленностью микросхем мультиплексоров не

превышает 16. Поэтому в случае необходимости иметь большее число входов

из имеющихся микросхем строят структуру так называемого мультипроцессорного дерева.Структурная схема 16-входового мультиплексор, построенного с использованием 4-входовых ИМС

Слайд 63Комбинационные схемы

ДЕМУЛЬТИПЛЕКСОРЫ

Демультиплексорами называются устройства, которые позволяют подключать сигнал с одного

входа к одному из нескольких выходов.

Демультиплексор можно построить на

основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора для усиления входного сигнала лучше поставить инвертор.Условно графическое обозначение демультиплексора с четырьмя выходами

Х

А0

А1

У1

У2

У3

У4

Слайд 64Комбинационные схемы

ДВУХНАПРАВЛЕННЫЕ КЛЮЧИ (МУЛЬТИПЛЕКСОРЫ-ДЕМУЛЬТИПЛЕКСОРЫ)

Двунаправленные ключи могут передавать цифровые и аналоговые сигналы.

Благодаря этому можно строить мультиплексоры — демультиплексоры.

Показанная на рисунке микросхема содержит два

четырёхвходовых мультиплексора, которые могут использоваться как демультиплексоры (МХ — ДМХ). На схемах они обозначаются буквами МХ.Микросхема содержит один общий инверсный вход Е разрешения (стробирования) и два общих адресных входа 1 и 2.

При логической 1 на входе разрешения выходы отключаются от информационных входов и переходят в высокоипедансное состояние.

При активизации входа разрешения, т. е. при подаче на него логического 0, происходит соединение одного из информационных входов (в соответствии с кодом на адресных входах) с выходом микросхемы. Поскольку это состояние происходит при помощи двунаправленных ключей на КМОП — транзисторах, то сигнал может передаваться как со входов на выход (режим мультиплексора), так и с выхода на входы ( режим демультиплексора). Кроме того, передаваемый сигнал может быть как аналоговым, так и цифровым.

Слайд 65Комбинационные схемы

Преобразователи кодов

Преобразователи кодов служат для преобразования входных двоичных кодов

в выходные двоично— десятичные и наоборот. Находят применение в схемах многоразрядной десятичной индикации.

На схемах обозначаются буквами X/Y.ИМС К155пп5

(преобразователь двоично-десятичного кода в код семисегментного индикатора)

Таблица истинности преобразователя двоично-десятичного кода в код семисегментного индикатора

Сегмент светится, если на него подаётся логическая 1.

Слайд 66Комбинационные схемы

СУММАТОРЫ

Сумматоры предназначены для выполнения арифметических действий с двоичными числами:

сложения, вычитания, умножения и деления – и относятся к арифметическим

устройствам. В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называются полусумматорами а вторые – полными одноразрядными сумматорами.Полусумматоры могут использоваться только для суммирования младших разрядов чисел. Полные одноразрядные сумматоры имеют дополнительный третий вход, на который подаётся перенос из предыдущего разряда при суммировании многоразрядных чисел.

Арифметические устройства воспринимают переменные "0" и "1" как цифры и выполняет действия над ними по законам двоичной арифметики.

Функциональная схема

одноразрядного полусумматора

на элементах «Не», «И»

Таблица истинности

одноразрядного полусумматора

Сигнал

переноса «1»

в следующий

разряд

Функциональная схема

одноразрядного полусумматора

на элементах «искл. ИЛИ», «И»

Условное обозначение

полусумматора

S

P

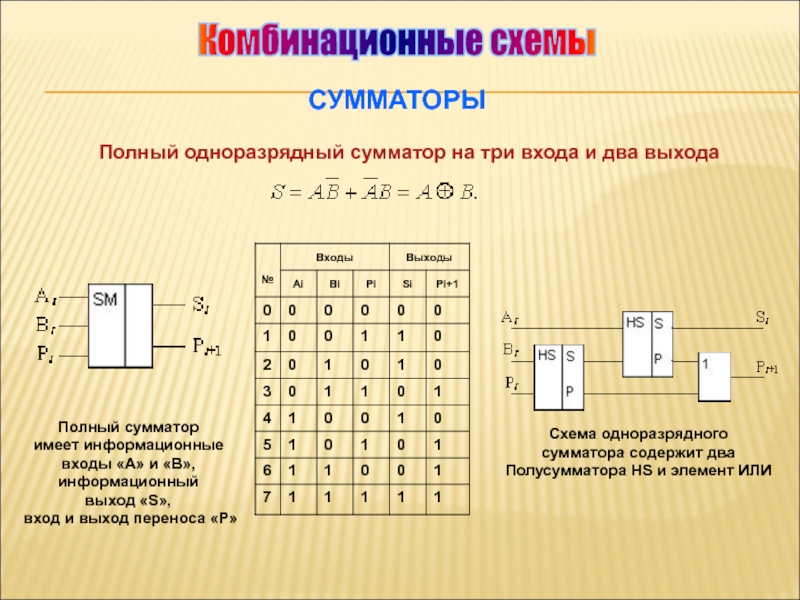

Слайд 67Комбинационные схемы

Полный одноразрядный сумматор на три входа и два выхода

Полный

сумматор

имеет информационные

входы «А» и «В»,

информационный

выход «S»,

вход

и выход переноса «Р»Схема одноразрядного

сумматора содержит два

Полусумматора HS и элемент ИЛИ

СУММАТОРЫ

Слайд 68Комбинационные схемы

СУММАТОРЫ

Параллельный

n-разрядный сумматор

Полный сумматор, синтезированный

из двух полусумматоров

Организация 12

- разрядного сумматора

С – вход расширения

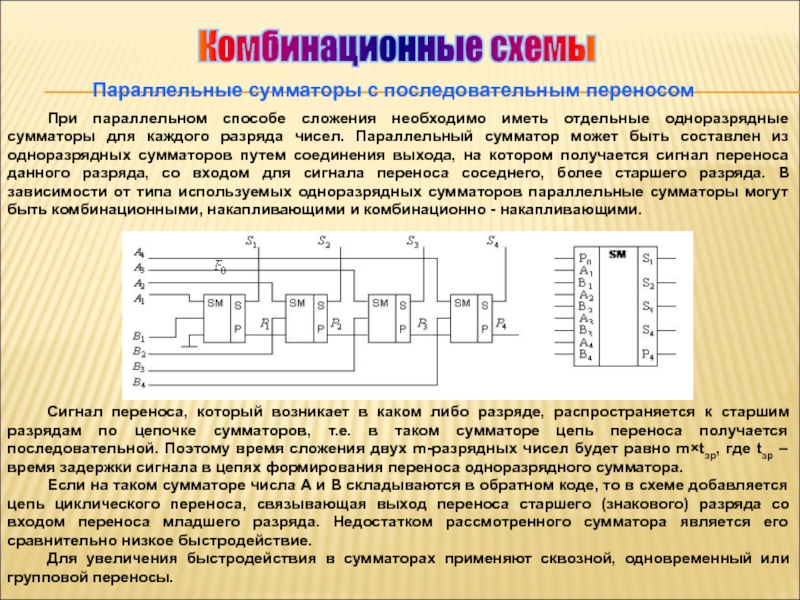

Слайд 69Комбинационные схемы

Параллельные сумматоры с последовательным переносом

При параллельном способе сложения необходимо

иметь отдельные одноразрядные сумматоры для каждого разряда чисел. Параллельный сумматор

может быть составлен из одноразрядных сумматоров путем соединения выхода, на котором получается сигнал переноса данного разряда, со входом для сигнала переноса соседнего, более старшего разряда. В зависимости от типа используемых одноразрядных сумматоров параллельные сумматоры могут быть комбинационными, накапливающими и комбинационно - накапливающими. Сигнал переноса, который возникает в каком либо разряде, распространяется к старшим разрядам по цепочке сумматоров, т.е. в таком сумматоре цепь переноса получается последовательной. Поэтому время сложения двух m-разрядных чисел будет равно m×tзр, где tзр – время задержки сигнала в цепях формирования переноса одноразрядного сумматора.

Если на таком сумматоре числа А и В складываются в обратном коде, то в схеме добавляется цепь циклического переноса, связывающая выход переноса старшего (знакового) разряда со входом переноса младшего разряда. Недостатком рассмотренного сумматора является его сравнительно низкое быстродействие.

Для увеличения быстродействия в сумматорах применяют сквозной, одновременный или групповой переносы.

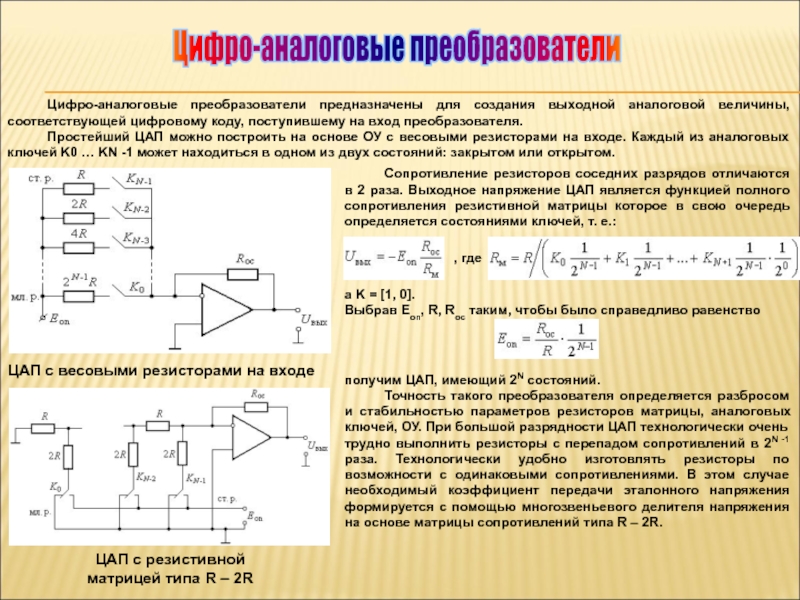

Слайд 70Цифро-аналоговые преобразователи

Цифро-аналоговые преобразователи предназначены для создания выходной аналоговой величины, соответствующей

цифровому коду, поступившему на вход преобразователя.

Простейший ЦАП можно построить на

основе ОУ с весовыми резисторами на входе. Каждый из аналоговых ключей K0 … KN -1 может находиться в одном из двух состояний: закрытом или открытом. Сопротивление резисторов соседних разрядов отличаются в 2 раза. Выходное напряжение ЦАП является функцией полного сопротивления резистивной матрицы которое в свою очередь определяется состояниями ключей, т. е.:

, где

a K = [1, 0].

Выбрав Eon, R, Roc таким, чтобы было справедливо равенство

получим ЦАП, имеющий 2N состояний.

Точность такого преобразователя определяется разбросом и стабильностью параметров резисторов матрицы, аналоговых ключей, ОУ. При большой разрядности ЦАП технологически очень трудно выполнить резисторы с перепадом сопротивлений в 2N -1 раза. Технологически удобно изготовлять резисторы по возможности с одинаковыми сопротивлениями. В этом случае необходимый коэффициент передачи эталонного напряжения формируется с помощью многозвеньевого делителя напряжения на основе матрицы сопротивлений типа R – 2R.

ЦАП с резистивной

матрицей типа R – 2R

ЦАП с весовыми резисторами на входе

Слайд 71Цифро-аналоговые преобразователи

Погрешности преобразования ЦАП

Абсолютная погрешность преобразо-вания dпш показывает максимальное отклонение

выходного напряжения в конечной точке реальной характеристики преобразования от выходного

напряжения в конечной точке идеальной характеристики преобразования. Абсолютная погрешность преобразо-вания оценивается в процентах или долях единицы младшего разряда (ЕМР).ЕМР – среднее значение ступени квантования по всей характеристике преобразо-вания.

Нелинейность преобразования ЦАП dлн определяет максимальное отклонение реальной ХП от идеальной и оценивается также в долях ЕМР.

Дифференциальная нелинейность преобразования ЦАП – dдиф.лн численно равна максимальной разности двух соседних шагов квантования:

dдиф.лн = D Uвых 2 – D Uвых 1

Дифференциальная нелинейность также оценивается в долях ЕМР.

Слайд 72Аналого-цифровые преобразователи

АЦП последовательного счета

Недостатком такой схемы АЦП является ее низкое

быстродействие, зависящее от величины входного сигнала. Например, пусть fT = 10

мГц и число разрядов счетчика N = 12. Максимальное число импульсов заполнения счетчика , тогда максимальная частота отсчетов входного сигнала составит Fотсч ≤ fT/K ≈ 107/(4 · 103) = 2,5 · 103 Гц, а высшая частота в спектре входного сигнала не может превысить Fв ≤ 1,25 · 103 Гц. АЦП состоит из компаратора, ЦАП, двоичного счетчика, выходного буферного регистра. После команд СБРОС и ПУСК, подаваемых на АЦП, импульсы тактового генератора начинают увеличивать показания счетчика, а, следовательно, и выходной сигнал ЦАП X(t) ступеньками по оси t. Компаратор определяет разницу между X(t) и Uвх. Если окажется, что X(t) - Uвх > 0, то компаратор выраба-тывает сигнал СТОП, счетчик останавливается и индицирует двоич-ный код, эквивалентный входному сигналу Uвх.

Структура АЦП

последовательного счета

Временная диаграмма

Слайд 73Аналого-цифровые преобразователи

АЦП последовательного приближения

Если окажется, что Uвх < UЦАП ,

последняя установленная в ЦАП единица заменяется компаратором на ноль, и

очередная единица записывается в последующий разряд. Описанные выше действия повторяются до N-го младшего разряда. Таким образом, после N тактов сравнения Uвх и UЦАП, в регистре памяти сформируется N-разрядный двоичный код, который является цифровым эквивалентом входного аналогового сигнала. В такой структуре АЦП полное время преобразования составит N · ДT, где ДT длительность одного такта.При той же частоте тактового генератора fT = 10 мГц и разрядности ЦАП N = 12 преобразование будет выполнено за 12 периодов fT, т. е. частота отсчетов входного сигнала достигнет Fотсч = fT/12 = 107/12 = 830 кГц, а высшая частота преобразуемых сигналов FВ ≈ 400 кГц.

После пуска схемы первым тактовым импульсом регистр памяти (РП) устанавливает старший разряд ЦАП в единицу. При этом, если Uвх > UЦАП, то компаратор подтверждает состояние РП и ЦАП. Следующим тактовым импуль-сом единица устанавливается в следую-щим за старшим разряде.

Слайд 74Триггеры

Классификация триггеров

Триггер - это устройство, имеющее два устойчивых состояния и

способное под действием управляющих сигналов скачкообразно переходить из одного состояния

в другое.Слайд 75 При подаче единицы на вход R (от англ. Reset —

сбросить) выходное состояние становится равным логическому нулю.

Состояние, при котором

на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний).

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

Асинхронный RS-триггер

RS-триггер или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице.

Слайд 76Синхронный RS-триггер

Известно, что из-за задержек переключения логических элементов могут возникнуть

ложные состояния. Устранить это помогает временное стробирование. Временное стробирование обеспечивается

синхронизирующими (тактовыми) импульсами, поэтому синхронный RS-триггер кроме информационных входов R и S имеется вход C, на который подается синхронизирующий сигнал «С».Такой триггер функционирует как RS-триггер только при условии наличия синхронизирующих импульсов. В противном случае, т.е. при отсутствии синхронизирующих импульсов, состояние его сохраняется неизменным Qn+1 = Qn , какие бы сигналы ни подавались на информационные входы, причем возможна подача сочетания R = S = 1 (или R = S = 0 для триггера с инверсными входами).

Слайд 77D-триггер

D-триггер — запоминает состояние входа и выдаёт его на выход.

D-триггеры имеют, как минимум, два входа: информационный D и синхронизации

С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С.Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

Слайд 78T-триггер синхронный

Триггер Т -типа, или счетный триггер, имеет один информационный

Т-вход. Смена его состояний происходит всякий раз, когда входной сигнал

меняет свое значение в определенном направлении. В зависимости от того, какой перепад напряжения используется для управления (от нуля к единице или от единицы к нулю), различают Т-триггеры с прямым или инверсным динамическим управлением ( -триггер).По способу ввода входной информации Т-триггеры могут быть асинхронными и синхронными.

Слайд 79JK-триггер

JK-триггер работает так же как RS-триггер, с одним лишь исключением:

при подаче логической единицы на оба входа J и K

состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и КИМС триггера К155ТВ1

Слайд 80JK-триггер

Использование JK-триггера в качестве:

D-триггера

асинхронного

T-триггера

синхронного T-триггера

Слайд 81Счетчики

Счетчиком называется устройство, предназначенное для подсчета числа входных сигналов и

хранения в определенном двоичном коде этого числа.

Счетчики - это цифровые

автоматы, внутренние состояния которых определяются только количеством сигналов "1", пришедших на вход. Сигналы "0" не изменяют их внутренние состояния. Триггер Т-типа является простейшим счетчиком, который считает до двух. Счетчик, образованный цепочкой из m триггеров, сможет подсчитывать в двоичном коде 2m входных импульсов. Каждый из триггеров в этой цепочке называют разрядом счетчика.

Основная характеристика счетчика – модуль счета, или емкость счетчика Kсч.. Это количество поступивших входных сигналов, которое возвращает счетчик в исходное состояние.

Количество триггеров, необходимое для реализации счетчика, равно m = log2 Kсч., где m – ближайшее большее целое число.

Классификация счетчиков

по модулю счета: двоичные, двоично-десятичные или с другим основанием счета, недвоичные с постоянным модулем счета, с перемен-ным модулем счета

по направлению счета: суммирующие, вычитающие, реверсивные;

по способу организации внутренних связей: с последовательным перено-сом, с параллельным переносом, с комбинированным переносом, кольце-вые

Слайд 82Счетчики

Последовательные счетчики

Счетчик может работать как суммирующий, так и как вычитающий.

В режиме вычитания сигналы на входы последующих разрядов подавать с

инверсных выходов триггеров предыдущих разрядов.Так как полученный счетчик – асинхронный, то каждый его триггер срабатывает с задержкой относительно входного сигнала. Поэтому по мере продвижения сигнала от младшего разряда к старшему эта задержка суммируется и может произойти искажение информации, в виде несоответствие числа уже поступивших в счетчик импульсов и кода на его выходах.

В общем случае суммарная задержка пропорциональна числу триггеров, что снижает быстродействие счетчика.

Суммирующий счетчик на JK-триггерах

Слайд 83Счетчики

Параллельные счетчики

Для повышения быстродействия счетчики выполняются синхронными с параллельным переносом

(или параллельными).

Их особенность заключается в том, что выходы всех предшествующих

разрядов соединяются с входами триггера последующего разряда, поэтому длительность переходного процесса определяется только длительностью переходного процесса одного разряда и не зависит от количества триггеров. Отсюда следует, что параллельные счетчики – синхронные. Структурная схема вычитающего счетчика для этого случая отличается тем, что сигналы на входы J и K последующих триггеров необходимо подавать с инверсных выходов триггеров предшествующих разрядов. Так как исходное состояние вычитающего счетчика – единицы во всех разрядах, то организуется общая шина установки по -входам.

Слайд 84Счетчики

Реверсивные счетчики

Реверсивный счетчик должен, в зависимости от сигналов управления, обеспечивать

или режим суммирования, или режим вычитания входных сигналов.

Реверсивный счетчик

должен содержать схему управления, обеспечивающую подключение либо прямых, либо инверсных выходов ко входам последующих разрядов, в зависимости от сигналов управления направлением счета T.Слайд 85Регистры

Цифровые регистры - это устройства, предназначенные для хранения и преобразования

многоразрядных двоичных чисел. Запоминающими элементами регистра являются триггеры, число которых

равно разрядности хранимых чисел. Кроме триггеров регистры содержат также комбинационные схемы, предназначенные для ввода и вывода хранимых чисел, преобразования их кодов, сдвига кодов на то или иное число разрядов. Информация в регистрах хранится, как правило, в течение некоторого количества тактовРазличают параллельные регистры (регистры памяти), последовательные регистры (регистры сдвига), параллельно-последовательные регистры (например, ввод в параллельном коде, вывод – в последовательном и наоборот).

В параллельных регистрах можно производить поразрядные логические операции с хранимым числом и вновь вводимым. Вид логических операций зависит от типа триггеров, составляющих регистр, и комбинации сигналов управления.

Регистры сдвига применяются для преобразования последовательного кода в параллельный (и обратно), для умножения и деления многоразрядных чисел и т. д.

Слайд 86Регистры

Параллельные регистры

однофазный

парафазный

Изменение хранящейся

информации (ввод новой информации) происходит после соответствующего изменения сигналов на входах A при поступлении определенного уровня (С = 0 или С = 1) или фронта синхросигналов. В качестве разрядов регистра памяти используются синхронизируемые D-триггеры, если информация поступает в виде однофазных сигналов, или RS-триггеры, если информация поступает в виде парафазных сигналов

Слайд 87Регистры

Последовательные регистры

Сдвиговый регистр на D-триггерах со сдвигом вправо

В регистре с

последовательным вводом производится последовательный сдвиг поступающей на вход информации на

один разряд вправо в каждом такте синхросигналов.После поступления m синхроимпульсов весь регистр оказывается заполненным разрядами числа А, и первый разряд числа (A0) появляется на выходе Q0 регистра. В течение последующих m синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным.

При построении последовательных регистров со сдвигом влево необходимо произвести переключение входов триггеров таким образом, чтобы состояние (Pm – i)-го триггера изменялось в соответствии с состоянием (Pm – i – 1)-го триггера.

Слайд 88Регистры

Реверсивные регистры

Для построения реверсивного сдвигового регистра необходимо между его триггерами

включать устройства управления направлением сдвига. Эти устройства в зависимости от

единичного сигнала, поступившего либо по шине Tс. прав. , либо по шине Tс. лев. , должны подключать входы каждого триггера регистра к выходам предыдущего или к выходам последующего триггеров.Для построения реверсивного сдвигового регистра необходимо между его триггерами включать устройства управления направлением сдвига. Эти устройства в зависимости от единичного сигнала, поступившего либо по шине Tс. прав. , либо по шине Tс. лев. , должны подключать входы каждого триггера регистра к выходам предыдущего или к выходам последующего триггеров.

При построении сдвиговых регистров обязательным является применение триггеров, синхронизируемых фронтом. В противном случае за время действия одного синхросигнала информация в регистре продвигается более чем на один разряд, т. е. нормальное функционирование регистра – сдвиг на один разряд за один такт – нарушается.

Функциональные возможности сдвигового регистра можно расширить, если его дополнить входами параллельной загрузки и выходами всех разрядов регистра для параллельной выдачи информации.

Слайд 89Генераторы числовых

последовательностей

Последовательностные устройства этого типа называют также распределителями сигналов,

так как последовательность двоичных чисел на их выходах используется для

управления работой других цифровых узлов. Число состояний генератора называется длиной последовательности чисел Ln, которая равна количеству тактов, после которого последовательность чисел на выходе генератора повторяется.По своей структуре генераторы чисел близки либо к счетчикам, либо к регистрам.

Генератор чисел 3 – 2 – 12 – 4 на основе счетчика

Любой счетчик можно считать генератором последовательности чисел, имеющей Ln = Kсч. Как правило, требуемое число разрядов генератора равно числу двоичных разрядов m в генерируемых числах. Если m > log2 Ln, то для уменьшения числа используемых триггеров структура генераторов изменяется. В этом случае генератор целесообразнее строить в виде счетчика с модулем счета Kс = Ln и подключенной к его выходам комбинационной схемой (КС), синтезирующей требуемые значения двоичных чисел последовательности.

Слайд 90Полупроводниковые запоминающие

устройства

Структура

ОЗУ

- ДШх, ДШу – адресные дешифраторы строк и

столбцов;

- ФЗС – формирователь сигналов записи/считывания;

- СУ – схема управления;

-

АШх, РШ – адресные и разрядные шины;- DI, DO – шины записи и считывания соответственно;

- БК – буферный каскад.

Накопитель представляет собой прямоугольную матрицу ЭП, содержащую nx строк и ny столбцов. Емкость накопителя N = nx · ny. Каждый ЭП подключен к адресным (АШ) и разрядным (РШ) шинам. Выбор необходимого ЭП осуществляется путем подачи определенной комбинации адресных переменных (Am … A1 , A0). Адресные дешифраторы строк (ДШx) и столбцов (ДШy) формируют сигналы выборки на соответствующих АШ, которые определяют строку и столбец накопителя, в котором расположен выбираемый ЭП. Таким образом, m адресных входов позволяют выбирать один из N = 2m элементов памяти.

Режим работы микросхемы определяется сигналами выбора микросхемы (CHIP SELECT) и записи-считывания (WRITE/READ). При подаче низкого потенциала на вход выбора схема управления (СУ) разрешает формирование сигналов выборки на АШx . Если при этом сигнал на входе , то СУ формирует управляющий сигнал, при котором ФЗС обеспечивает запись в выбранном ЭП информации, поступающей на вход DI. Выход DO в этом случае находится в отключенном состоянии. Если сигнал , то СУ переключает ФЗС в режим считывания, при котором информация из выбранного ЭП передается на выход DO, при этом состояние входа DI не влияет на работу микросхемы.

При микросхема находится в режиме хранения, т. е. состояние ЭП не меняется при любых сигналах на входах (Am … A0), DI, . Выход DO находится в отключенном состоянии.

Слайд 91Генераторы импульсных сигналов

на микросхемах

В схеме использованы микросхемы 176

серии, у которых два входных ограничительных диода, длительность импульсов и

пауз будет равна: tи = tп = 0,7∙R2∙C1, Полный период — 1,4∙R2∙C1, а частота следования импульсов — f = 0,7/R2∙C1.Резистор R1 нужен для ограничения тока через входные диоды, но можно обойтись и без него.

Схема генератора на двух элементах, но частота такого генератора менее стабильна

Генератор с возможностью отключения

Нумерация выводов логических элементов соответствует микросхеме К176ЛА7, К176ЛЕ5

Слайд 92Генераторы импульсных сигналов

на микросхемах

Схема с возможностью регулировки скважности

импульсов в

широких пределах

При необходимости в генераторе, который формирует определенное

число импульсов используется схема, в которой содержатся ждущий мультивибратор DD1.1 DD1.2, необходимый для подавления дребезга контактов, генератор импульсов DD1.3, DD1.4 и десятичный счетчик с дешифратором — К176ИЕ8. Число генерируемых импульсов соответствует номеру нажатой кнопки.