Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Обмен в режиме прерывания. Программные и аппаратные средства, обеспечивающие обмен в режиме прерывания

Содержание

- 1. Обмен в режиме прерывания. Программные и аппаратные средства, обеспечивающие обмен в режиме прерывания

- 2. Организация прерываний

- 3. Действия, выполняемые

- 4. Слайд 4

- 5. Обычно задача сохранения содержимого

- 6. Существуют два основных способа

- 7. Слайд 7

- 8. При организации

- 9. Вектор прерывания

- 10. Аппаратный опрос

- 11. Маскируемые прерывания

- 12. БИС программируемого контроллера прерываний Intel

- 13. Маскируемые прерывания

- 14. Маскируемые прерывания

- 15. Аппаратные прерывания PC AT0Bh0Ch0Dh0Eh0Fh1213141516RS232RS232Параллельный порт

- 16. Маскируемые прерывания

- 17. Маскируемые прерывания

- 18. Слайд 18

- 19. Маскируемые прерывания

- 20. Режимы работы ПКП Режим полного

- 21. Маскирование прерываний. Позволяет устройствам с

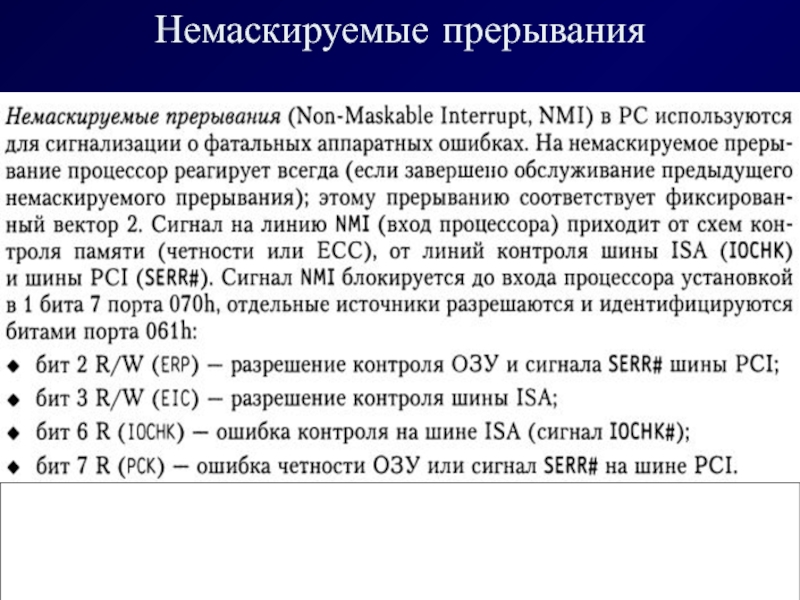

- 22. Немаскируемые прерывания

- 23. Прерывания могут быть внешними и внутренними. Внешние

- 24. Таблица векторов прерываний (Таблица дескрипторов прерываний )

- 25. Организация прямого доступа к памяти

- 26. Организация прямого доступа к памяти

- 27. В целях сокращения количества линий

- 28. Наиболее распространенным является ПДП

- 29. Применение в компьютере обмена данными

- 30. 2. Обмен данными в режиме

- 31. Скачать презентанцию

Организация прерываний Одной из разновидностей программно-управляемого обмена данными с ВУ в микрокомпьютере является обмен с прерыванием программы отличающийся от асинхронного программно-управляемого обмена тем, что переход к

Слайды и текст этой презентации

Слайд 1Лекция

Обмен в режиме прерывания. Программные и аппаратные средства, обеспечивающие

обмен в режиме прерывания

памятиСлайд 2Организация прерываний

Одной из разновидностей

программно-управляемого обмена данными с ВУ в микрокомпьютере является обмен с

прерыванием программы отличающийся от асинхронного программно-управляемого обмена тем, что переход к выполнению команд, физически реализующих обмен данными, осуществляется с помощью специальных аппаратных средств. Команды обмена данными в этом случае выделяют в отдельный программный модуль - подпрограмму обработки прерывания. Задачей аппаратных средств обработки прерывания в процессоре микрокомпьютера как раз и является приостановка выполнения одной программы (ее еще называют основной программой) и передача управления подпрограмме обработки прерывания.Слайд 3

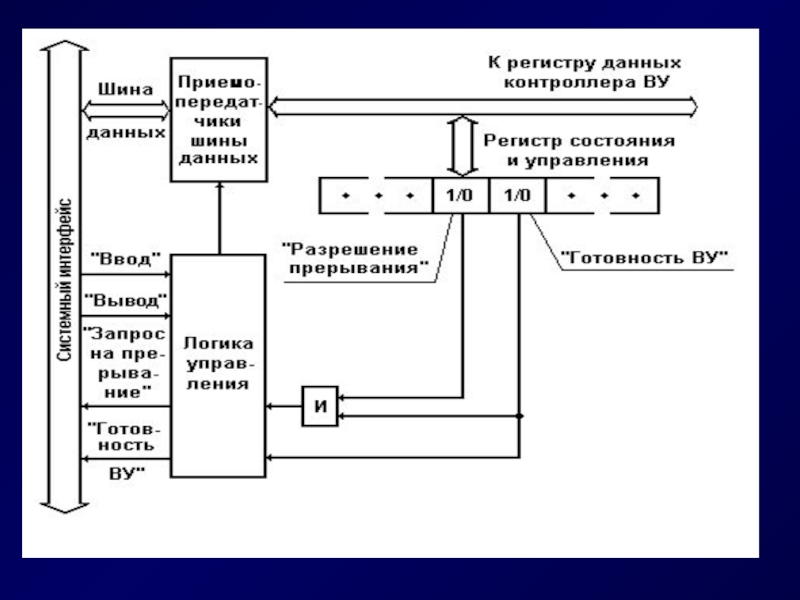

Действия, выполняемые при этом процессором,

как правило, те же, что и при обращении к подпрограмме.

Только при обращении к подпрограмме они инициируются командой, а при обработке прерывания - управляющим сигналом от ВУ, который называют «Требование прерывания» или «Запрос на прерывание».Регистр состояния контроллера ВУ дополняют еще одним разрядом - «Разрешение прерывания». Запись 1 или 0 в разряд «Разрешение прерывания» регистра состояния производится программным путем по одной из линий шины данных системного интерфейса. Управляющий сигнал системного интерфейса «Предоставление прерывания» формируется с помощью схемы совпадения только при наличии единиц в разрядах «Готовность ВУ» и «Разрешение прерывания» регистра состояния контроллера.

Слайд 5

Обычно задача сохранения содержимого счетчика команд и

регистра состояния процессора возлагается на аппаратные средства обработки прерывания. Сохранение

содержимого других регистров процессора, используемых в подпрограмме обработки прерывания, производится непосредственно в подпрограмме.В микрокомпьютере обычно используется одноуровневая система прерываний, т. е. сигналы «Требование прерывания» от всех ВУ поступают на один вход процессора. Поэтому возникает проблема идентификации ВУ, запросившего обслуживание, и реализации заданной очередности (приоритета) обслуживания ВУ при одновременном поступлении нескольких сигналов прерывания.

Слайд 6

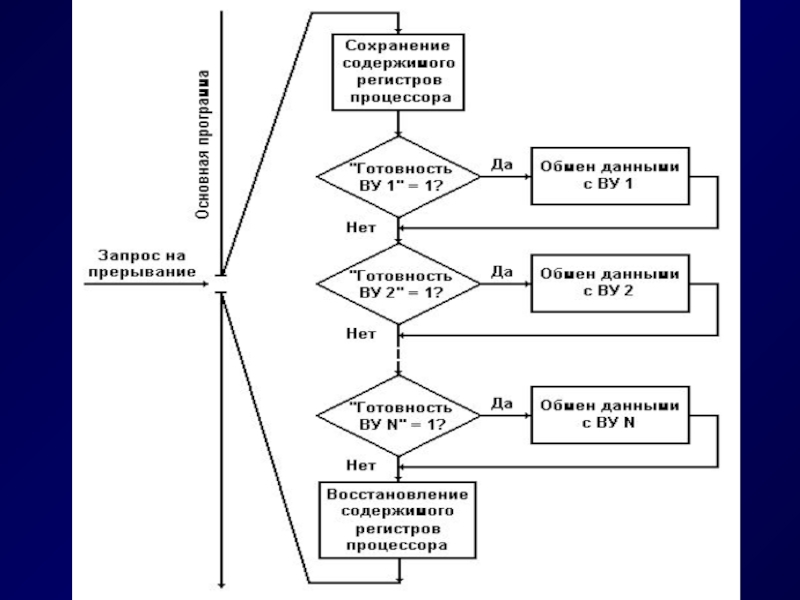

Существуют два основных способа идентификации ВУ, запросивших

обслуживания:

программный опрос регистров состояния (разряд «Готовность ВУ») контроллеров

всех ВУ; использование векторов прерывания.

Организация прерываний с программным опросом готовности предполагает наличие в памяти микрокомпьютера единой подпрограммы обслуживания прерываний от всех ВУ.

Приоритет ВУ в микрокомпьютере с программным опросом готовности ВУ однозначно определяется порядком их опроса в подпрограмме обработки прерываний.

Слайд 8

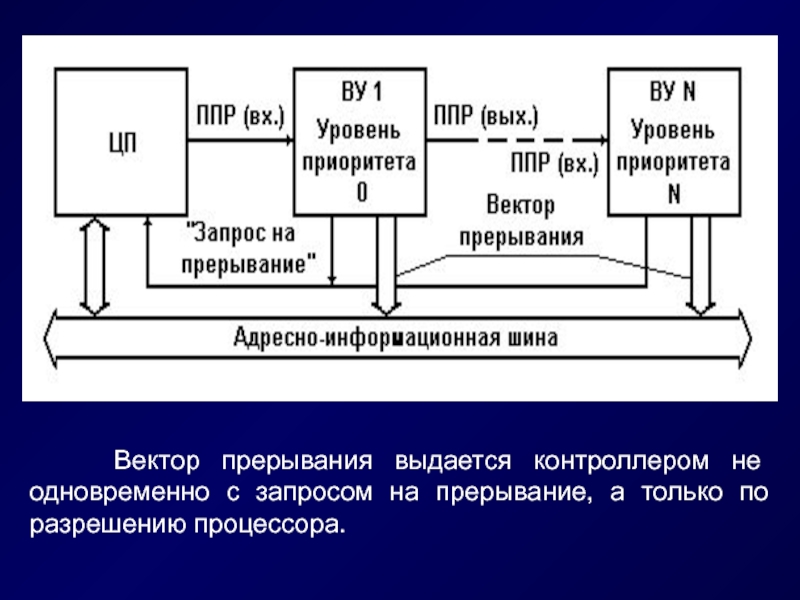

При организации системы прерываний с

использованием векторов прерываний ВУ, запросившее обслуживания, само идентифицирует себя с

помощью вектора прерывания - адреса ячейки основной памяти микроЭВМ, в которой хранится либо первая команда подпрограммы обслуживания прерывания данного ВУ, либо адрес начала такой подпрограммы.Таким образом, процессор, получив из контроллера ВУ вектор прерывания, сразу переключается на выполнение требуемой подпрограммы обработки прерывания. В микрокомпьютере с векторной системой прерывания каждое ВУ должно иметь собственную подпрограмму обработки прерывания.

Слайд 9

Вектор прерывания выдается контроллером не

одновременно с запросом на прерывание, а только по разрешению процессора.

Слайд 10

Аппаратный опрос готовности ВУ производится

гораздо быстрее, нежели программный. Но если обслуживания запросили одновременно два

или более ВУ, обслуживание менее приоритетных ВУ будет отложено на время обслуживания более приоритетных, как и в системе прерывания с программным опросом.Слайд 12

БИС программируемого контроллера прерываний Intel 8259A

Контроллер прерываний (ПКП)

представляет собой устройство, реализующее до восьми уровней запросов на прерывания,

с возможностью программного маскирования и изменения порядка обслуживания прерываний.Слайд 15

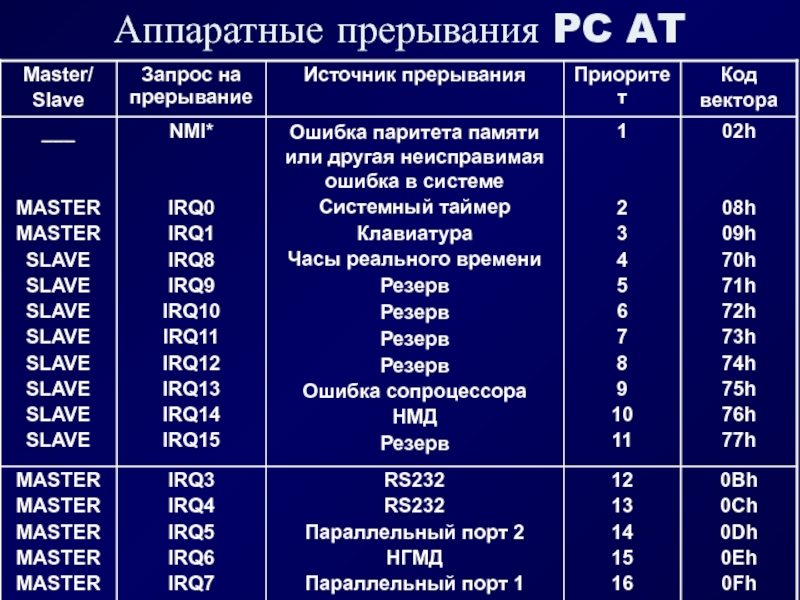

Аппаратные прерывания PC AT

0Bh

0Ch

0Dh

0Eh

0Fh

12

13

14

15

16

RS232

RS232

Параллельный порт 2

НГМД

Параллельный порт 1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

MASTER

MASTER

MASTER

MASTER

MASTER

02h

08h

09h

70h

71h

72h

73h

74h

75h

76h

77h

1

2

3

4

5

6

7

8

9

10

11

Ошибка

паритетa памяти или другая неисправимая ошибка в системе

Системный таймер

Клавиатура

Часы реального

времениРезерв

Резерв

Резерв

Резерв

Ошибка сопроцессора

НМД

Резерв

NMI*

IRQ0

IRQ1

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

___

MASTER

MASTER

SLAVE

SLAVE

SLAVE

SLAVE

SLAVE

SLAVE

SLAVE

SLAVE

Код

вектора

Приоритет

Источник прерывания

Запрос на прерывание

Master/

Slave

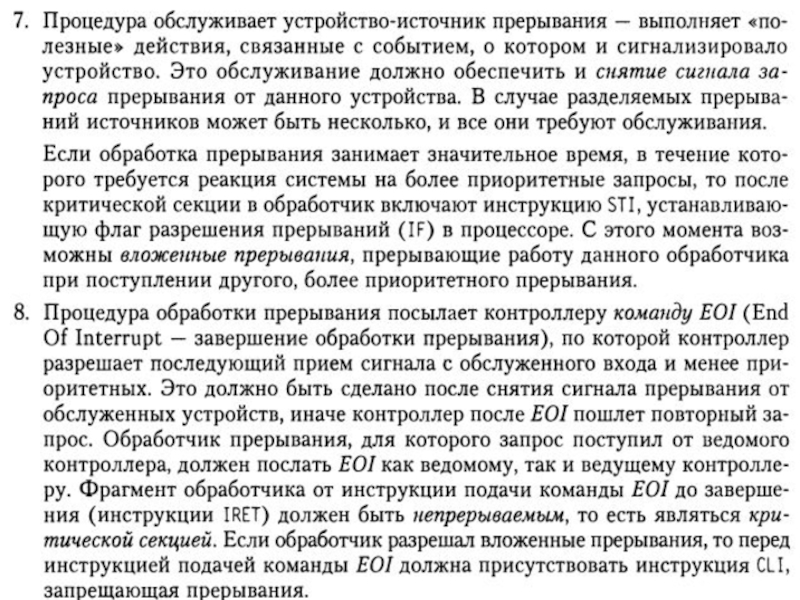

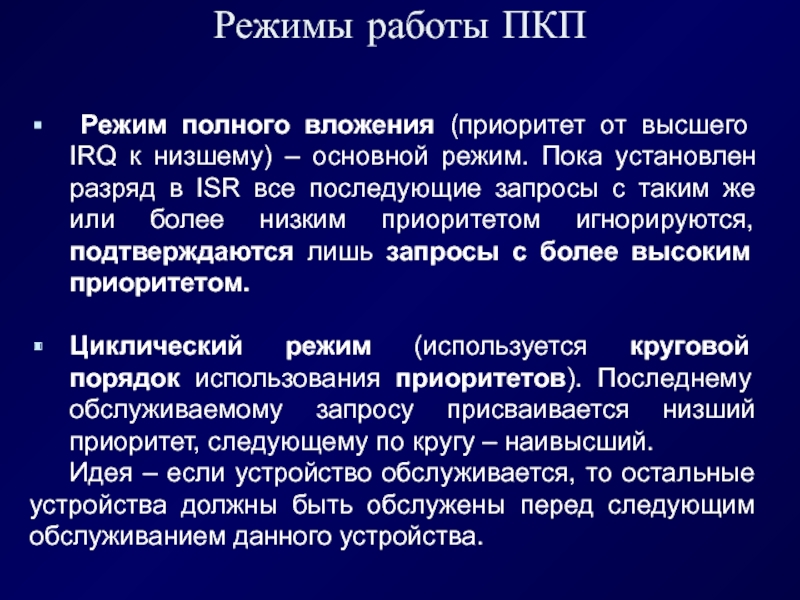

Слайд 20Режимы работы ПКП

Режим полного вложения (приоритет от

высшего IRQ к низшему) – основной режим. Пока установлен разряд

в ISR все последующие запросы с таким же или более низким приоритетом игнорируются, подтверждаются лишь запросы с более высоким приоритетом.Циклический режим (используется круговой порядок использования приоритетов). Последнему обслуживаемому запросу присваивается низший приоритет, следующему по кругу – наивысший.

Идея – если устройство обслуживается, то остальные устройства должны быть обслужены перед следующим обслуживанием данного устройства.

Слайд 21

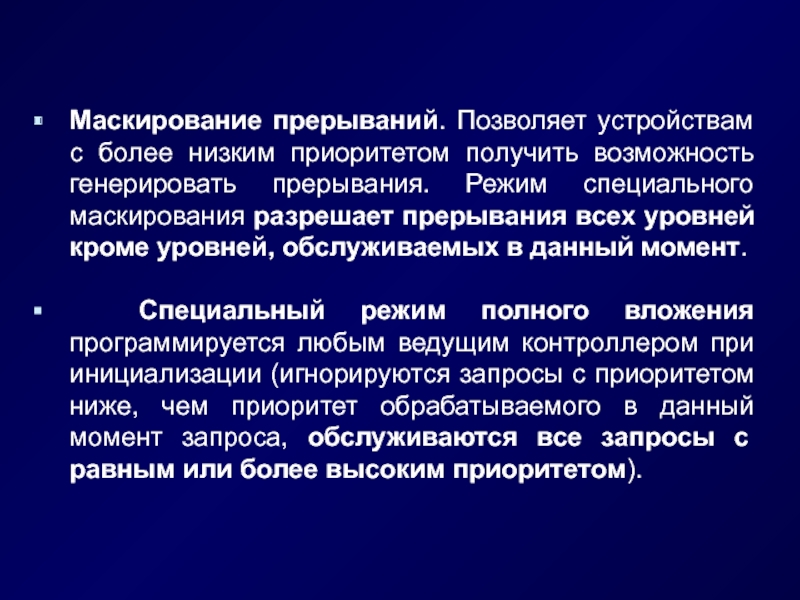

Маскирование прерываний. Позволяет устройствам с более низким приоритетом

получить возможность генерировать прерывания. Режим специального маскирования разрешает прерывания всех

уровней кроме уровней, обслуживаемых в данный момент.Специальный режим полного вложения программируется любым ведущим контроллером при инициализации (игнорируются запросы с приоритетом ниже, чем приоритет обрабатываемого в данный момент запроса, обслуживаются все запросы с равным или более высоким приоритетом).

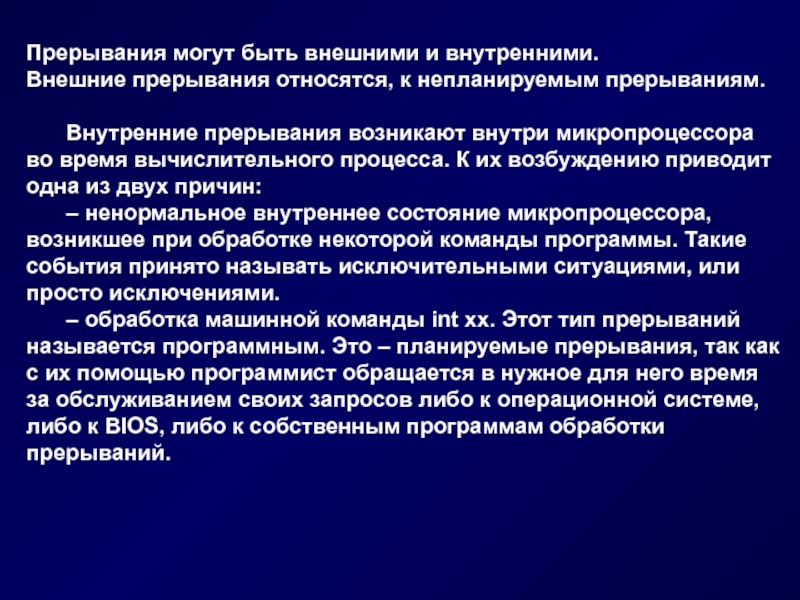

Слайд 23Прерывания могут быть внешними и внутренними.

Внешние прерывания относятся, к

непланируемым прерываниям.

Внутренние прерывания возникают внутри микропроцессора во время вычислительного процесса.

К их возбуждению приводит одна из двух причин:– ненормальное внутреннее состояние микропроцессора, возникшее при обработке некоторой команды программы. Такие события принято называть исключительными ситуациями, или просто исключениями.

– обработка машинной команды int xx. Этот тип прерываний называется программным. Это – планируемые прерывания, так как с их помощью программист обращается в нужное для него время за обслуживанием своих запросов либо к операционной системе, либо к BIOS, либо к собственным программам обработки прерываний.

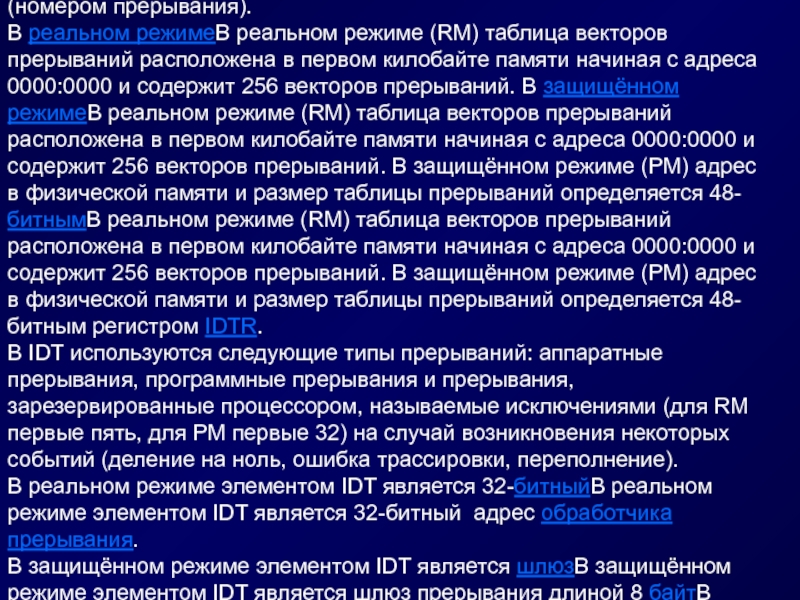

Слайд 24Таблица векторов прерываний (Таблица дескрипторов прерываний ) (англ.) (англ. Interrupt Descriptor

Table, IDT) используется в x86 архитектуре и служит для связи

обработчика прерывания с вектором (номером прерывания).В реальном режимеВ реальном режиме (RM) таблица векторов прерываний расположена в первом килобайте памяти начиная с адреса 0000:0000 и содержит 256 векторов прерываний. В защищённом режимеВ реальном режиме (RM) таблица векторов прерываний расположена в первом килобайте памяти начиная с адреса 0000:0000 и содержит 256 векторов прерываний. В защищённом режиме (PM) адрес в физической памяти и размер таблицы прерываний определяется 48-битнымВ реальном режиме (RM) таблица векторов прерываний расположена в первом килобайте памяти начиная с адреса 0000:0000 и содержит 256 векторов прерываний. В защищённом режиме (PM) адрес в физической памяти и размер таблицы прерываний определяется 48-битным регистром IDTR.

В IDT используются следующие типы прерываний: аппаратные прерывания, программные прерывания и прерывания, зарезервированные процессором, называемые исключениями (для RM первые пять, для PM первые 32) на случай возникновения некоторых событий (деление на ноль, ошибка трассировки, переполнение).

В реальном режиме элементом IDT является 32-битныйВ реальном режиме элементом IDT является 32-битный адрес обработчика прерывания.

В защищённом режиме элементом IDT является шлюзВ защищённом режиме элементом IDT является шлюз прерывания длиной 8 байтВ защищённом режиме элементом IDT является шлюз прерывания длиной 8 байт, содержащий сегментный (логический) адрес обработчика прерывания, права доступа и др.

Слайд 25Организация прямого доступа

к памяти

Одним из способов обмена

данными с ВУ является обмен в режиме прямого доступа к

памяти (ПДП).В этом режиме обмен данными между ВУ и основной памятью компьютера происходит без участия процессора.

Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно схемы, управляющие обменом в режиме ПДП, размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти.

Слайд 26Организация прямого доступа

к памяти

Необходимость реализации в микрокомпьютере

обмена данными в режиме ПДП вызывается двумя основными факторами.

Во-первых,

при использовании режима ПДП появляется возможность начальной загрузки программ в основную память из устройства ввода. Во-вторых, что и является наиболее важным, режим ПДП обеспечивает возможность использования быстродействующих внешних запоминающих устройств, таких, например, как накопители на жестких магнитных дисках.

Слайд 27

В целях сокращения количества линий в шинах микрокомпьютера

контроллер ПДП подключается к памяти посредством шин адреса и данных

системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Можно выделить два основных способа ее решения: реализация обмена в режиме ПДП с «захватом цикла» и в режиме ПДП с блокировкой процессора.Существуют две разновидности прямого доступа к памяти с «захватом цикла». Наиболее простой способ организации ПДП состоит в том, что для обмена используются те машинные циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора.

Слайд 28 Наиболее распространенным является ПДП с «захватом цикла»

и принудительным отключением процессора от шин системного интерфейса. Для реализации

такого режима ПДП системный интерфейс микрокомпьютера дополняется двумя линиями для передачи управляющих сигналов «Требование прямого доступа к памяти» (ТПДП) и «Предоставление прямого доступа к памяти» (ППДП).

Слайд 29

Применение в компьютере обмена данными с ВУ в

режиме ПДП всегда требует предварительной подготовки, а именно: для каждого

ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер, т. е. количество записываемых в память или читаемых из памяти байтов (слов) информации.На практике любой сеанс обмена данными с ВУ в режиме ПДП всегда инициируется программой, реализуемой процессором, и включает два следующих этапа.

На этапе подготовки ВУ к очередному сеансу обмена процессор в режиме программно-управляемого обмена опрашивает состояние ВУ (проверяет его готовность к обмену) и посылает в ВУ команды, обеспечивающие его подготовку к обмену.

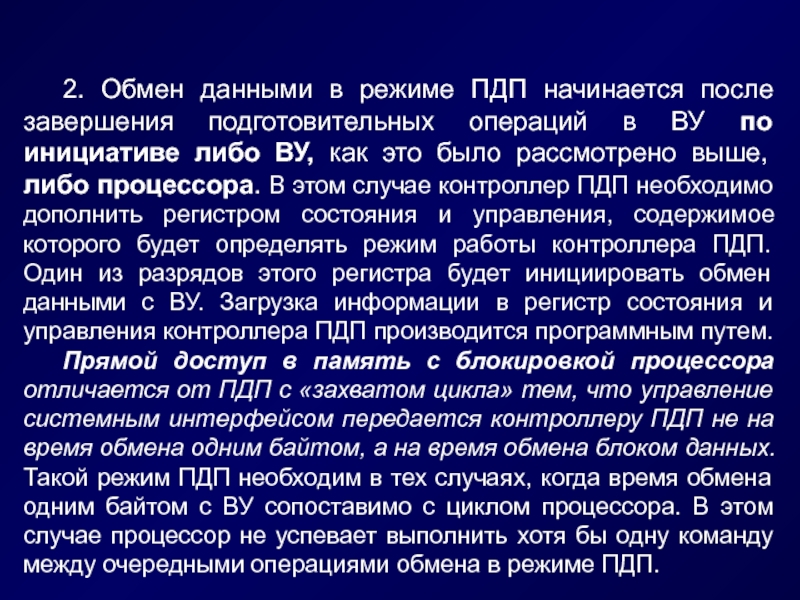

Слайд 30

2. Обмен данными в режиме ПДП начинается после

завершения подготовительных операций в ВУ по инициативе либо ВУ, как

это было рассмотрено выше, либо процессора. В этом случае контроллер ПДП необходимо дополнить регистром состояния и управления, содержимое которого будет определять режим работы контроллера ПДП. Один из разрядов этого регистра будет инициировать обмен данными с ВУ. Загрузка информации в регистр состояния и управления контроллера ПДП производится программным путем.Прямой доступ в память с блокировкой процессора отличается от ПДП с «захватом цикла» тем, что управление системным интерфейсом передается контроллеру ПДП не на время обмена одним байтом, а на время обмена блоком данных. Такой режим ПДП необходим в тех случаях, когда время обмена одним байтом с ВУ сопоставимо с циклом процессора. В этом случае процессор не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП.