Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Операционные элементы

Содержание

- 1. Операционные элементы

- 2. 1. Комбинационные ОЭ (без памяти)а) Преобразователи

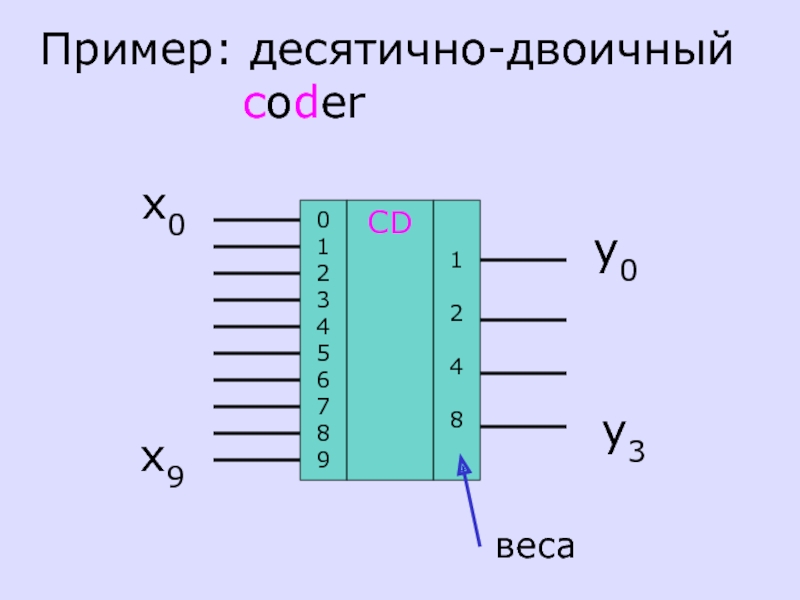

- 3. 0123456789CD1248x0x9y0y3Пример: десятично-двоичный coderвеса

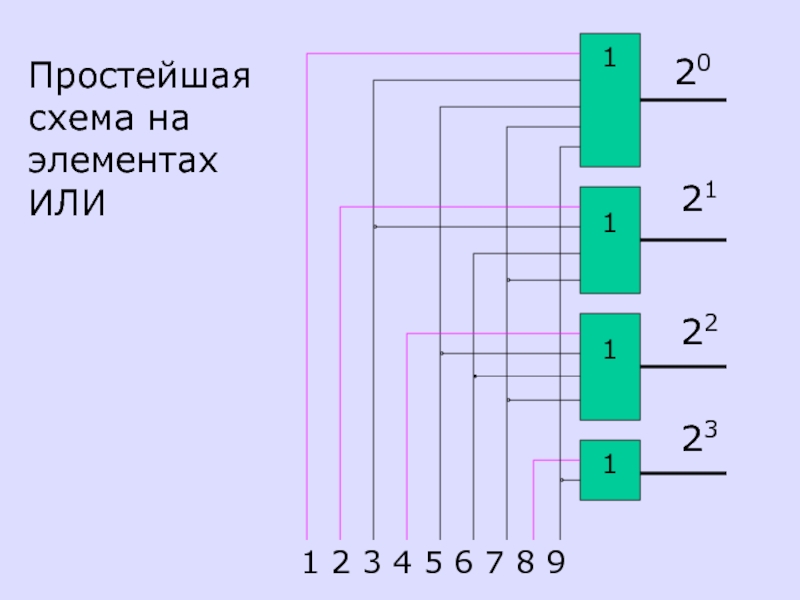

- 4. Простейшая схема на элементах ИЛИ

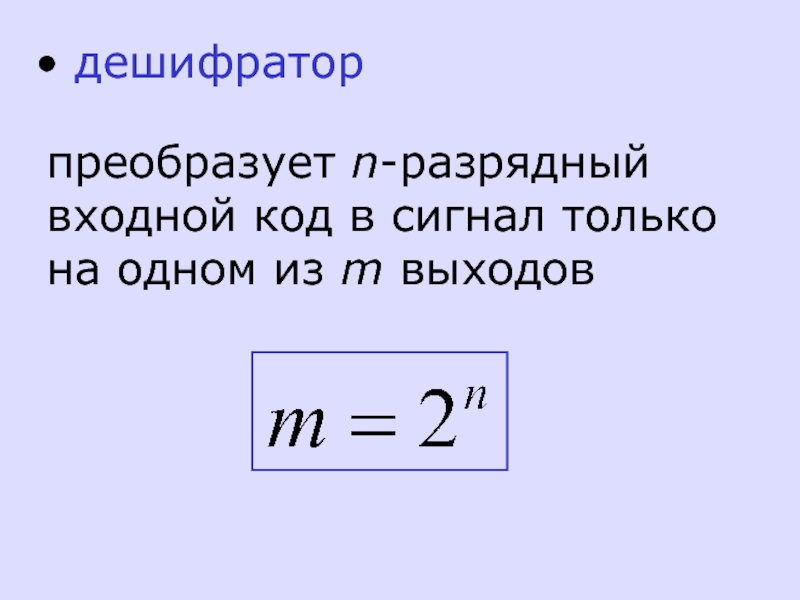

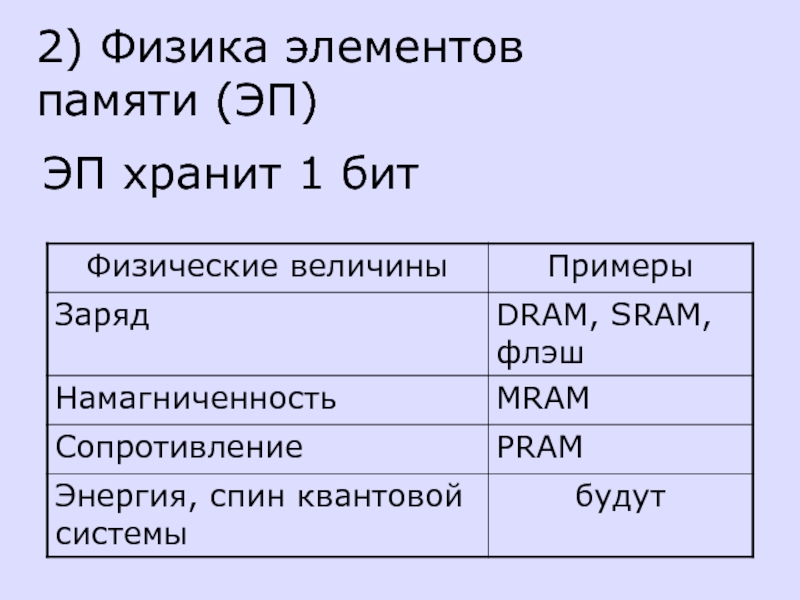

- 5. дешифраторпреобразует n-разрядный входной код в сигнал только на одном из m выходов

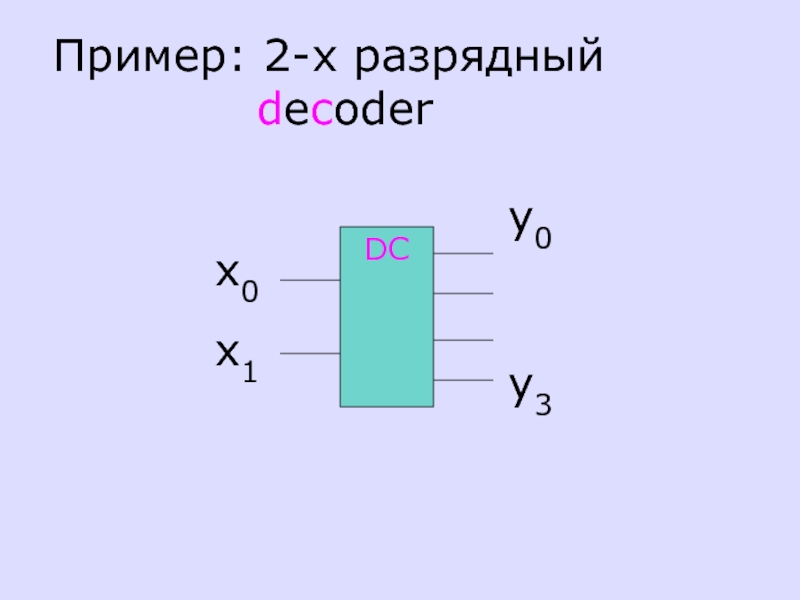

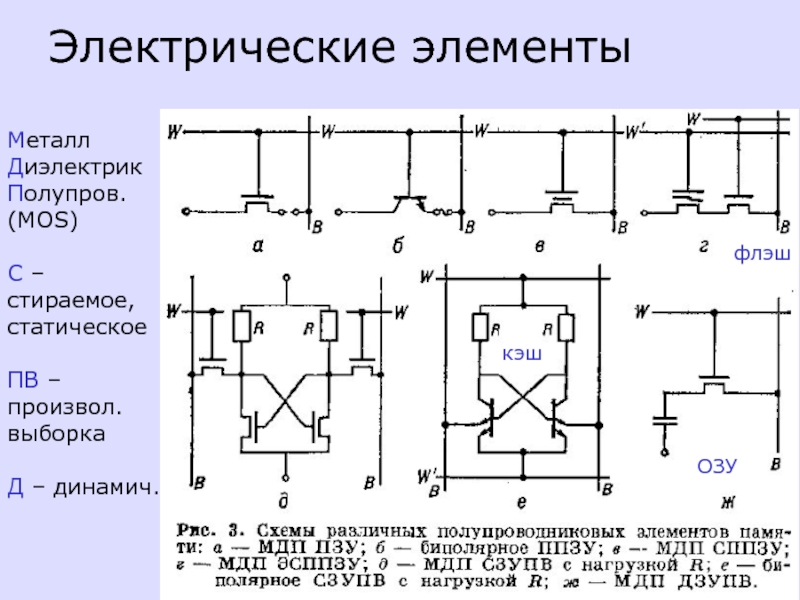

- 6. DC Пример: 2-х разрядный decoderx0x1y0y3

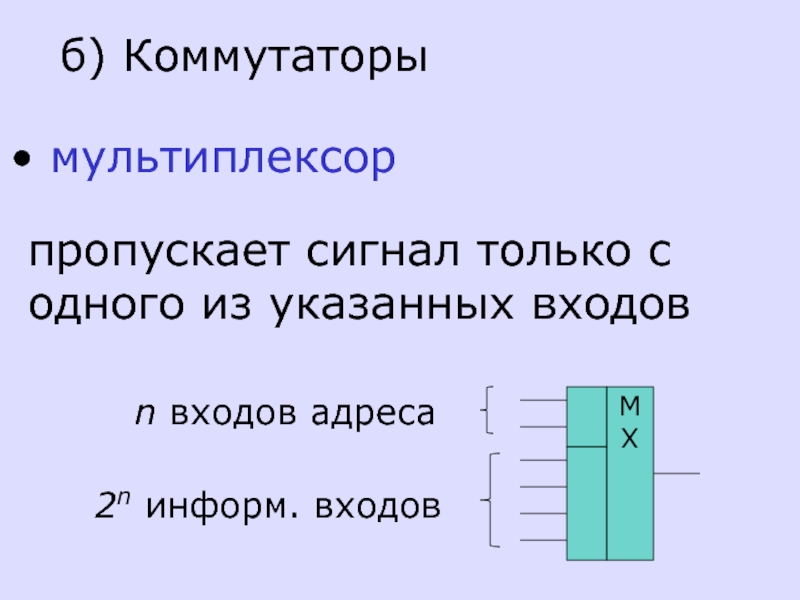

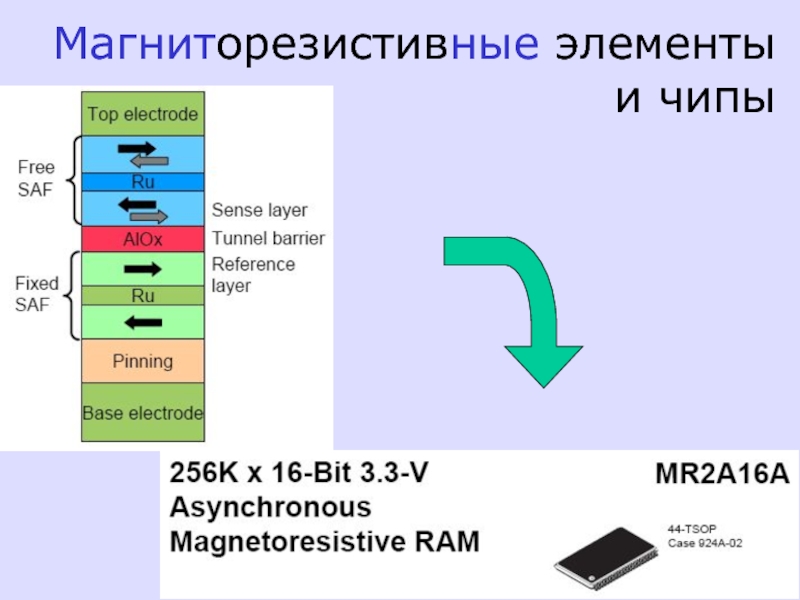

- 7. б) Коммутаторы мультиплексорпропускает сигнал только с одного из указанных входовMXn входов адреса2n информ. входов

- 8. демультиплексорпосылает входной сигнал на указанный выходDMXA0A1xy0y3

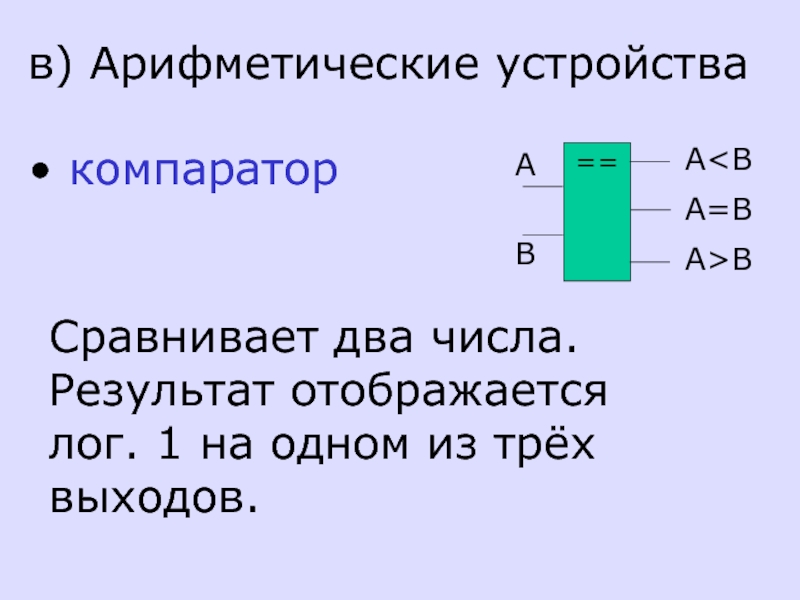

- 9. в) Арифметические устройства компараторСравнивает два числа. Результат отображается лог. 1 на одном из трёх выходов.

- 10. Слайд 10

- 11. сумматорСкладывает несколько чисел.Двоичный сумматор используется также для операций вычитания, умножения и деления.SMPLABSP

- 12. Одноразрядный сумматор с переносом

- 13. 2. Триггерыа) Триггер – это ОЭ, имеющий два устойчивых выходных состояния.Trigger – спусковой крючок, защёлка.

- 14. Устойчивость вызвана наличием обратных связей – выход одного замыкается на вход другого.1 1 RSПример:RS-триггер

- 15. R – resetS – set– прямой выход– инверсный выходСостояние RS-триггера – уровень сигнала на

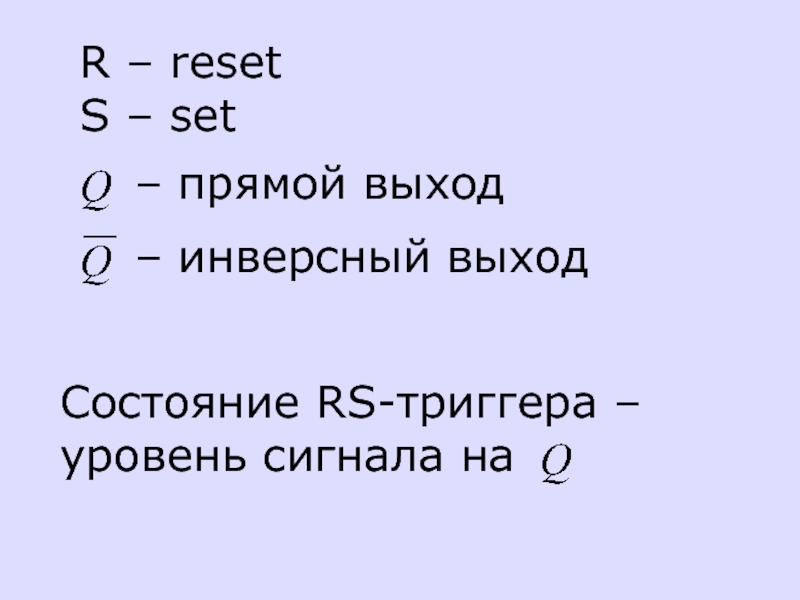

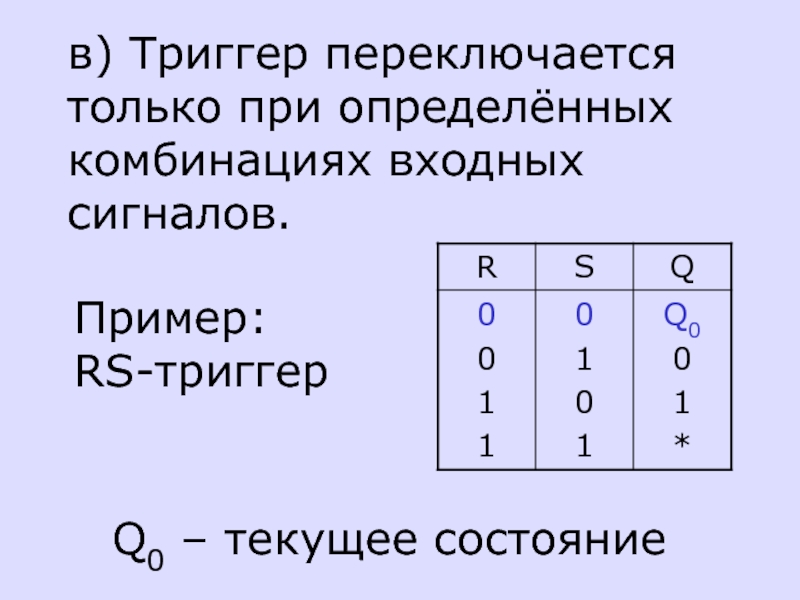

- 16. в) Триггер переключается только при определённых комбинациях входных сигналов.Пример:RS-триггерQ0 – текущее состояние

- 17. * – оба выходных сигнала нулевые:комбинация R=S=1 запрещённаяПосле R=S=1 RS-триггер переходит в случайное состояние

- 18. У RS-триггера есть четыре режима работы: хранение информации запись нуля запись единицы запрещённый

- 19. RS-триггер является базовым элементом ЛУ с памятью

- 20. г) Триггеры без запрещённых комбинацийJK-триггерD-триггер (delay)T-триггер (делитель ν)

- 21. д) СинхронизацияТриггер называется синхронным, если меняет состояние только при подаче импульса на спец. вход C (синхронизирующий)с

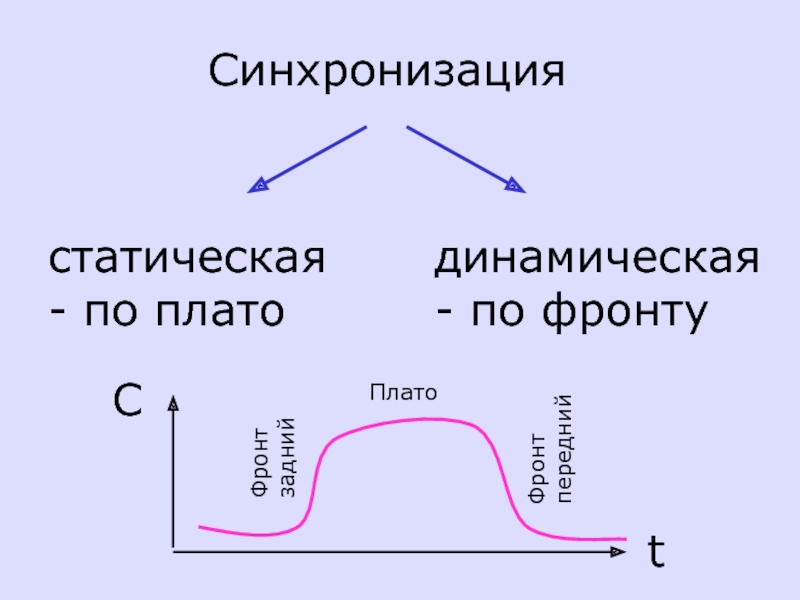

- 22. Синхронизациястатическая - по плато динамическая- по фронтуПлатоФронт переднийСtФронт задний

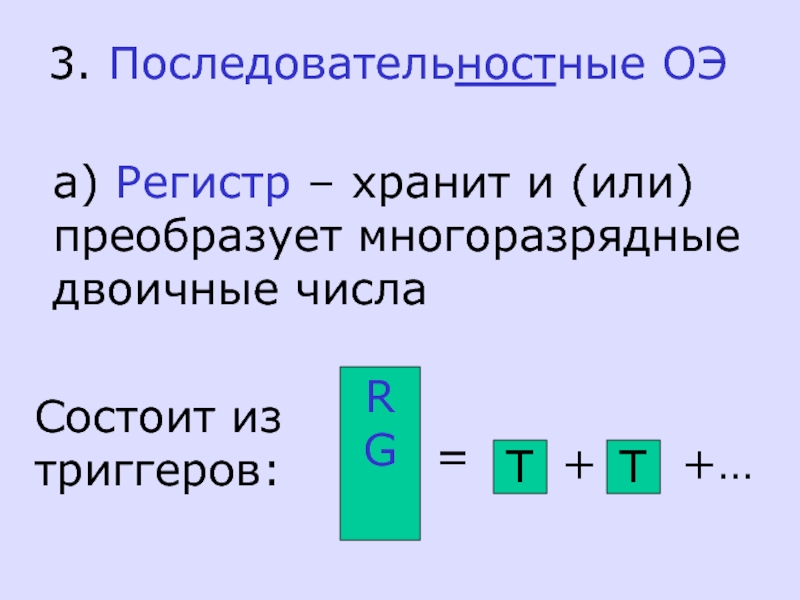

- 23. 3. Последовательностные ОЭа) Регистр – хранит и (или) преобразует многоразрядные двоичные числа Состоит из триггеров:RG=TT++…

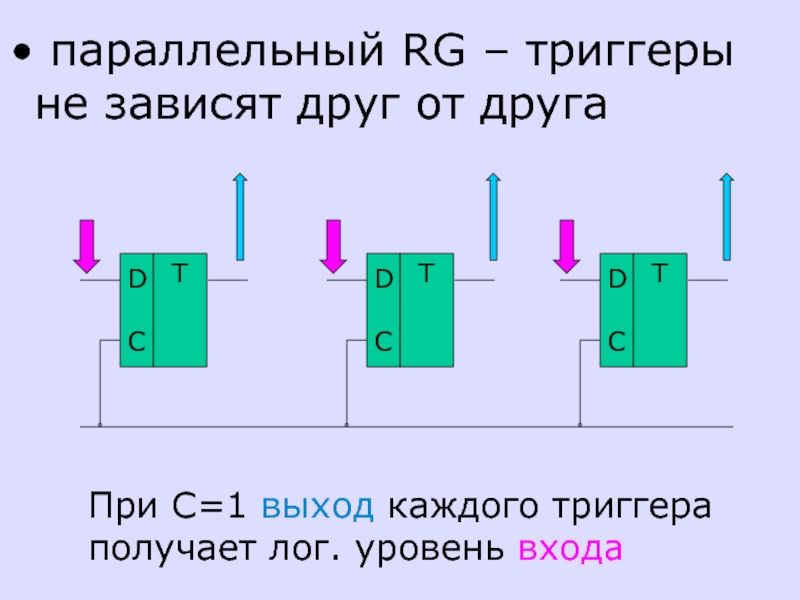

- 24. параллельный RG – триггеры не зависят

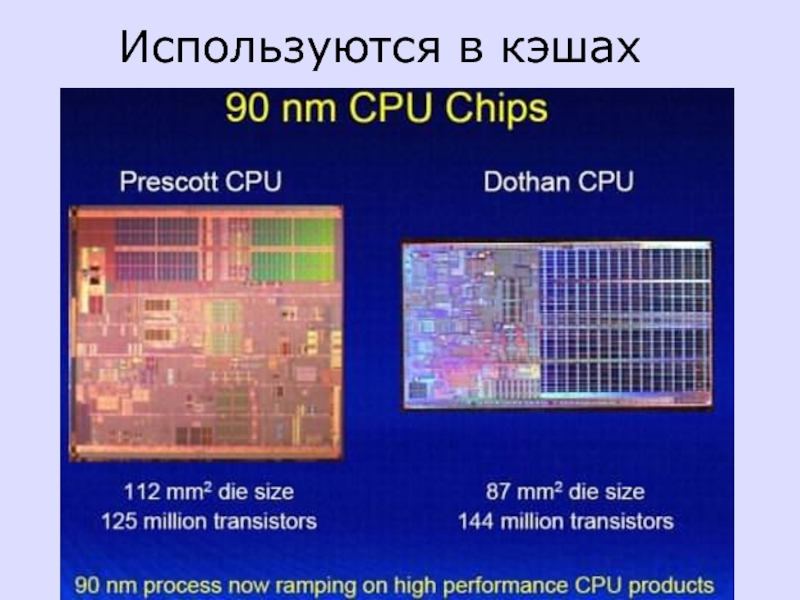

- 25. Используются в кэшах

- 26. последовательный RG – выход каждого триггера идёт на вход следующегоDCTDCTDCTдинамическая синхр.

- 27. Фронт делают узким настолько, чтобы сигнал успел пройти не более одного триггера!

- 28. Каждый синхроимпульс сдвигает код числа на один разряд1000010000100001Н-р:сдвигающийрегистр

- 29. Для записи N-разрядного числа нужно N тактов.

- 30. А для чтения достаточно одного такта!Сдвиговым RG можно преобразовать последов. код в парал.

- 31. универсальный RG – может записывать и

- 32. Вывод:благодаря своей многофункциональности регистры стали одними из самых распр. ОЭ

- 33. б) Счётчик – запоминает кол-во Nf пришедших

- 34. §4. Микросхемы памяти1) Виды ЗУ ОЗУ – оперативные ПЗУ – постоянные ППЗУ – перепрограммируемые постоянные

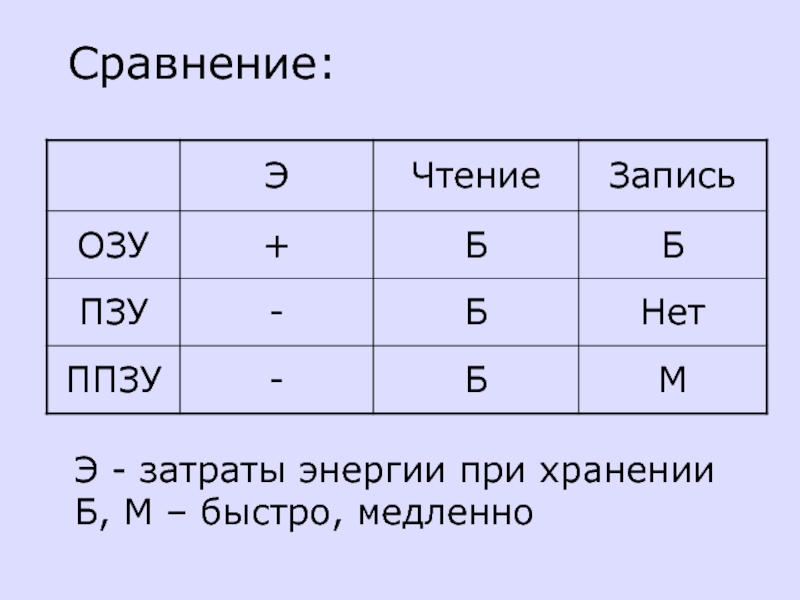

- 35. Сравнение: Э - затраты энергии при храненииБ, М – быстро, медленно

- 36. Для ППЗУ также указывают гарантийное время хранения допустимое число циклов перезаписи

- 37. 2) Физика элементов памяти (ЭП)ЭП хранит 1 бит

- 38. Электрические элементыМеталл Диэлектрик Полупров.(MOS)С – стираемое, статическоеПВ – произвол. выборкаД – динамич.флэшкэшОЗУ

- 39. Магниторезистивные элементы и чипы

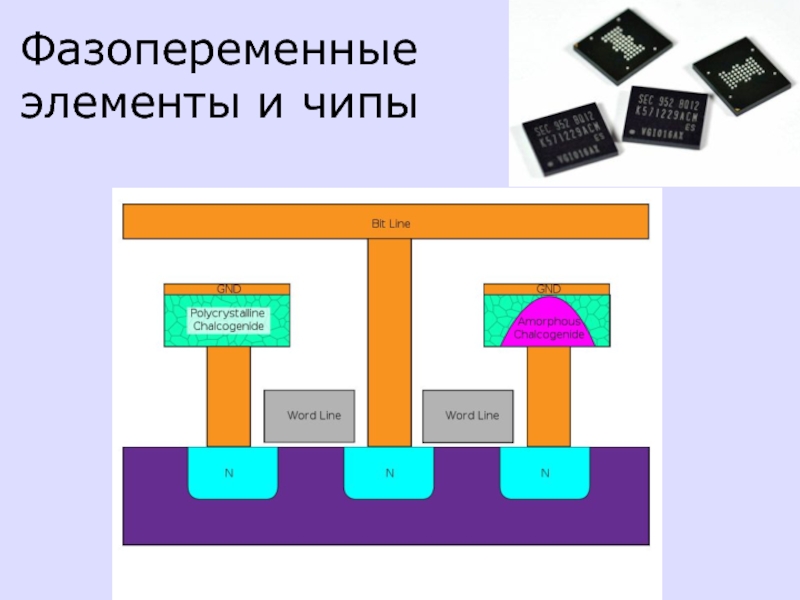

- 40. Фазопеременные элементы и чипы

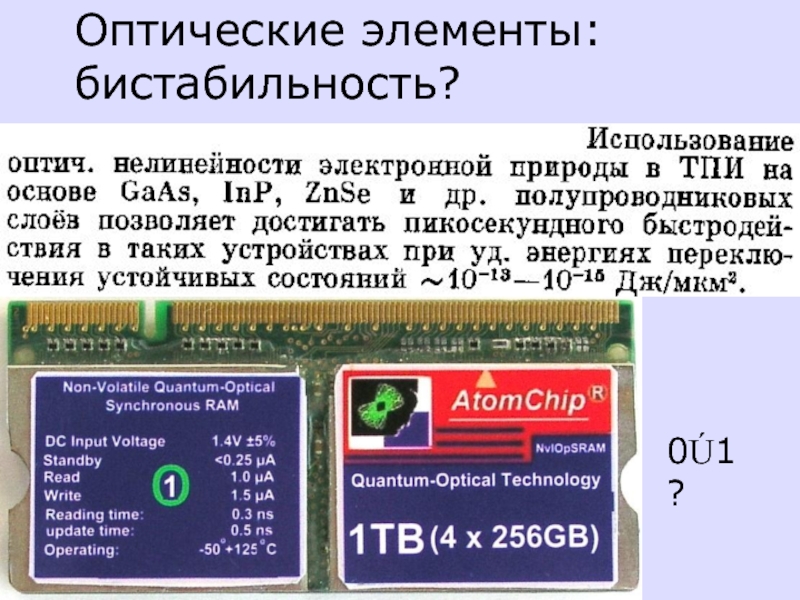

- 41. Оптические элементы: бистабильность?0Ú1?

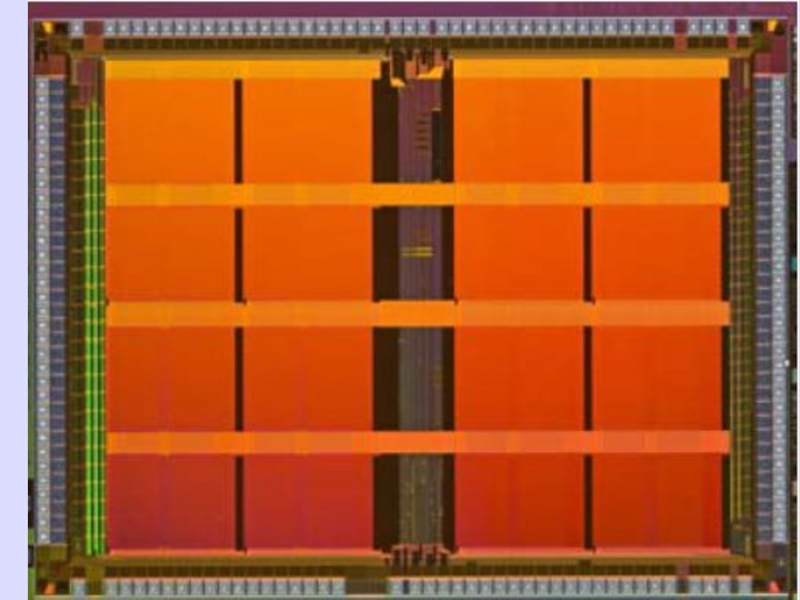

- 42. 64 слова по 64 бита (512 байт)на 1 мкм2 ?

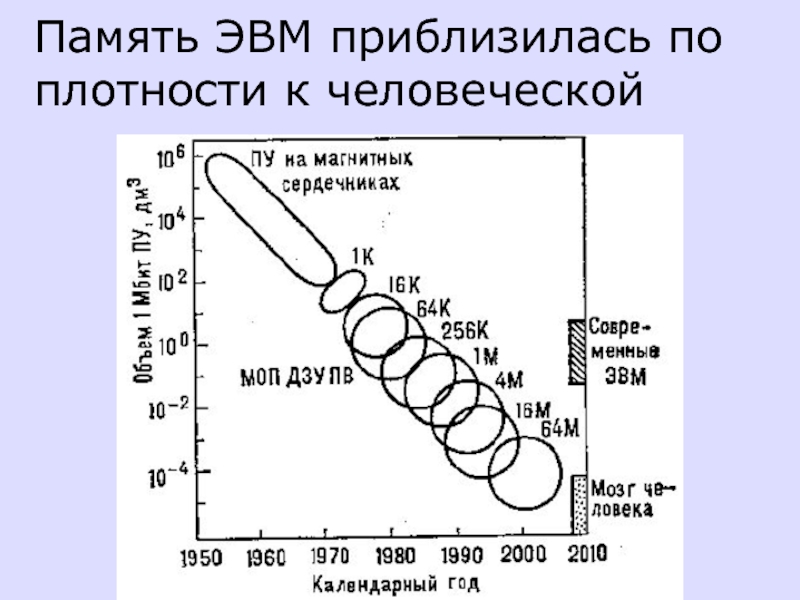

- 43. Память ЭВМ приблизилась по плотности к человеческой

- 44. 3) Организация МПа) Логическая: - N ячеек

- 45. Страница – область памяти фиксированного размера(н-р, 4

- 46. Накопитель – матрица из ЭПАдрес ЭП: номер строки и номер столбцаб) Физическая

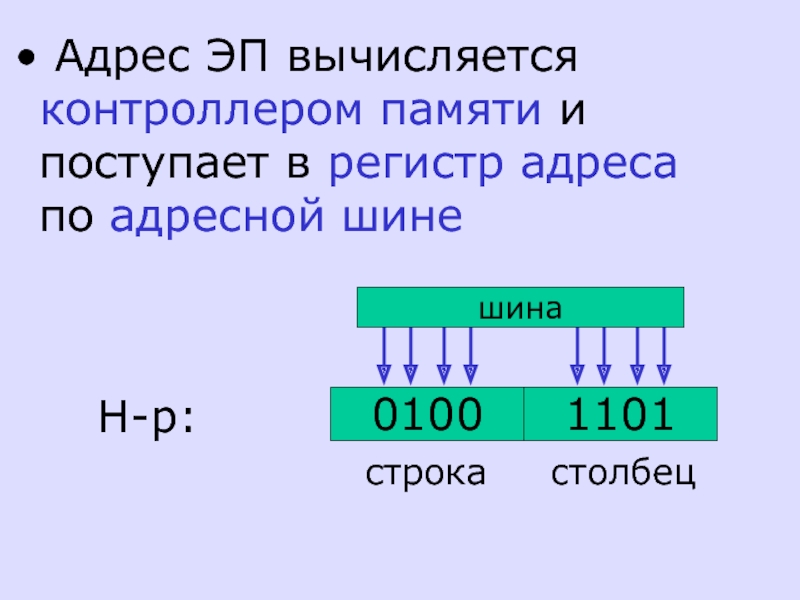

- 47. Адрес ЭП вычисляется контроллером памяти и поступает в регистр адреса по адресной шинеН-р:

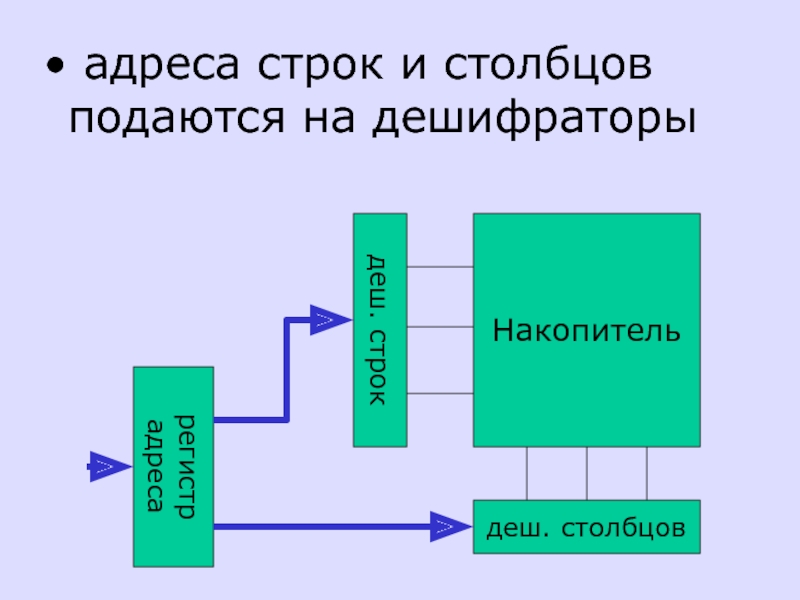

- 48. адреса строк и столбцов подаются на дешифраторыНакопительдеш. столбцовдеш. строкрегистрадреса

- 49. режимы работы ЭП- хранение: отключается от

- 50. Слайд 50

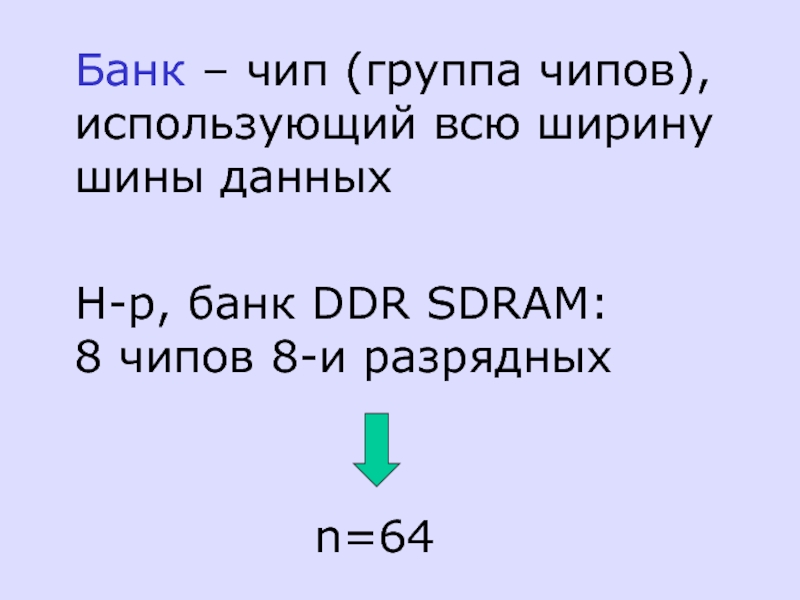

- 51. Банк – чип (группа чипов), использующий всю

- 52. Скачать презентанцию

1. Комбинационные ОЭ (без памяти)а) Преобразователи кодов шифраторпреобразует сигнал на одном из n входов в m-разрядный выходной код

Слайды и текст этой презентации

Слайд 1§3. Операционные элементы

(ОЭ)

ОЭ – ЛУ, выполняющие не элементарные операции.

Н-р, сумматоры,

счётчики, …

Слайд 21. Комбинационные ОЭ

(без памяти)

а) Преобразователи кодов

шифратор

преобразует сигнал

на одном из n входов в m-разрядный выходной код

Слайд 7б) Коммутаторы

мультиплексор

пропускает сигнал только с одного из указанных входов

MX

n

входов адреса

2n информ. входов

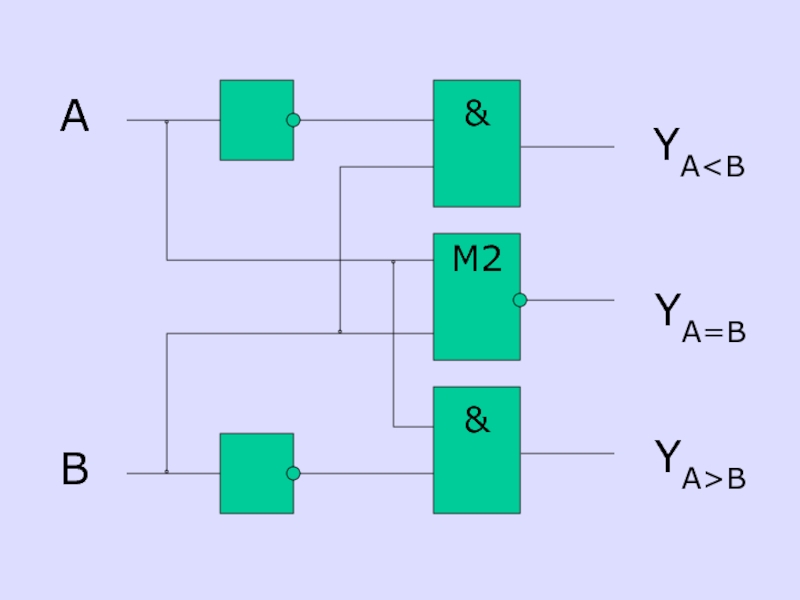

Слайд 9в) Арифметические устройства

компаратор

Сравнивает два числа. Результат отображается лог. 1

на одном из трёх выходов.

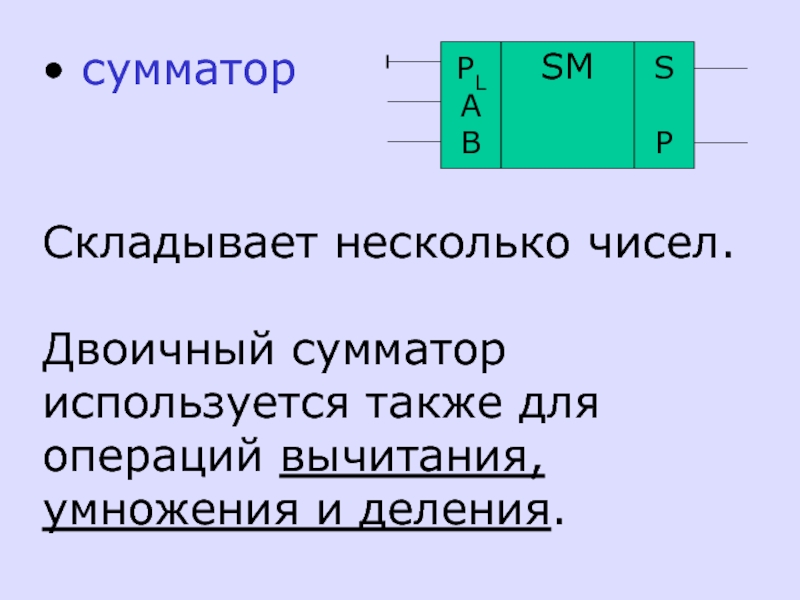

Слайд 11 сумматор

Складывает несколько чисел.

Двоичный сумматор используется также для операций вычитания,

умножения и деления.

SM

PL

A

B

S

P

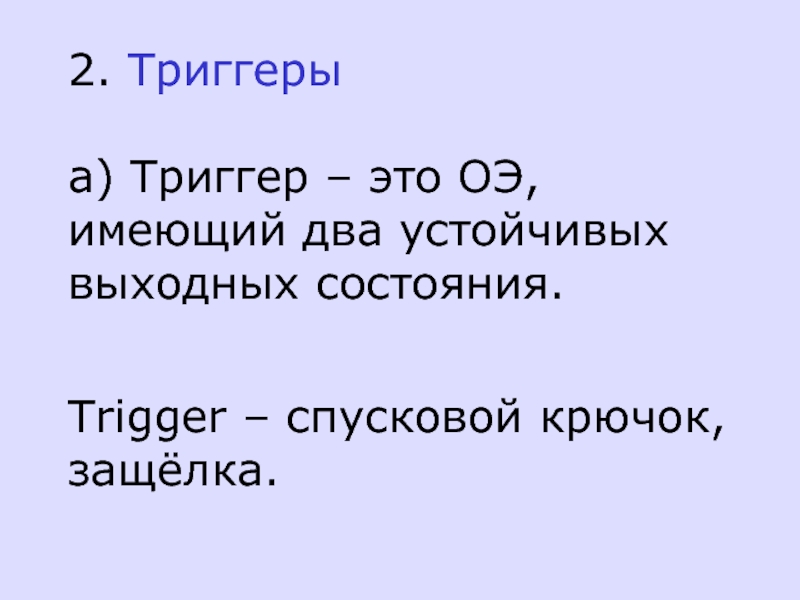

Слайд 132. Триггеры

а) Триггер – это ОЭ, имеющий два устойчивых выходных

состояния.

Trigger – спусковой крючок, защёлка.

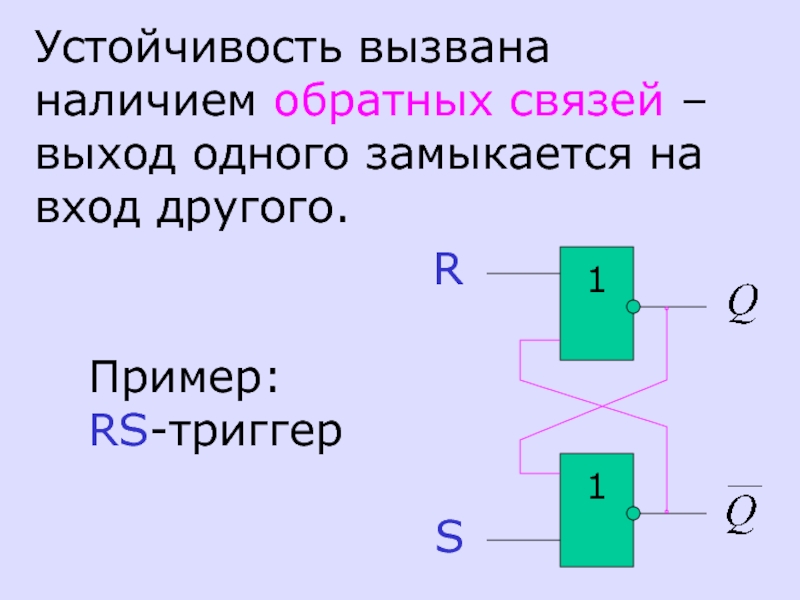

Слайд 14Устойчивость вызвана наличием обратных связей – выход одного замыкается на

вход другого.

1

1

R

S

Пример:

RS-триггер

Слайд 16в) Триггер переключается только при определённых комбинациях входных сигналов.

Пример:

RS-триггер

Q0 –

текущее состояние

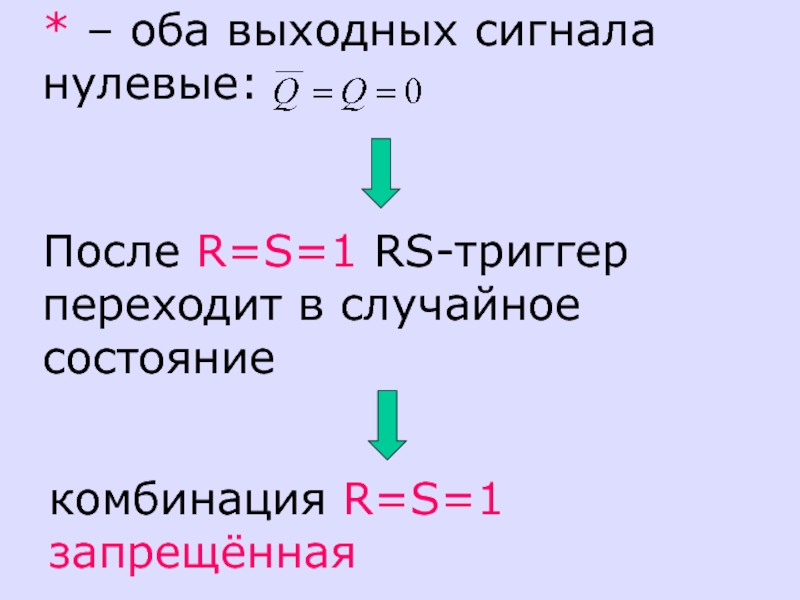

Слайд 17* – оба выходных сигнала нулевые:

комбинация R=S=1 запрещённая

После R=S=1 RS-триггер

переходит в случайное состояние

Слайд 18У RS-триггера есть четыре режима работы:

хранение информации

запись нуля

запись единицы

запрещённый

Слайд 21д) Синхронизация

Триггер называется синхронным, если меняет состояние только при подаче

импульса на спец. вход C (синхронизирующий)

с

Слайд 22Синхронизация

статическая - по плато

динамическая

- по фронту

Плато

Фронт передний

С

t

Фронт задний

Слайд 233. Последовательностные ОЭ

а) Регистр – хранит и (или) преобразует многоразрядные

двоичные числа

Состоит из

триггеров:

RG

=

T

T

+

+…

Слайд 24 параллельный RG – триггеры не зависят друг от друга

D

C

T

D

C

T

D

C

T

При

С=1 выход каждого триггера получает лог. уровень входа

Слайд 26 последовательный RG – выход каждого триггера идёт на вход

следующего

D

C

T

D

C

T

D

C

T

динамическая синхр.

Слайд 28 Каждый синхроимпульс сдвигает код числа на один разряд

1000

0100

0010

0001

Н-р:

сдвигающий

регистр

Слайд 30А для чтения достаточно одного такта!

Сдвиговым RG можно преобразовать последов.

код в парал.

Слайд 31 универсальный RG – может записывать и выдавать числа как

в последов., так и парал. режимах.

Используется для

преобразования кодов

операций

умножения и деленияСлайд 33б) Счётчик – запоминает кол-во Nf пришедших фронтов.

Состоит из цепочки

триггеров, число которых K наз. модулем счёта.

CT

Слайд 34§4. Микросхемы памяти

1) Виды ЗУ

ОЗУ – оперативные

ПЗУ –

постоянные

ППЗУ – перепрограммируемые постоянные

Слайд 38Электрические элементы

Металл Диэлектрик Полупров.

(MOS)

С – стираемое, статическое

ПВ – произвол. выборка

Д

– динамич.

флэш

кэш

ОЗУ

Слайд 443) Организация МП

а) Логическая:

- N ячеек по n

разрядов

- последовательная нумерация

- номер ячейки – адрес

Байт –

минимальная адресуемая единица информации.Обычно n=8