Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Описание памяти с использованием VHDL

Содержание

- 1. Описание памяти с использованием VHDL

- 2. Описание памяти как массиваПамять – это массив

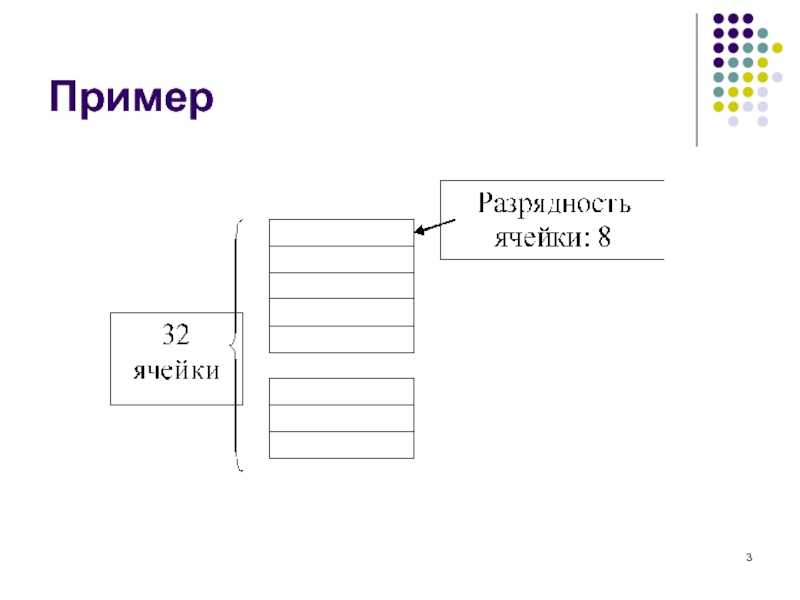

- 3. Пример

- 4. Объявление памятиОписать тип type mem is array

- 5. Пример параметризированного модуляgeneric (addr_width: natural := 5);port

- 6. Преобразование типовunsignedintegersignedstd_logic_vectorsigned ()unsigned ()to_integer ()to_integer ()to_signed ()to_unsigned ()std_logic_vector ()std_logic_vector ()numeric_stdnumeric_stdstandartstd_logic_1164

- 7. ПЗУПри описании ПЗУ прошивка должна определяться при

- 8. ПЗУ – вариант 1. Инициализация.type ROM is

- 9. ПЗУ - вариант 1. Использование.Доступ к памяти:Data_out

- 10. ПЗУ – вариант 1. Пример.library ieee;use ieee.std_logic_1164.all;use

- 11. architecture Behav of ROM is type

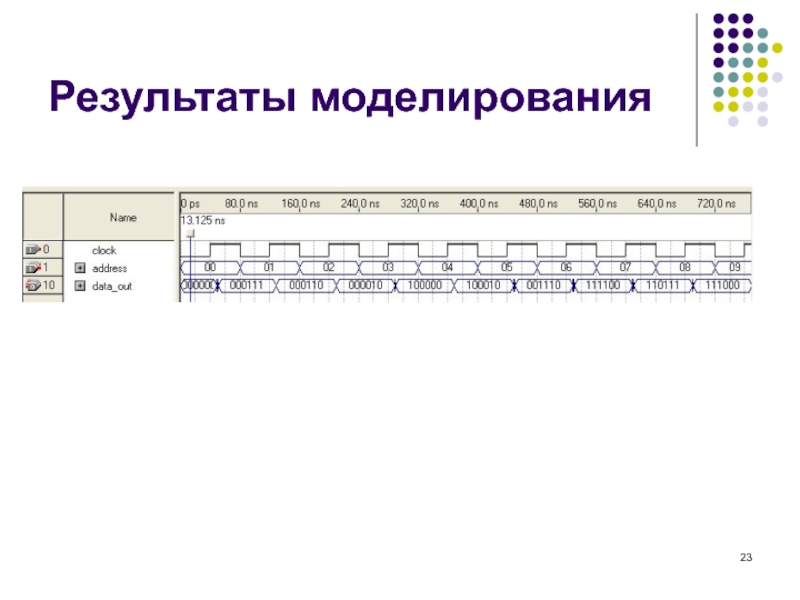

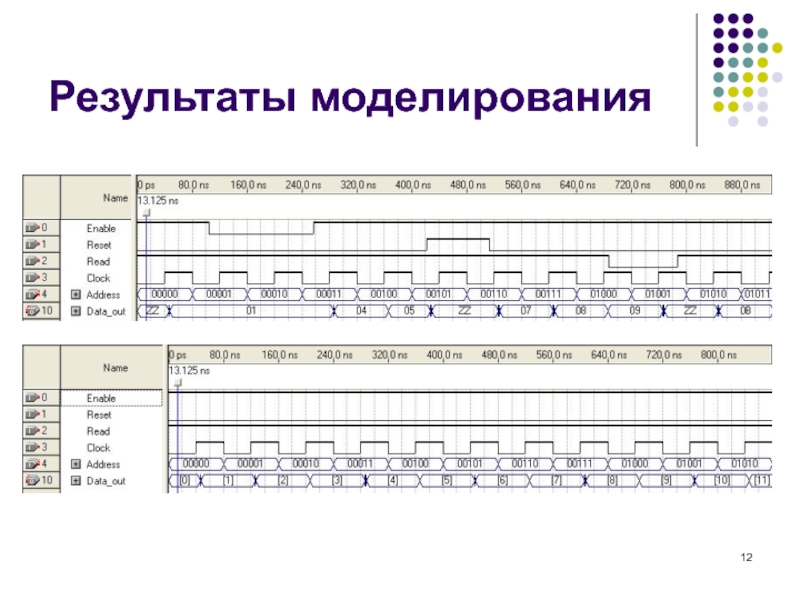

- 12. Результаты моделирования

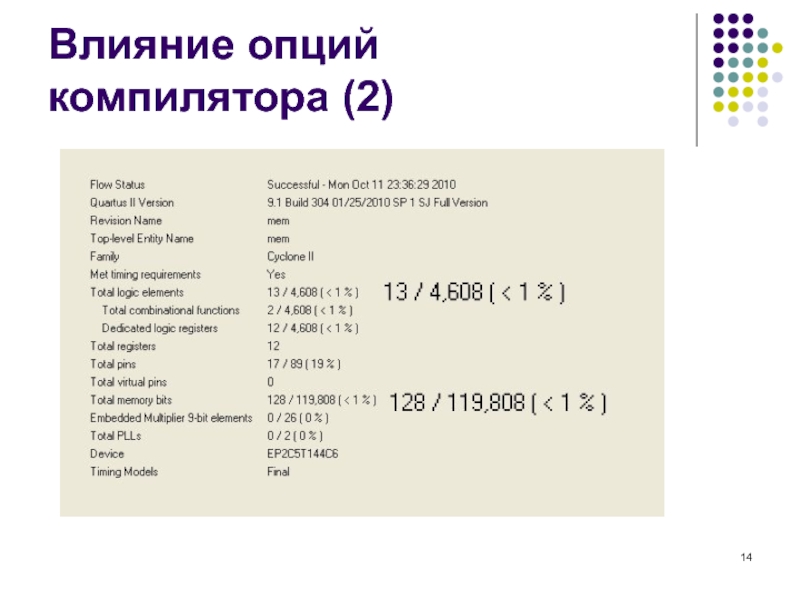

- 13. Влияние опций компилятора (1)

- 14. Влияние опций компилятора (2)

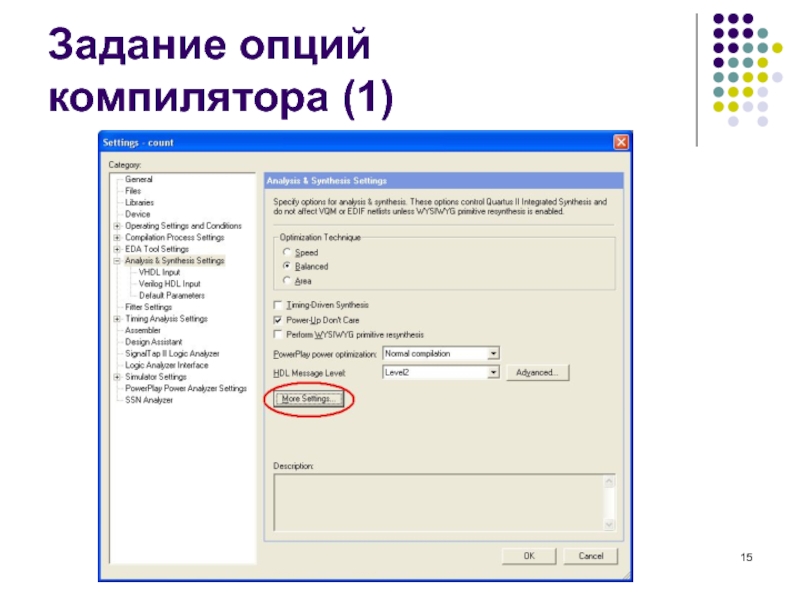

- 15. Задание опций компилятора (1)

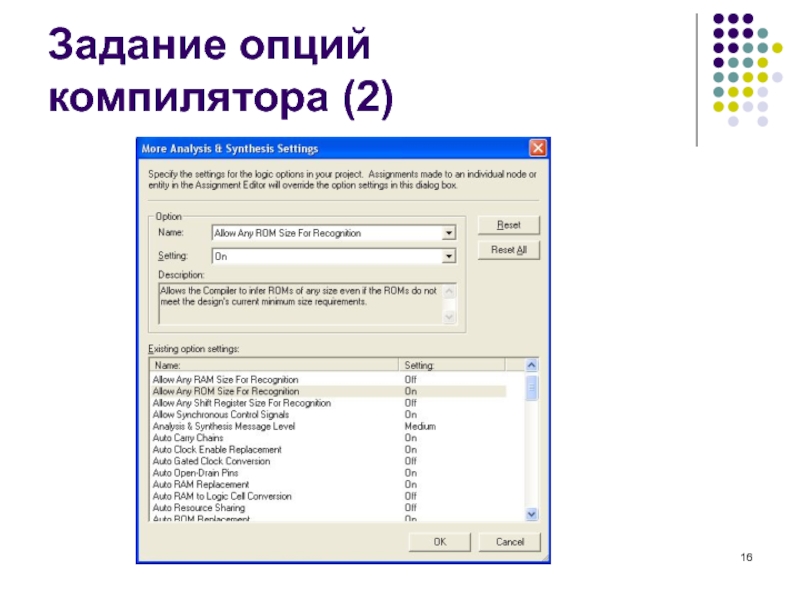

- 16. Задание опций компилятора (2)

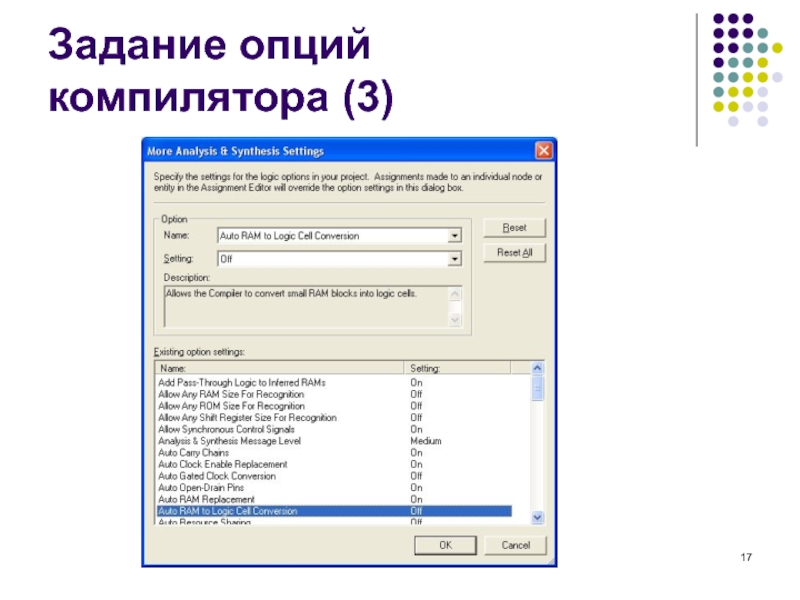

- 17. Задание опций компилятора (3)

- 18. Задание опций компилятора (4)Меню Assignments ->

- 19. ПЗУ – вариант 2. Инициализация.port ( … data : out

- 20. ПЗУ – вариант 2. Использование.case addr is when 0 => data data data data data

- 21. ПЗУ – вариант 2. Пример.LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY

- 22. ARCHITECTURE rtl OF mem IS BEGINPROCESS (clock)BEGIN IF rising_edge

- 23. Результаты моделирования

- 24. ПЗУ – вариант 3. Инициализация (1).type mem_t

- 25. ПЗУ – вариант 3. Инициализация (2).Используем атрибут

- 26. ПЗУ – вариант 3. Инициализация (3).Для использования

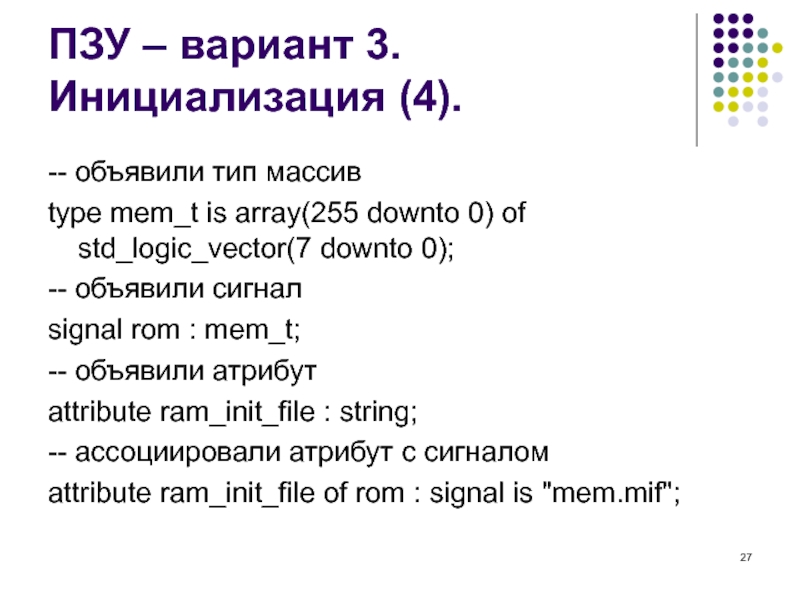

- 27. ПЗУ – вариант 3. Инициализация (4).-- объявили

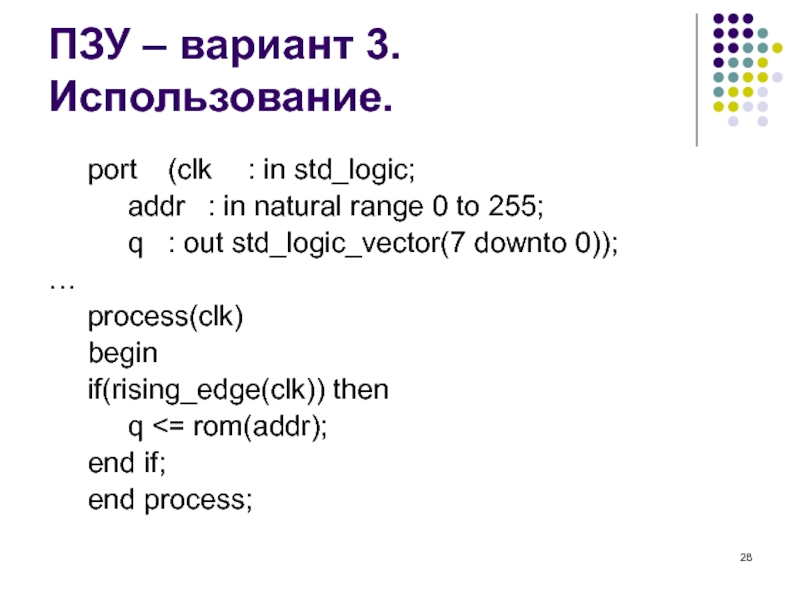

- 28. ПЗУ – вариант 3. Использование. port (clk : in

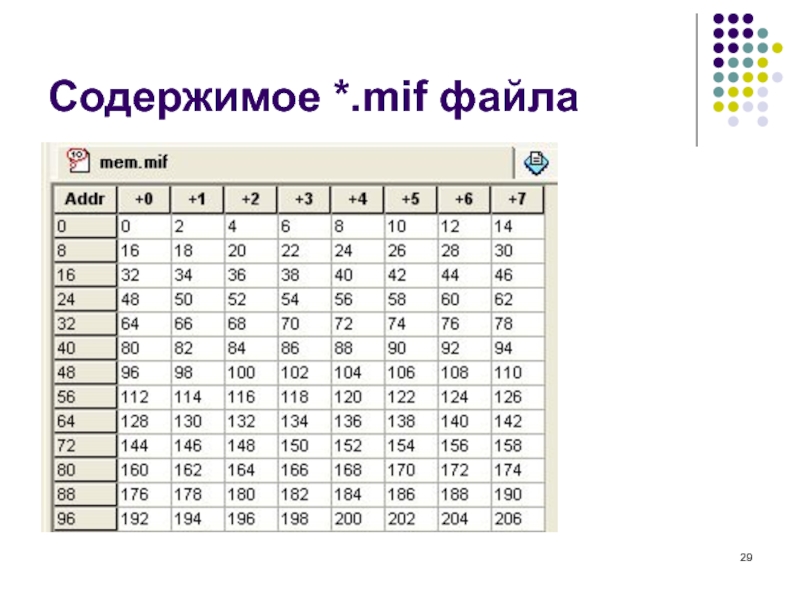

- 29. Содержимое *.mif файла

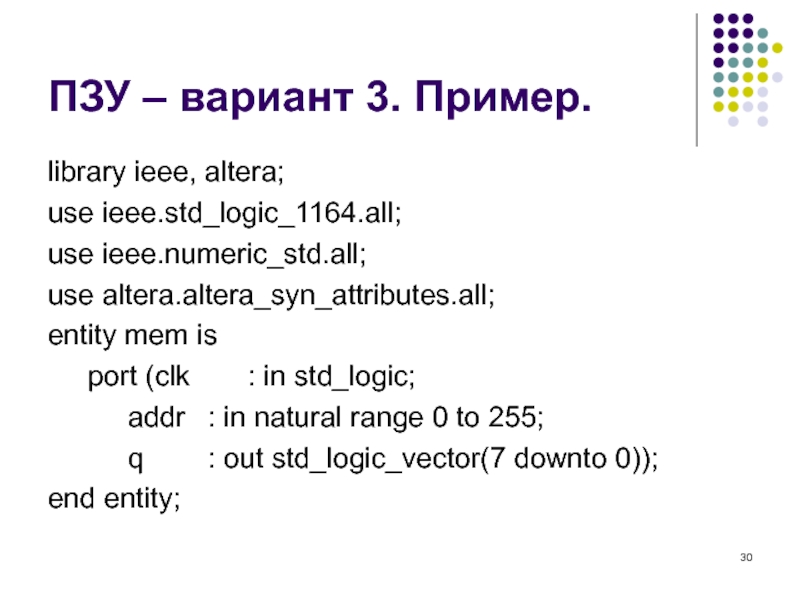

- 30. ПЗУ – вариант 3. Пример.library ieee, altera;use

- 31. architecture rtl of mem is type mem_t is

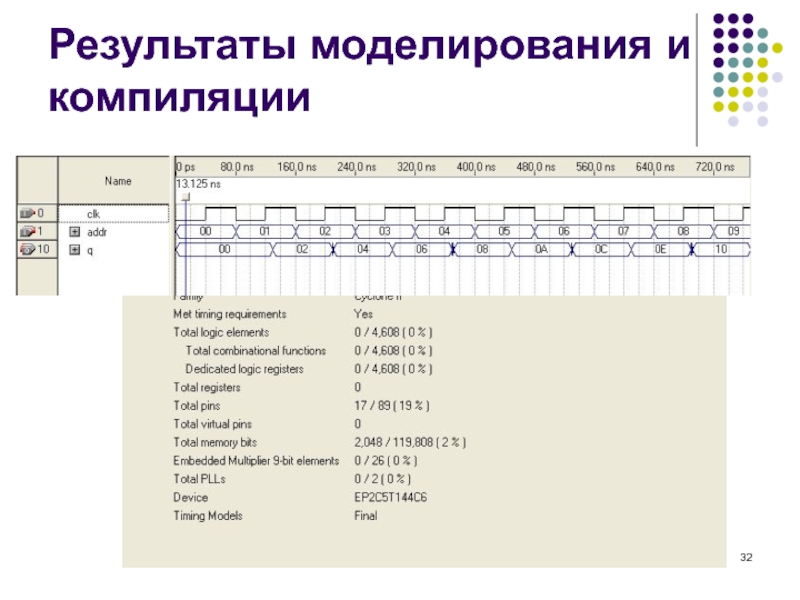

- 32. Результаты моделирования и компиляции

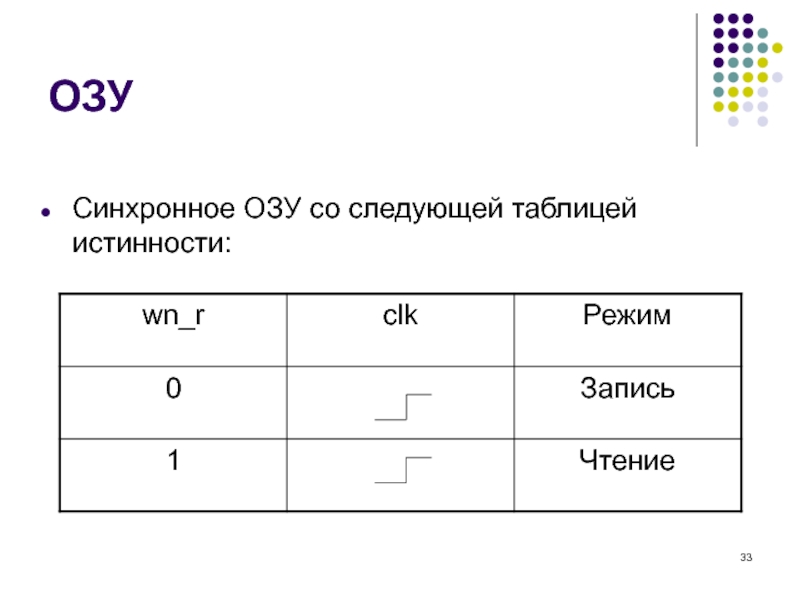

- 33. ОЗУСинхронное ОЗУ со следующей таблицей истинности:

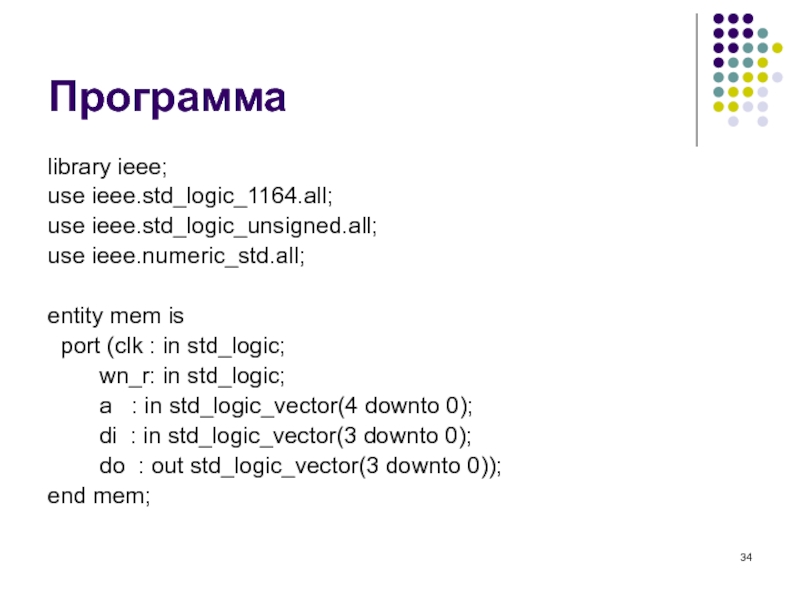

- 34. Программаlibrary ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;use ieee.numeric_std.all;entity

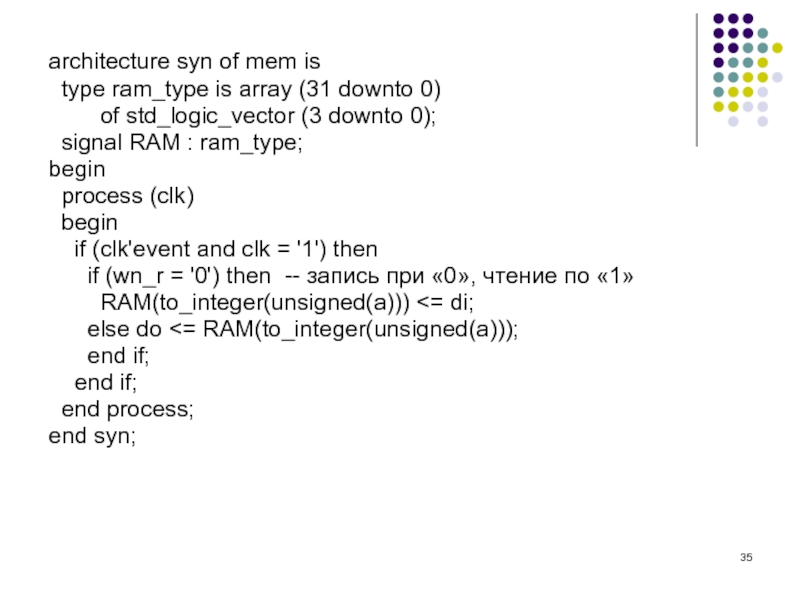

- 35. architecture syn of mem is type

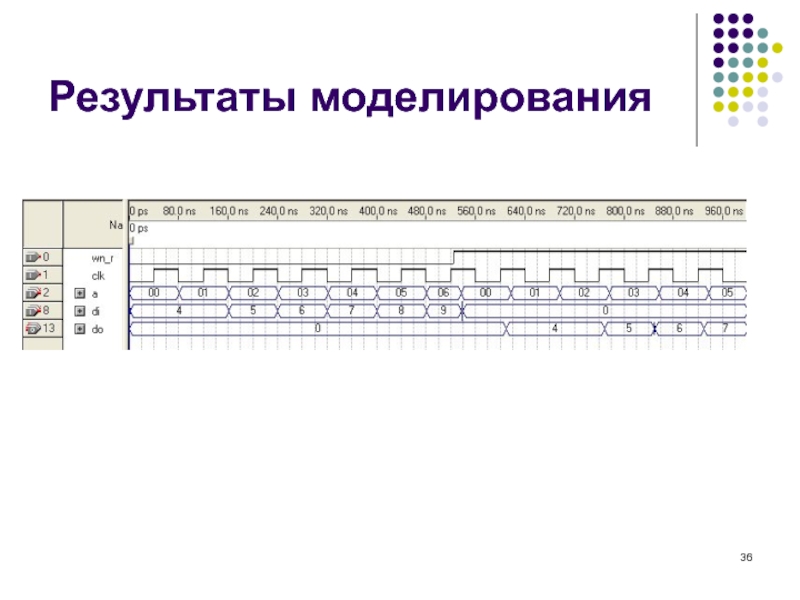

- 36. Результаты моделирования

- 37. Двухпортовая памятьОЗУПорт АПорт БАдрес ААдрес БВходные данные АВыходные данные АВходные данные БВыходные данные Б

- 38. Достоинства двухпортовой памятиВозможность одновременного чтения и записи данных в один блок памяти.Увеличение быстродействия.

- 39. Проблемы двухпортовой памятиНеобходимо четко определить поведение во

- 40. library ieee;use ieee.std_logic_1164.all;entity mem is generic ( DATA_WIDTH :

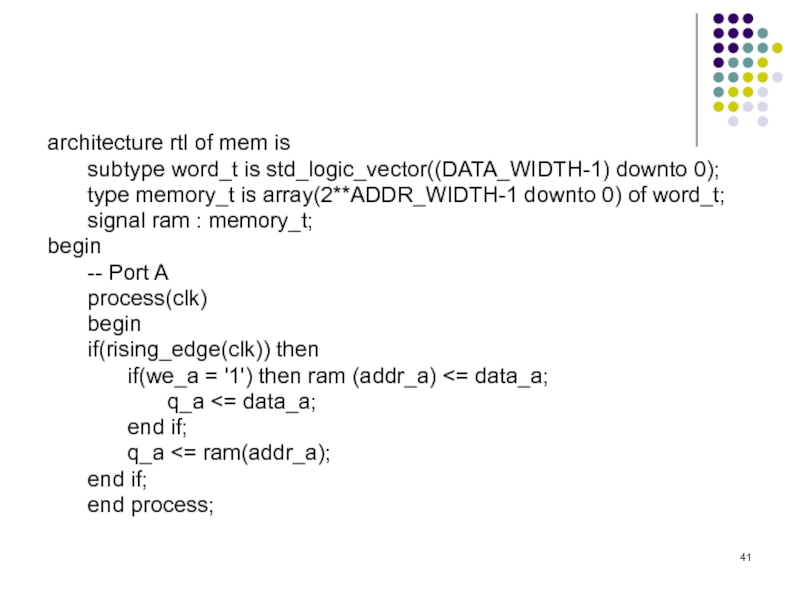

- 41. architecture rtl of mem is subtype word_t is

- 42. -- Port B process(clk) begin if(rising_edge(clk)) then if(we_b = '1') then ram(addr_b)

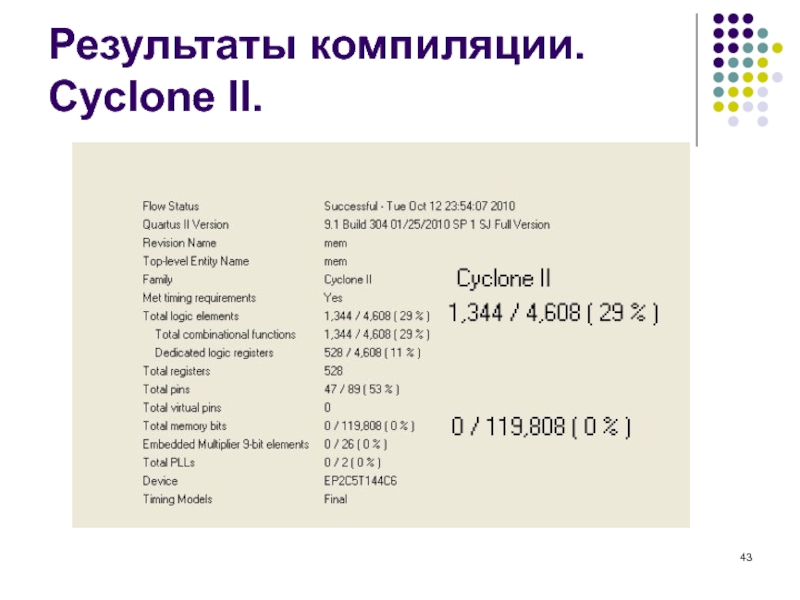

- 43. Результаты компиляции. Cyclone II.

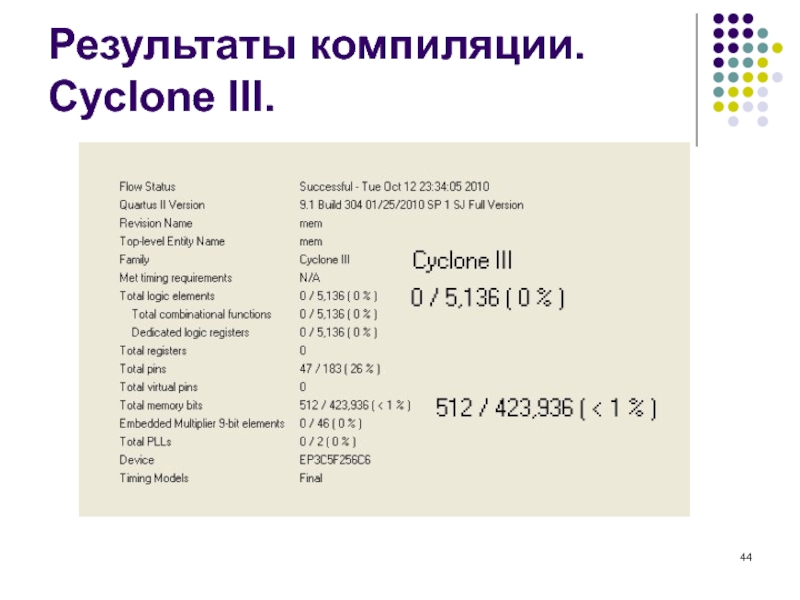

- 44. Результаты компиляции. Cyclone III.

- 45. Результаты моделирования

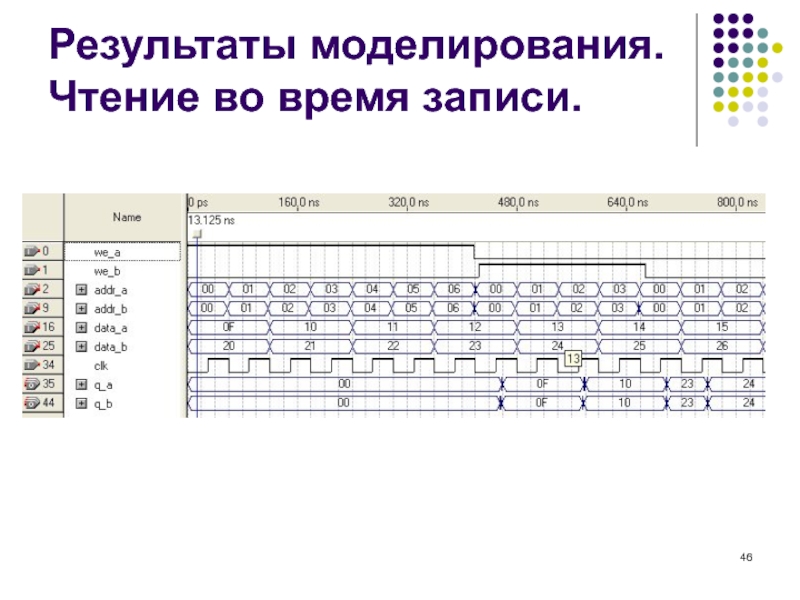

- 46. Результаты моделирования. Чтение во время записи.

- 47. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2Описание памяти как массива

Память – это массив векторов.

Количество ячеек (векторов)

определяет разрядность.

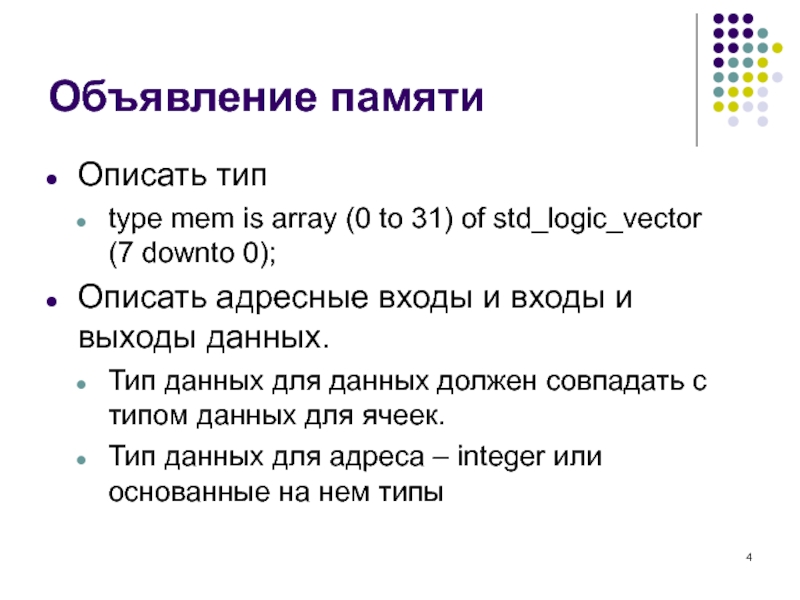

Слайд 4Объявление памяти

Описать тип

type mem is array (0 to 31)

of std_logic_vector

(7 downto 0);

Описать адресные входы и входы и

выходы данных. Тип данных для данных должен совпадать с типом данных для ячеек.

Тип данных для адреса – integer или основанные на нем типы

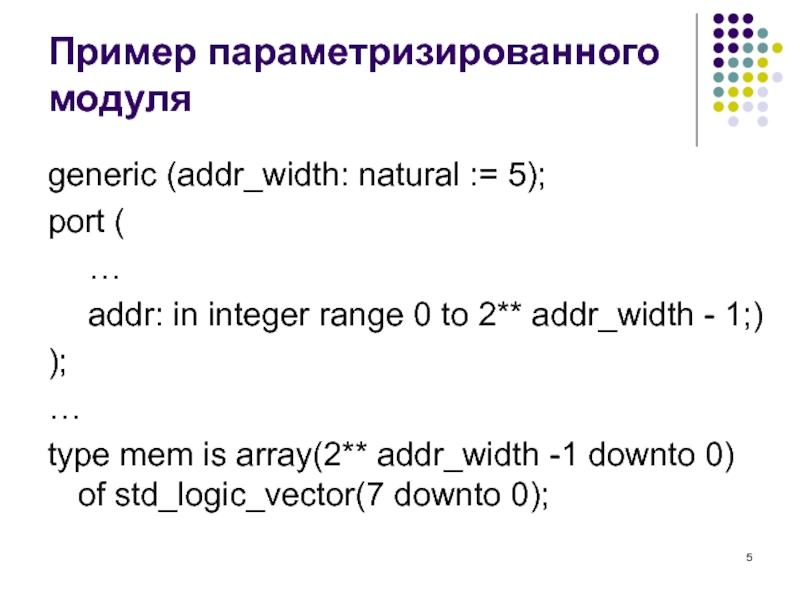

Слайд 5Пример параметризированного модуля

generic (addr_width: natural := 5);

port (

…

addr: in integer

range 0 to 2** addr_width - 1;)

);

…

type mem is array(2**

addr_width -1 downto 0) of std_logic_vector(7 downto 0);Слайд 6Преобразование типов

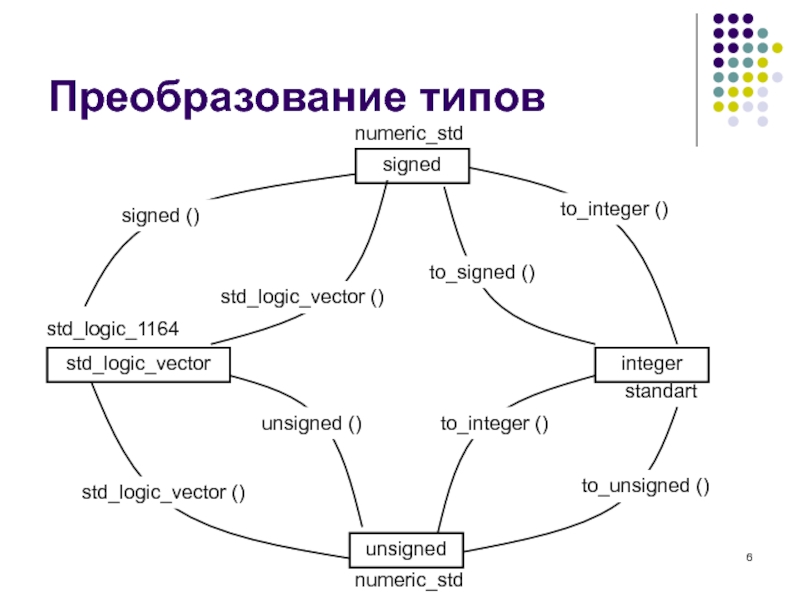

unsigned

integer

signed

std_logic_vector

signed ()

unsigned ()

to_integer ()

to_integer ()

to_signed ()

to_unsigned ()

std_logic_vector ()

std_logic_vector ()

numeric_std

numeric_std

standart

std_logic_1164

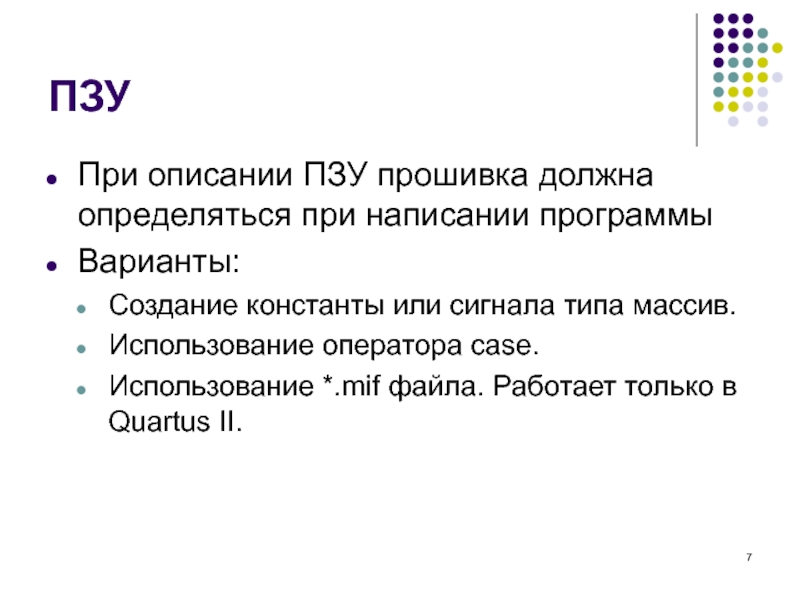

Слайд 7ПЗУ

При описании ПЗУ прошивка должна определяться при написании программы

Варианты:

Создание константы

или сигнала типа массив.

Использование оператора case.

Использование *.mif файла. Работает только

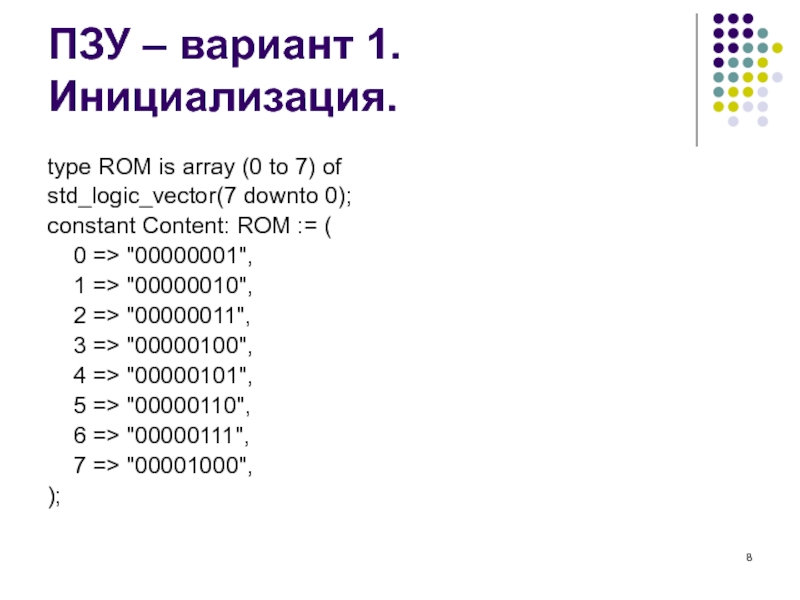

в Quartus II.Слайд 8ПЗУ – вариант 1. Инициализация.

type ROM is array (0 to

7) of

std_logic_vector(7 downto 0);

constant Content: ROM := (

0 => "00000001", 1 => "00000010",

2 => "00000011",

3 => "00000100",

4 => "00000101",

5 => "00000110",

6 => "00000111",

7 => "00001000",

);

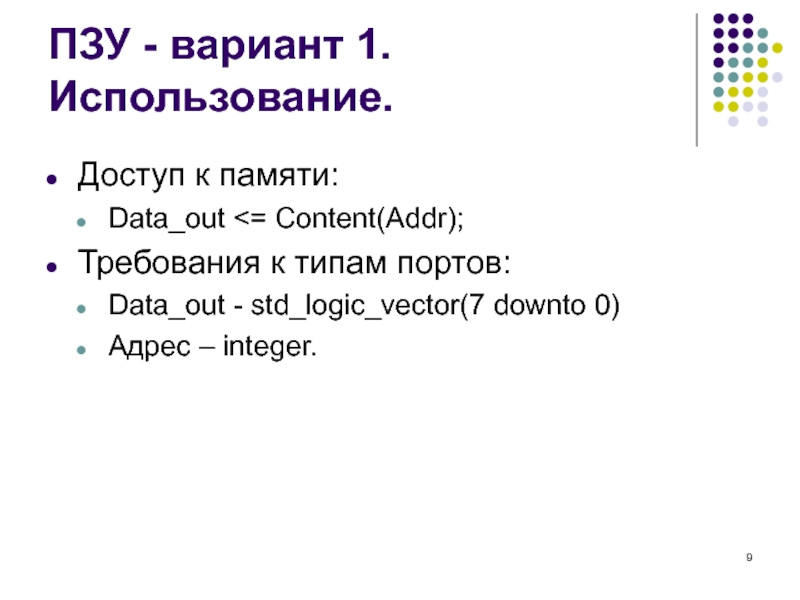

Слайд 9ПЗУ - вариант 1. Использование.

Доступ к памяти:

Data_out

типам портов:

Data_out - std_logic_vector(7 downto 0)

Адрес – integer.

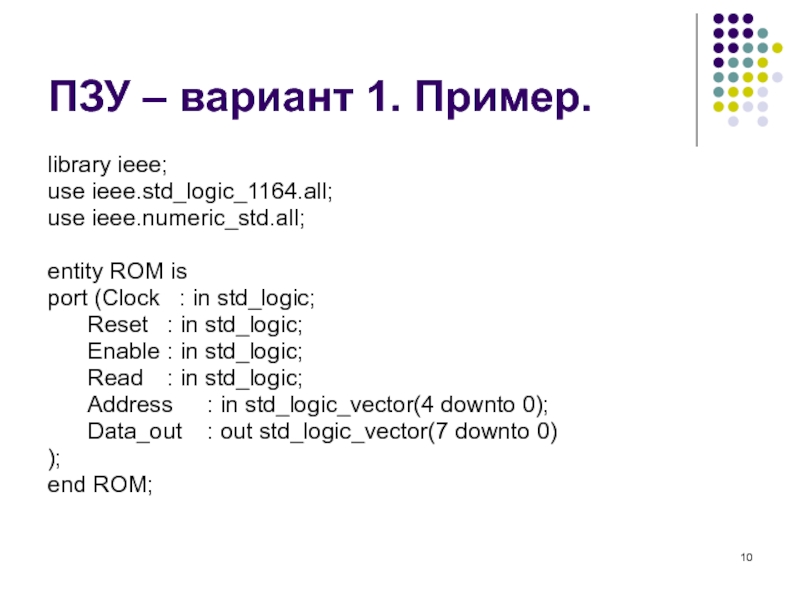

Слайд 10ПЗУ – вариант 1. Пример.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity ROM is

port

(Clock : in std_logic;

Reset : in std_logic;

Enable : in std_logic;

Read : in

std_logic;Address : in std_logic_vector(4 downto 0);

Data_out : out std_logic_vector(7 downto 0)

);

end ROM;

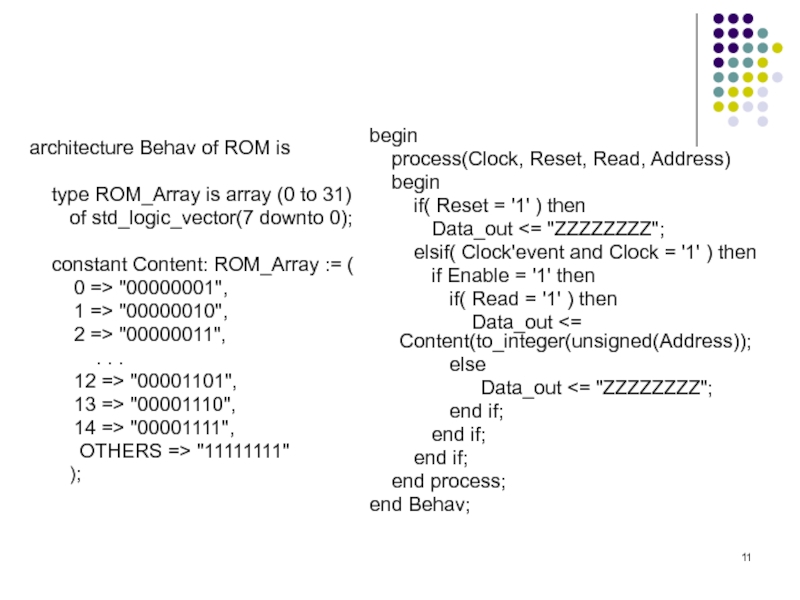

Слайд 11architecture Behav of ROM is

type ROM_Array is array

(0 to 31)

of std_logic_vector(7 downto 0);

constant Content:

ROM_Array := (0 => "00000001",

1 => "00000010",

2 => "00000011",

. . .

12 => "00001101",

13 => "00001110",

14 => "00001111",

OTHERS => "11111111"

);

begin

process(Clock, Reset, Read, Address)

begin

if( Reset = '1' ) then

Data_out <= "ZZZZZZZZ";

elsif( Clock'event and Clock = '1' ) then

if Enable = '1' then

if( Read = '1' ) then

Data_out <= Content(to_integer(unsigned(Address));

else

Data_out <= "ZZZZZZZZ";

end if;

end if;

end if;

end process;

end Behav;

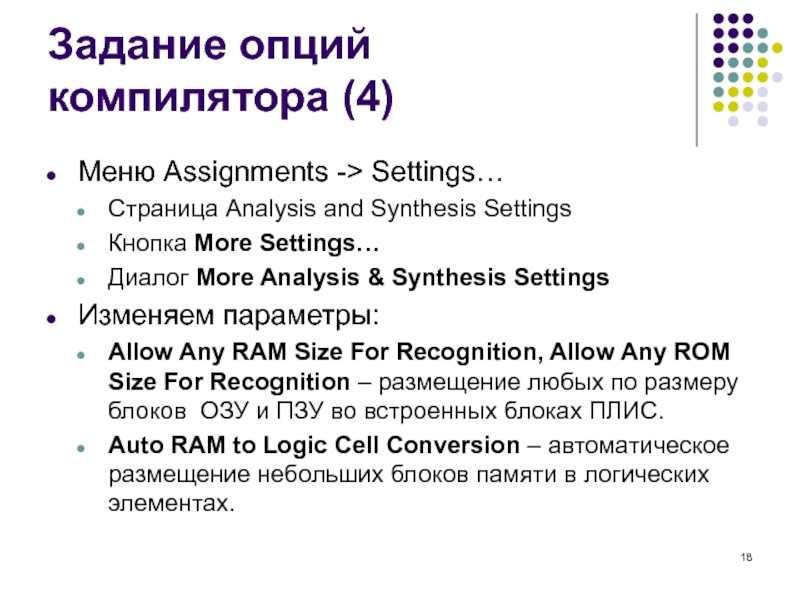

Слайд 18Задание опций

компилятора (4)

Меню Assignments -> Settings…

Страница Analysis and Synthesis

Settings

Кнопка More Settings…

Диалог More Analysis & Synthesis Settings

Изменяем

параметры:Allow Any RAM Size For Recognition, Allow Any ROM Size For Recognition – размещение любых по размеру блоков ОЗУ и ПЗУ во встроенных блоках ПЛИС.

Auto RAM to Logic Cell Conversion – автоматическое размещение небольших блоков памяти в логических элементах.

Слайд 19ПЗУ – вариант 2. Инициализация.

port (

…

data : out std_logic_vector (3 downto

0);

addr : in integer range 0 to 7;)

);

Слайд 20ПЗУ – вариант 2. Использование.

case addr is

when 0 => data

data data

<= “1101”;when 3 => data <= “1100”;

when other => data <= “0000”;

end case;

Слайд 21ПЗУ – вариант 2. Пример.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY mem IS

PORT (

clock:

IN STD_LOGIC;

address: IN STD_LOGIC_VECTOR(7 downto 0);

data_out: OUT STD_LOGIC_VECTOR(5 downto 0)

);

END

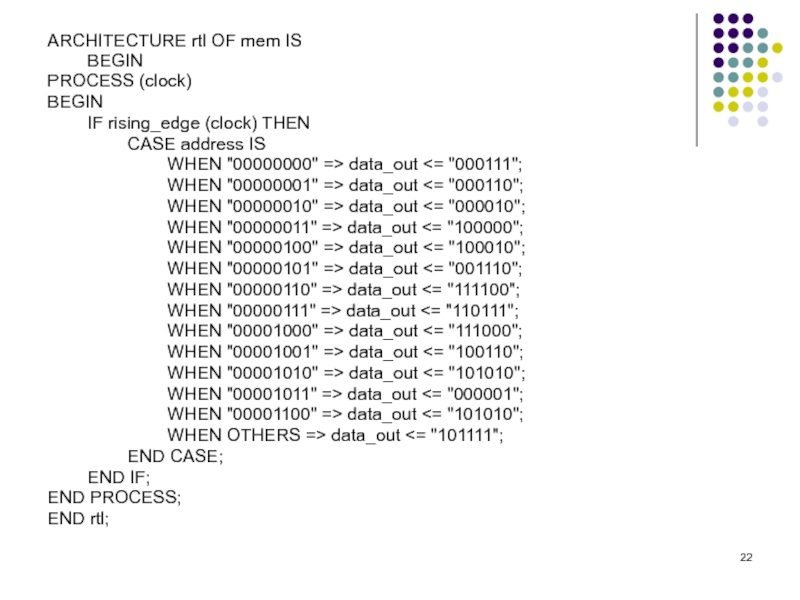

mem;Слайд 22ARCHITECTURE rtl OF mem IS

BEGIN

PROCESS (clock)

BEGIN

IF rising_edge (clock) THEN

CASE address

IS

WHEN "00000000" => data_out data_out

"000110";WHEN "00000010" => data_out <= "000010";

WHEN "00000011" => data_out <= "100000";

WHEN "00000100" => data_out <= "100010";

WHEN "00000101" => data_out <= "001110";

WHEN "00000110" => data_out <= "111100";

WHEN "00000111" => data_out <= "110111";

WHEN "00001000" => data_out <= "111000";

WHEN "00001001" => data_out <= "100110";

WHEN "00001010" => data_out <= "101010";

WHEN "00001011" => data_out <= "000001";

WHEN "00001100" => data_out <= "101010";

WHEN OTHERS => data_out <= "101111";

END CASE;

END IF;

END PROCESS;

END rtl;

Слайд 24ПЗУ – вариант 3. Инициализация (1).

type mem_t is array(255 downto

0) of std_logic_vector(7 downto 0);

signal rom : mem_t;

attribute ram_init_file :

string;attribute ram_init_file of rom : signal is "mem.mif";

Слайд 25ПЗУ – вариант 3. Инициализация (2).

Используем атрибут синтеза под названием

«ram_init_file»

Атрибут задает *.mif файл, который содержит прошивку ПЗУ.

Атрибут находится в

библиотеке «altera_syn_attributes». Папка C:\altera\91\quartus\libraries\vhdl\altera\Слайд 26ПЗУ – вариант 3. Инициализация (3).

Для использования ram_init_file:

Декларировать атрибут синтеза

как строковый тип:

attribute ram_init_file : string;

Создать связь атрибута ram_init_file

с сигналом, который описывает ПЗУ. Значение атрибута должно совпадать с именем *.mif файла:attribute ram_init_file of rom : signal is "mem.mif";

Слайд 27ПЗУ – вариант 3. Инициализация (4).

-- объявили тип массив

type mem_t

is array(255 downto 0) of std_logic_vector(7 downto 0);

-- объявили сигнал

signal

rom : mem_t;-- объявили атрибут

attribute ram_init_file : string;

-- ассоциировали атрибут с сигналом

attribute ram_init_file of rom : signal is "mem.mif";

Слайд 28ПЗУ – вариант 3. Использование.

port (clk : in std_logic;

addr : in natural

range 0 to 255;

q : out std_logic_vector(7 downto 0));

…

process(clk)

begin

if(rising_edge(clk)) then

q

rom(addr);end if;

end process;

Слайд 30ПЗУ – вариант 3. Пример.

library ieee, altera;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use altera.altera_syn_attributes.all;

entity

mem is

port (clk : in std_logic;

addr : in natural range 0 to

255;q : out std_logic_vector(7 downto 0));

end entity;

Слайд 31architecture rtl of mem is

type mem_t is array(255 downto 0)

of std_logic_vector(7 downto 0);

signal rom : mem_t;

attribute ram_init_file : string;

attribute

ram_init_file of rom : signal is "mem.mif";begin

process(clk)

begin

if(rising_edge(clk)) then

q <= rom(addr);

end if;

end process;

end rtl;

Слайд 34Программа

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity mem is

port

(clk : in std_logic;

wn_r: in

std_logic; a : in std_logic_vector(4 downto 0);

di : in std_logic_vector(3 downto 0);

do : out std_logic_vector(3 downto 0));

end mem;

Слайд 35architecture syn of mem is

type ram_type is array

(31 downto 0)

of std_logic_vector (3

downto 0); signal RAM : ram_type;

begin

process (clk)

begin

if (clk'event and clk = '1') then

if (wn_r = '0') then -- запись при «0», чтение по «1»

RAM(to_integer(unsigned(a))) <= di;

else do <= RAM(to_integer(unsigned(a)));

end if;

end if;

end process;

end syn;

Слайд 37Двухпортовая память

ОЗУ

Порт А

Порт Б

Адрес А

Адрес Б

Входные данные А

Выходные данные А

Входные

данные Б

Выходные данные Б

Слайд 38Достоинства двухпортовой памяти

Возможность одновременного чтения и записи данных в один

блок памяти.

Увеличение быстродействия.

Слайд 39Проблемы двухпортовой памяти

Необходимо четко определить поведение во время операции «чтение

во время записи»

Поддерживается не всеми семействами и микросхемами.

Слайд 40library ieee;

use ieee.std_logic_1164.all;

entity mem is

generic ( DATA_WIDTH : natural := 8;

ADDR_WIDTH

: natural := 6);

port (clk : in std_logic;

addr_a : in natural range

0 to 2**ADDR_WIDTH - 1;addr_b : in natural range 0 to 2**ADDR_WIDTH - 1;

data_a : in std_logic_vector((DATA_WIDTH-1) downto 0);

data_b : in std_logic_vector((DATA_WIDTH-1) downto 0);

we_a : in std_logic := '1';

we_b : in std_logic := '1';

q_a : out std_logic_vector((DATA_WIDTH -1) downto 0);

q_b : out std_logic_vector((DATA_WIDTH -1) downto 0));

end mem;

Слайд 41architecture rtl of mem is

subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0);

type

memory_t is array(2**ADDR_WIDTH-1 downto 0) of word_t;

signal ram : memory_t;

begin

--

Port Aprocess(clk)

begin

if(rising_edge(clk)) then

if(we_a = '1') then ram (addr_a) <= data_a;

q_a <= data_a;

end if;

q_a <= ram(addr_a);

end if;

end process;

Слайд 42 -- Port B

process(clk)

begin

if(rising_edge(clk)) then

if(we_b = '1') then

ram(addr_b)

data_b;

q_b

process;end rtl;

data_out data_out data_out data_out">

data_out data_out data_out data_out">