Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

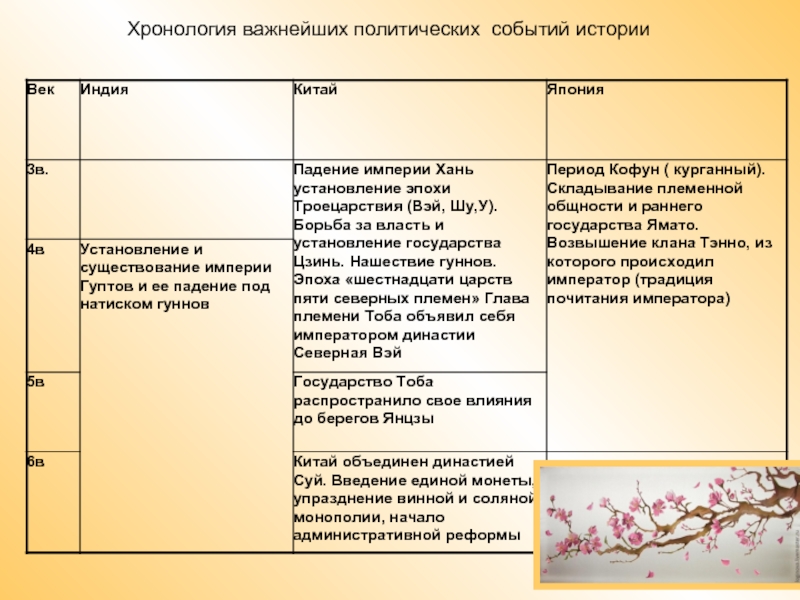

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Организация памяти ЭВМ

Содержание

- 1. Организация памяти ЭВМ

- 2. Список литературыВ.Ф. Мелехин. Вычислительные машины системы и сети. Лекция 7. Кэш процессора. http://iproc.ru/parallel-programming/lection-7/

- 3. Иерархия запоминающих устройствПамять наряду с процессором в

- 4. Иерархия запоминающих устройствСовокупность устройств, обеспечивающих запись, хранение и чтение информации в ВМ, образуют систему памяти.

- 5. Иерархия запоминающих устройств

- 6. Иерархия запоминающих устройствГОУ ОГУ 2008Закономерности: • чем

- 7. Иерархия запоминающих устройствГОУ ОГУ 2008По мере движения

- 8. Структура микросхемы памятиГОУ ОГУ 2008

- 9. Запоминающие элементыГОУ ОГУ 2008Запоминающий элемент динамического ОЗУЗапоминающий элемент статического ОЗУ

- 10. Кэш-памятьКэш-память представляет собой быстродействующее ЗУ, размещенное на

- 11. Кэш-памятьОдной из проблем взаимодействия является согласование скоростных

- 12. Кэш-памятьКэш состоит из собственно кэш-памяти, и кэш-контроллера . Кэш-контроллер управляет

- 13. Кэш-память

- 14. В структуре кэш-памяти выделяют два типа блоков

- 15. Полностью ассоциативный кэш 8х8 для 10-битного адреса

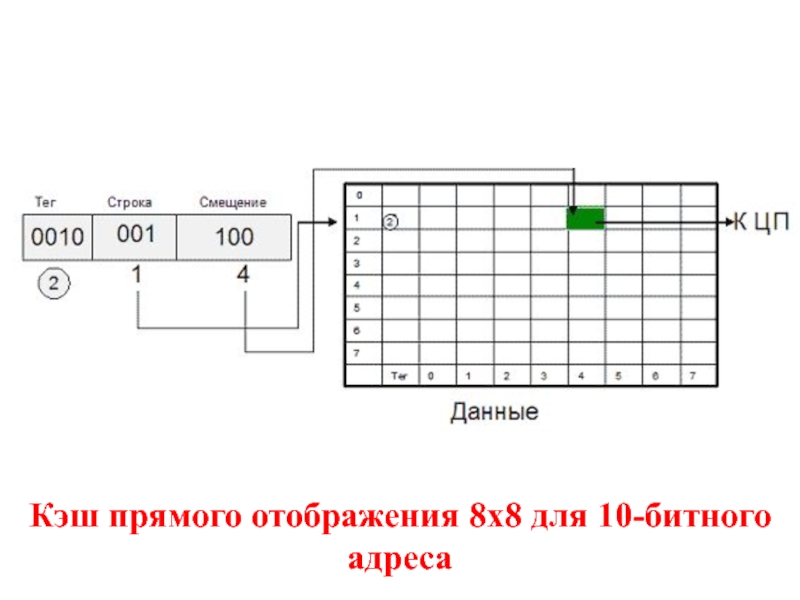

- 16. Кэш прямого отображения 8х8 для 10-битного адреса

- 17. Двухвходовый ассоциативный кэш 8х8 для 10-битного адреса

- 18. Для согласования содержимого кэш-памяти и оперативной памяти

- 19. Tср = (Thit x Rhit) + (Tmiss

- 20. Скачать презентанцию

Список литературыВ.Ф. Мелехин. Вычислительные машины системы и сети. Лекция 7. Кэш процессора. http://iproc.ru/parallel-programming/lection-7/

Слайды и текст этой презентации

Слайд 1Организация памяти ЭВМ

Аппаратные средства вычислительной техники

ОГУ, кафедра ВТиЗИ

Галимов Р.Р.

2015

Слайд 2Список литературы

В.Ф. Мелехин. Вычислительные машины системы и сети.

Лекция 7.

Кэш процессора. http://iproc.ru/parallel-programming/lection-7/

Слайд 3Иерархия запоминающих устройств

Память наряду с процессором в значительной мере определяет

основные возможности ВМ — ее производительность и сложность решаемых задач,

характеризуемую объемом программ и данных.Основными системными требованиями, предъявляемыми к памяти являются:

- большой информационный объем;

малое время доступа к данным;

низкая стоимость;

энергонезависимость.

В настоящее время не существуют физические устройства памяти, полностью удовлетворяющие перечисленным системным требованиями, в связи с чем память ВМ реализуется не в виде отдельного устройства, а в виде иерархической многоуровневой системы, представляющей собой совокупность взаимодействующих устройств памяти.

Слайд 4Иерархия запоминающих устройств

Совокупность устройств, обеспечивающих запись, хранение и чтение информации

в ВМ, образуют систему памяти.

Слайд 6Иерархия запоминающих устройств

ГОУ ОГУ 2008

Закономерности:

• чем меньше время доступа,

тем выше стоимость хранения бита;

• чем больше емкость, тем

ниже стоимость хранения бита, но больше время доступа. При создании системы памяти постоянно приходится решать задачу обеспечения требуемой емкости и высокого быстродействия за приемлемую цену.

Уровни иерархии взаимосвязаны: все данные на одном уровне могут быть также найдены на более низком уровне, и все данные на этом более низком уровне могут быть найдены на следующем нижележащем уровне и т. д.

Слайд 7Иерархия запоминающих устройств

ГОУ ОГУ 2008

По мере движения вниз по иерархической

структуре:

1. Уменьшается соотношение «стоимость/бит».

2. Возрастает емкость.

3. Растет

время доступа. 4. Уменьшается частота обращения к памяти со стороны центрального процессора

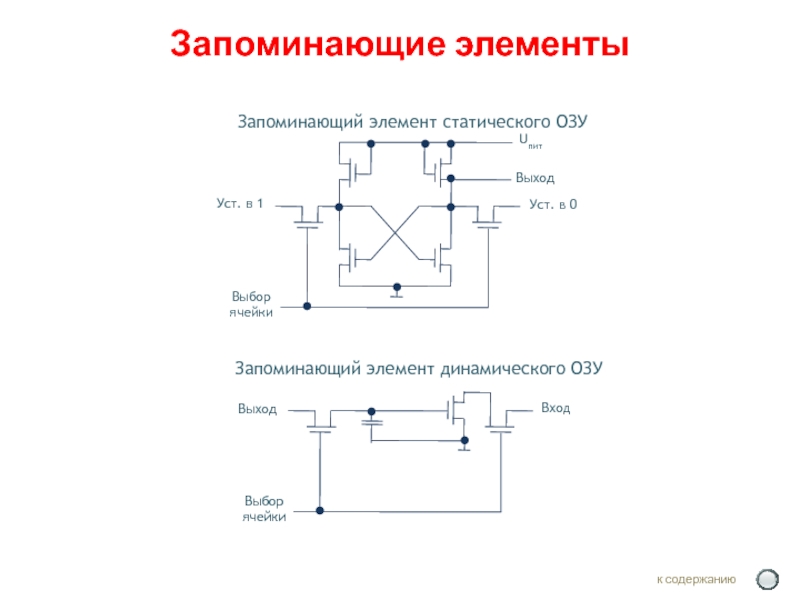

Слайд 9Запоминающие элементы

ГОУ ОГУ 2008

Запоминающий элемент динамического ОЗУ

Запоминающий элемент статического ОЗУ

Слайд 10Кэш-память

Кэш-память представляет собой быстродействующее ЗУ, размещенное на одном кристалле с

ЦП или внешнее по отношению к ЦП.

Кэш служит высокоскоростным

буфером между ЦП и относительно медленной основной памятью. Идея кэш-памяти основана на прогнозировании наиболее вероятных обращений ЦП к оперативной памяти.

В основу такого подхода положен принцип временной и пространственной локальности программы.

Слайд 11Кэш-память

Одной из проблем взаимодействия является согласование скоростных характеристик процессора и

ОП. При современном уровне развития микроэлектроники процессор имеет значительно более

высокое быстродействие по сравнению с быстродействием ОП.Основным архитектурным способом согласования скоростных характеристик процессора и ОП является кэширование ОП. Под кэшированием понимается использование быстродействующей буферной памяти относительно малого размера, выполненной на элементах памяти статического типа (триггерах), которые имеют более высокое быстродействие по сравнению с динамическими элементами ОП.

В эту буферную память из ОП помещаются копии команд и данных, относящихся к обрабатываемому в данный момент фрагменту программы.

Работа буферной памяти прозрачна для программ, т. е. скрыта от пользователя. По этой причине ее называют кэш-памятью (cache — тайник).

Слайд 12Кэш-память

Кэш состоит из собственно кэш-памяти, и кэш-контроллера . Кэш-контроллер управляет кэш-памятью: загружает в

неё нужные данные из оперативной памяти, и возвращает, когда нужно,

модифицированные процессором данные в оперативную память.Слайд 14В структуре кэш-памяти выделяют два типа блоков данных:

- память отображения

данных (собственно сами данные, дублированные из оперативной памяти);

память тегов (признаки,

указывающие на расположение кэшированных данных в оперативной памяти).По алгоритмам отображения оперативной памяти в кэш выделяют три типа кэш-памяти:

- полностью ассоциативный кэш;

- кэш прямого отображения;

- множественный ассоциативный кэш.

Кэш-память

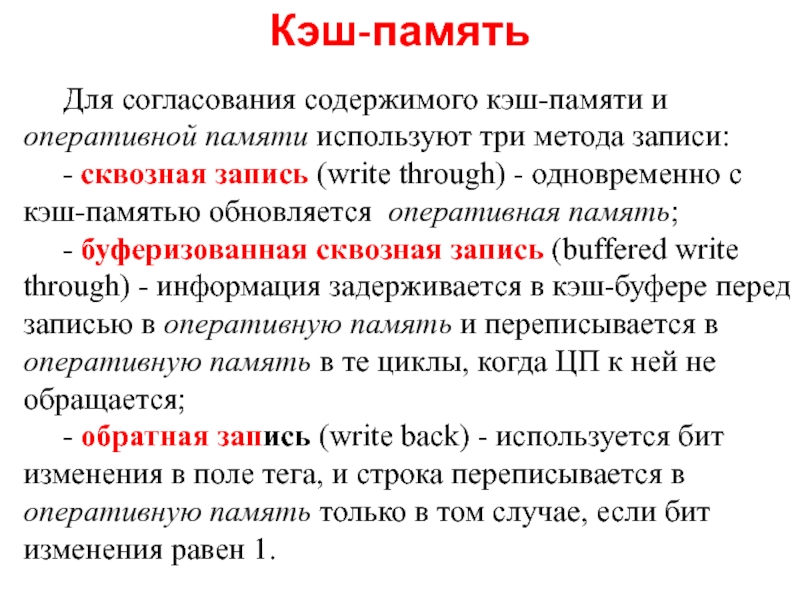

Слайд 18Для согласования содержимого кэш-памяти и оперативной памяти используют три метода

записи:

- cквозная запись (write through) - одновременно с кэш-памятью обновляется

оперативная память;- буферизованная сквозная запись (buffered write through) - информация задерживается в кэш-буфере перед записью в оперативную память и переписывается в оперативную память в те циклы, когда ЦП к ней не обращается;

- обратная запись (write back) - используется бит изменения в поле тега, и строка переписывается в оперативную память только в том случае, если бит изменения равен 1.

Кэш-память

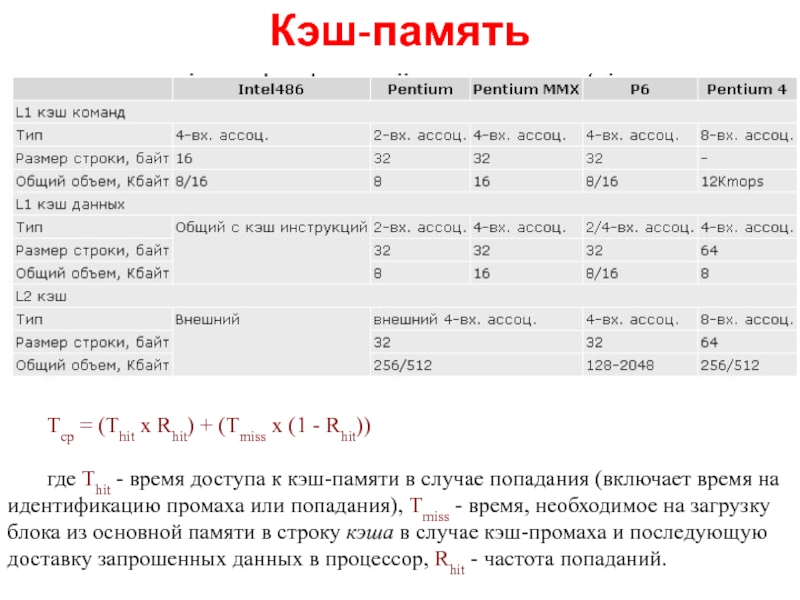

Слайд 19Tср = (Thit x Rhit) + (Tmiss x (1 -

Rhit))

где Thit - время доступа к кэш-памяти в случае

попадания (включает время на идентификацию промаха или попадания), Tmiss - время, необходимое на загрузку блока из основной памяти в строку кэша в случае кэш-промаха и последующую доставку запрошенных данных в процессор, Rhit - частота попаданий.Кэш-память