Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Процессор и память 1

Содержание

- 1. Процессор и память 1

- 2. Основные понятия микропроцессорной техникиОсновой современных систем управления

- 3. Основные понятия микропроцессорной техникиТакие устройства стало возможным

- 4. Основные понятия микропроцессорной техникиВведем основные понятия микропроцессорной

- 5. Основные понятия микропроцессорной техники МЭВМ (микро-ЭВМ) – конструктивно

- 6. Основные понятия микропроцессорной техники МПК ИС (микропроцессорный комплект

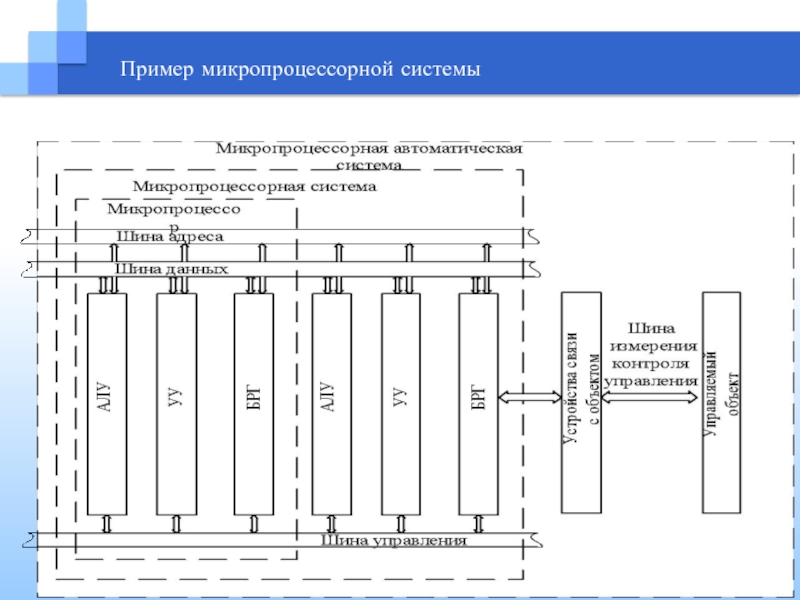

- 7. Пример микропроцессорной системы

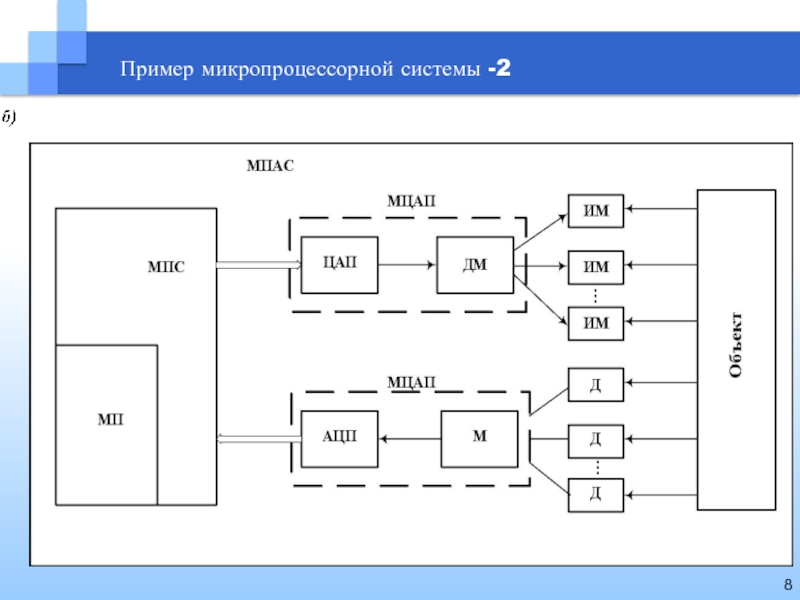

- 8. Пример микропроцессорной системы -2

- 9. Элементы и узлы ЭВМВсе устройства ЭВМ состоят

- 10. Элементы и узлы ЭВМПримерами логических переменных являются

- 11. Элементы и узлы ЭВМВысказывания могут быть простыми

- 12. Элементы и узлы ЭВМДве логические переменные А

- 13. Элементы и узлы ЭВМЛогическое отрицание НЕ переменной

- 14. Элементы и узлы ЭВМ

- 15. Элементы и узлы ЭВМЛогическое умножение И двух

- 16. Элементы и узлы ЭВМ

- 17. Элементы и узлы ЭВМЛогическая сумма ИЛИ переменных

- 18. Элементы и узлы ЭВМЭлементами ЭВМ называют устройства,

- 19. Элементы и узлы ЭВМЛогический элемент — изделие

- 20. Элементы и узлы ЭВМУзлы ЭВМ состоят из простых элементов.Основные функциональные узлы ЭВМ: Триггеры;Регистры;Счетчики;Сумматоры;Мультиплексоры;Селекторы;Шифраторы;Дешифраторы.

- 21. Элементы и узлы ЭВМВ качестве устройства, запоминающего

- 22. Элементы и узлы ЭВМНазвание триггеров определяется первыми

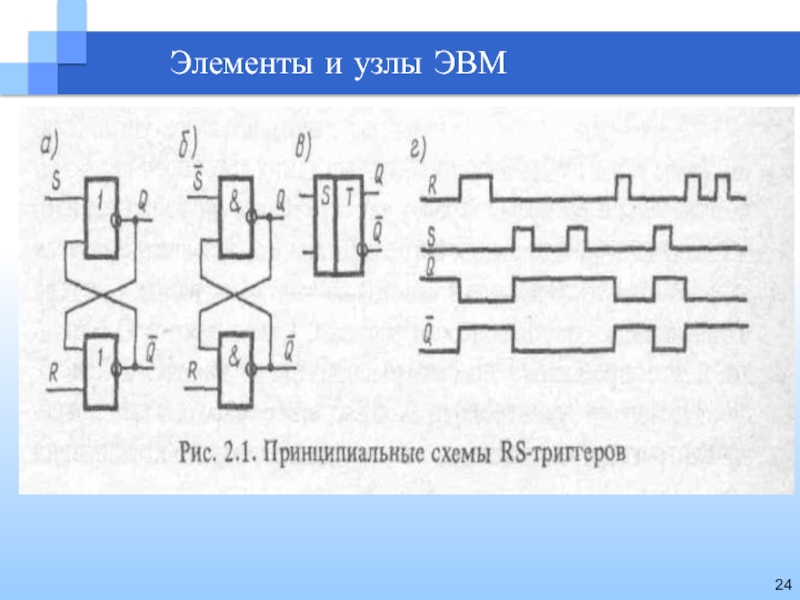

- 23. Элементы и узлы ЭВМRS-триггеры с раздельной установкой

- 24. Элементы и узлы ЭВМ

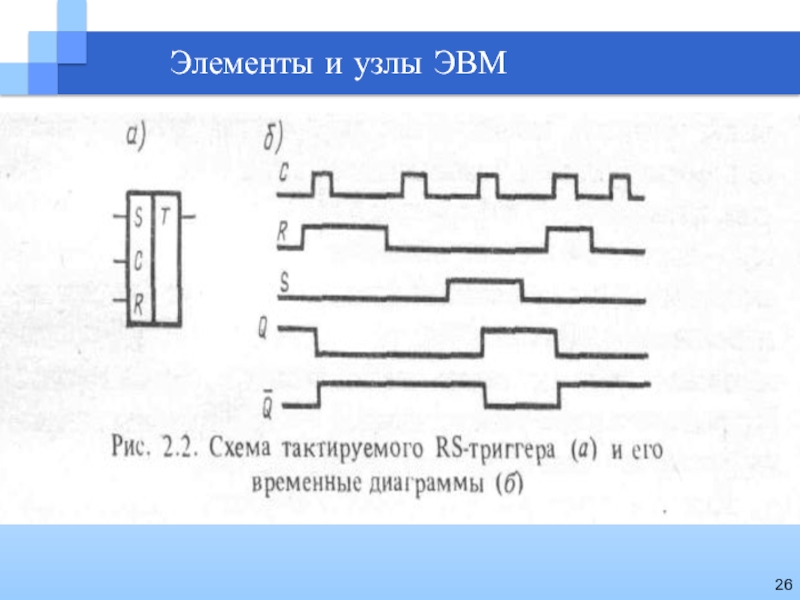

- 25. Элементы и узлы ЭВМСинхронный (тактируемый) RS-триггер имеет

- 26. Элементы и узлы ЭВМ

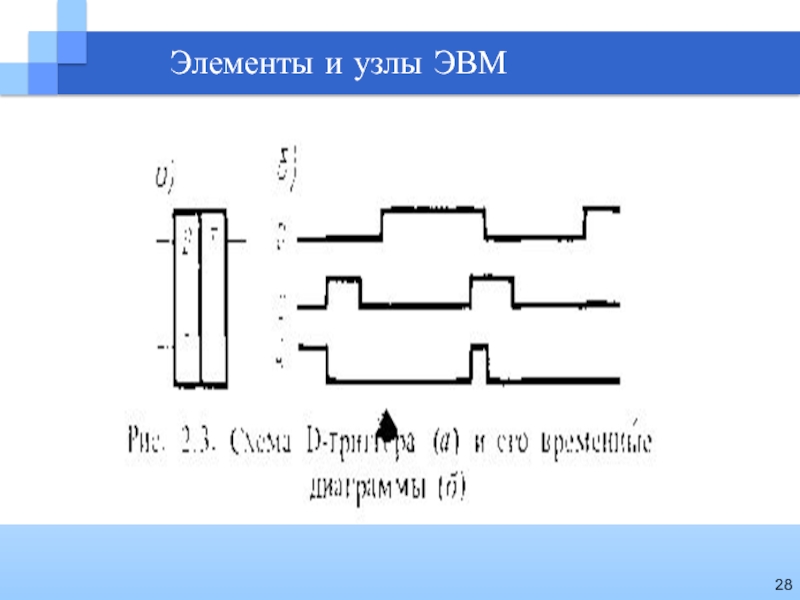

- 27. Элементы и узлы ЭВМ D-триггер задержки. D-триггер

- 28. Элементы и узлы ЭВМ

- 29. Элементы и узлы ЭВМ Широко применяют D-триггеры

- 30. Элементы и узлы ЭВМ

- 31. Элементы и узлы ЭВМ JK-триггер универсальный.

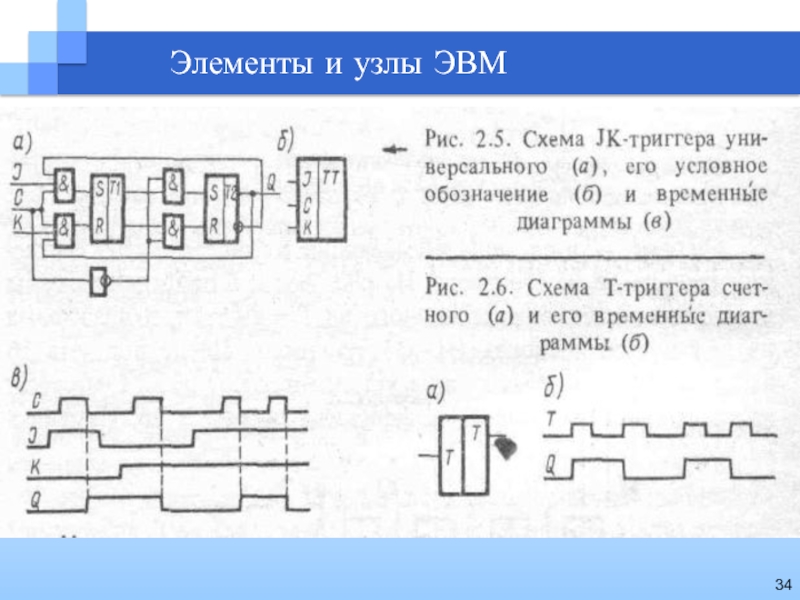

- 32. Элементы и узлы ЭВМ Реализуется JK-триггер

- 33. Элементы и узлы ЭВМ Т-триггер счетный.

- 34. Элементы и узлы ЭВМ

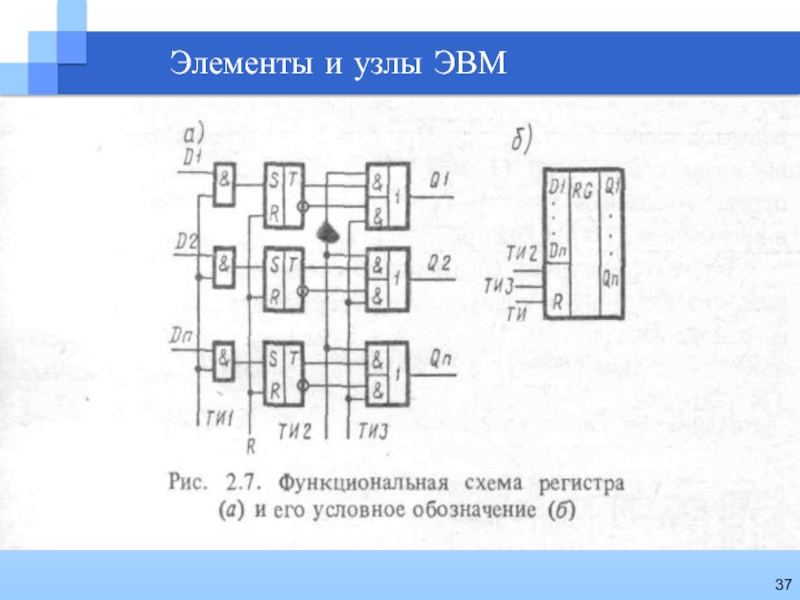

- 35. Элементы и узлы ЭВМ Регистр —

- 36. Элементы и узлы ЭВМ Перед записью

- 37. Элементы и узлы ЭВМ

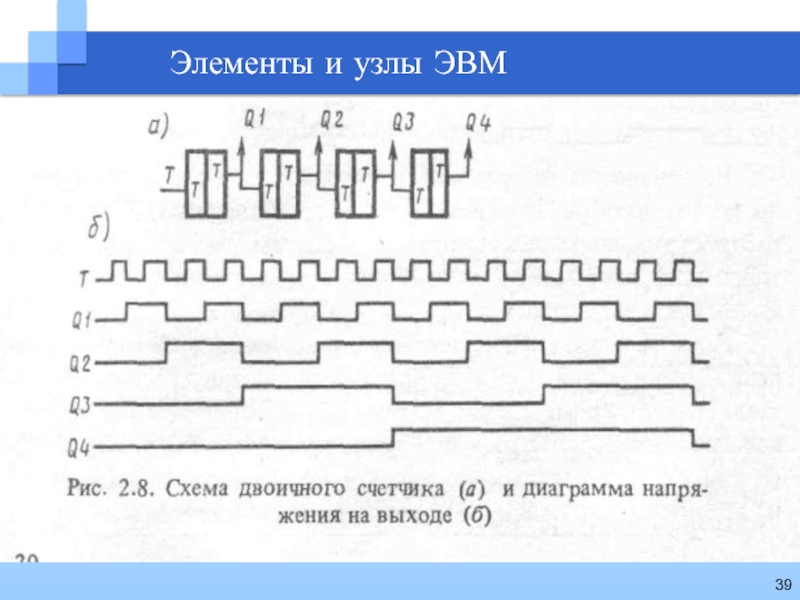

- 38. Элементы и узлы ЭВМ Счетчик -

- 39. Элементы и узлы ЭВМ

- 40. Элементы и узлы ЭВМ Изменить коэффициент

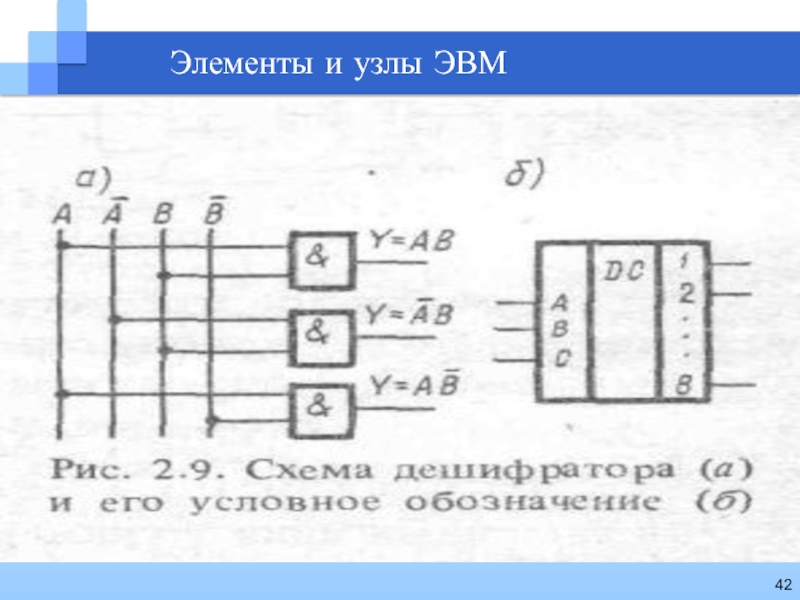

- 41. Элементы и узлы ЭВМ Дешифратор -

- 42. Элементы и узлы ЭВМ

- 43. Элементы и узлы ЭВМ Шифратор -

- 44. Элементы и узлы ЭВМ Мультиплексор -

- 45. Элементы и узлы ЭВМ Селектор (переключатель)

- 46. Элементы и узлы ЭВМ

- 47. Элементы и узлы ЭВМ Сумматор -

- 48. Элементы и узлы ЭВМ Сумматор и

- 49. Элементы и узлы ЭВМ Рассмотрим работу

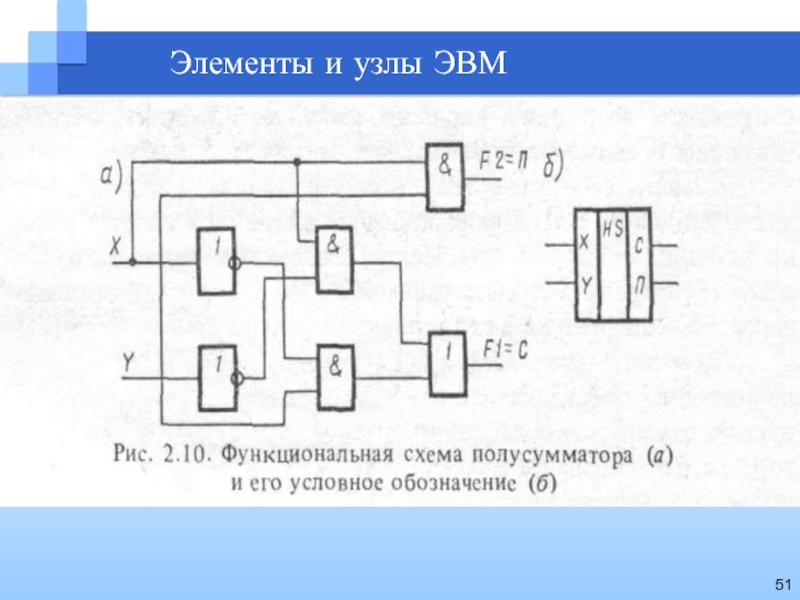

- 50. Элементы и узлы ЭВМОдноразрядный двоичный сумматор может

- 51. Элементы и узлы ЭВМ

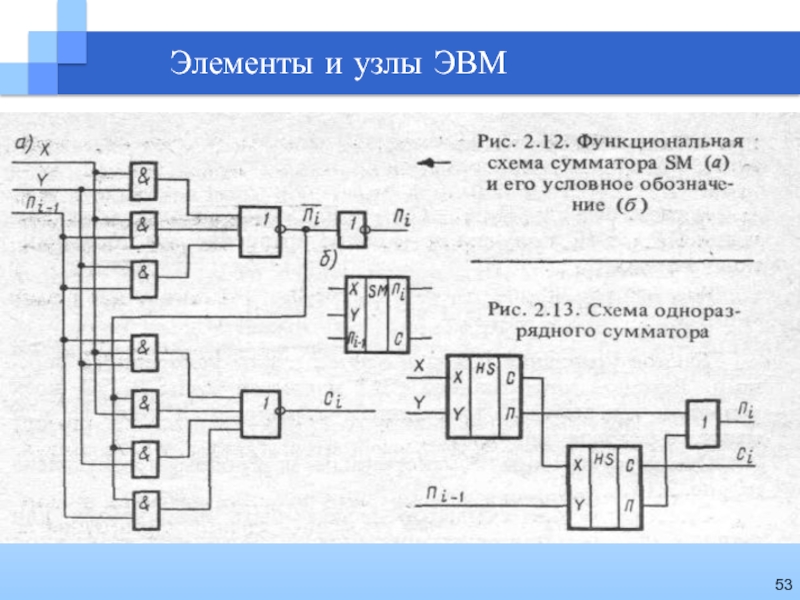

- 52. Элементы и узлы ЭВМФункциональная схема одного из

- 53. Элементы и узлы ЭВМ

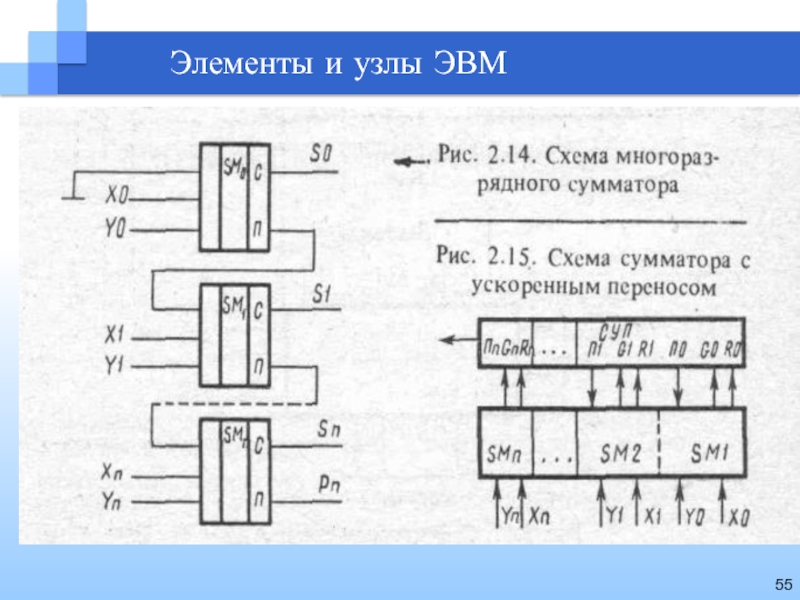

- 54. Элементы и узлы ЭВММногоразрядный сумматор можно получить

- 55. Элементы и узлы ЭВМ

- 56. Элементы и узлы ЭВМВ современных ЭВМ элементы

- 57. Центральным процессором (ЦП) называется такое функциональное устройство

- 58. Операции, выполняемые за один командный цикл

- 59. Организация работы центрального процессораВызвать команду . Для

- 60. Выполнить команду. Содержимое регистра команд анализируется процессором,

- 61. Осуществить проверку запросов прерывания. Во многих случаях

- 62. Устройства ЭВМ, осуществляющие прерывание процессора называются системами

- 63. Способность прерывания является решающим инструментом обработки информации

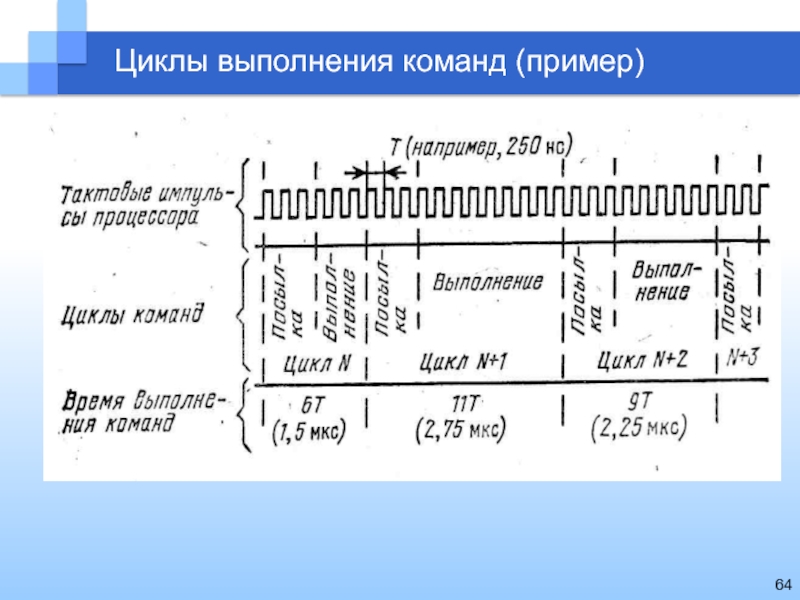

- 64. Циклы выполнения команд (пример)

- 65. Циклы выполнения команд в конвейере (пример)

- 66. Циклы выполнения команд в конвейере (пример)За

- 67. Спасибо за внимание!

- 68. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2

Основные понятия микропроцессорной техники

Основой современных систем управления является микропроцессорная техника,

Слайд 3

Основные понятия микропроцессорной техники

Такие устройства стало возможным встраивать в различные

машины и механизмы и реализовать на основе их системы с

большими вычислительными возможностями в бортовом исполнении для различных транспортных средств, в том, числе для летательных и космических аппаратовСлайд 4

Основные понятия микропроцессорной техники

Введем основные понятия микропроцессорной техники:

МП (микропроцессор) -

программно-управляемое устройство цифровой обработки информации на одной или нескольких БИС;

МПС

(микропроцессорная система) - совокупность одного или нескольких МП, ЗУ, УВВ и др. устройств для выполнения функций цифрового управления (регулирования); Слайд 5

Основные понятия микропроцессорной техники

МЭВМ (микро-ЭВМ) – конструктивно законченная МПС, имеющая

панель управления, собственное ПО и УВВ;

МК (микроконтроллер) - микропроцессорное

управляющее устройство с развитыми функциями логического анализа;Слайд 6

Основные понятия микропроцессорной техники

МПК ИС (микропроцессорный комплект ИМС) - совокупность

микропроцессорных БИС (базовый МПК) и других совместимых с ними ИС

- т.е. элементная база МПС, МЭВМ и МПАС;МПАС (микропроцессорная автоматическая система) - автоматическая система со встроенными микропроцессорными средствами.

Слайд 9

Элементы и узлы ЭВМ

Все устройства ЭВМ состоят из элементарных логических

схем. Работа этих схем основана на законах и правилах алгебры

логики, которая оперирует двумя понятиями: истинности и ложности высказывания. В соответствии с такой двоичной природой высказываний условились называть их логическими двоичными переменными и обозначать 1 в случае истинности и 0 в случае ложности.Слайд 10

Элементы и узлы ЭВМ

Примерами логических переменных являются высказывания: А =

"Земля плоская", В = "Автомобиль имеет двигатель".

На основании этих

высказываний можно записать А = 0; В •- 1, так как высказывание А ложно, а высказывание В истинно. Слайд 11

Элементы и узлы ЭВМ

Высказывания могут быть простыми и сложными: простые

содержат одно законченное утверждение, сложные образуются из двух или большего

числа простых высказываний, связанных между собой некоторыми логическими связями. Формализация и преобразование связей между логическими переменными осуществляется в соответствии с правилами алгебры логики, называемой алгеброй Буля (в честь ее автора — английского математика Джорджа Буля).Слайд 12

Элементы и узлы ЭВМ

Две логические переменные А к В, принимающие

значения О или 1, могут образовывать логические функции. Из 16

возможных функций двух переменных наибольший практический интерес представляют функции отрицания, логического умножения и логического сложения.Слайд 13

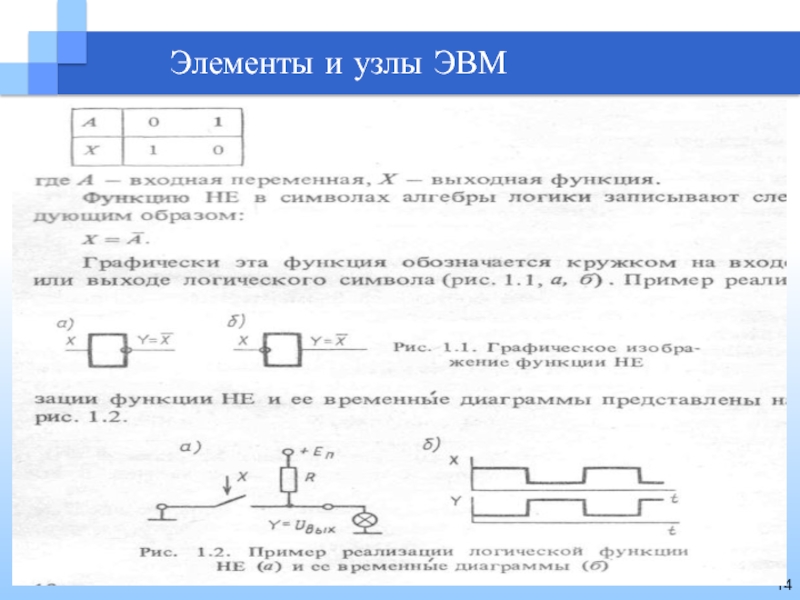

Элементы и узлы ЭВМ

Логическое отрицание НЕ переменной А есть логическая

функция X, которая истинна только тогда, когда ложно А, и

наоборот.В алгебре логики любые функции удобно изображать в виде таблицы соответствия всех возможных комбинаций входных логических переменных и выходной логической функции, называемой таблицей истинности. Для функции логического отрицания НЕ эта таблица имеет вид, показанный ниже:

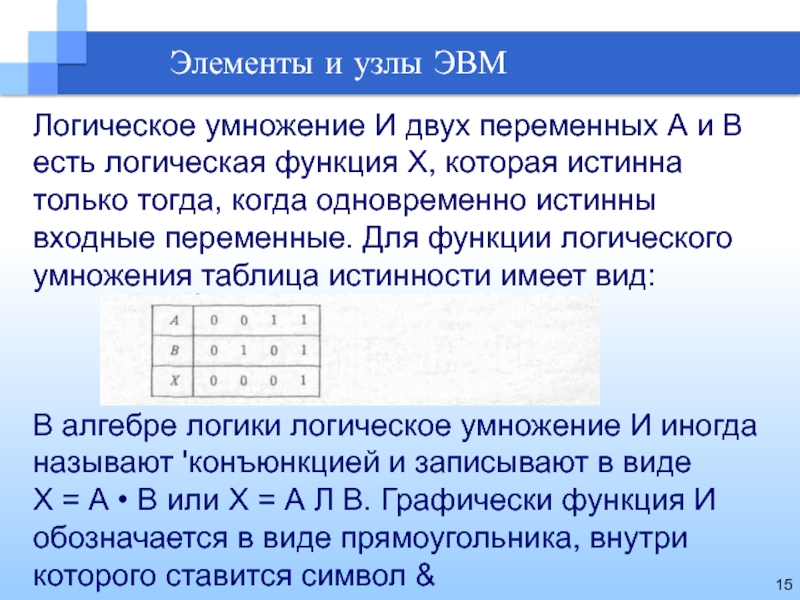

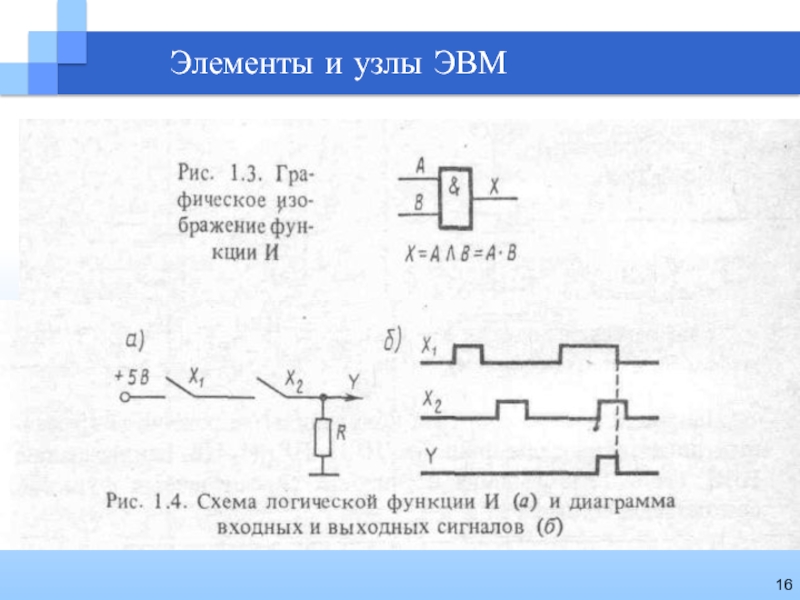

Слайд 15

Элементы и узлы ЭВМ

Логическое умножение И двух переменных А и

В есть логическая функция X, которая истинна только тогда, когда

одновременно истинны входные переменные. Для функции логического умножения таблица истинности имеет вид:В алгебре логики логическое умножение И иногда называют 'конъюнкцией и записывают в виде X = А • В или X = А Л В. Графически функция И обозначается в виде прямоугольника, внутри которого ставится символ &

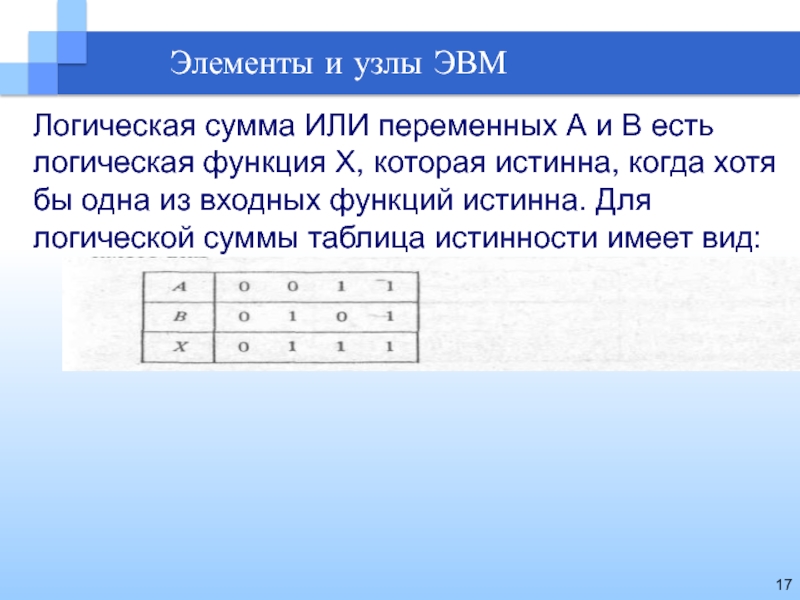

Слайд 17

Элементы и узлы ЭВМ

Логическая сумма ИЛИ переменных А и В

есть логическая функция X, которая истинна, когда хотя бы одна

из входных функций истинна. Для логической суммы таблица истинности имеет вид:Слайд 18

Элементы и узлы ЭВМ

Элементами ЭВМ называют устройства, выполняющие логические функции,

запоминающие информацию, преобразующие ее и формирующие и усиливающие сигналы.

По

функциональному назначению элементы ЭВМ подразделяются на:логические (ЛЭ);

запоминающие (ЗЭ);

вспомогательные.

Слайд 19

Элементы и узлы ЭВМ

Логический элемент — изделие или его часть,

реализующие функцию или систему функций алгебры логики.

Запоминающие элементы, предназначены для

хранения двоичной информации. В качестве ЗЭ широко используются триггеры, реализованные на ЛЭ.К вспомогательным элементам можно отнести усилители, формирователи и генераторы импульсных сигналов, элементы индикации и преобразователи логических уровней, специальные элементы ЗУ.

Слайд 20

Элементы и узлы ЭВМ

Узлы ЭВМ состоят из простых элементов.

Основные функциональные

узлы ЭВМ:

Триггеры;

Регистры;

Счетчики;

Сумматоры;

Мультиплексоры;

Селекторы;

Шифраторы;

Дешифраторы.

Слайд 21

Элементы и узлы ЭВМ

В качестве устройства, запоминающего информацию в элементах,

используют триггер - логический элемент, обладающий двумя устойчивыми состояниями.

Для

переключения триггера применяют входные логические схемы. По способу переключения и по закону функционирования триггеры можно разделить на следующие группы: RS-триггеры с раздельной установкой 0 и 1;

D-триггеры задержки;

универсальные JK-триггеры;

Т-триггеры счетные.

Слайд 22

Элементы и узлы ЭВМ

Название триггеров определяется первыми буквами английских слов:

S (set - установить);

R (reset - выключить);

Т (toggle

- релаксатор); J (jerk - резко включить);

К (kill -резко выключить);

D (delay - задержка).

Выходной сигнал триггера принято обозначать буквой Q.

Слайд 23

Элементы и узлы ЭВМ

RS-триггеры с раздельной установкой 0 и 1.

Простейший RS-триггер имеет два входа: R и S. При комбинации

входных сигналов S = 1, R = 0 триггер устанавливается в единичное состояние Q = 1, при входных сигналах S = 0, R = 1 - в состояние Q = 0, при R = О, S = 0 триггер сохраняет свое состояние. Если на входы R и S подать 1, то его выходной сигнал не определен, так как триггер при этом находится в неустойчивом состоянии. Слайд 25

Элементы и узлы ЭВМ

Синхронный (тактируемый) RS-триггер имеет управляющий сигнал С

на входе (clock - основная синхронизация), который при С =

1 разрешает переключение по закону RS-триггера, при С = 0 триггер сохраняет свое состояние.Схема и временные диаграммы тактируемого синхронного RS-триггера приведены на рис. ниже:

Слайд 27

Элементы и узлы ЭВМ

D-триггер задержки.

D-триггер имеет один

информационный вход и вход для синхронизирующего импульса С. Основное назначение

D-триггера — задержка и хранение сигнала, поданного на вход при С = 1.Разновидностью D-триггера является DV-триггер, в котором по управляющему входу V (valve - вентиль) разрешается переключение при V = 1 или триггер не реагирует на изменение входных сигналов при V = 0. На рис. Ниже приведены схема D-триггера и временные диаграммы, поясняющие его работу.

Слайд 29

Элементы и узлы ЭВМ

Широко применяют D-триггеры с динамическим

управлением. Выходной сигнал таких триггеров переключается только во время фронта

тактирующего сигнала С на входе. Направление изменения сигнала С, при котором записывается информация, определяется наклоном черты на входе триггера с динамическим управлением записью.Слайд 31

Элементы и узлы ЭВМ

JK-триггер универсальный.

JK-триггер работает

по правилу RS-триггера и отличается от последнего тем, что комбинация сигналов

J = К = 1 не является запретной. При этих сигналах JK-триггер изменяет свое состояние на обратное тому, в котором он находился.Слайд 32

Элементы и узлы ЭВМ

Реализуется JK-триггер обычно по

двухступенчатой схеме (см. рис. ниже).

При С = 1 входная

информация записывается в триггер Т1, при С = 0 информация с триггера Т1 переписывается в триггер Т2.

Слайд 33

Элементы и узлы ЭВМ

Т-триггер счетный.

Он изменяет

свое состояние с приходом каждого входного импульса. Т-триггер может быть

реализован на основе JK-триггера. При J = К = 1 сигналы С и Т на входе становятся эквивалентны, а JK-триггер работает как счетныйСлайд 35

Элементы и узлы ЭВМ

Регистр — узел ЭВМ,

предназначенный для временного хранения информации и ее преобразования. Основу регистров

составляют триггерные схемы.Количество триггеров в регистре определяет разрядность записываемых и хранимых слов. Каждый триггер используется для записи одного разряда слова.

Слайд 36

Элементы и узлы ЭВМ

Перед записью информации все

триггеры управляющим сигналом R устанавливаются в состояние Q = 0.

По тактирующему импульсу ТИ1 информация записывается в триггеры.Для формирования прямого кода Q на вход регистра подается тактирующий импульс Т2, для обратного кода Q - импульс ТЗ.

Слайд 38

Элементы и узлы ЭВМ

Счетчик - узел, подсчитывающий

количество электрических импульсов на его входе.

На рис. ниже для

примера приведены схемы двоичного счетчика, построенного на Т-триггерах, и диаграмма напряжений на выходах Ql—Q4 триггеров. После подсчета 16 импульсов на выходе счетчика установится код 0000. Считается, что такой счетчик имеет коэффициент пересчета 16.Слайд 40

Элементы и узлы ЭВМ

Изменить коэффициент пересчета можно

изменив число триггеров или введя обратные связи между ними. Двоично-десятичные

счетчики, например, устанавливаются в исходное нулевое состояние после подсчета десяти импульсов. Логическими связями между триггерами можно обеспечить вычитание 1 из первоначального кода с приходом очередного входного импульса. Счетчики, обеспечивающие и сложение, и вычитание, называются реверсивными.Слайд 41

Элементы и узлы ЭВМ

Дешифратор - узел ЭВМ,

обеспечивающий формирование для n-входовой схемы формирования активного сигнала только на

одном из его выходов. Максимальное количество выходов в дешифраторе может быть равным 2n. На рис. Ниже приведены схема дешифратора и его условное обозначение.Слайд 43

Элементы и узлы ЭВМ

Шифратор - узел ЭВМ,

выполняющий операцию, обратную по отношению к дешифратору, т.е. формирование соответствующего

двоичного кода при появлении сигнала на одном из входов шифратора.Слайд 44

Элементы и узлы ЭВМ

Мультиплексор - узел ЭВМ,

обеспечивающий коммутацию одного из нескольких входных сигналов на один выходной.

Выбор входного сигнала осуществляется в соответствии с кодом, поступающим на адресный управляющий вход.Слайд 45

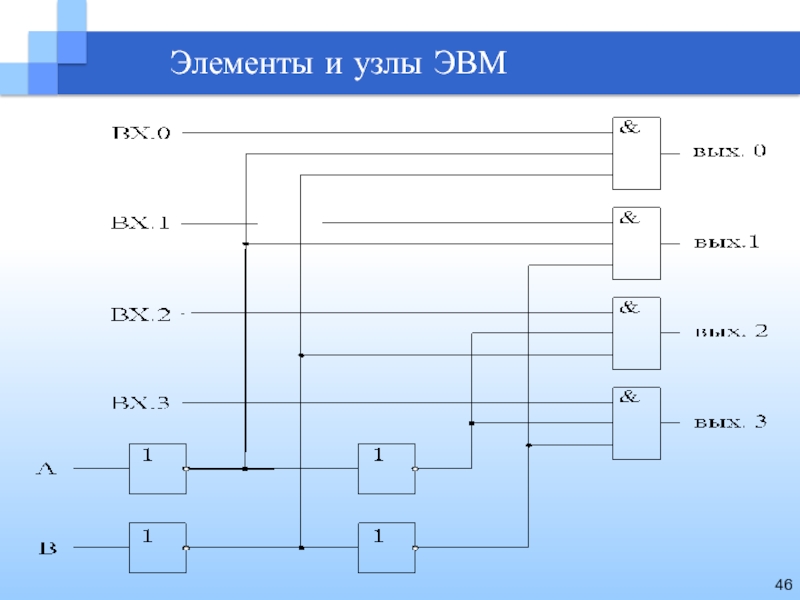

Элементы и узлы ЭВМ

Селектор (переключатель) - устройство,

обеспечивающее отключение отдельных блоков ЭВМ и связь их с другими

блоками. В зависимости от кодовой комбинации на управляющих входах селектора тот или иной вход схемы подключается к выходу.На рис. ниже приведен пример функциональной схемы 2-разрядного селектора.

Слайд 47

Элементы и узлы ЭВМ

Сумматор - устройство, выполняющее

операцию суммирования двух двоичных чисел. Сложение содержимого одноименного разряда двух

чисел (например, i-ого) в сумматоре происходит с учетом прибавления единицы переноса (если она возникает) из соседнего младшего переноса (i=1)-го разряда. В результате формируется значение суммы в i-м разряде и может возникнуть перенос в соседний старший (i+1) разряд.Слайд 48

Элементы и узлы ЭВМ

Сумматор и арифметическо-логическое устройство

преобразуют исходные данные в соответствии с введенной в ЭВМ программой.

Элементарными действиями преобразования чисел являются арифметические и логические операции, операции сдвига и т.д.Слайд 49

Элементы и узлы ЭВМ

Рассмотрим работу устройства, обеспечивающего

сложение двух чисел. Сложение многоразрядных чисел выполняется многоразрядным сумматором, который

строится на основе одноразрядных сумматоров. Каждый одноразрядный сумматор складывает коды соответствующих разрядов слагаемых, прибавляет к ним значение переноса из младшего разряда и при необходимости формирует единицу переноса в следующий старший разряд.Слайд 50

Элементы и узлы ЭВМ

Одноразрядный двоичный сумматор может быть построен на

основе полусумматоров, осуществляющих сложение двух одноразрядных двоичных чисел без прибавления

к ним значения переноса из младшего разряда

Слайд 52

Элементы и узлы ЭВМ

Функциональная схема одного из вариантов сумматора SM

и его условное обозначение на схемах показаны на рис. ниже.

Одноразрядный

сумматор может быть реализован на основе полусумматора HS.

Слайд 54

Элементы и узлы ЭВМ

Многоразрядный сумматор можно получить простым последовательным соединением

одноразрядных сумматоров (см. рис. ниже). Очевидно, что время выполнения операции

сложения в такой схеме будет определяться временем распространения возможного сигнала через все одноразрядные сумматоры. Уменьшить время выполнения операции сложения можно с помощью блока ускоренного переноса.

Слайд 56

Элементы и узлы ЭВМ

В современных ЭВМ элементы и узлы компьютера

существуют в виде библиотек, реализуемых в виде «прошивки» логической структуры

ЧИПа процессора, называемой IP-блоком.IP-блок физически реализуется в виде ПЛИС, БМК или ASIC.

Далее рассмотрим построение элементарного микропроцессора на базе первого однокристального ЧИПа КР580, ставшего прототипом всех ЭВМ.

Слайд 57

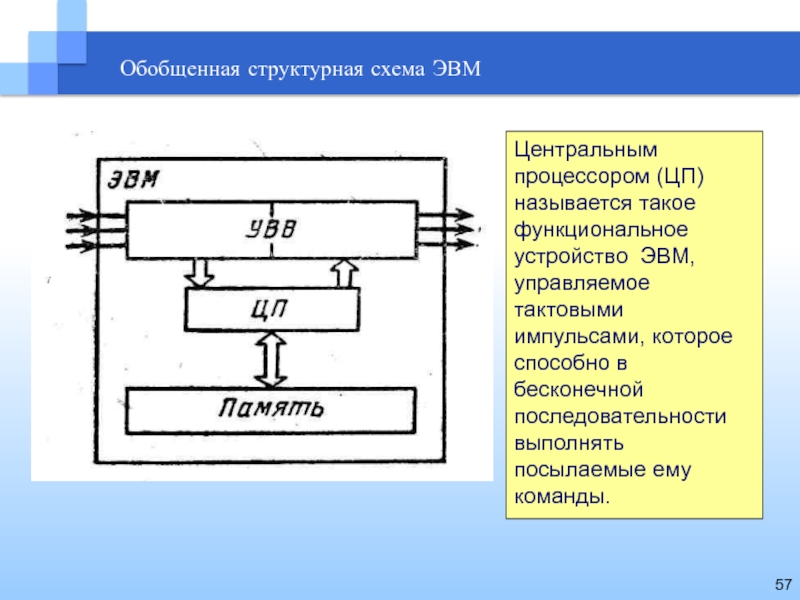

Центральным процессором (ЦП) называется такое функциональное устройство ЭВМ, управляемое тактовыми

импульсами, которое способно в бесконечной последовательности выполнять посылаемые ему команды.

Обобщенная

структурная схема ЭВМСлайд 59Организация работы центрального процессора

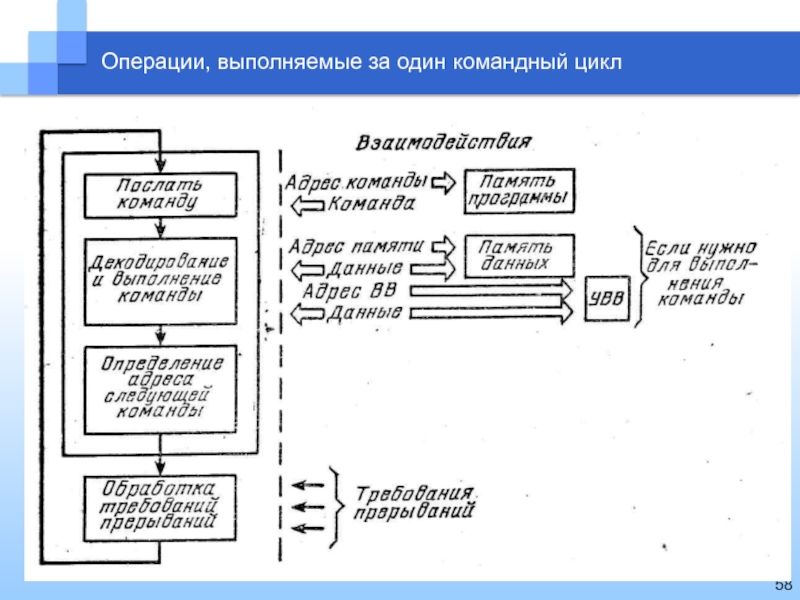

Вызвать команду . Для нее процессор располагает

местом в памяти — регистром команд. Поэтому команда из памяти

программы сначала загружается в этот регистр.Слайд 60Выполнить команду. Содержимое регистра команд анализируется процессором, декодируется и выполняется

в типовой для каждого процессора последовательности элементарных шагов — микрокоманд.

При этом в зависимости от ее содержания нужны либо действия внутри процессора, либо процессы обмена данными, взаимодействия с элементами памяти (считывание или запись) или с каналами ввода-вывода (выдача или ввод информации). Продолжительность этого этапа может быть различной.Организация работы центрального процессора

Слайд 61Осуществить проверку запросов прерывания. Во многих случаях работы в реальном

времени нужно среагировать на определенные события, возникающие вне процессора случайно.

Поэтому в такой ситуации должен произойти переход к подпрограмме, выполняемой как необходимая реакция ЭВМ. Это означает, что осуществляется прерывание текущей программыОрганизация работы центрального процессора

Слайд 62Устройства ЭВМ, осуществляющие прерывание процессора называются системами прерывания и являются

(по крайней мере, частично) составной частью, каждого ЦП.

Последующий адрес сохраняется

в специально предусмотренной для этого области памяти, а системой прерывания вырабатывается предусмотренный для каждого конкретного случая начальный адрес подпрограммы обслуживания прерывания. Таким образом, гарантируется, что после ее выполнения сохраненный первоначальный адрес следующей команды извлекается (разумеется, с временной задержкой) и прерванная программу может быть продолжена без потери информацииСистема прерываний центрального процессора

Слайд 63

Способность прерывания является решающим инструментом обработки информации в реальном времени.

Пропускная способность систем прерывания (например, требуемое время перехода к подпрограмме)

является поэтому важнейшим параметром ЭВМ.Система прерываний центрального процессора