Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

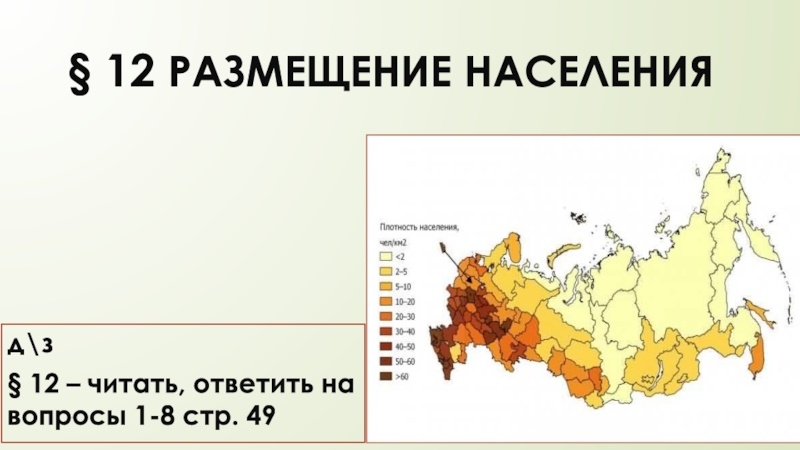

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

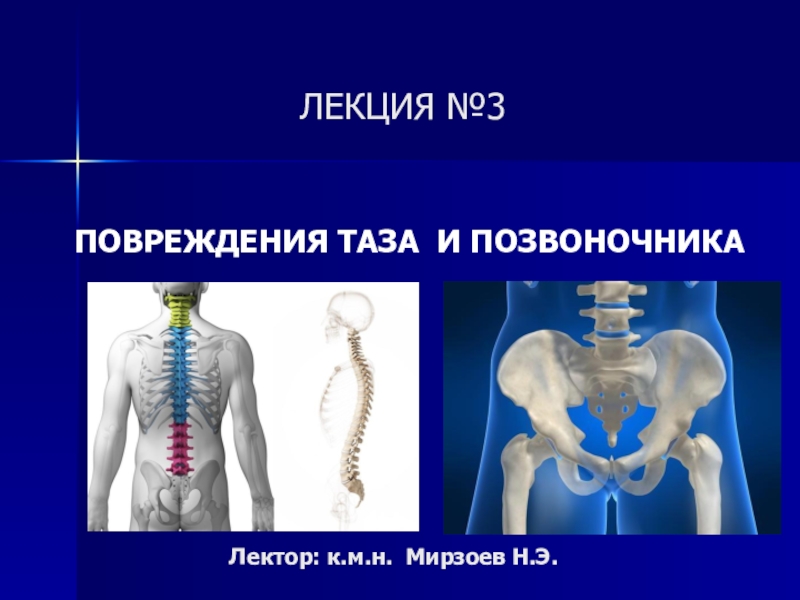

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Современные МП

Содержание

- 1. Современные МП

- 2. SPARC – SUN MIPS – Silicon

- 3. 2. Эволюция Intel x86 8086 16 разрядов

- 4. 286 появился защищ. режим поддержка многозадачности 386 32 разряда поддержка страничной адресации памяти мобильный вариант!

- 5. 486 в 2 раза меньше тактов

- 6. 586 – Pentium два конвейера отдельные

- 7. MMX-расширение – 57 спец. команд для

- 8. Pentium Pro Исполнение по предположению Внеочередное

- 9. P-II = PentiumPro + MMX Дешевле, чем

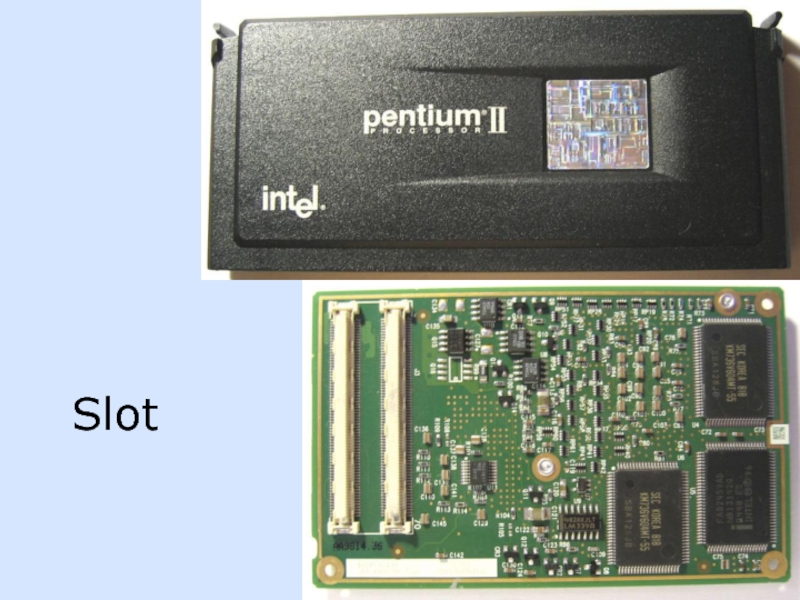

- 10. Slot

- 11. Слайд 11

- 12. P-III Streaming SIMD Extensionsобработка 4 двойных слов в FPU одновременно

- 13. Новые регистры – для обработки арифметических

- 14. P-IV Гиперконвейер: >20 шаговSpeed Daemon

- 15. “quad pumped” busЭффективная частота СШ до 1066 МГц SSE2 L3 до 2 МБ (Extreme Edition)

- 16. Hyper-Threading (HT) – «многопоточная» обработкаУдвоение числа некоторых регистровДва потока командБолее полная загрузка ОУ

- 17. Itanium 2 VLIW 64 бит ALU, 80

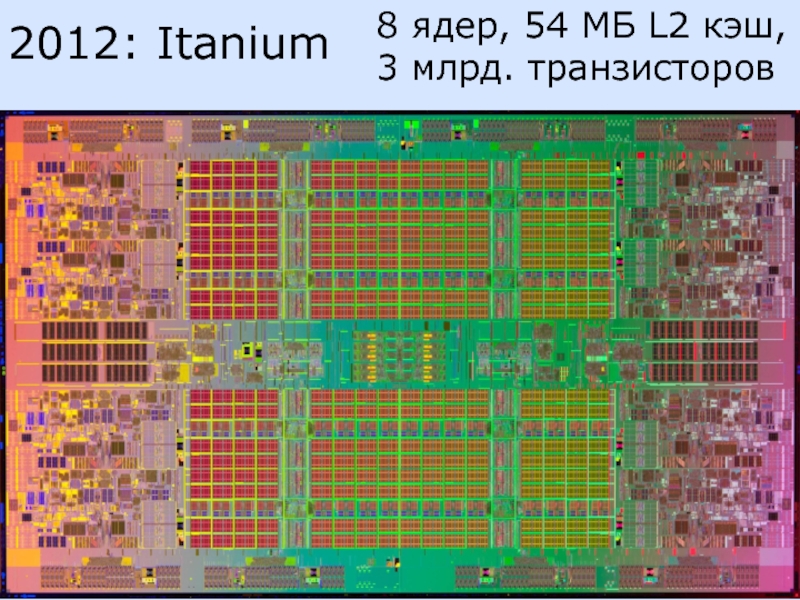

- 18. 2012: Itanium8 ядер, 54 МБ L2 кэш, 3 млрд. транзисторов

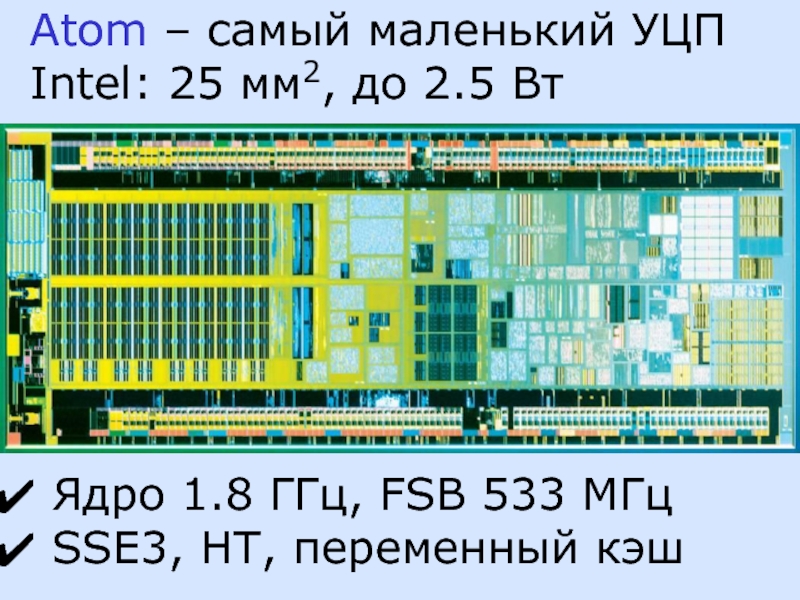

- 19. Atom – самый маленький УЦП Intel: 25

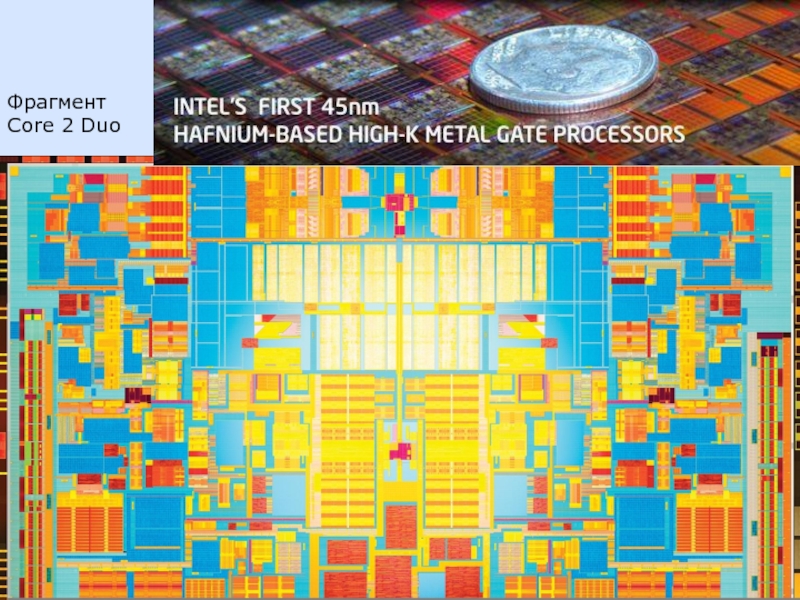

- 20. Фрагмент Core 2 Duo

- 21. 2008C трёхканальным контроллером DDR3

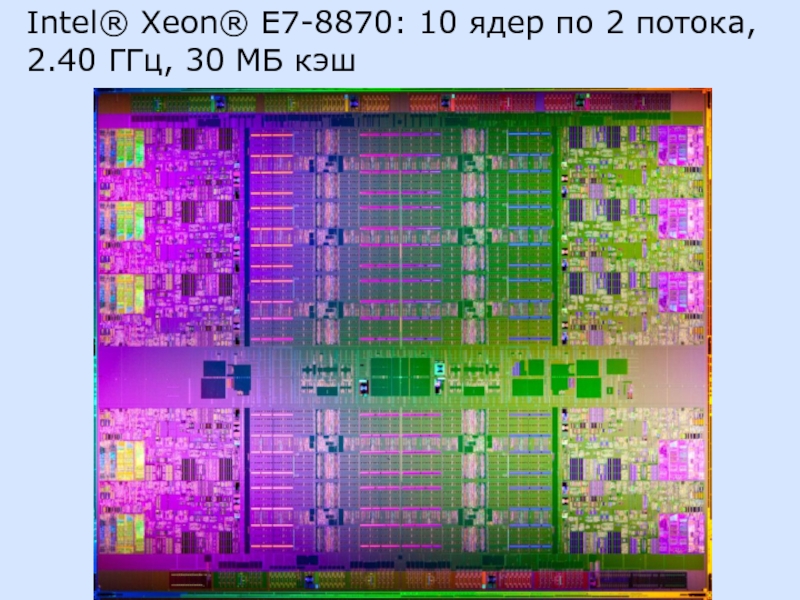

- 22. Intel® Xeon® E7-8870: 10 ядер по 2 потока, 2.40 ГГц, 30 МБ кэш

- 23. 3. Современные AMD x86 Фирма AMD основана

- 24. K6-II (Athlon) – герой AMD 1999 г.

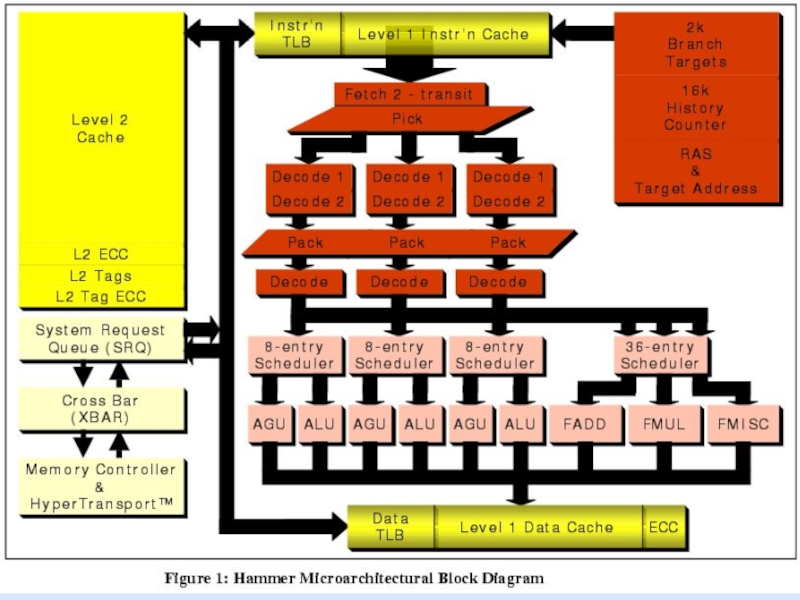

- 25. 8 поколение AMDАрхитектура x86-64 (Hammer): полная совместимость

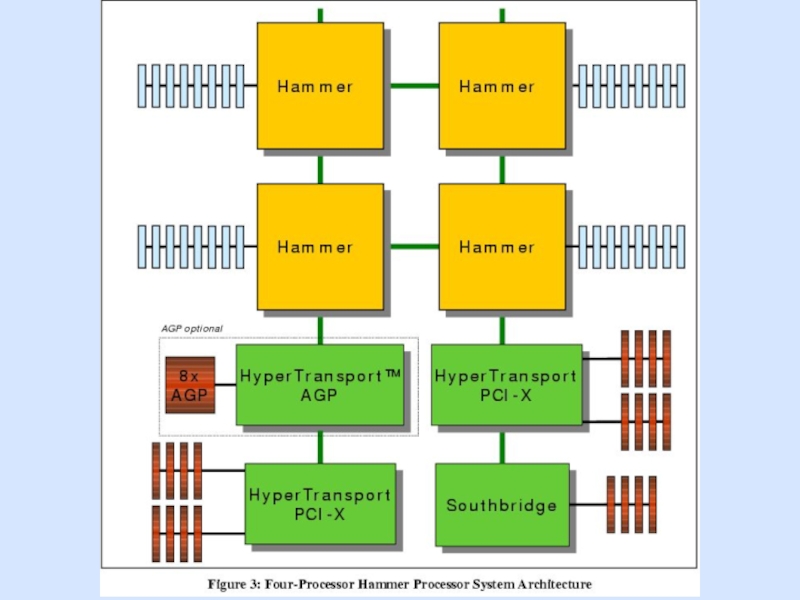

- 26. Opteron – серверный ЦП: встроен 2-канальный

- 27. Слайд 27

- 28. Слайд 28

- 29. Athlon 64 – урезанный Opteron: одноканальный контроллер пямяти Cool‘n'QuietСистема бесшумна, если мало загружена

- 30. Sempron – урезанная (32-бит, 256 КБ L2 и 333 МГц FSB)версия Athlon 64

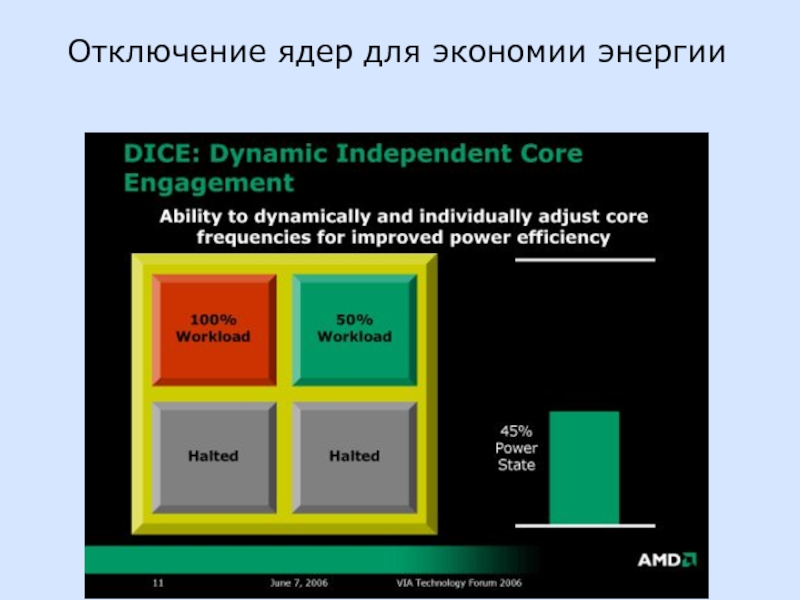

- 31. Отключение ядер для экономии энергии

- 32. Модное направление – использование GPU для научных вычислений: > 1Топ/c

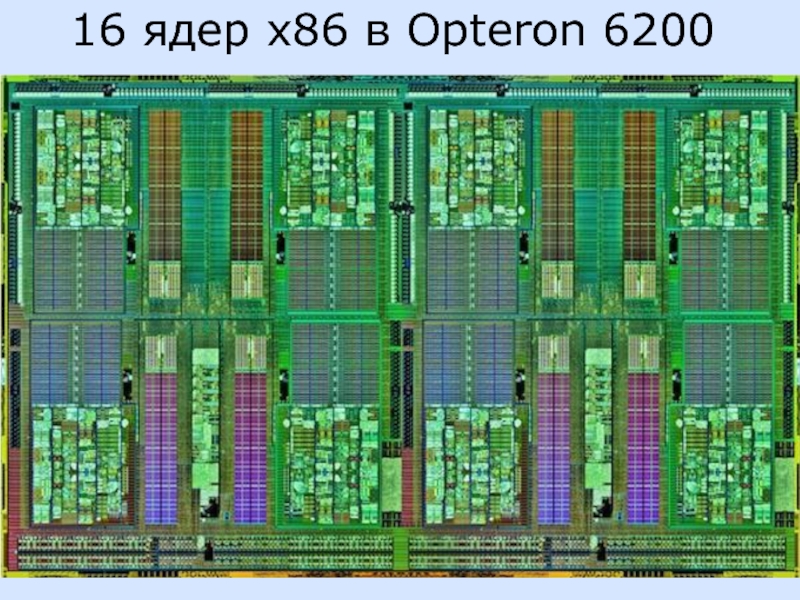

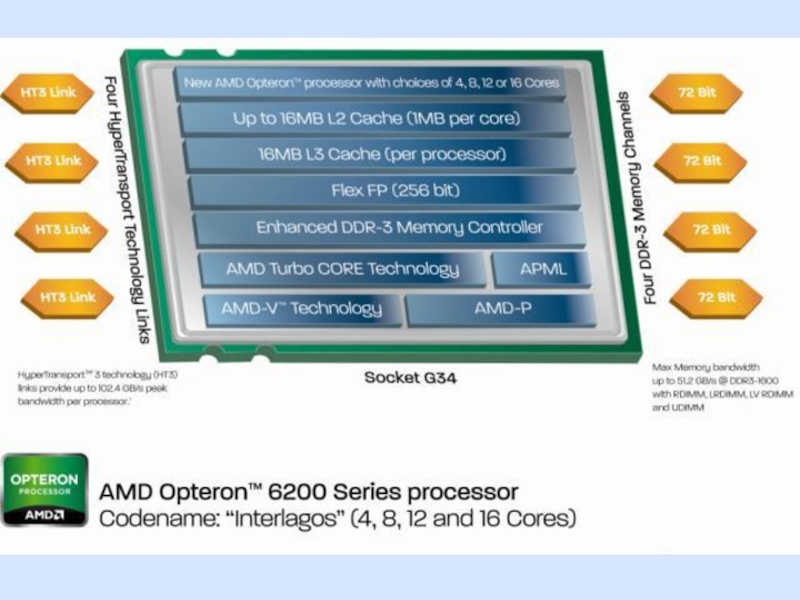

- 33. 16 ядер x86 в Opteron 6200

- 34. Слайд 34

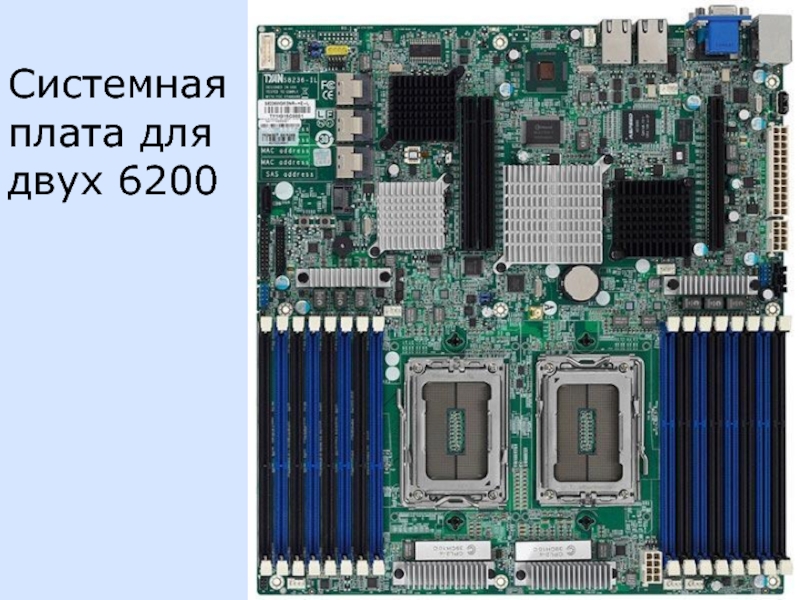

- 35. Системная плата для двух 6200

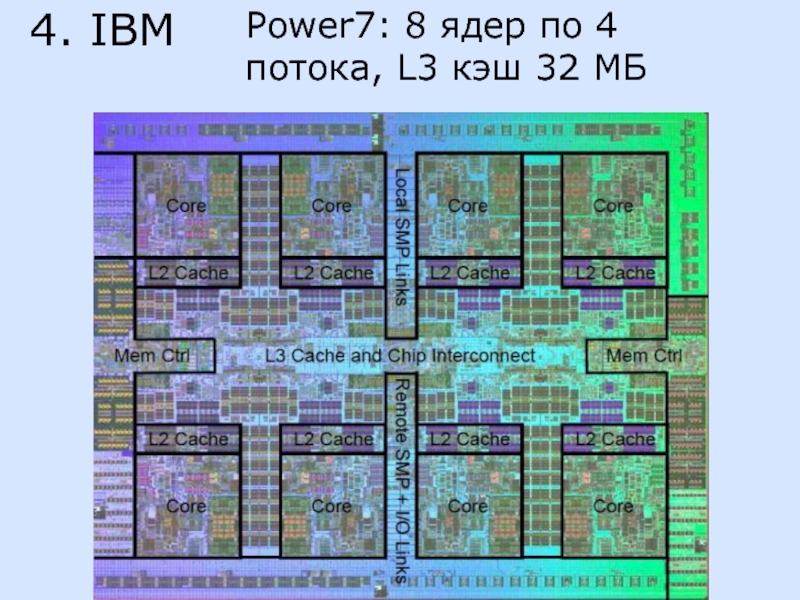

- 36. Power7: 8 ядер по 4 потока, L3 кэш 32 МБ4. IBM

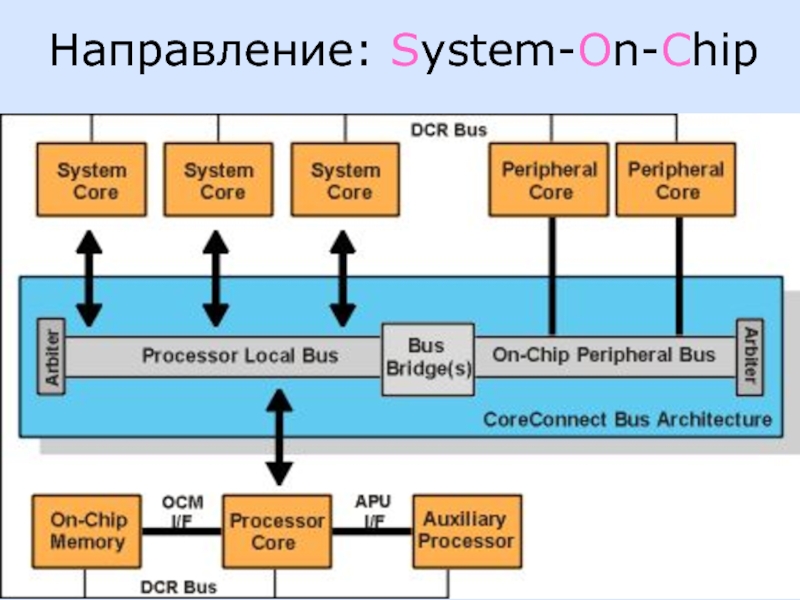

- 37. Направление: System-On-Chip

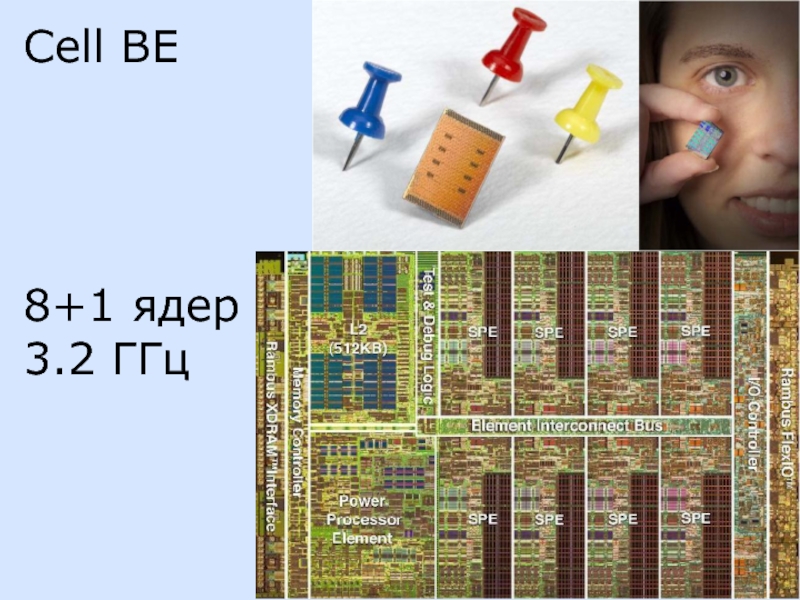

- 38. Cell BE8+1 ядер3.2 ГГц

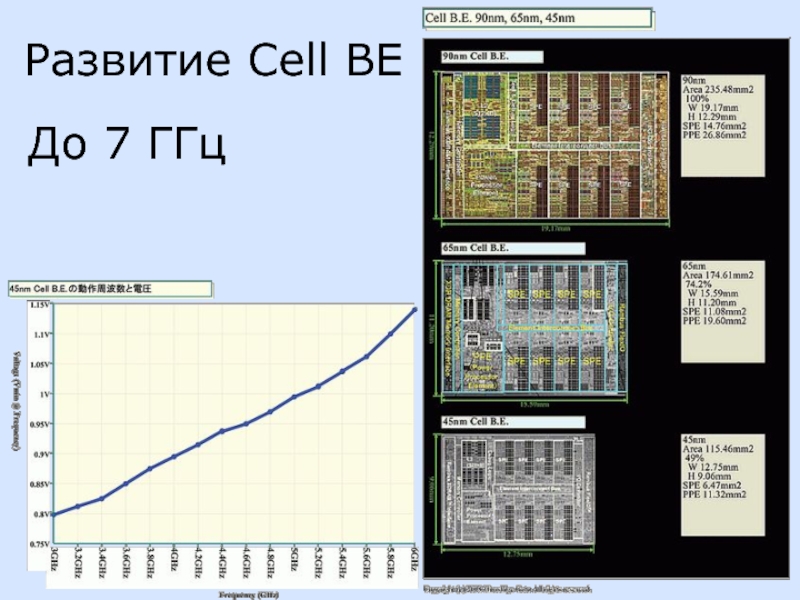

- 39. Развитие Cell BEДо 7 ГГц

- 40. 5. SUN“Stanford University Network”since 1982 1987 –

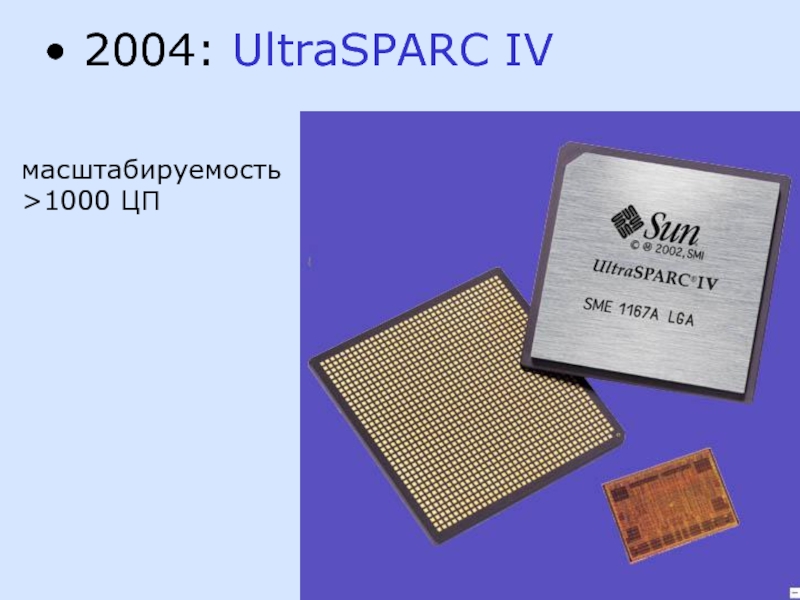

- 41. 2004: UltraSPARC IV масштабируемость >1000 ЦП

- 42. 8 ядер по 4 потока =32 потока1.2 ГГц80 Вт 2005: UltraSPARC T1

- 43. 2007: UltraSPARC T2 8 ядер по

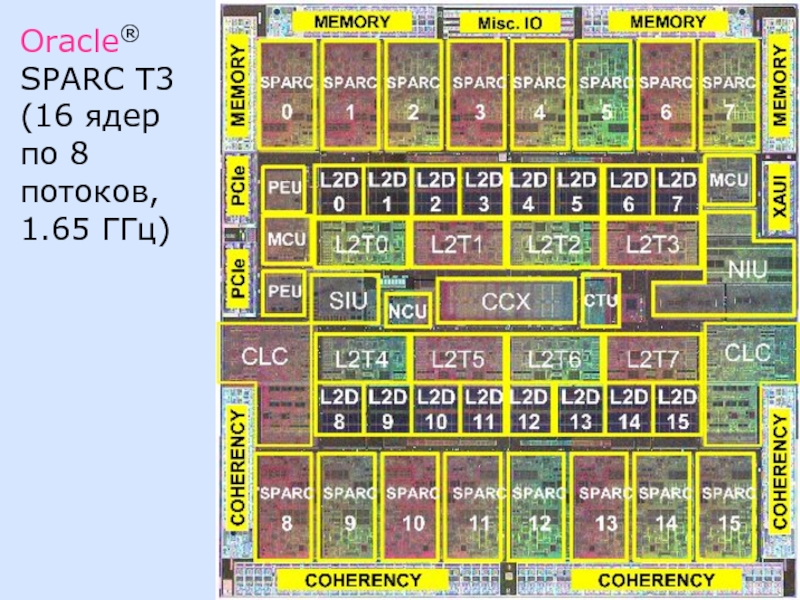

- 44. Oracle® SPARC T3 (16 ядер по 8 потоков, 1.65 ГГц)

- 45. 6. МЦСТЭльбрус 2000 300 МГц L2 256

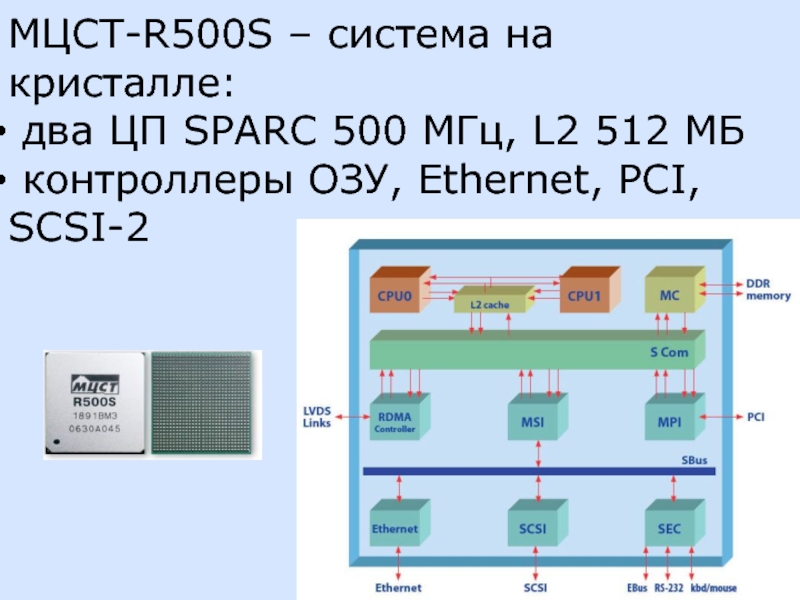

- 46. МЦСТ-R500S – система на кристалле: два ЦП

- 47. Восьмипроцессорная одноплатная универсальная ЭВМ на базе МЦСТ-R500SВычислительный комплекс «Эльбрус-3М1» в серверном исполнении

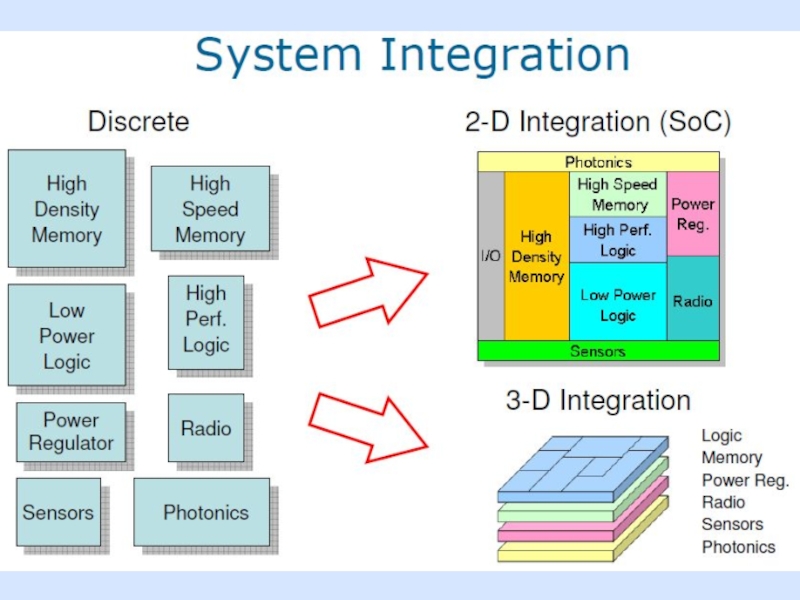

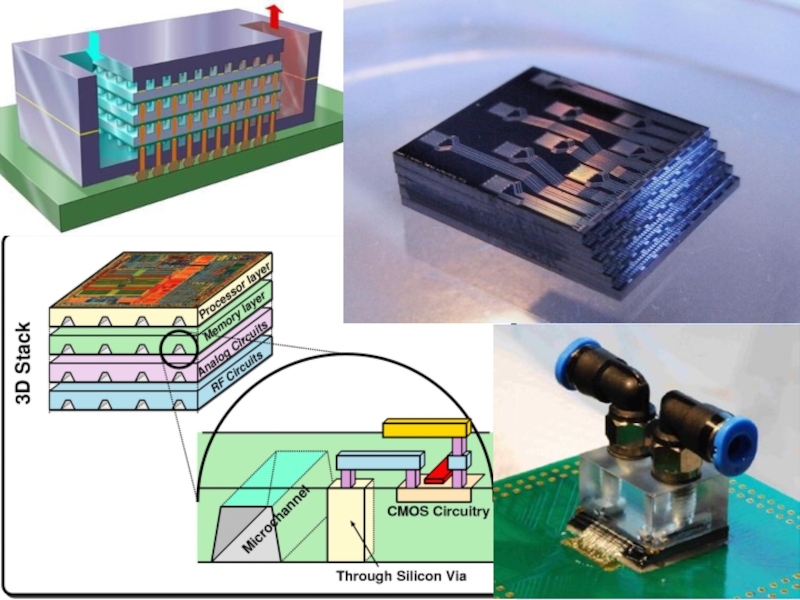

- 48. 7. Тенденции развития УМП Рост числа ядер числа параллельных конвейеров объёма кэшей

- 49. Brainiac-методы Уменьшение энергопотребления и размеров Интеграция с чипсетом (SOC)

- 50. Слайд 50

- 51. Слайд 51

- 52. Скачать презентанцию

SPARC – SUN MIPS – Silicon GraphicsИсторически x86 доминировала в ПК, остальные – в серверах и суперкомпьютерах.Но сейчас всё смешалось.

Слайды и текст этой презентации

Слайд 1§3 Современные универсальные МП (УМП)

1. Основные архитектуры

x86(-64) – Intel,

AMD, VIA

Alpha – HP (Compaq, DEC)Слайд 2 SPARC – SUN

MIPS – Silicon Graphics

Исторически x86 доминировала

в ПК, остальные – в серверах и суперкомпьютерах.

Но сейчас всё

смешалось.Слайд 32. Эволюция Intel x86

8086

16 разрядов для команд и

данных, 20 – для адреса !

дешевле, чем Apple II

Успех

Слайд 4 286

появился защищ. режим

поддержка многозадачности

386

32 разряда

поддержка страничной адресации памяти

мобильный вариант!

Слайд 5 486

в 2 раза меньше тактов на выполнение команды

встроены: L1-кэш, FPU

частота ядра: 40*3 МГц !

Скорость!

Триумф

графического

интерфейса

Слайд 6 586 – Pentium

два конвейера

отдельные кэши L1 для

команд и данных

предсказание переходов

64 бит шина данных

режимы

SMP и Master/Checkerконтроллер многопроц. прерываний (до 60 !)

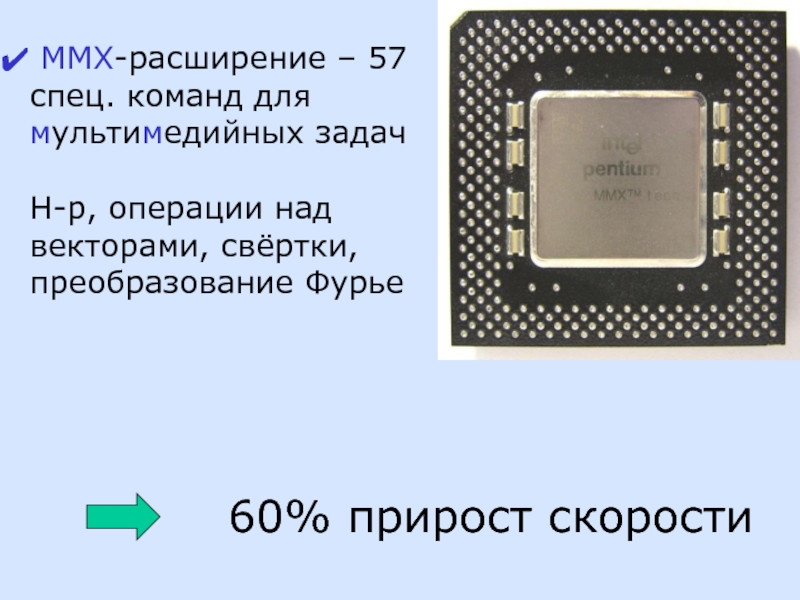

Слайд 7 MMX-расширение – 57 спец. команд для мультимедийных задач

Н-р,

операции над векторами, свёртки, преобразование Фурье

60% прирост скорости

Слайд 8 Pentium Pro

Исполнение по предположению

Внеочередное исполнение

DIB –

Dual Independent Bus (see BSB, FSB)

Встроен L2-кэш 1 М

Слайд 9P-II = PentiumPro + MMX

Дешевле, чем PPro, за счёт

вынесения L2-кэша на другой кристалл

ECC в кэше L2 и

на шине адреса – надёжностьтермодиод – контроль T

Xeon-версия – кэш до 2 МБ

Слайд 13 Новые регистры – для обработки арифметических исключений

Более надёжные

расчёты

Самоконтроль сбоев в микрокоде и кэше

Серийный номер

Слайд 16Hyper-Threading (HT) – «многопоточная» обработка

Удвоение числа некоторых регистров

Два потока команд

Более

полная загрузка ОУ

Слайд 17Itanium 2

VLIW

64 бит ALU, 80 – FPU, 128

– шина данных

встроен L3-кэш до 3 МБ

масштабируемость

Слайд 19Atom – самый маленький УЦП Intel: 25 мм2, до 2.5

Вт

Ядро 1.8 ГГц, FSB 533 МГц

SSE3, HT, переменный

кэшСлайд 233. Современные AMD x86

Фирма AMD основана в 1969 г.

Sunnyvale,

California

До 1990 г. отставала от Intel на одно поколение

Делала «клоны»

по лицензииСлайд 24K6-II (Athlon) – герой AMD 1999 г.

3DNow! – команды

для 2 real операндов

мощный блок предсказаний

Слайд 258 поколение AMD

Архитектура x86-64 (Hammer):

полная совместимость с x86

64

разрядные регистры общего назначения

- VLIW

- выше точность FPU

- либо удвоение

скоростиСлайд 26 Opteron – серверный ЦП:

встроен 2-канальный контроллер DDR DRAM

(по 4 DIMM на канал)

HyperTransport линки для 8 ЦП,

PCI-X, AGP8xПоддержка SSE2

L2=1MB