Слайд 1Технология ИС

Путря Михаил Георгиевич

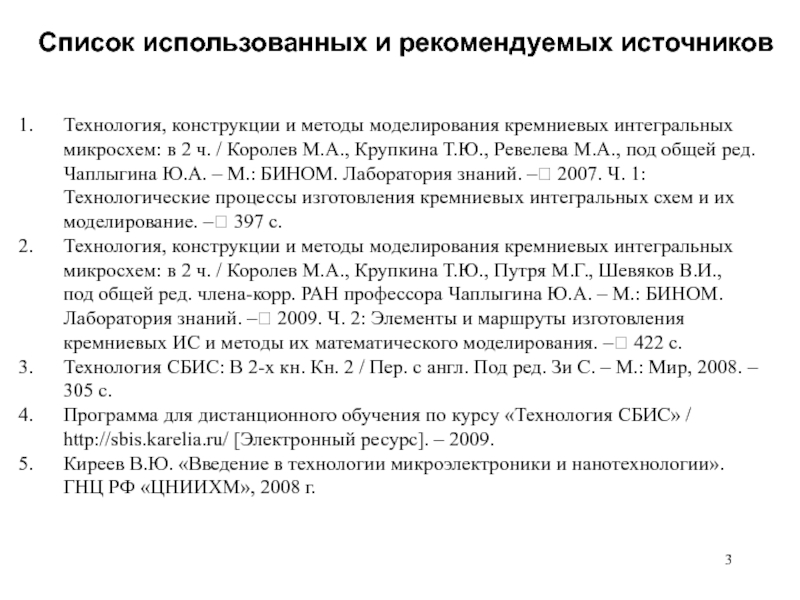

Слайд 3Список использованных и рекомендуемых источников

Технология, конструкции и методы моделирования кремниевых

интегральных микросхем: в 2 ч. / Королев М.А., Крупкина Т.Ю.,

Ревелева М.А., под общей ред. Чаплыгина Ю.А. – М.: БИНОМ. Лаборатория знаний. – 2007. Ч. 1: Технологические процессы изготовления кремниевых интегральных схем и их моделирование. – 397 с.

Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч. / Королев М.А., Крупкина Т.Ю., Путря М.Г., Шевяков В.И., под общей ред. члена-корр. РАН профессора Чаплыгина Ю.А. – М.: БИНОМ. Лаборатория знаний. – 2009. Ч. 2: Элементы и маршруты изготовления кремниевых ИС и методы их математического моделирования. – 422 с.

Технология СБИС: В 2-х кн. Кн. 2 / Пер. с англ. Под ред. Зи С. – М.: Мир, 2008. – 305 с.

Программа для дистанционного обучения по курсу «Технология СБИС» / http://sbis.karelia.ru/ [Электронный ресурс]. – 2009.

Киреев В.Ю. «Введение в технологии микроэлектроники и нанотехнологии». ГНЦ РФ «ЦНИИХМ», 2008 г.

Слайд 4Уровень технологии определяется минимально возможной топологической нормой, т. е. минимальным

размером элемента или зазора в периодических структурах с минимальным периодом

(с максимальной плотностью упаковки).

Lmin= ½ pitch (шаг), который в настоящее время определяется по первому уровню разводки.

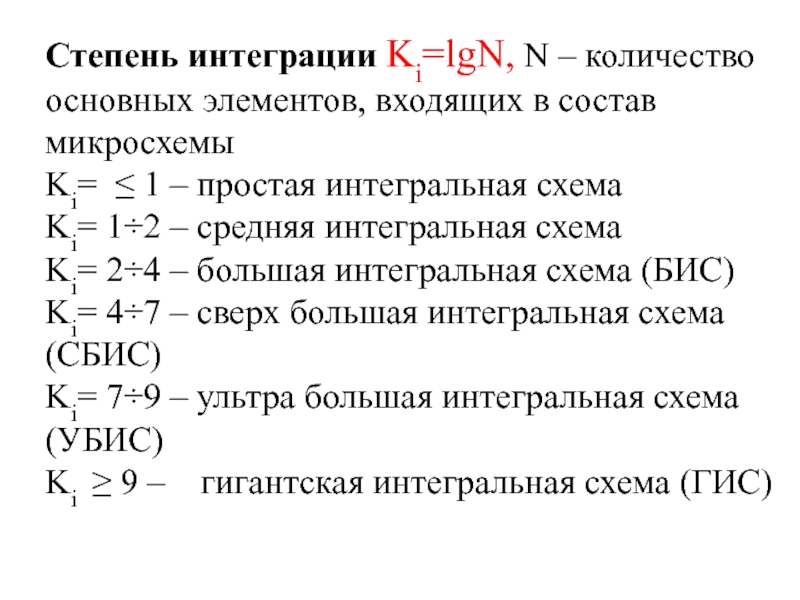

Слайд 5Степень интеграции Ki=lgN, N – количество основных элементов, входящих в

состав микросхемы

Ki= ≤ 1 – простая интегральная схема

Ki= 1÷2 –

средняя интегральная схема

Ki= 2÷4 – большая интегральная схема (БИС)

Ki= 4÷7 – сверх большая интегральная схема (СБИС)

Ki= 7÷9 – ультра большая интегральная схема (УБИС)

Ki ≥ 9 – гигантская интегральная схема (ГИС)

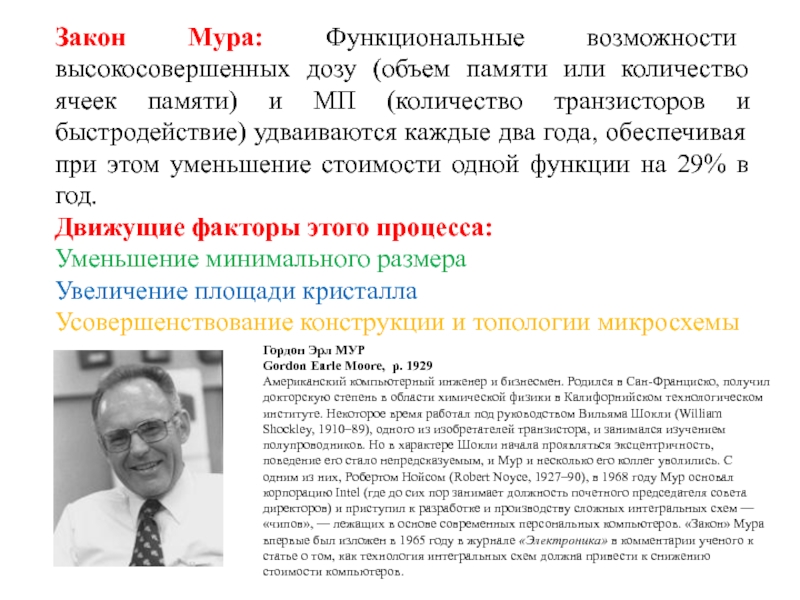

Слайд 6Закон Мура: Функциональные возможности высокосовершенных дозу (объем памяти или количество

ячеек памяти) и МП (количество транзисторов и быстродействие) удваиваются каждые

два года, обеспечивая при этом уменьшение стоимости одной функции на 29% в год.

Движущие факторы этого процесса:

Уменьшение минимального размера

Увеличение площади кристалла

Усовершенствование конструкции и топологии микросхемы

Гордон Эрл МУР

Gordon Earle Moore, р. 1929

Американский компьютерный инженер и бизнесмен. Родился в Сан-Франциско, получил докторскую степень в области химической физики в Калифорнийском технологическом институте. Некоторое время работал под руководством Вильяма Шокли (William Shockley, 1910–89), одного из изобретателей транзистора, и занимался изучением полупроводников. Но в характере Шокли начала проявляться эксцентричность, поведение его стало непредсказуемым, и Мур и несколько его коллег уволились. С одним из них, Робертом Нойсом (Robert Noyce, 1927–90), в 1968 году Мур основал корпорацию Intel (где до сих пор занимает должность почетного председателя совета директоров) и приступил к разработке и производству сложных интегральных схем — «чипов», — лежащих в основе современных персональных компьютеров. «Закон» Мура впервые был изложен в 1965 году в журнале «Электроника» в комментарии ученого к статье о том, как технология интегральных схем должна привести к снижению стоимости компьютеров.

Слайд 7 Современные тенденции масштабирования ИС могут

быть сформулированы следующим образом:

- новое поколение технологии появляется через каждые

три года;

- при этом уровень интеграции ИС памяти увеличивается в четыре раза, а логических ИС – в 2-3 раза;

- за каждые два поколения технологии (то есть за 6 лет) минимальный характеристический размер уменьшается в два раза, а плотность тока, быстродействие, площадь кристалла и максимальное количество входов и выходов увеличиваются в два раза.

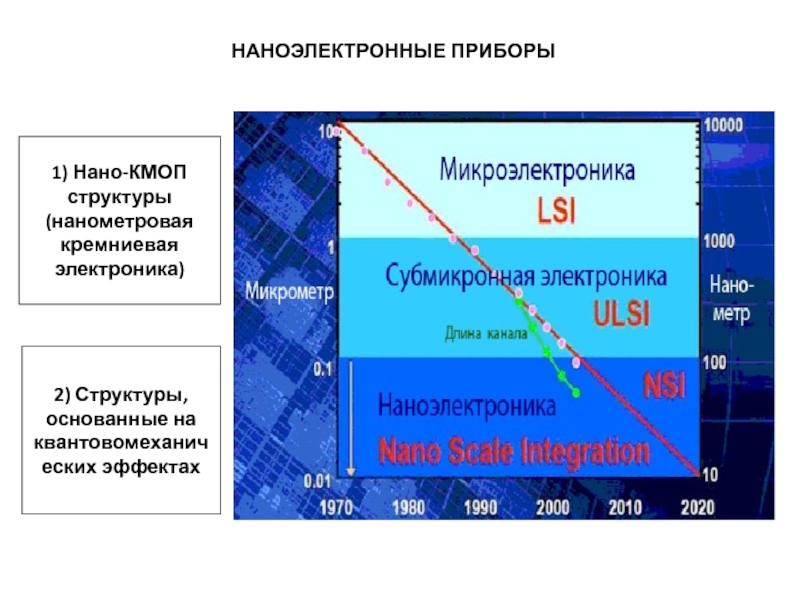

Слайд 8НАНОЭЛЕКТРОННЫЕ ПРИБОРЫ

2) Структуры, основанные на

квантовомеханических эффектах

1) Нано-КМОП

структуры (нанометровая

кремниевая

электроника)

Слайд 9

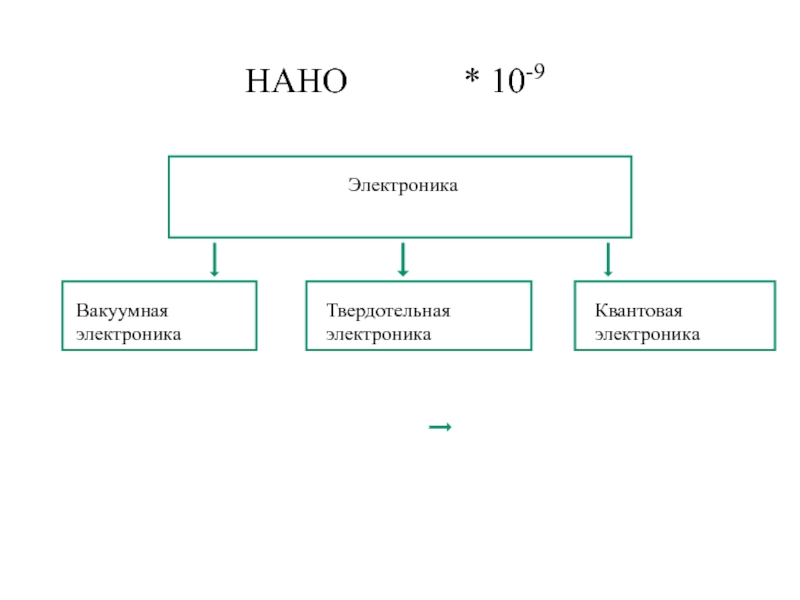

Электроника

Вакуумная электроника

Твердотельная электроника

Квантовая электроника

НАНО

* 10-9

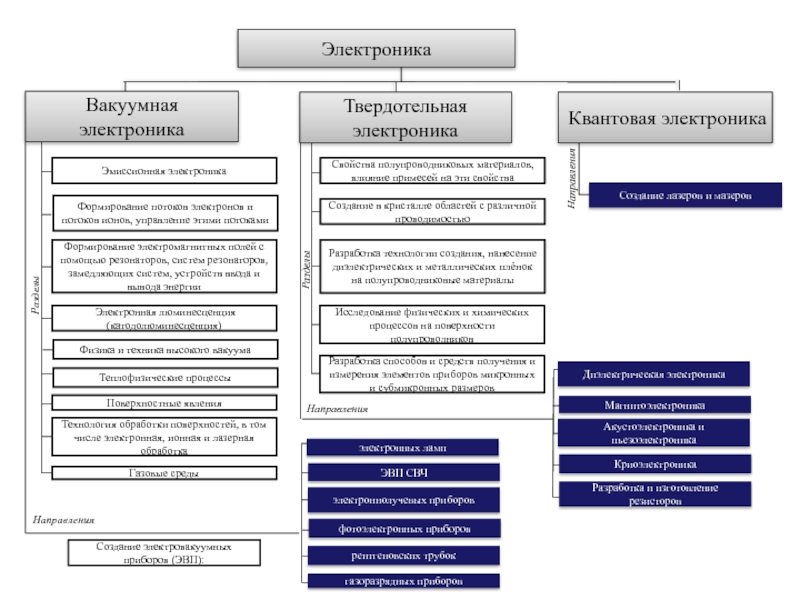

Слайд 10Электроника

Квантовая электроника

Создание электровакуумных приборов (ЭВП):

Акустоэлектроника и пьезоэлектроника

Разработка и изготовление резисторов

Криоэлектроника

Магнитоэлектроника

Диэлектрическая электроника

Создание

лазеров и мазеров

Вакуумная электроника

Твердотельная электроника

Разделы

Направления

Разделы

Направления

Направления

Слайд 11

Электроника

Нанотехнологии

Наноэлектроника

Слайд 12Лауреат Нобелевской премии Р. Фейман «При переходе к изучению самых

маленьких объектов мы сталкиваемся со многими разнообразными явлениями, создающими новые

возможности. Поведение отдельных атомов подчиняется законам квантовой механики и не имеет аналогов в макроскопическом масштабе, поэтому «внизу» мы будем постоянно наблюдать новые закономерности и эффекты, предполагающие новые варианты использования»

Академик РАН Вячеслав Михайлович Бузник: «…под нанотехнологиями каждый часто понимает то, что ему удобно…»

Слайд 13Хотя, в силу широкой междисциплинарности нанотехнологий, единого определения на сегодняшний

день пока не существует., любое из определений должно обязательно отображать,

как минимум, три следующие характерные особенности нанотехнологий:

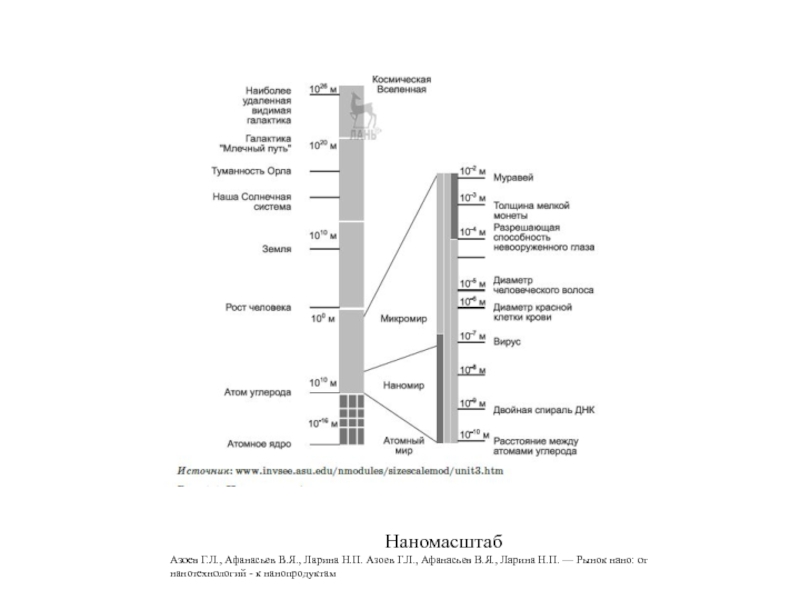

Нанодиапазон материальных структур, являющихся объектами нанотехнологий, -зот размеров отельных атомов или молекул до 100 нм;

Способность выполнения измерений (контроля)), манипулирования и разного рода преобразований в нанодиапазоне;

Использование новых свойств и функций, проявляющихся в нанодиапазоне.

Нанотехнология — это целенаправленный инжиниринг (создание и манипуляция) материалов и веществ на уровне менее 100 нм для получения свойств и функций, возникающих только при переходе в нано размер.

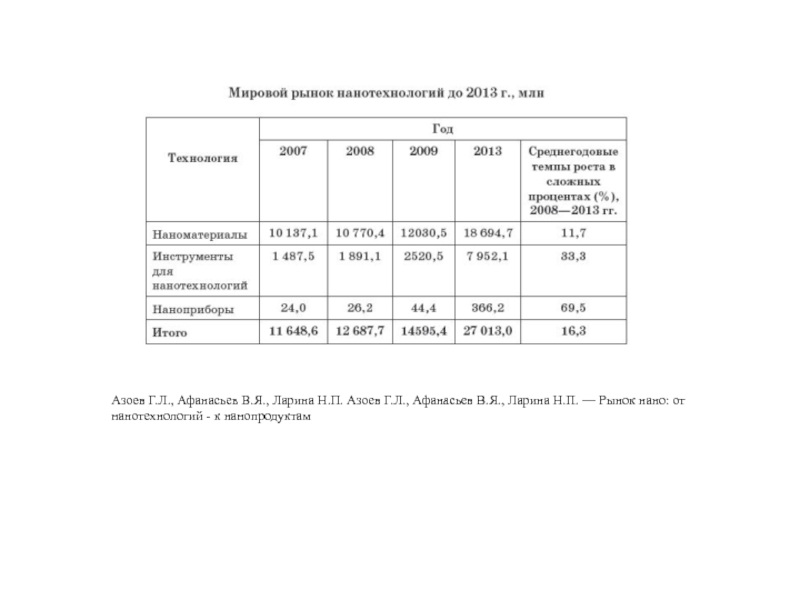

Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. — Рынок нано: от нанотехнологий - к нанопродуктам

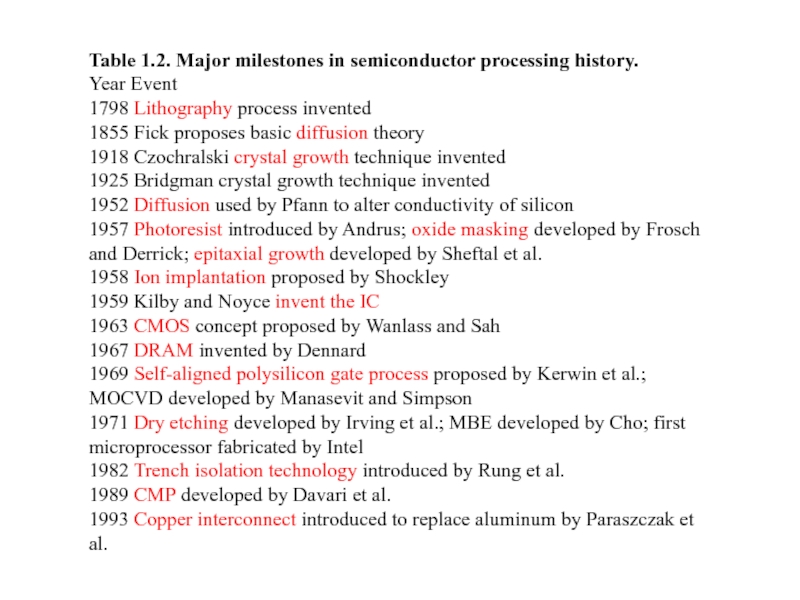

Слайд 14Table 1.2. Major milestones in semiconductor processing history.

Year Event

1798 Lithography

process invented

1855 Fick proposes basic diffusion theory

1918 Czochralski crystal growth

technique invented

1925 Bridgman crystal growth technique invented

1952 Diffusion used by Pfann to alter conductivity of silicon

1957 Photoresist introduced by Andrus; oxide masking developed by Frosch

and Derrick; epitaxial growth developed by Sheftal et al.

1958 Ion implantation proposed by Shockley

1959 Kilby and Noyce invent the IC

1963 CMOS concept proposed by Wanlass and Sah

1967 DRAM invented by Dennard

1969 Self-aligned polysilicon gate process proposed by Kerwin et al.;

MOCVD developed by Manasevit and Simpson

1971 Dry etching developed by Irving et al.; MBE developed by Cho; first

microprocessor fabricated by Intel

1982 Trench isolation technology introduced by Rung et al.

1989 CMP developed by Davari et al.

1993 Copper interconnect introduced to replace aluminum by Paraszczak et al.

Слайд 15Достижения микроэлектроники: a - кристалл одной из первых в мире

микросхем, изготовленной на фирме Fairchild (США) осенью 1960 г. по

100 мкм топологическим нормам (Lmin= 100 мкм) на кремниевой пластины диаметром 13 мм (0,5 дюйма) и содержащей 4-е биполярных транзистора; b - кристаллы размером (26х33) мм четырех ядерного (quad-core) микропроцессора Penryn, изготовленного фирмой Intel (США) в ноябре 2007 г. по 45 нм топологическим нормам (Lmin= 45 нм) на кремниевой пластине диаметром 300 мм (8 дюймов) и содержащего 820 миллионов КМОП-транзисторов.

Киреев В.Ю. Введение в технологии микроэлектроники и нанотехнологии. - М.:ФГУП «ЦНИИХМ», 2008. – 432 с

a)

b)

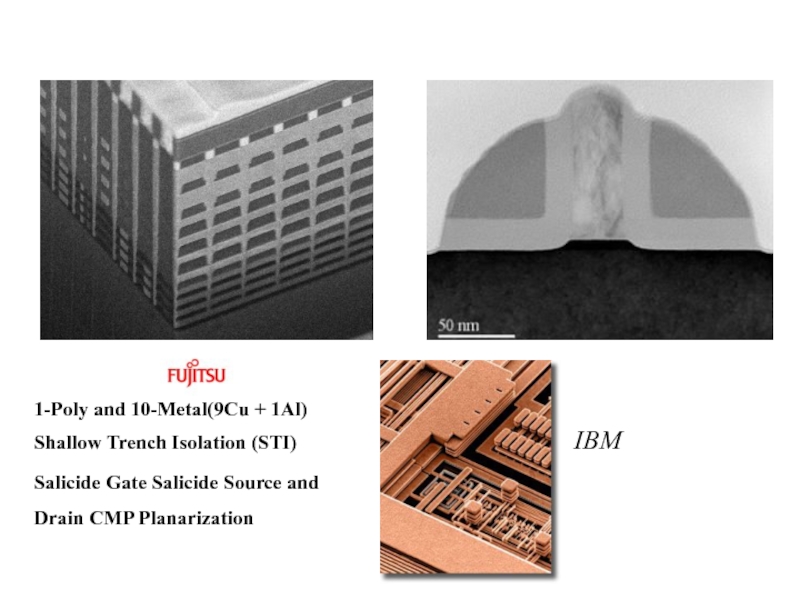

Слайд 161-Poly and 10-Metal(9Cu + 1Al)

Shallow Trench Isolation (STI)

Salicide Gate Salicide

Source and

Drain CMP Planarization

IBM

Слайд 18Наномасштаб

Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я.,

Ларина Н.П. — Рынок нано: от

нанотехнологий - к нанопродуктам

Слайд 20Вся продукция микро-, нано- электронной отрасли традиционно сегментируется на следующие

основные четыре группы компонентов:

оптоэлектроника;

датчики;

дискретные компоненты;

интегральные схемы

(ИС).

Слайд 21Оптоэлектронные компоненты:

• ПЗС и КМОП датчики изображения;

• лазерные

передатчики и звукосниматели;

• светоизлучающие диоды и светодиодные индикаторы;

•

инфракрасные устройства;

• устройства связи;

• цифровые дисплеи;

• другие оптоэлектронные устройства.

Слайд 22Датчики:

температурные датчики;

датчики давления;

датчики поворота и ускорения;

датчики

магнитного поля;

управляющие датчики.

микрогироскопы

Слайд 23Дискретные компоненты:

• cиловые транзисторы и модули;

• малосигнальные транзисторы;

• переключающие транзисторы;

• диоды, выпрямители и тиристоры;

• ВЧ/СВЧ-транзисторы

и модули.

Слайд 24Интегральные схемы:

микропроцессоры (Microprocessing Units - MPU);

микроконтроллеры (Microcontrolling

Units - MCU);

цифровые сигнальные процессоры (Digital Signal Processors -

DSP);

схемы памяти;

аналоговые схемы;

логические схемы.

Системы на кристалле

Слайд 25Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я.,

Ларина Н.П. — Рынок нано: от нанотехнологий - к нанопродуктам

Слайд 26Развитие рынка наноэлектронной продукции

Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев

Г.Л., Афанасьев В.Я., Ларина Н.П. — Рынок нано: от нанотехнологий

- к нанопродуктам

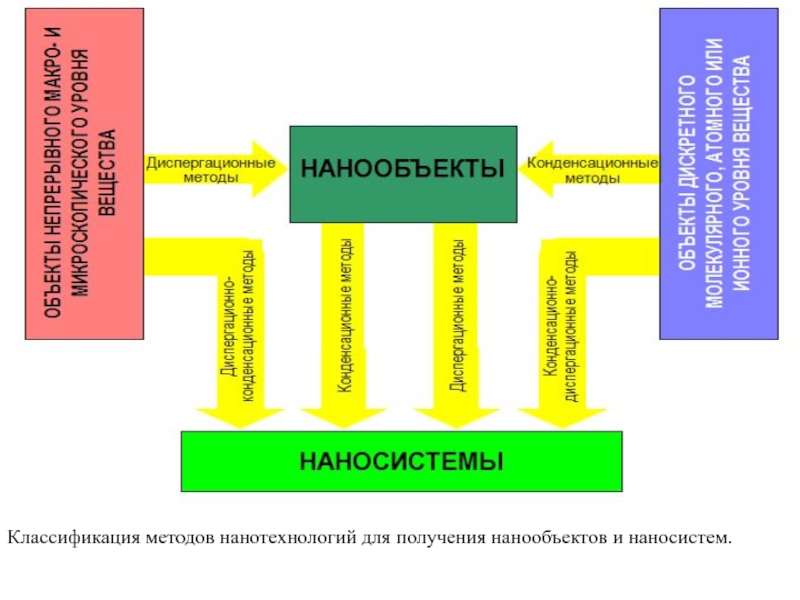

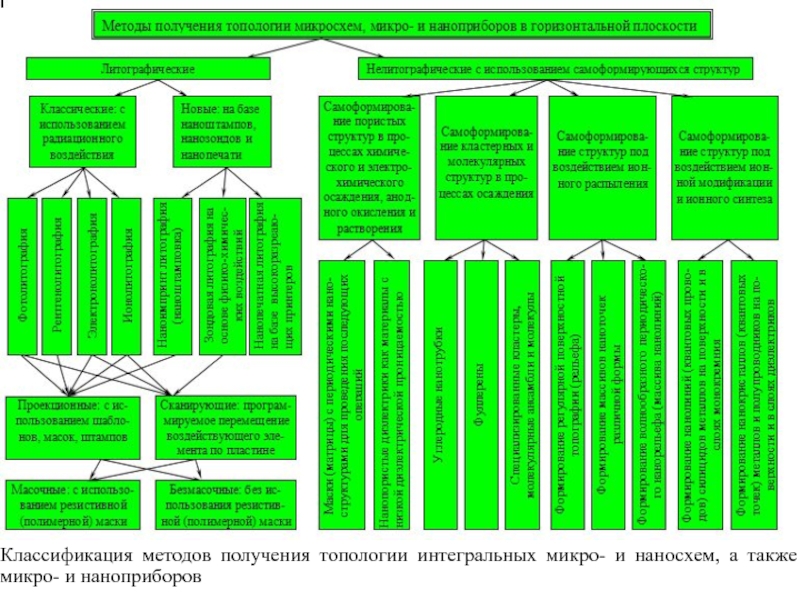

Слайд 27Классификация методов нанотехнологий для получения нанообъектов и наносистем.

Слайд 28Некоторые особенности работы наноэлектронных устройств

Слайд 29.

Принципиальная схема транзисторной структуры с управляющим затвором

Г.И. Зебрев «Физические основы

кремниевой наноэлектроники». Учебное пособие. — М.: МИФИ, 2008. — 288

с.

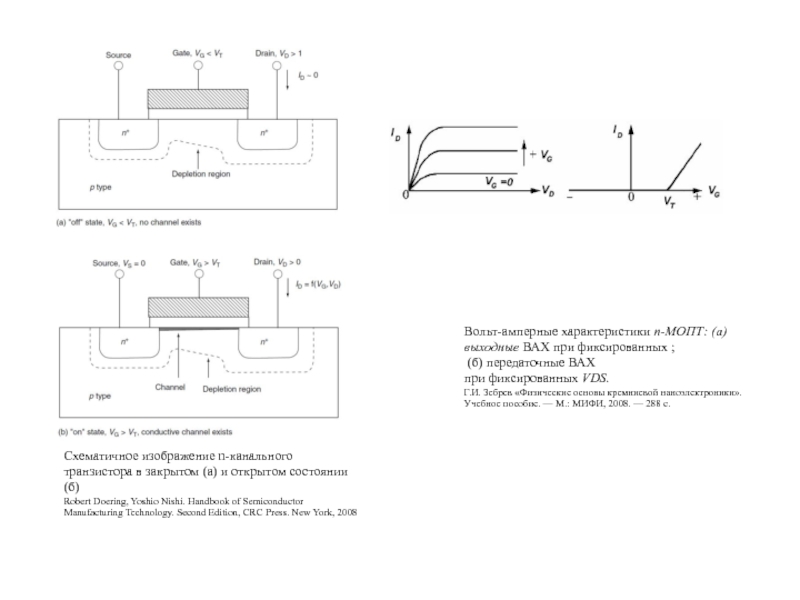

Слайд 30Схематичное изображение n-канального транзистора в закрытом (а) и открытом состоянии

(б)

Robert Doering, Yoshio Nishi. Handbook of Semiconductor Manufacturing Technology. Second

Edition, CRC Press. New York, 2008

Вольт-амперные характеристики n-МОПТ: (а) выходные ВАХ при фиксированных ;

(б) передаточные ВАХ

при фиксированных VDS.

Г.И. Зебрев «Физические основы кремниевой наноэлектроники». Учебное пособие. — М.: МИФИ, 2008. — 288 с.

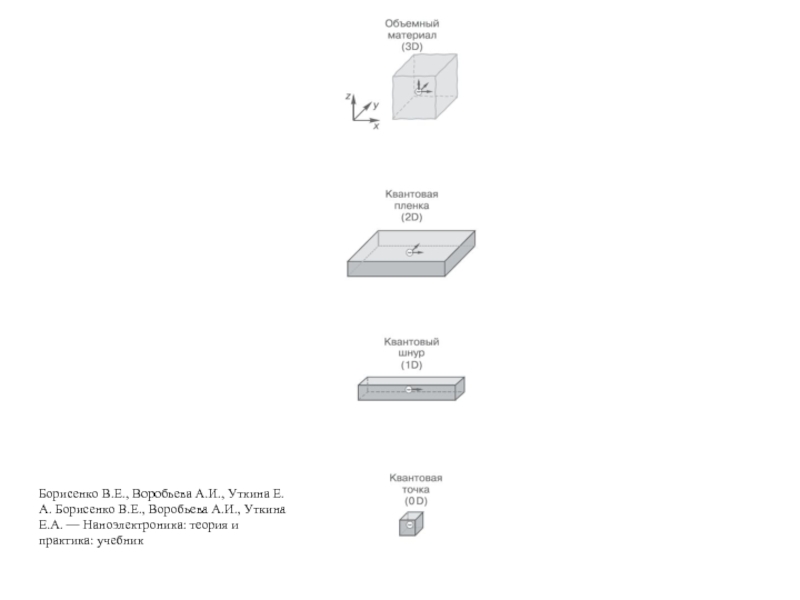

Слайд 31Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И.,

Уткина Е.А. — Наноэлектроника: теория и практика: учебник

Физические явления,

используемые в наноэлектронных приборах

Слайд 32Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И.,

Уткина

Е.А. — Наноэлектроника: теория и практика: учебник

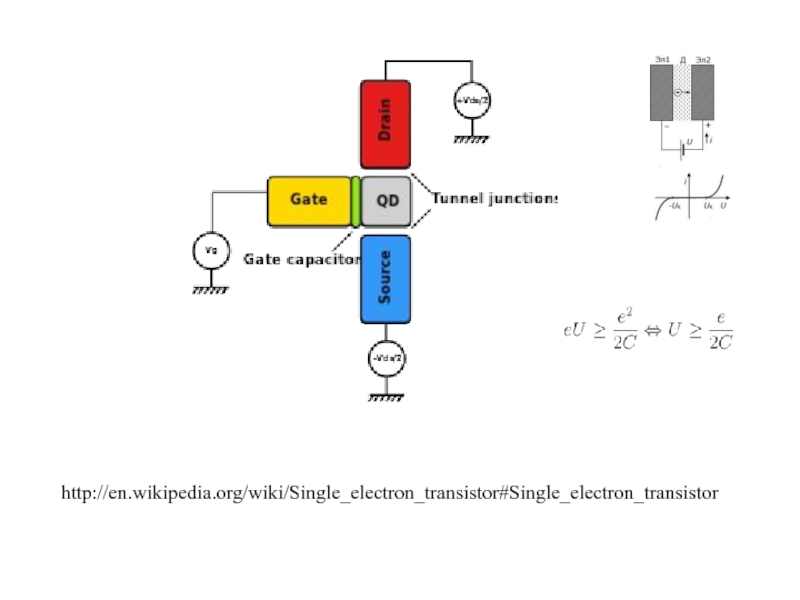

Слайд 33http://en.wikipedia.org/wiki/Single_electron_transistor#Single_electron_transistor

Слайд 34Схема одноэлектронного транзистора. Г. Г. Шишкин, И. М. Агеев Наноэлектроника.

Элементы, приборы, устройства. М. : БИНОМ. Лаборатория знаний, 2011 г.

408с.

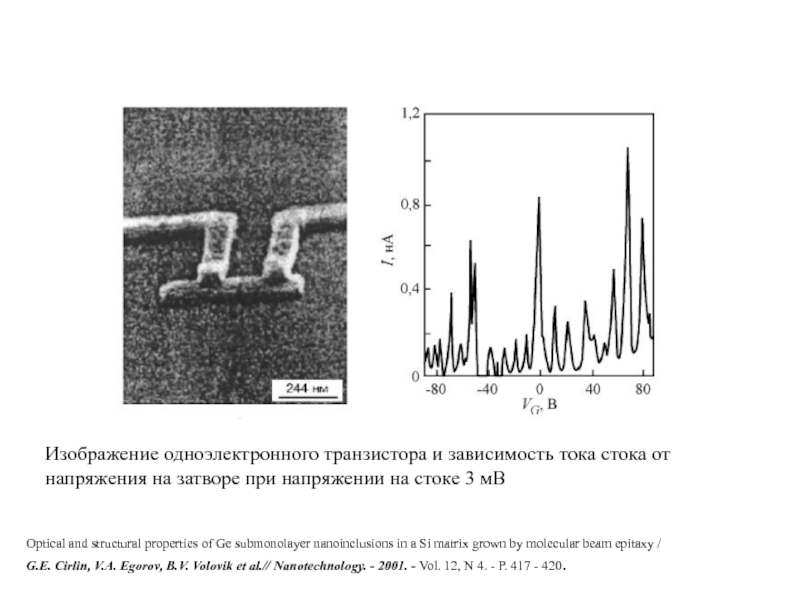

Слайд 35Изображение одноэлектронного транзистора и зависимость тока стока от напряжения на

затворе при напряжении на стоке 3 мВ

Optical and structural properties

of Ge submonolayer nanoinclusions in a Si matrix grown by molecular beam epitaxy /

G.E. Cirlin, V.A. Egorov, B.V. Volovik et al.// Nanotechnology. - 2001. - Vol. 12, N 4. - P. 417 - 420.

Слайд 36Конструкция транзистора на основе нанотрубки (разработчик — компания ≪Infineon Technologies

AG≫)

Щука

А.А. Щука А.А. — Наноэлектроника. Монография. - М.: Физматкнига, 2007.

- 465 с.

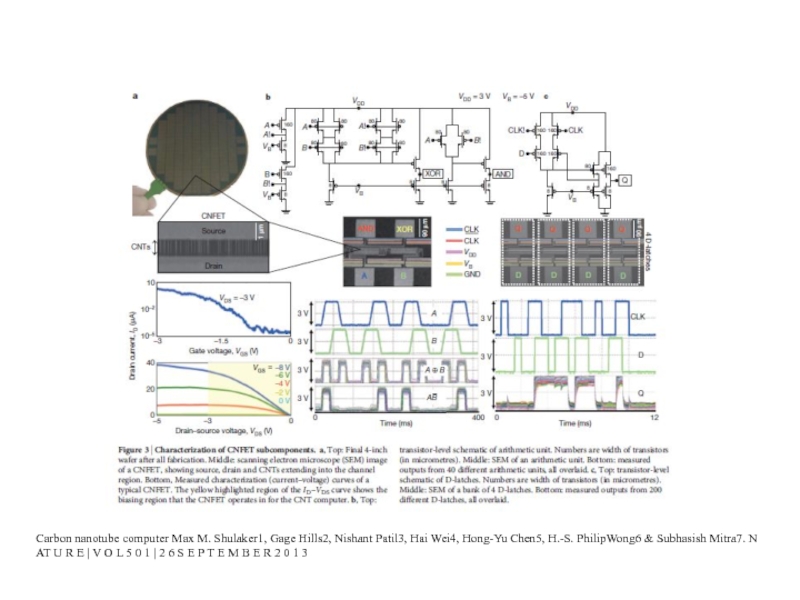

Слайд 37Carbon nanotube computer Max M. Shulaker1, Gage Hills2, Nishant Patil3,

Hai Wei4, Hong-Yu Chen5, H.-S. PhilipWong6 & Subhasish Mitra7. N

AT U R E | V O L 5 0 1 | 2 6 S E P T E M B E R 2 0 1 3

Слайд 38Классификация методов получения топологии интегральных микро- и наносхем, а также

микро- и наноприборов

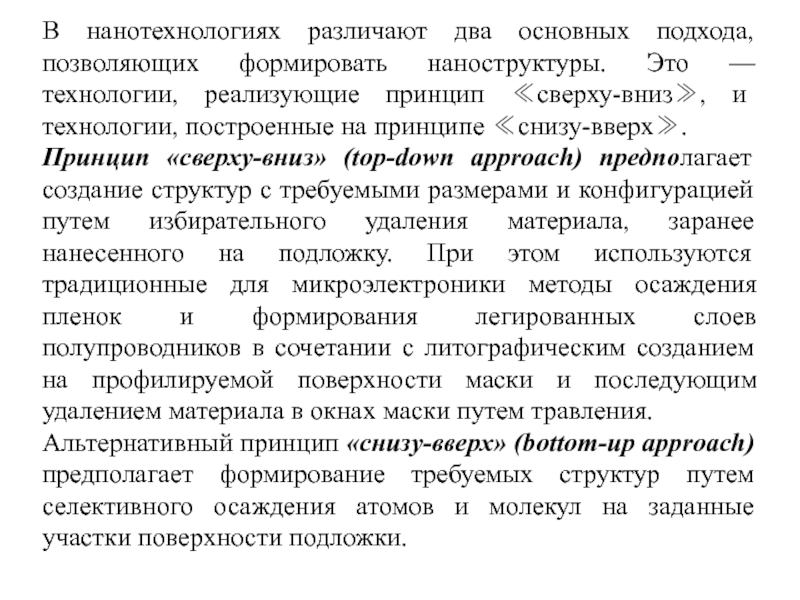

Слайд 39В нанотехнологиях различают два основных подхода, позволяющих формировать наноструктуры. Это

— технологии, реализующие принцип ≪сверху-вниз≫, и технологии, построенные на принципе

≪снизу-вверх≫.

Принцип «сверху-вниз» (top-down approach) предполагает создание структур с требуемыми размерами и конфигурацией путем избирательного удаления материала, заранее нанесенного на подложку. При этом используются традиционные для микроэлектроники методы осаждения пленок и формирования легированных слоев полупроводников в сочетании с литографическим созданием на профилируемой поверхности маски и последующим удалением материала в окнах маски путем травления.

Альтернативный принцип «снизу-вверх» (bottom-up approach) предполагает формирование требуемых структур путем селективного осаждения атомов и молекул на заданные участки поверхности подложки.

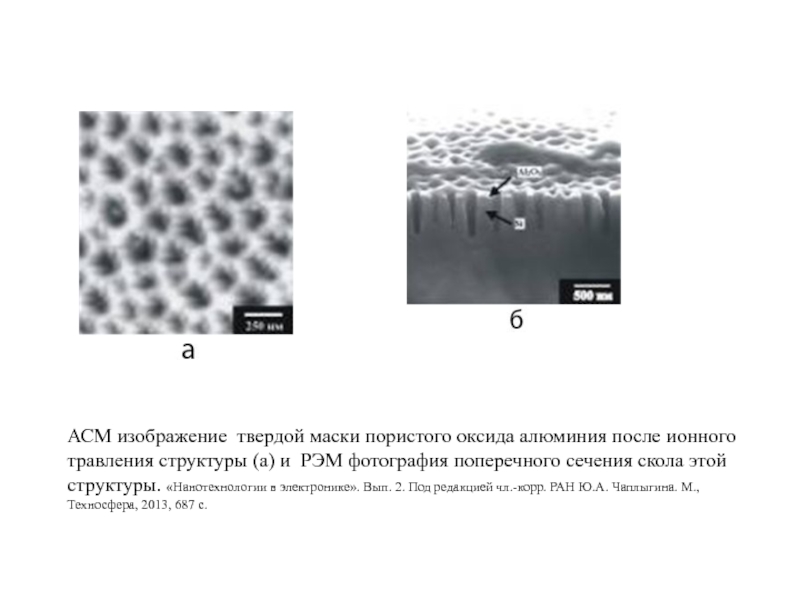

Слайд 40АСМ изображение твердой маски пористого оксида алюминия после ионного травления

структуры (а) и РЭМ фотография поперечного сечения скола этой структуры.

«Нанотехнологии в электронике». Вып. 2. Под редакцией чл.-корр. РАН Ю.А. Чаплыгина. М., Техносфера, 2013, 687 с.

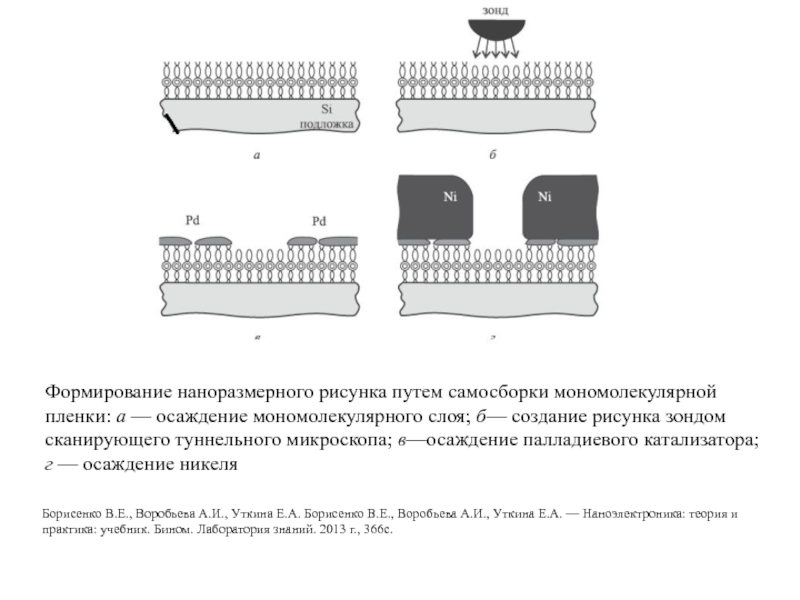

Слайд 41Формирование наноразмерного рисунка путем самосборки мономолекулярной пленки: а — осаждение

мономолекулярного слоя; б— создание рисунка зондом сканирующего туннельного микроскопа; в—осаждение

палладиевого катализатора; г — осаждение никеля

Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А. — Наноэлектроника: теория и практика: учебник. Бином. Лаборатория знаний. 2013 г., 366с.

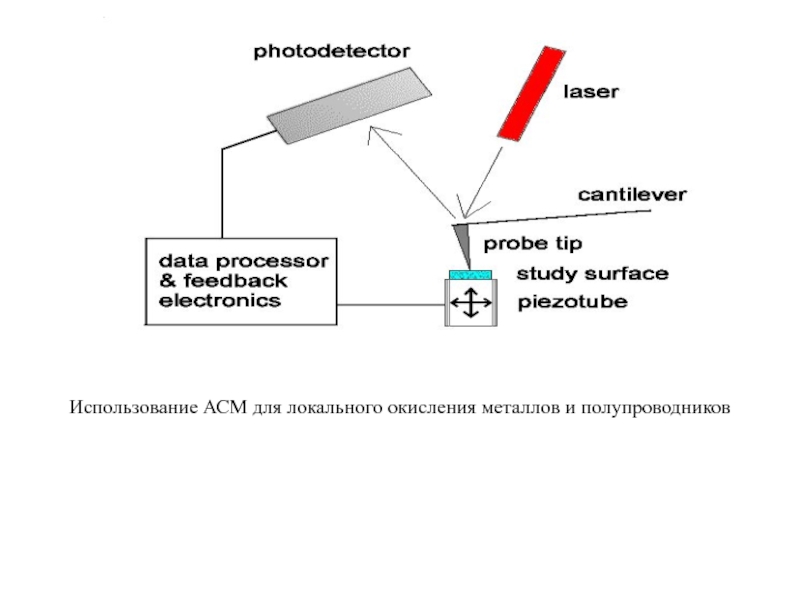

Слайд 42Использование АСМ для локального окисления металлов и полупроводников

Слайд 43Вертикально ориентированные углеродные нанотрубки, полученные химическим осаждением из газовой фазы.

Nanolithography and pattering techniques in microelectronics /edited by D.G. Bucknall,

Woodhead Publishing Ltd., Cambridge, England, 2005. – 424 pp.

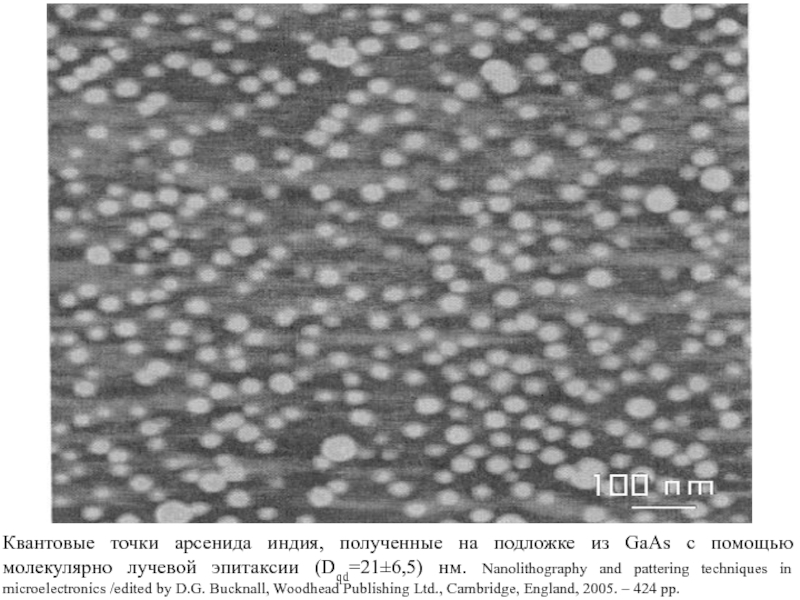

Слайд 44Квантовые точки арсенида индия, полученные на подложке из GaAs с

помощью молекулярно лучевой эпитаксии (Dqd=21±6,5) нм. Nanolithography and pattering techniques

in microelectronics /edited by D.G. Bucknall, Woodhead Publishing Ltd., Cambridge, England, 2005. – 424 pp.

Слайд 45Фотография на просвечивающем электронном микроскопе массива нанокристаллов серебра, образованного в

процессе самосборки

ОБРАЗОВАТЕЛЬНЫЙ МОДУЛЬ «ТЕХНОЛОГИЯ НАНОЛИТОГРАФИИ» ОБРАЗОВАТЕЛЬНЫЙ БЛОК БАЗОВЫХ ЗНАНИЙ.

Лекции. д.т.н. Киреев В.Ю., М., МИЭТ

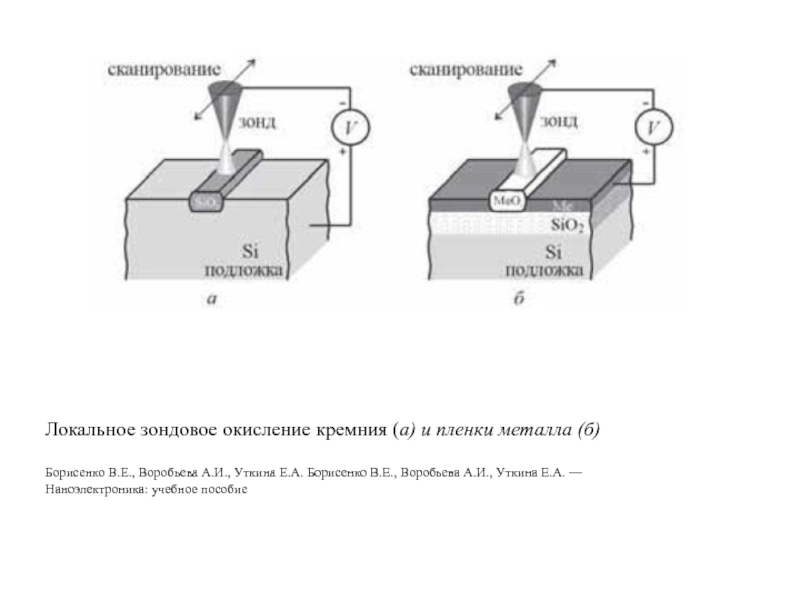

Слайд 46Локальное зондовое окисление кремния (а) и пленки металла (б)

Борисенко В.Е.,

Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А.

—

Наноэлектроника: учебное пособие

Слайд 48

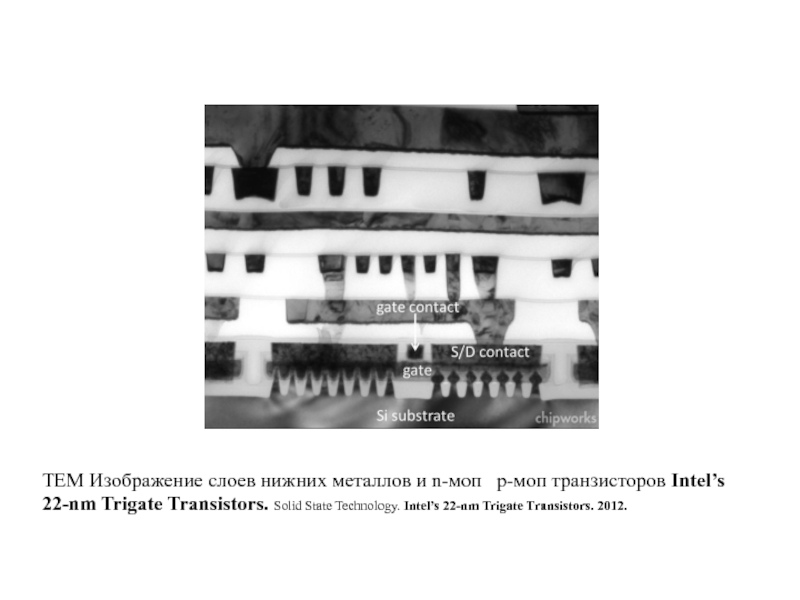

TEM Изображение слоев нижних металлов и n-моп p-моп транзисторов

Intel’s 22-nm Trigate Transistors. Solid State Technology. Intel’s 22-nm Trigate

Transistors. 2012.

Слайд 49Вопросы промежуточного контроля:

Дайте определение наноэлектроники.

Сформулируйте Мура.

Назовите основные сегменты электронной

отрасли.

Какой из сегментов электронной отрасли занимает основную долю на рынке?

Какая

основная причина перехода электроника в наноразмерную область?

Что такое наноразмерная структура

Что такое низкоразмерная структура

Что такое квантовая пленка, квантовый шнур, квантовая точка

Что такое баллистический транспорт

Что такое туннелирование

Что такое кулоновская блокада

В чем основное достоинство одноэлектронных приборов

Что такое квантовое ограничение

Что такое принцип формирования наноструктур «сверху – вниз»

Что такое принцип формирования наноструктур «снизу – вверх»

Слайд 50Планарная технология

Основным технологическим методом создания современных интегральных микросхем остается разработанная

в конце 50-х годов двадцатого столетия

планарная технология.

Практически все современные процессы создания широко используемых интегральных микросхем различного назначения основываются на технологических операциях планарной технологии.

1959

Год появления –

Слайд 51Планарная технология

(от англ. planar, от лат. planus – плоский, ровный),

– форма организации технологического процесса при изготовлении ИМС, при которой

все ее элементы и соединения создаются через плоскость на верхней поверхности подложки без затрагивания ее боковых и жижней стороны.

Несколько технологических операций при изготовлении ИМС служат для соединения отдельных элементов в схему и присоединения их к специальным контактным площадкам. Поэтому необходимо, чтобы выводы всех элементов и контактные площадки находились в одной плоскости, что и обеспечивает планарная технология.

Слайд 52 Планарная технология

позволяет реализовать групповой процесс изготовления элементов интегральных схем

на полупроводниковой подложке

одновременно и

на одном кристалле

Слайд 53Основные операции планарной технологии

легирование полупроводника (диффузия примесей в полупроводник

и ионная имплантация)

окисление кремния

травление (жидкостное химическое травление –

ЖХТ и плазмохимическое травление – ПХТ

фотолитография

высокотемпературные обработки полупроводниковых структур (отжиги в различных средах)

осаждения тонких пленок различных материалов (слоев проводников и диэлектриков).

Слайд 54Легирование атомами примеси

Сущность процессов легирования полупроводника заключается в создании на

поверхности полупроводника источника примеси и проведении отжига, при котором примесь

проникает с поверхности в глубь материала за счет теплового движения атомов.

Слайд 55Окисление кремния

В результате процесса окисления происходит взаимодействие поверхностного слоя кремния

с кислородом и создание на поверхности полупроводника пленки оксида SiO2

или окисла.

Слайд 56Травление

Травление – это технологическая операция удаления обрабатываемого материала в процессе

химического взаимодействия и растворения в подходящем травителе. Локальное травление –

это удаление материала с определенной, заранее заданной части поверхности, соприкасающейся с травителем. Другие участки, на которые не должно распространяться действие травления, должны быть защищены инертными к действию травителя материалами.

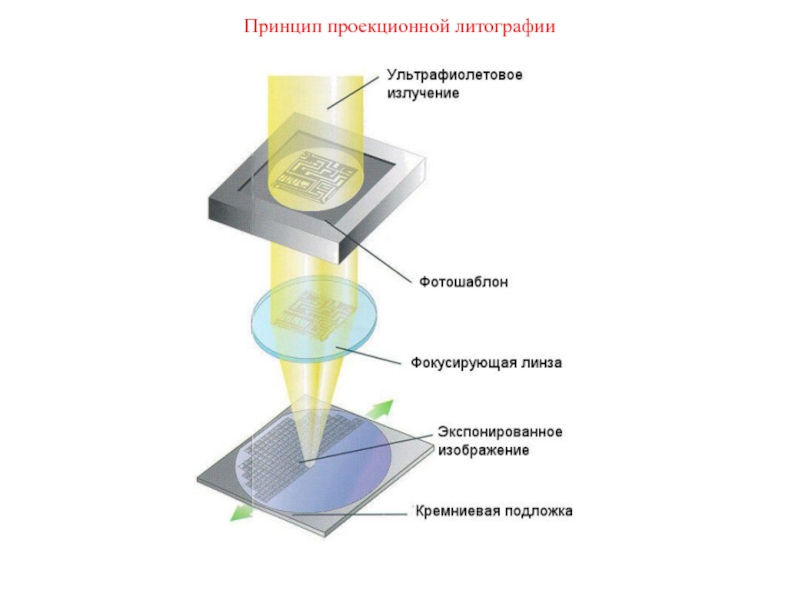

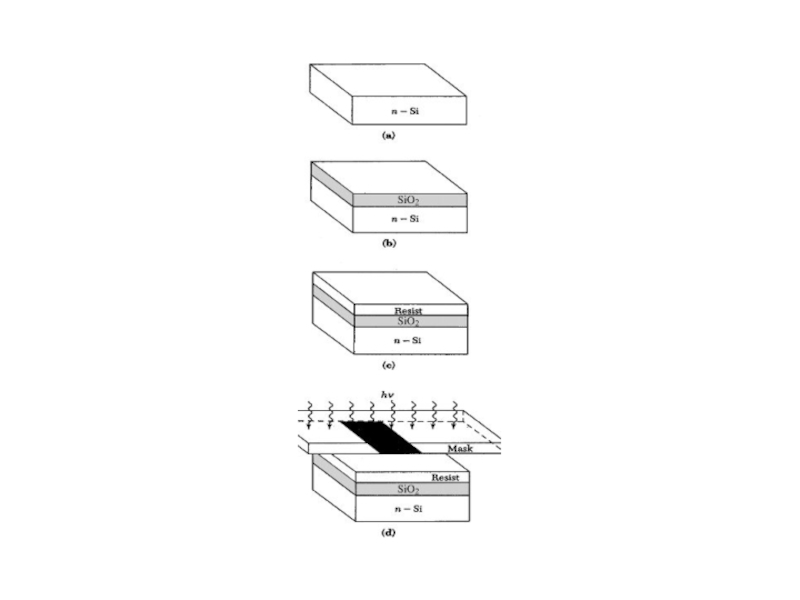

Слайд 57Локальное травление и фотолитография

Метод фотолитографии, использует в качестве защитного слоя

стойкое к действию травителей вещество, меняющее свою растворимость под действием

света (химически стойкое органическое полимерное соединение - фоторезист).

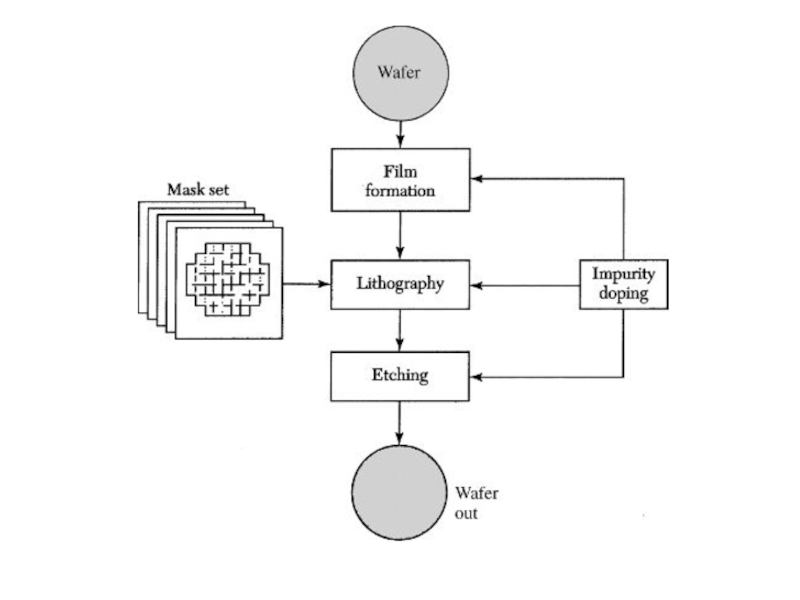

Слайд 58Технологический маршрут

Изготовление каждого полупроводникового прибора (соответственно, интегральной микросхемы) идет

по строго определенной последовательности. Такая последовательность называется технологическим маршрутом изготовления.

Основные технологические маршруты создания кремниевых ИС:

Биполярные

КМОП

БиКМОП

Слайд 59Сопроводительный лист

На предприятиях микроэлектроники данная последовательность отражена в маршрутной карте

(сопроводительном листе) соответствующей партии пластин, на которых будут изготовлены конкретные

полупроводниковые приборы. В сопроводительном листе отражаются режимы технологических операций и результаты контрольных измерений различных физических и электрических параметров получаемых слоёв и структур (после соответствующей операции)

Слайд 60Принципы планарной технологии

взаимосвязь конструкции интегральных микросхем и технологии их

изготовления

совместимость элементов (на одном кристалле)

локальность технологических обработок

послойное формирование элементов микросхем

Слайд 61Взаимосвязь конструкции интегральных микросхем и технологии их изготовления

Проектирование конструкции интегральной

микросхемы связано с технологией ее создания.

Необходимо учитывать влияние паразитных связей

между элементами.

Необходимость учёта технологического разброса при выборе значений параметров полупроводниковых приборов

Слайд 62Конструктивно-технологические ограничения при разработке и изготовлении интегральных микросхем

Наряду с конструктивными,

эксплутационными и электрическими параметрами для интегральных микросхем вводятся данные, отражающие

ограничения технологии. Они определяют оптимальную конструкцию.

Для производства микросхем понятия «проектирование» и «технология» тесно взаимосвязаны, при этом технологии принадлежит определяющая роль.

Слайд 63Совместимость элементов интегральных микросхем

Единый групповой метод изготовления.

Основной элемент – самый

сложный элемент ИС - транзистор.

На основе транзистора изготавливаются другие элементы

ИС.

Несовместимость элементов – не всегда «препятствие» для создания ИС, но значительное повышение себестоимости

Слайд 64Локальность технологических обработок

Во время технологических операций обрабатывается не вся

поверхность пластины.

Методы локальных технологий:

масочная технология: трафареты и

шаблоны (фотошаблоны);

безмасочные технологии (электронный луч, ионный луч, лазер) – по программе с ЭВМ.

Слайд 65Послойное формирование элементов микросхем

Локальные обработки различных участков пластины выполняют

многократно.

Фотолитографический цикл: 2 типа

Слайд 66

Послойное формирование элементов микросхем

Фотолитографический цикл: 1 тип

ЛЕГИРОВАНИЕ

Окисление

Фотолитография

Травление

через ФРМ

Удаление ФР

Легирование

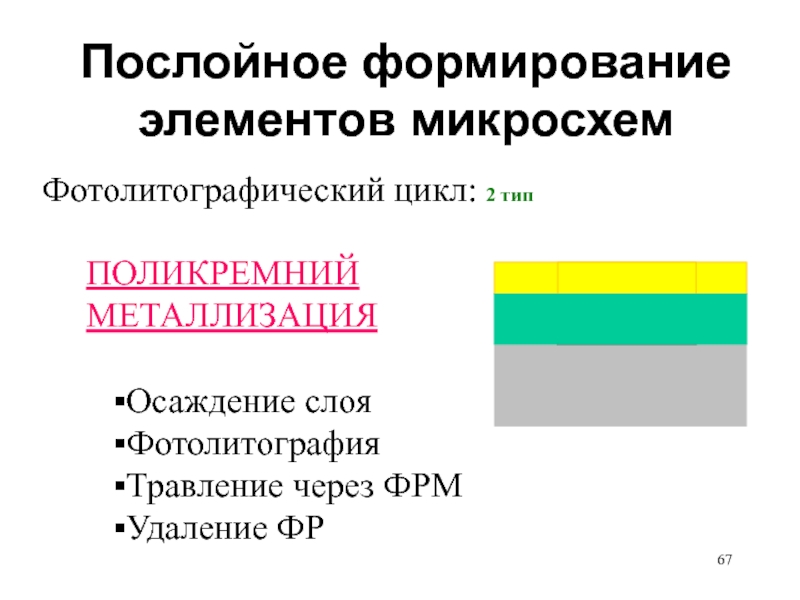

Слайд 67

Послойное формирование элементов микросхем

Фотолитографический цикл: 2 тип

ПОЛИКРЕМНИЙ МЕТАЛЛИЗАЦИЯ

Осаждение

слоя

Фотолитография

Травление через ФРМ

Удаление ФР

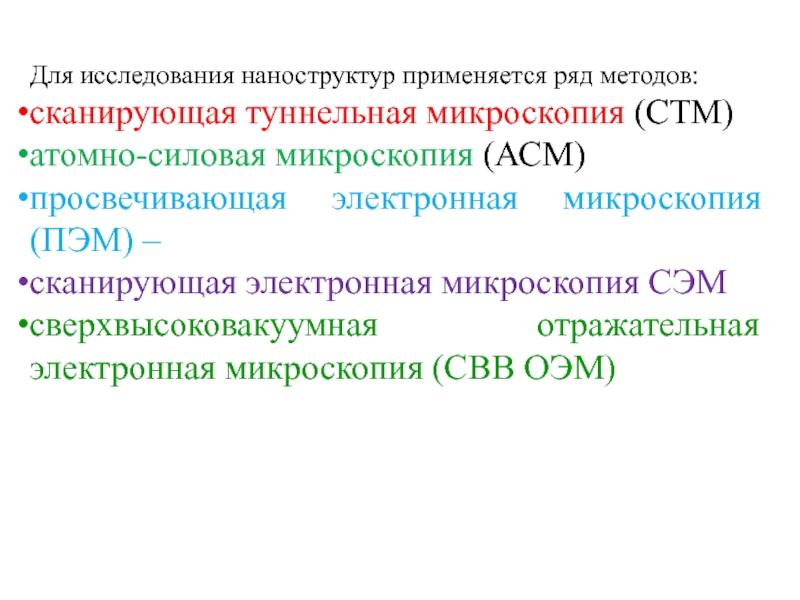

Слайд 72Для исследования наноструктур применяется ряд методов:

сканирующая туннельная микроскопия (СТМ)

атомно-силовая

микроскопия (АСМ)

просвечивающая электронная микроскопия (ПЭМ) –

сканирующая электронная микроскопия СЭМ

сверхвысоковакуумная

отражательная электронная микроскопия (СВВ ОЭМ)

Слайд 73

Сканирование обычно проводят в двух режимах: постоянного тока или постоянного

уровня кантилевера (сенсорное устройство, закрепленно на консоли). В первом случае

предполагается, что постоянный ток соответствует постоянному зазору между поверхностью и кантилевером. При сканировании снимается положение кантилевера, что фактически соответствует рельефу поверхности. Во втором - снимаются токовые зависимости.

Сканирующая туннельная микроскопия (СТМ)

Слайд 74

Общая энергия взаимодействия атомов приближённо описывается формулой Леннарда-Джонса:

где

r— расстояние между

частицами,

D— энергия связи,

a— длина связи.

В зависимости от расстояний от иглы

до образца возможны следующие режимы работы атомно-силового микроскопа:

контактный режим (contact mode);

бесконтактный режим (non-contact mode);

полуконтактный режим (tapping mode).

Топографические изображения в атомно-силовом микроскопе обычно получают в одном из двух режимов:

режим постоянной высоты

режим постоянной силы.

Разрешающая способность данного метода составляет примерно 0,1-1 нм по горизонтали и 0,01 нм по вертикали

Атомно-силовая микроскопия

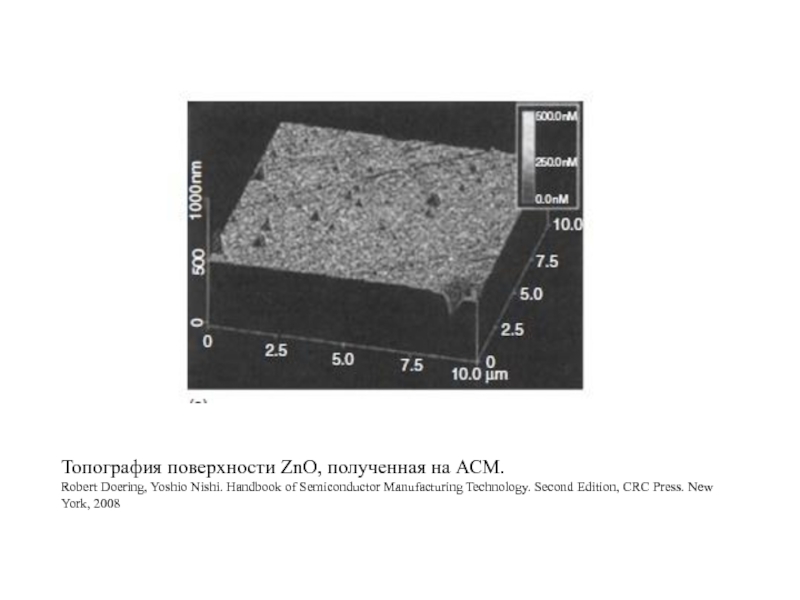

Слайд 75Топография поверхности ZnO, полученная на АСМ.

Robert Doering, Yoshio Nishi.

Handbook of Semiconductor Manufacturing Technology. Second Edition, CRC Press. New

York, 2008

Слайд 76

Просвечивающий электронный микроскоп

Метод просвечивающей электронной микроскопии позволяет изучать внутреннюю

структуру исследуемых материалов:

определять тип и параметры кристаллической решетки матрицы и

фаз;

определять ориентационные соотношения между фазой и матрицей;

изучать строение границ зерен;

определять кристаллографическую ориентацию отдельных зерен, субзерен;

определять углы разориентировки между зернами, субзернами;

определять плоскости залегания дефектов кристаллического строения;

изучать плотность и распределение дислокаций в материалах изделий;

изучать процессы структурных и фазовых превращений;

изучать влияние на структуру конструкционных материалов технологических факторов.

Слайд 77При проведении исследований на СЭМ (часто также встречается название «растровый

электроный микроскоп» или сокращенно РЭМ)

Тонкий электронный зонд (электронный пучок

средних энергий (200 эВ – 50 кэВ) направляется на анализируемый образец.

В результате взаимодействия между электронным зондом и образцом генерируются низкоэнергетичные вторичные электроны, которые собираются детектором вторичных электронов. Интенсивность электрического сигнала детектора зависит как от природы образца (в меньшей степени), так и от топографии (в большей степени) образца в области взаимодействия. Таким образом, сканируя электронным пучком поверхность объекта возможно получить карту рельефа проанализированной зоны.

Электроны зонда (пучка) взаимодействуют с материалом образца и генерируют различные типы сигналов: вторичные электроны, обратноотраженные электроны, Оже-электроны, рентгеновское излучение, световое излучение (катодолюминесценция) и т.д. Эти сигналы являются носителями информации о топографии и материале образца.

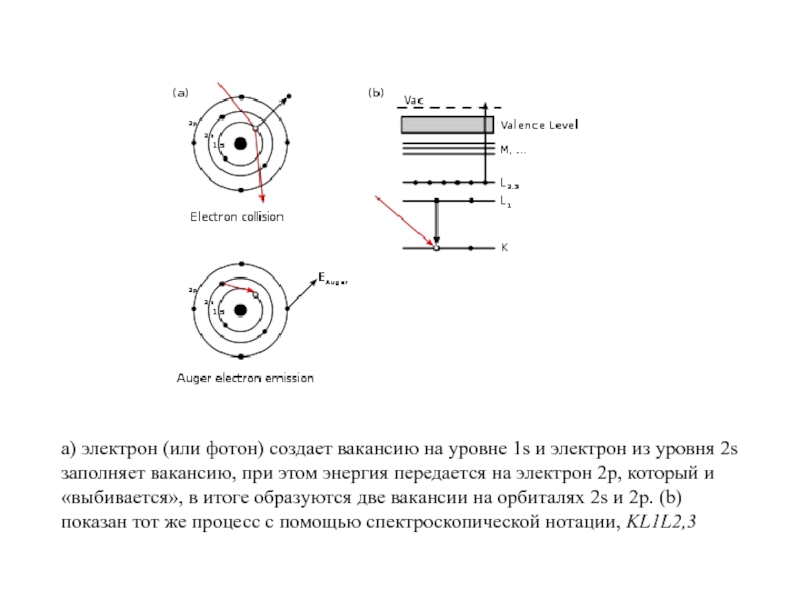

Слайд 78a) электрон (или фотон) создает вакансию на уровне 1s и

электрон из уровня 2s заполняет вакансию, при этом энергия передается

на электрон 2p, который и «выбивается», в итоге образуются две вакансии на орбиталях 2s и 2p. (b) показан тот же процесс с помощью спектроскопической нотации, KL1L2,3

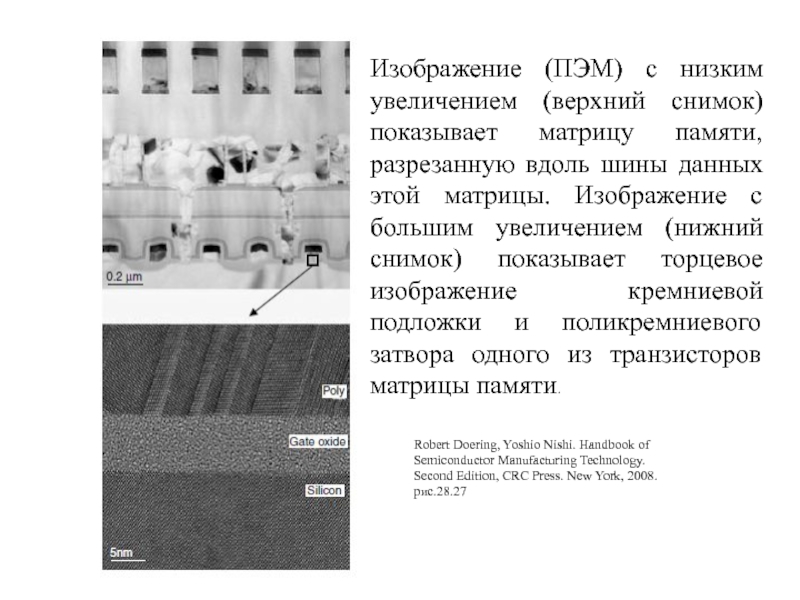

Слайд 79Robert Doering, Yoshio Nishi. Handbook of Semiconductor Manufacturing Technology. Second

Edition, CRC Press. New York, 2008. рис.28.27

Изображение (ПЭМ) с низким

увеличением (верхний снимок) показывает матрицу памяти, разрезанную вдоль шины данных этой матрицы. Изображение с большим увеличением (нижний снимок) показывает торцевое изображение кремниевой подложки и поликремниевого затвора одного из транзисторов матрицы памяти.