Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Учебная дисциплина Схемотехника дискретных устройств Московский Государственный

Содержание

- 1. Учебная дисциплина Схемотехника дискретных устройств Московский Государственный

- 2. Дешифраторы Дешифратором называется комбинационная схема с несколькими

- 3. ДешифраторыЧисло входов и выходов в так называемом

- 4. Дешифраторы На выходах дешифратора вырабатываются значения булевых

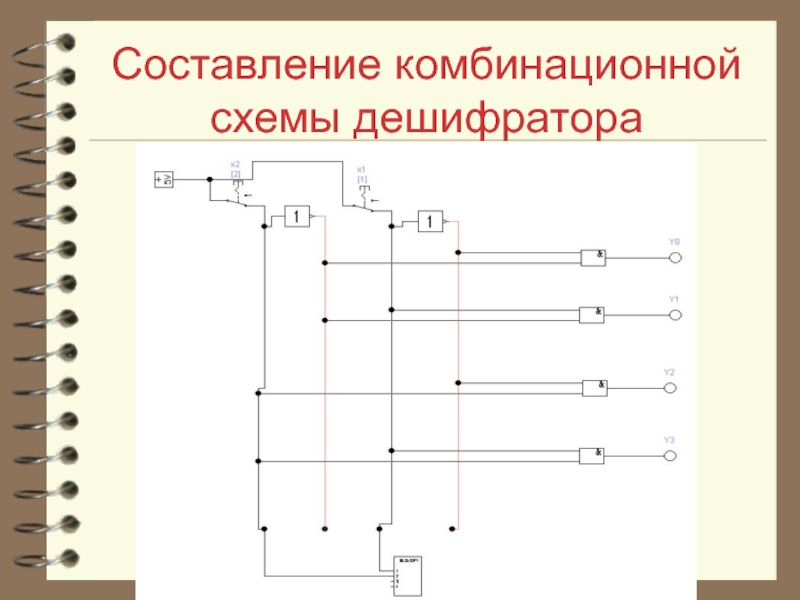

- 5. Составление комбинационной схемы дешифратора

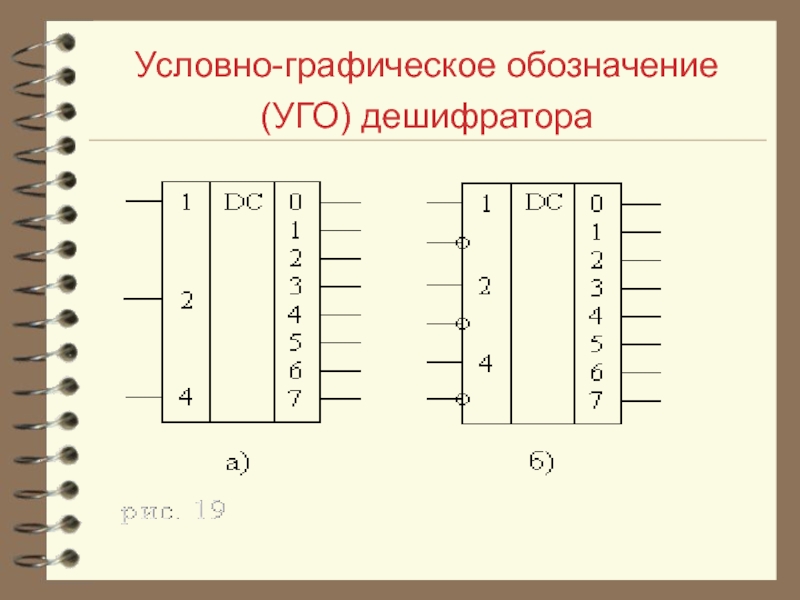

- 6. Условно-графическое обозначение (УГО) дешифратора

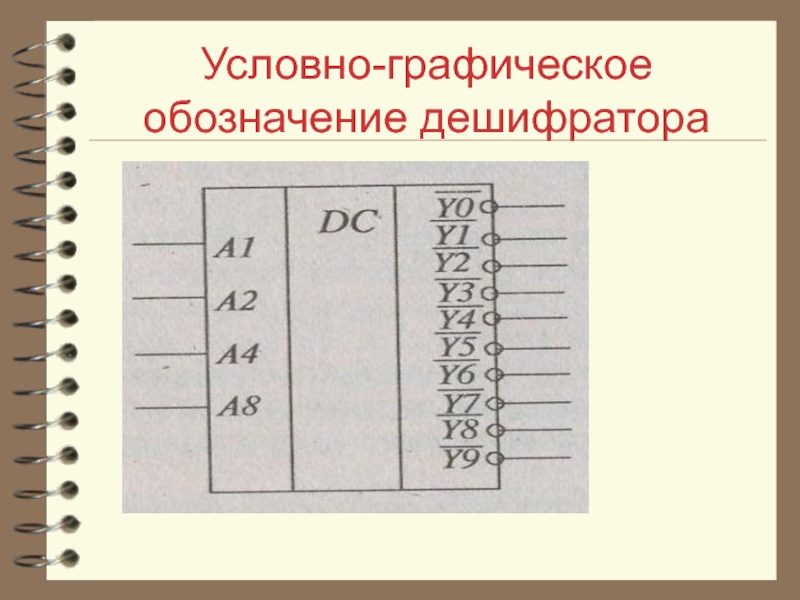

- 7. Условно-графическое обозначение дешифратора

- 8. Вход разрешения в схеме дешифратора В схеме

- 9. Каскадное включение дешифраторов Из логических элементов,

- 10. Матричная схема включения дешифраторов Другим способом реализации

- 11. Матричная схема включения дешифраторов В матричной схеме

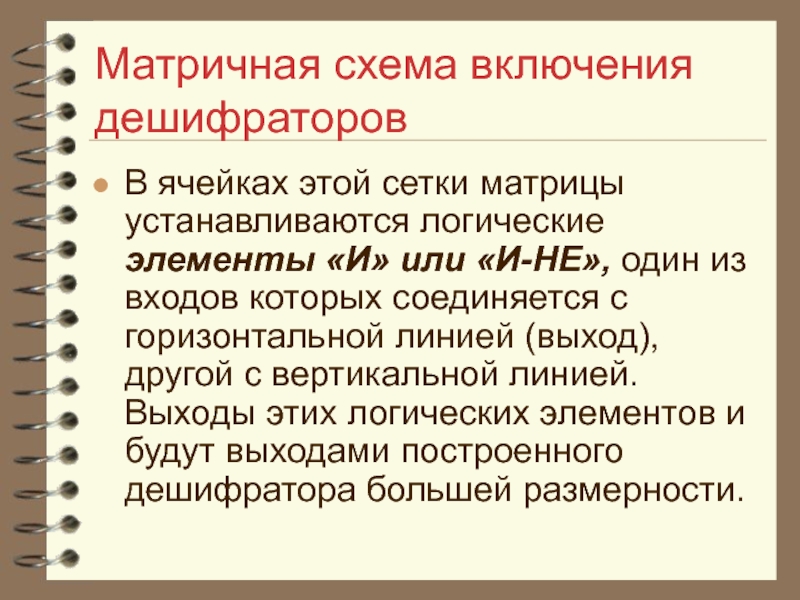

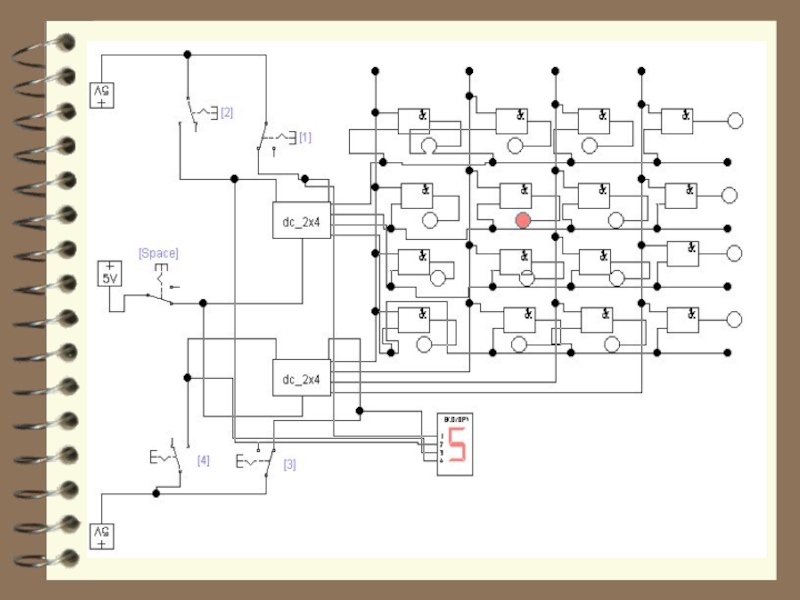

- 12. Матричная схема включения дешифраторовВ ячейках этой сетки

- 13. Слайд 13

- 14. Шифраторы Шифратор — это комбинационное

- 15. Шифраторы Шифратор иногда называют «кодером» (от

- 16. Типы шифраторов

- 17. Типы шифраторов Так, для преобразования

- 18. Синтез схемы шифратора Рассмотрим пример

- 19. Таблица соответствия входов и выходов шифратора

- 20. Синтез схемы шифратора Используя данную таблицу соответствия,

- 21. Схема шифратора 10х4

- 22. Мультиплексоры Мультиплексоры осуществляют подключение одного

- 23. Структура входов и выхода мультиплексора В

- 24. Передача входного сигнала на выход Двоичный

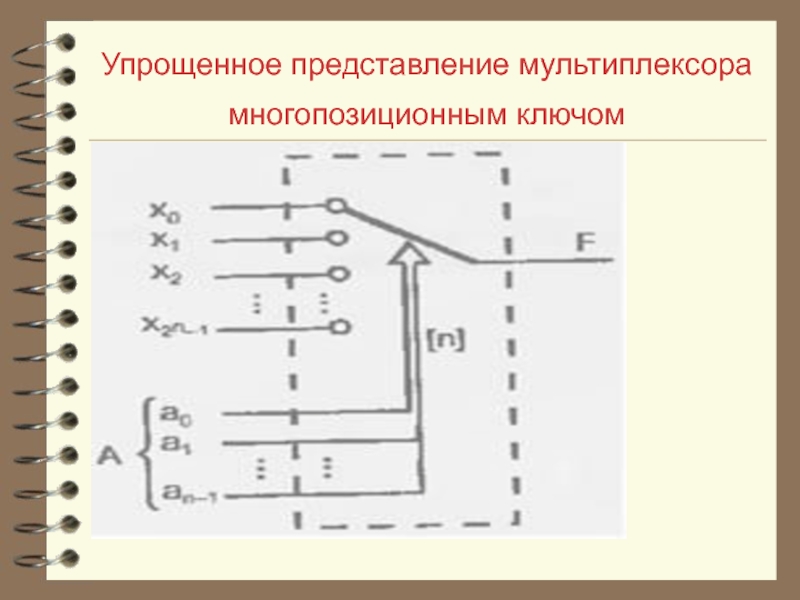

- 25. Упрощенное представление мультиплексора многопозиционным ключом

- 26. Таблица истинности мультиплексора

- 27. Выражение для сигнала на выходе мультиплексора Y=(E*!A1*!A0*X0)+(E*!A1*A0*X1)+

- 28. Схема мультиплексора на элементах «И» и «ИЛИ».

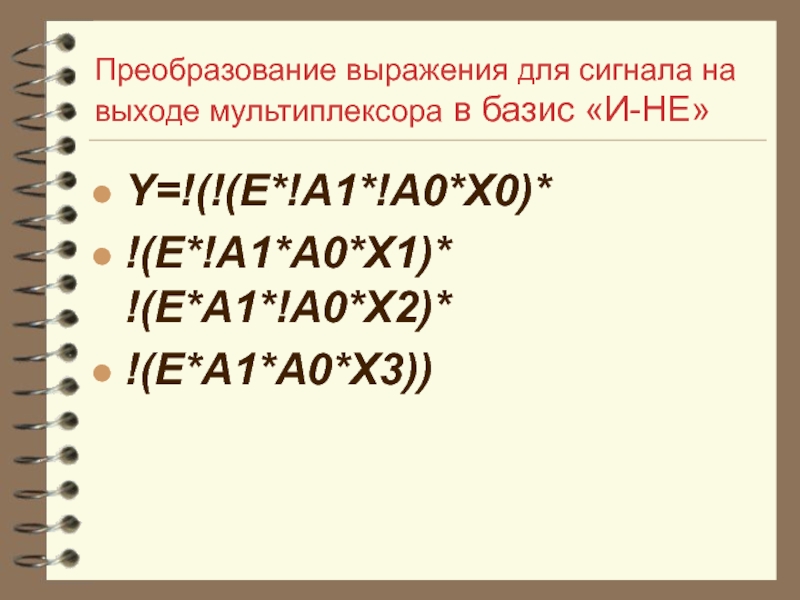

- 29. Преобразование выражения для сигнала на выходе мультиплексора в базис «И-НЕ»Y=!(!(E*!A1*!A0*X0)*!(E*!A1*A0*X1)* !(E*A1*!A0*X2)*!(E*A1*A0*X3))

- 30. Схема мультиплексора на элементах «И-НЕ»

- 31. Каскадное включение мультиплексоров При недостаточной размерности

- 32. Каскадное включение мультиплексоров Пространство адресного

- 33. Каскадное включение мультиплексоров Выходная ступень организуется

- 34. Каскадное включение мультиплексоров На мультиплексор выходной ступени подаются разряды старшей адресной группы.

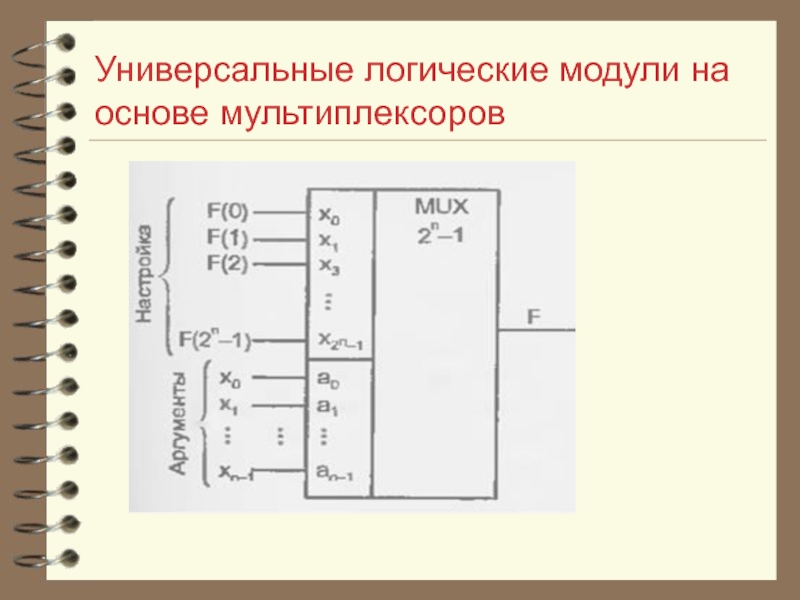

- 35. Универсальные логические модули на основе мультиплексоров

- 36. Универсальные логические модули на основе мультиплексоров

- 37. Универсальные логические модули на основе мультиплексоров

- 38. Универсальные логические модули на основе мультиплексоровПоясним на примере замены синтеза комбинационной схемы применением мультиплексора.

- 39. Табличное задание булевой функции

- 40. Универсальные логические модули на основе мультиплексоров

- 41. Универсальные логические модули на основе мультиплексоров

- 42. Демультиплексоры Демультиплексорами называются устройства, которые

- 43. Демультиплексоры Существенным отличием от мультиплексора

- 44. Принципиальная схема демультиплексора, управляемого двоичным кодом.

- 45. Идентичность демультиплексора с дешифратором с входом разрешения

- 46. Условно графическое обозначение демультиплексора с четырьмя выходами

- 47. Скачать презентанцию

Дешифраторы Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов (так называемый унарный код). Если на входы дешифратора подаются двоичные

Слайды и текст этой презентации

Слайд 2Дешифраторы

Дешифратором называется комбинационная схема с несколькими входами и выходами,

преобразующая код, подаваемый на входы, в сигнал на одном из

выходов (так называемый унарный код).Если на входы дешифратора подаются двоичные переменные, то на одном из выходов дешифратора вырабатывается сигнал 1, а на остальных выходах сохраняются нули.

Слайд 3Дешифраторы

Число входов и выходов в так называемом полном дешифраторе связано

соотношением

m=2n, где n — число входов, а m —

число выходов.Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

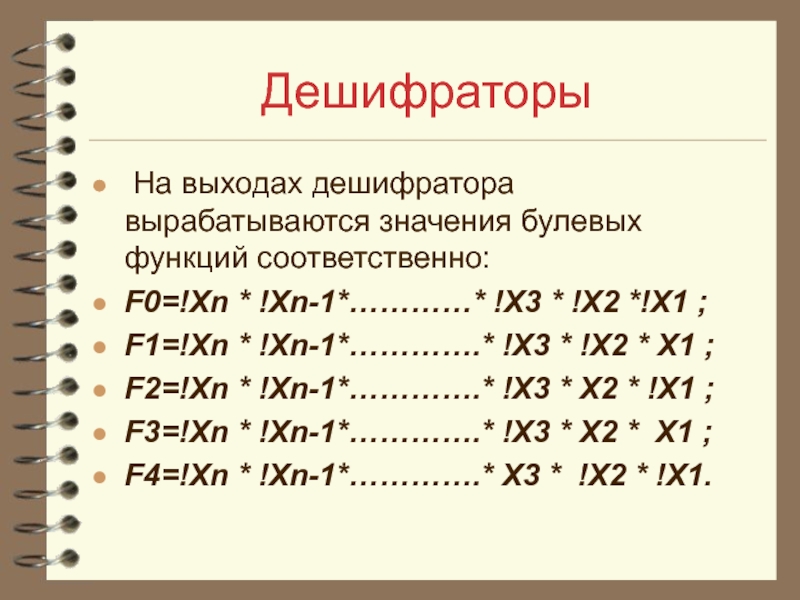

Слайд 4Дешифраторы

На выходах дешифратора вырабатываются значения булевых функций соответственно:

F0=!Xn *

!Xn-1*…………* !X3 * !X2 *!X1 ;

F1=!Xn * !Xn-1*………….* !X3 *

!X2 * X1 ;F2=!Xn * !Xn-1*………….* !X3 * X2 * !X1 ;

F3=!Xn * !Xn-1*………….* !X3 * X2 * X1 ;

F4=!Xn * !Xn-1*………….* X3 * !X2 * !X1.

Слайд 8Вход разрешения в схеме дешифратора

В схеме дешифратора может быть

организован дополнительный вход для сигнала разрешения Е. При Е=0 дешифратор

не работает даже при наличии кода на его входах, а при Е=1 работает как обычный линейный дешифратор. Такого вида схемы выпускаются в составе комплексов интегральных логических элементов.Слайд 9Каскадное включение дешифраторов

Из логических элементов, являющихся дешифраторами, можно

строить дешифраторы на большее число входов, при этом, как правило,

используются дешифраторы с дополнительными входами сигнала разрешения. Каскадное включение таких схем позволяет легко наращивать число дешифрируемых переменных.Слайд 10Матричная схема включения дешифраторов

Другим способом реализации дешифратора на количество

выходов, превышающее количество выходов в имеющихся микросхемах дешифраторов это составление

матричной схемы построения составного дешифратора.Слайд 11Матричная схема включения дешифраторов

В матричной схеме используются два идентичных

по размерности дешифратора, выходы одного образуют горизонтальные линии, выходы другого

- вертикальные линии. Эти линии составляют матрицу, но не соединяются между собой.Слайд 12Матричная схема включения дешифраторов

В ячейках этой сетки матрицы устанавливаются логические

элементы «И» или «И-НЕ», один из входов которых соединяется с

горизонтальной линией (выход), другой с вертикальной линией. Выходы этих логических элементов и будут выходами построенного дешифратора большей размерности.Слайд 14Шифраторы

Шифратор — это комбинационное устройство, преобразующее унарный

код (например десятичные числа) в двоичную систему счисления, причем каждому

входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.Слайд 15Шифраторы

Шифратор иногда называют «кодером» (от англ. coder) и

используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного

пульта управления, в двоичные числа.Слайд 16 Типы шифраторов

Если количество

входов настолько велико, что в шифраторе используются все возможные комбинации

сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением n = 2m, где n — число входов, m — число выходов.Слайд 17Типы шифраторов

Так, для преобразования кода кнопочного пульта

в четырехразрядное двоичное число достаточно использовать лишь 10 входов, в

то время как полное число возможных входов будет равно 16 , поэтому шифратор 10x4 (из 10 в 4) будет неполным.Слайд 18Синтез схемы шифратора

Рассмотрим пример построения шифратора для

преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9)

в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подается только на один вход.Слайд 20Синтез схемы шифратора

Используя данную таблицу соответствия, запишем логические выражения,

включая в логическую сумму те входные переменные, которые соответствуют единице

некоторой выходной переменной. Так, на выходе Y0, будет логическая «1»тогда, когда логическая «1» будет или на входе K1, или K3, или K5, или K7, или K9, т. е.:Y0= K1 + K3 + K5 + K7 + K9.

Y1 = K2 + K3 + K6 + K7.

Y2 = K4 + K5 + K6 + K7,

Y3 = K8+ K9.