Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Высокопроизводительные системы

Содержание

- 1. Высокопроизводительные системы

- 2. ПланТипы высокопроизводительных системОднопроцессорные системыSMPВекторные процессорыМассивно-параллельные системыNUMA системыКластерыМетакомпьютерыОсновные характеристики

- 3. Литератураhttp://www.intel.comhttp://www.parallel.ruКогерентность кэша http://www.update.uu.se/~gus/Misc/Compositions/cache_coherence.html

- 4. Высокопроизводительные системыОсновная цель – получение высокой скорости

- 5. Пути повышения производительностиИспользование новых физических эффектов Увеличение

- 6. Типы высокопроизводительных системОднопроцессорные системы (UP)Симметричные многопроцессорные системы (SMP)Векторно-конвейерные системы (PVP)NUMA системыВычислительные кластерыМетакомпьютры

- 7. Однопроцессорные ЭВМОдин процессорОбщая шинаПараллелизм на уровне инструкций за счет особенностей устройства процессора

- 8. Скалярная обработкаОдин поток инструкцийОдно функциональное устройствоВсе инструкции

- 9. Кэширование оперативной памятиКэш – память с быстрым

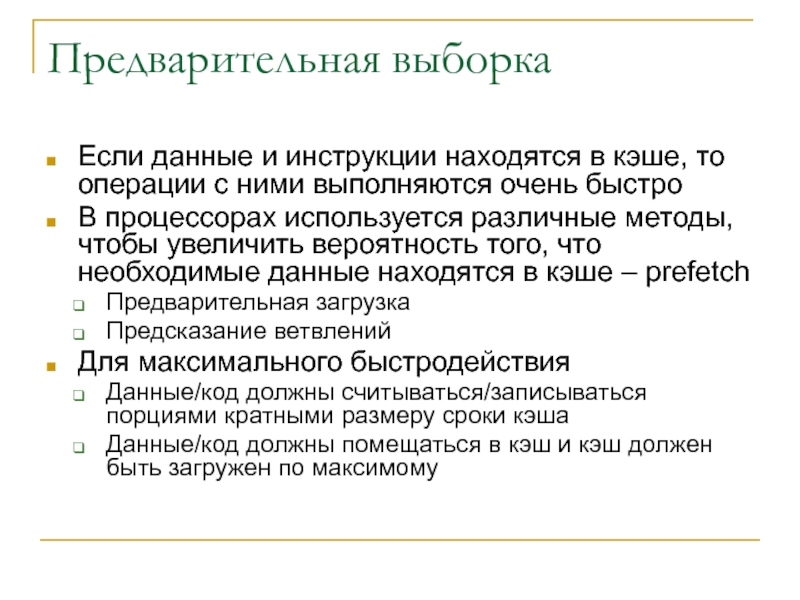

- 10. Предварительная выборкаЕсли данные и инструкции находятся в

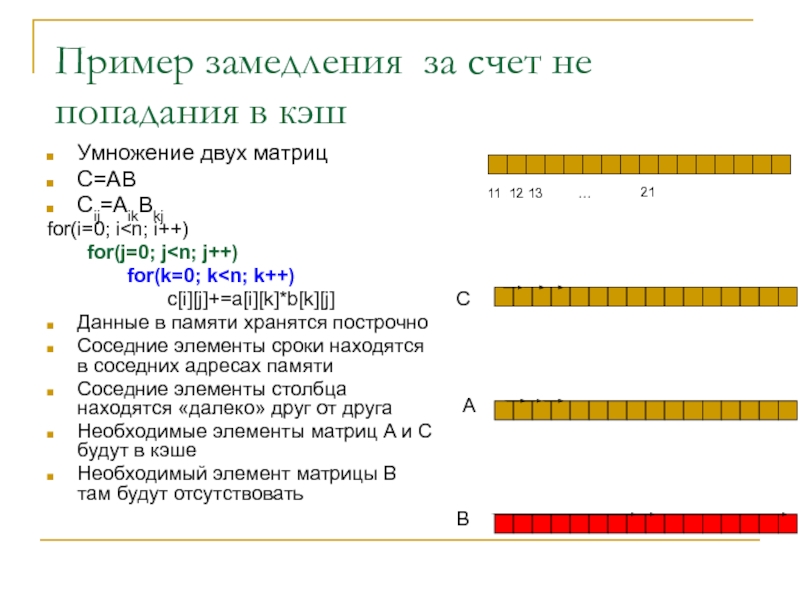

- 11. Пример замедления за счет не попадания в кэшУмножение двух матрицC=ABCij=AikBkjfor(i=0; i

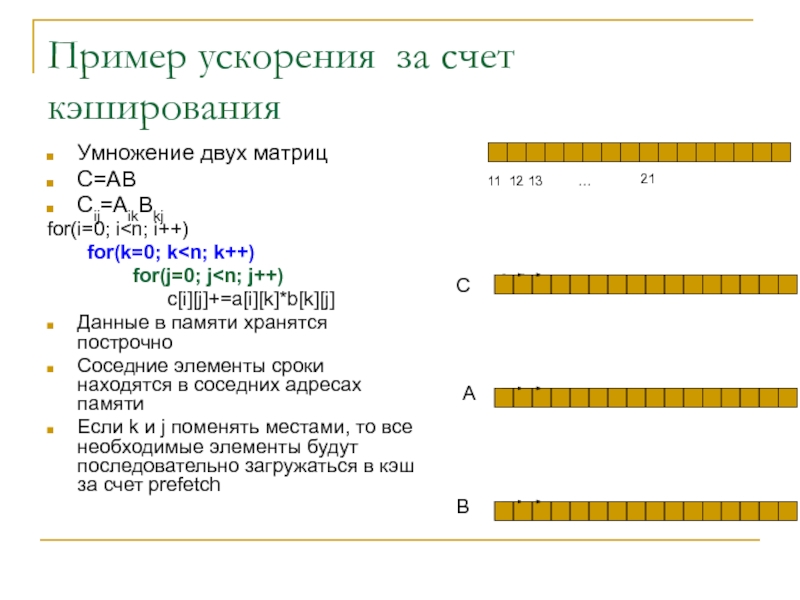

- 12. Пример ускорения за счет кэшированияУмножение двух матрицC=ABCij=AikBkjfor(i=0; i

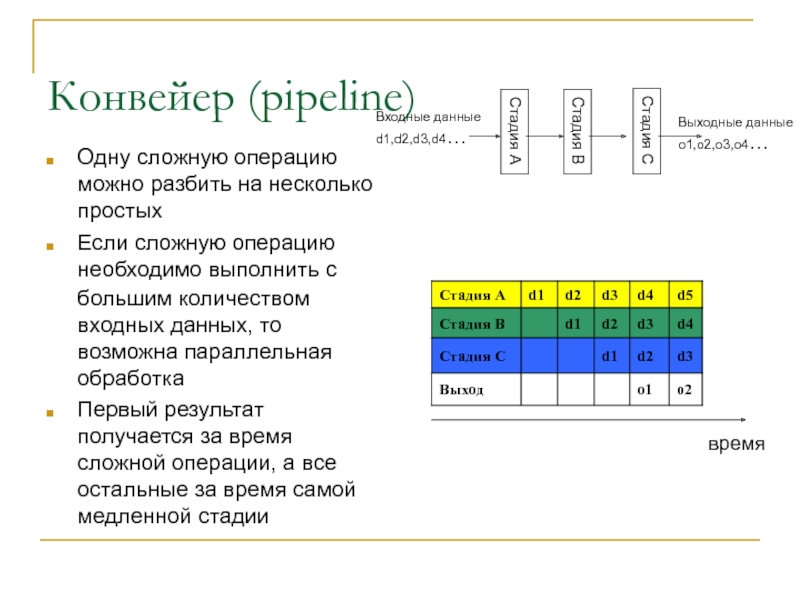

- 13. Конвейер (pipeline)Одну сложную операцию можно разбить на

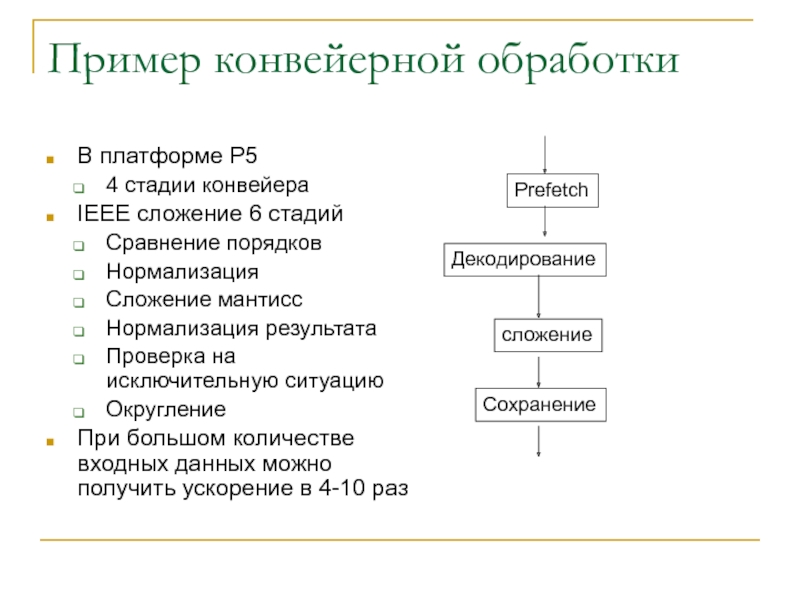

- 14. Пример конвейерной обработкиВ платформе P54 стадии конвейераIEEE

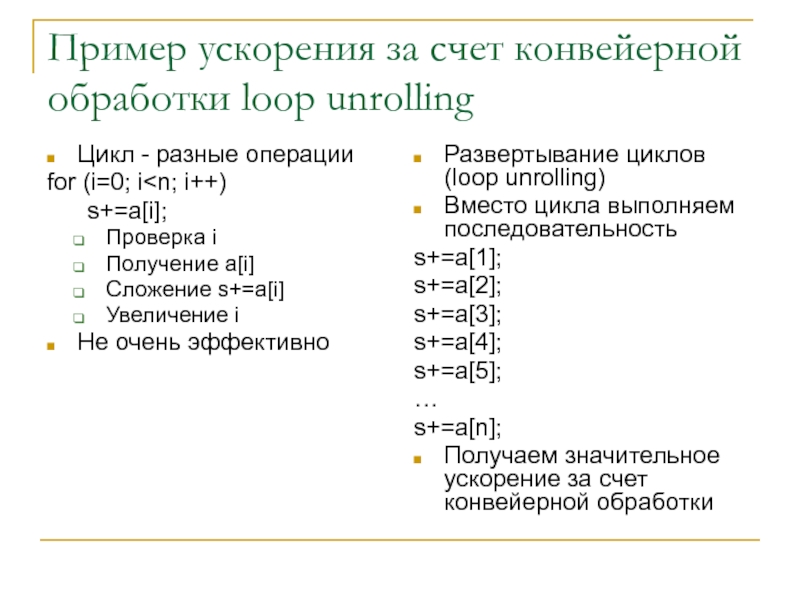

- 15. Пример ускорения за счет конвейерной обработки loop unrollingЦикл - разные операцииfor (i=0; i

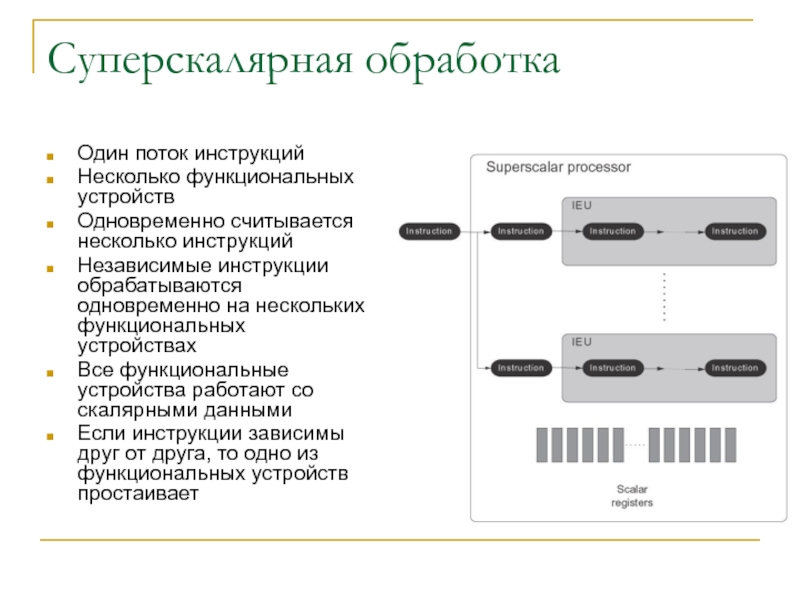

- 16. Суперскалярная обработкаОдин поток инструкцийНесколько функциональных устройствОдновременно считывается

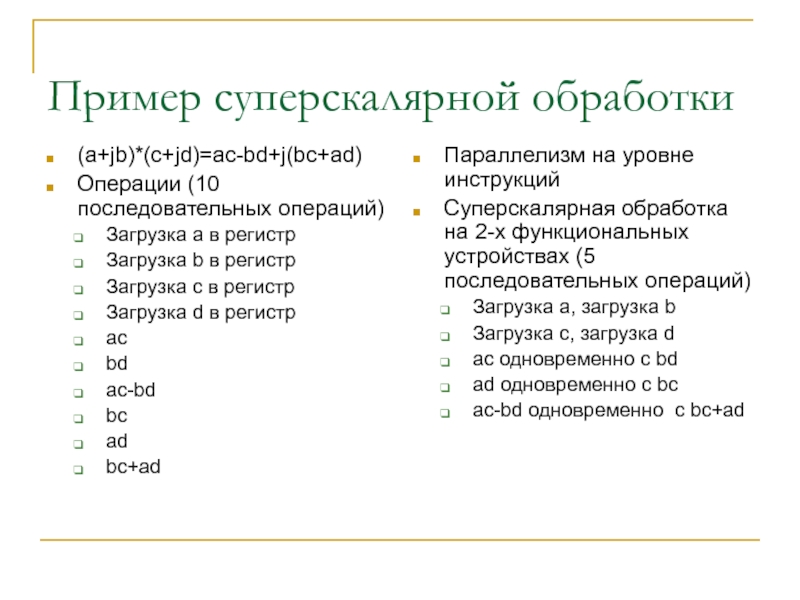

- 17. Пример суперскалярной обработки(a+jb)*(c+jd)=ac-bd+j(bc+ad)Операции (10 последовательных операций)Загрузка a

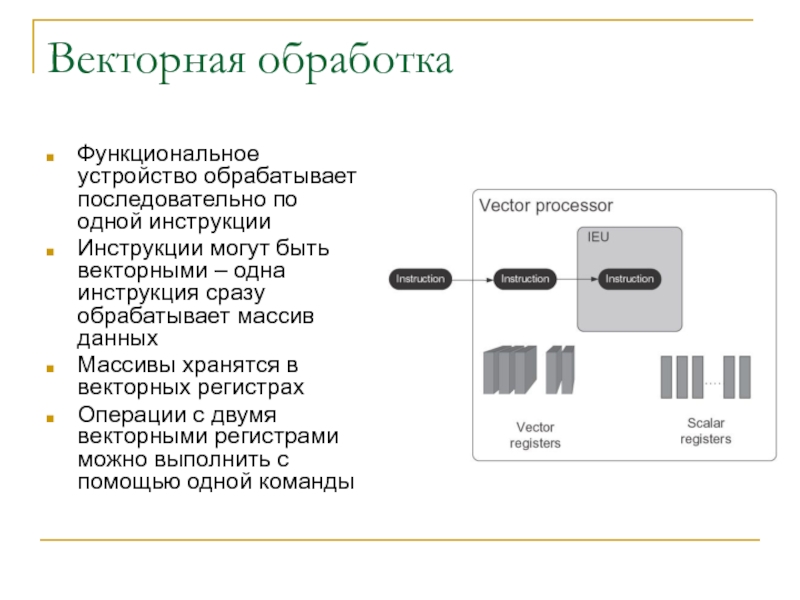

- 18. Векторная обработкаФункциональное устройство обрабатывает последовательно по одной

- 19. Пример векторной обработкиСложение двух массивовa[i]+b[i]=c[i]Последовательный вариантc[1]=a[1]+b[1]c[2]=a[2]+b[2]….c[N]=a[N]+b[N]Порядка 4N

- 20. Векторно-конвейерная обработкаКонвейер очень эффективен для векторных операцийc[]=a[]+b[]Процессор всегда работает эффективно для длинных последовательностей одинаковых операций

- 21. Современные микропроцессорыИспользуются все рассмотренные подходы в комбинацииКаждый

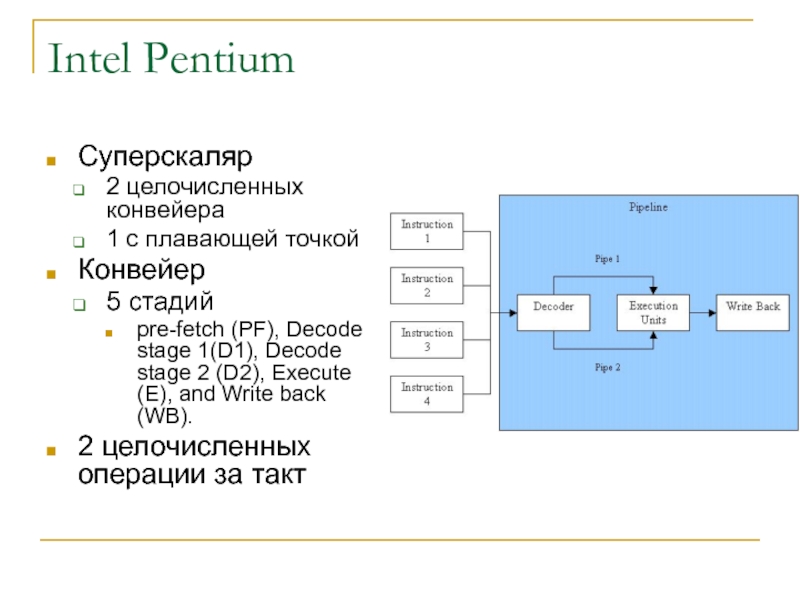

- 22. Intel PentiumСуперскаляр2 целочисленных конвейера1 с плавающей точкойКонвейер5

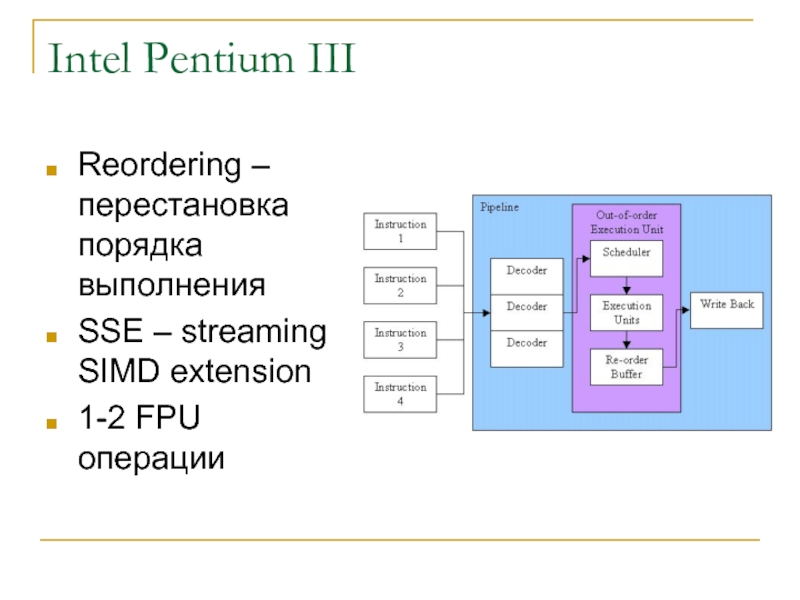

- 23. Intel Pentium IIIReordering – перестановка порядка выполненияSSE – streaming SIMD extension1-2 FPU операции

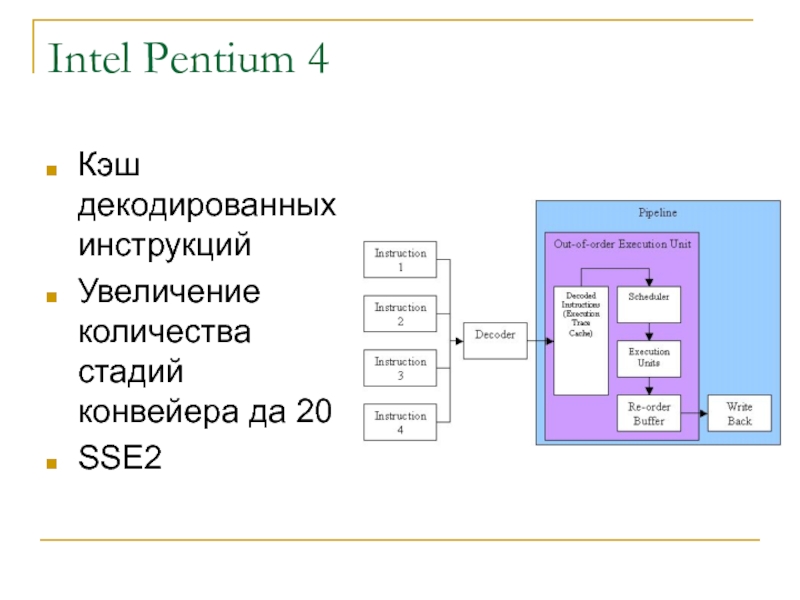

- 24. Intel Pentium 4Кэш декодированных инструкцийУвеличение количества стадий конвейера да 20SSE2

- 25. MMX, SSE, SSE2, SSE3MMX – multimedia extension8

- 26. Как работают SIMD расширенияДанные записываются в векторные

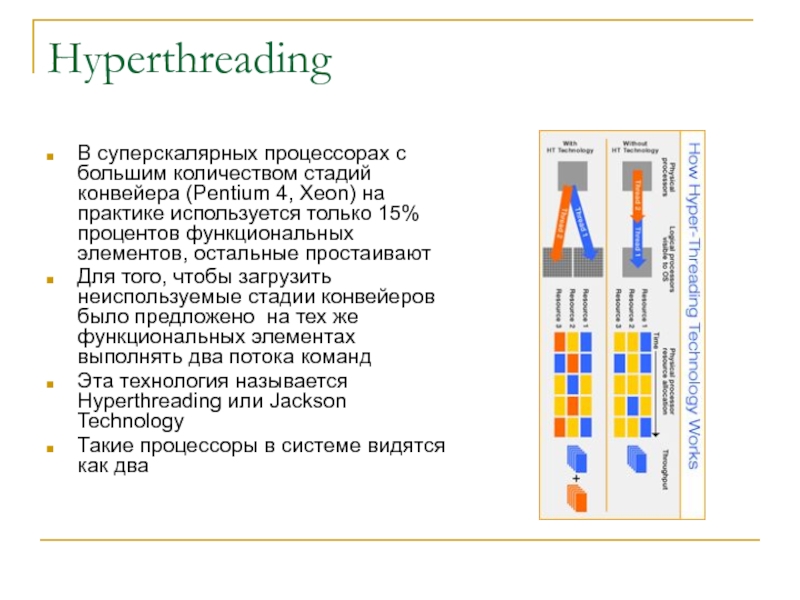

- 27. HyperthreadingВ суперскалярных процессорах с большим количеством стадий

- 28. Когда Hyperthreading эффективен?ЭффективенБолее эффективная обработка прерыванийБолее эффективный

- 29. RISC процессорыRISC – reduced instruction setУменьшение количества

- 30. Характеристики UP процессоровТактовая частотаКоличество операций за один

- 31. Единицы производительностиMIPS - миллион инструкций в секундуХарактеристика

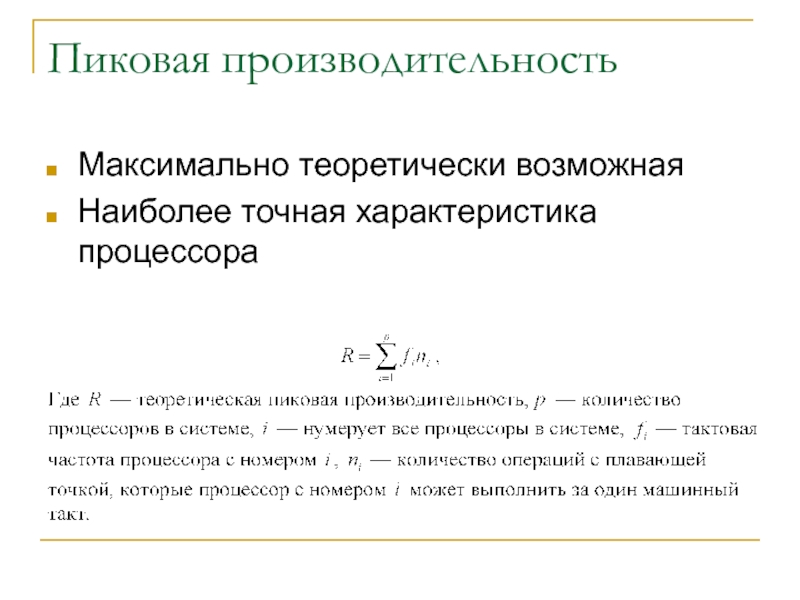

- 32. Пиковая производительностьМаксимально теоретически возможнаяНаиболее точная характеристика процессора

- 33. Пример расчета пиковой производительностиIntel Xeon 2 операции

- 34. Измеренная производительностьИзмеренная производительность зависит от задачиПроцессор эффективен

- 35. Как использовать возможности параллельной обработки UP системМашинные

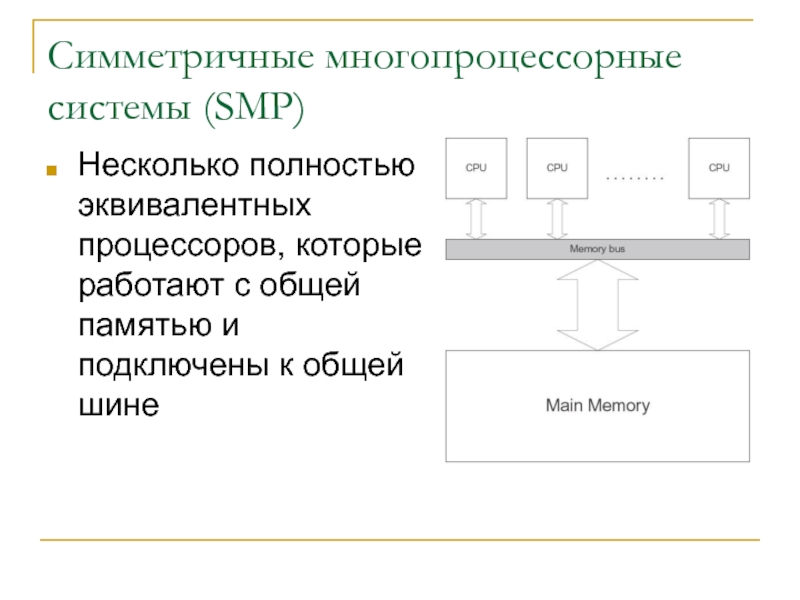

- 36. Симметричные многопроцессорные системы (SMP)Несколько полностью эквивалентных процессоров,

- 37. ОсобенностиПреимуществаПараллелизм на уровне процедурМногопоточные программыБыстрая обработка прерыванийПовышение

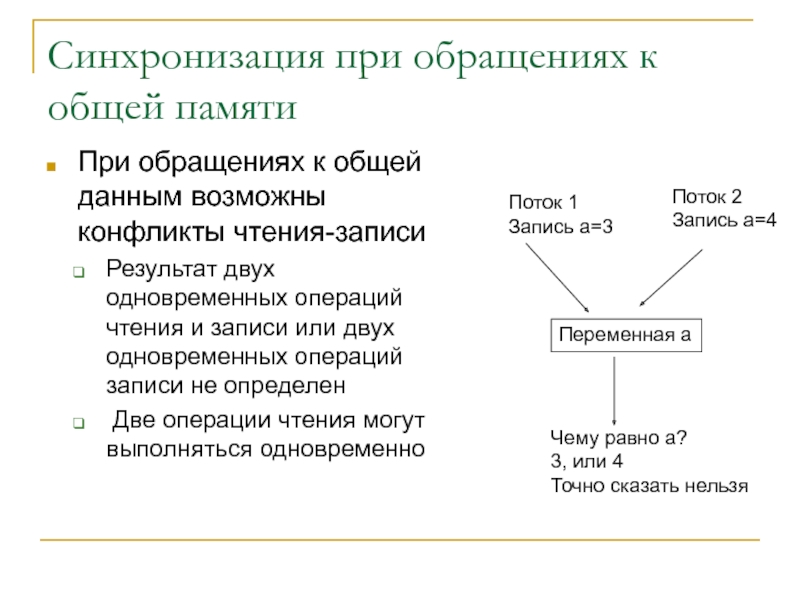

- 38. Синхронизация при обращениях к общей памятиПри обращениях

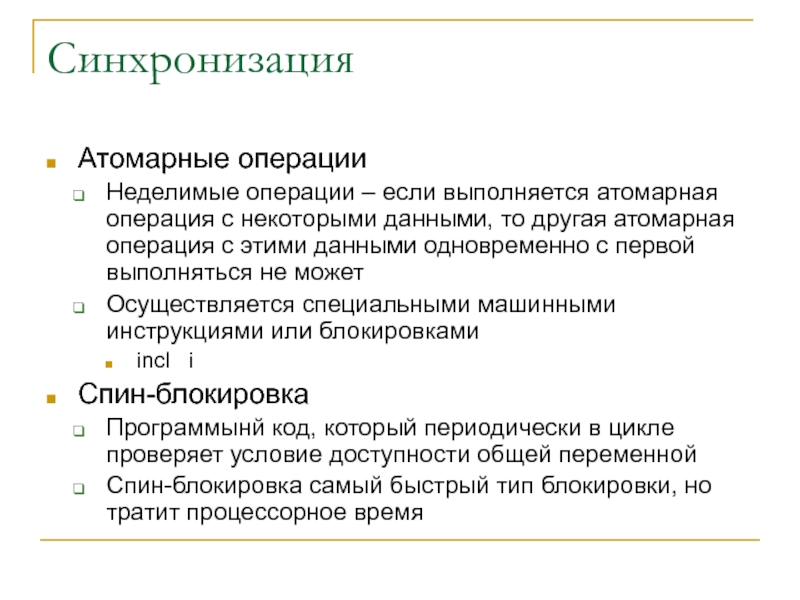

- 39. СинхронизацияАтомарные операцииНеделимые операции – если выполняется атомарная

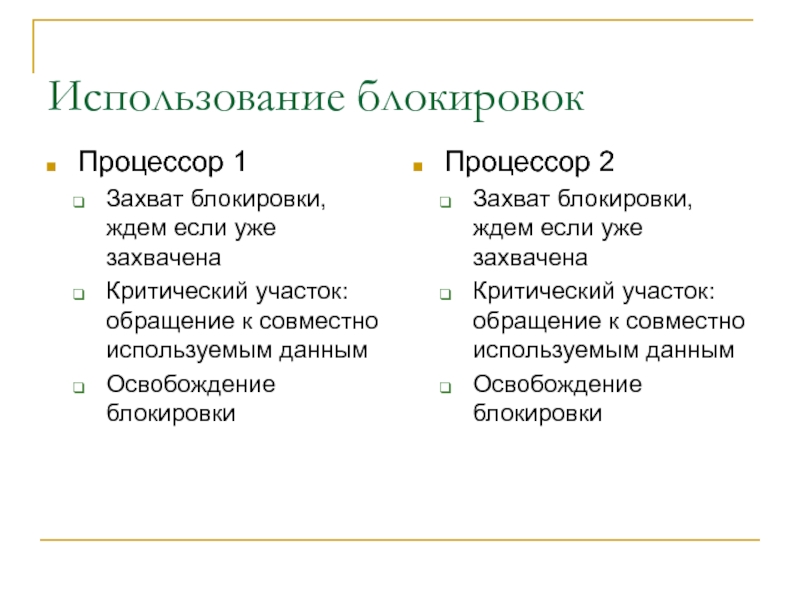

- 40. Использование блокировокПроцессор 1Захват блокировки, ждем если уже

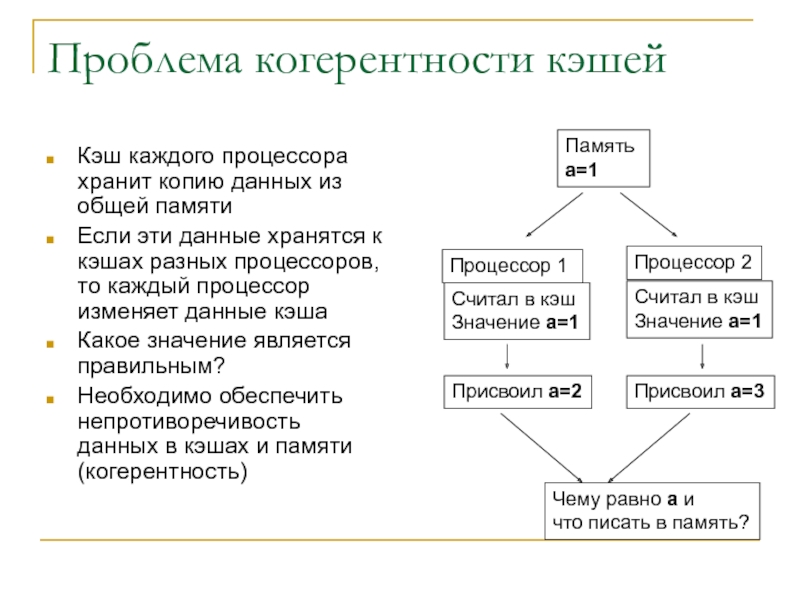

- 41. Проблема когерентности кэшейКэш каждого процессора хранит копию

- 42. Обеспечение когерентности кэшейОбщий кэшНесколько процессоров имеют общий

- 43. Перестановка порядка выполнения ввода-выводаПерестановка порядкаСовременные процессы могут

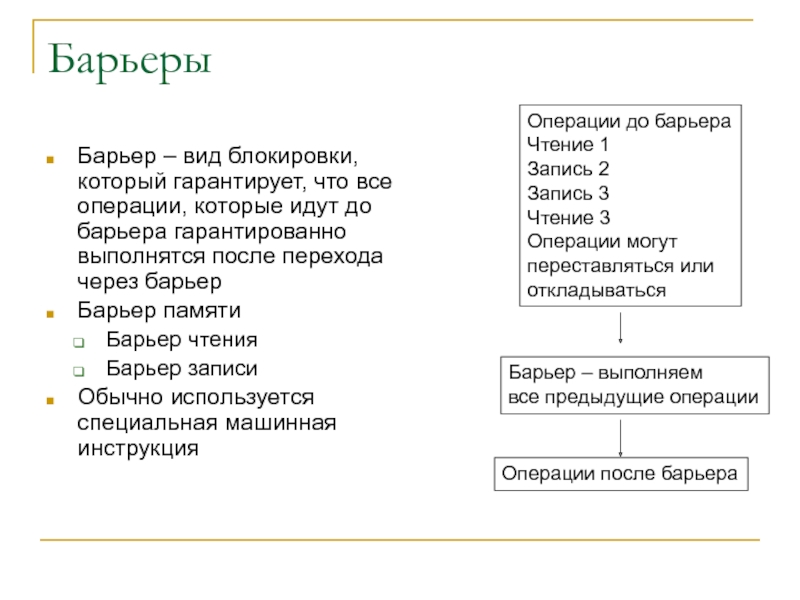

- 44. БарьерыБарьер – вид блокировки, который гарантирует, что

- 45. Обеспечение совместимости за счет компилятораКомпилятору можно указывать

- 46. Работа с общей шинойДанные между памятью и

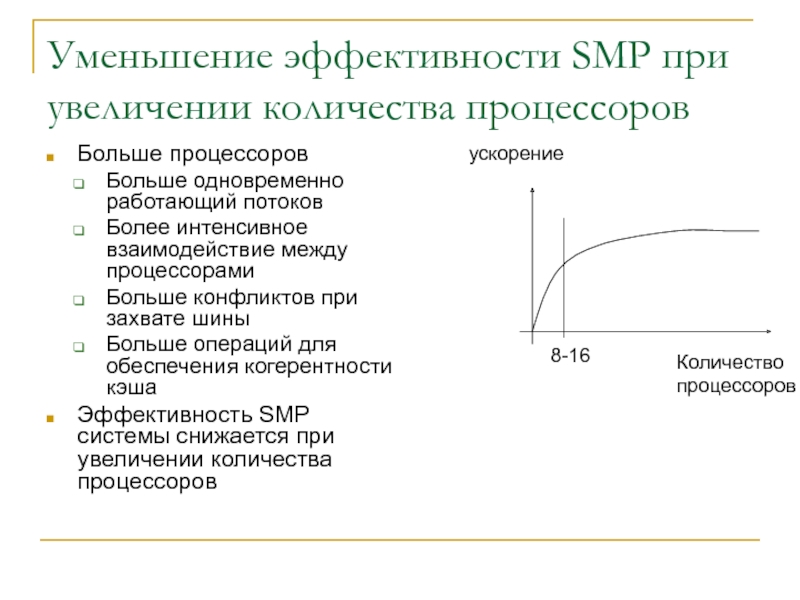

- 47. Уменьшение эффективности SMP при увеличении количества процессоровБольше

- 48. Практические SMP системыОбычно до 8 процессоровAlpha до 64 процессоровНаиболее эффективные 2-4 процессора

- 49. ОптимизацияСуществуют компиляторы с автораспараллеливаниемOpneMPpthreadSysV SHM, SEM

- 50. RISС процессорыМогут отсутствовать следующие функцииАтомарные операцииОбеспечение когерентности

- 51. Вопросы ?

- 52. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Высокопроизводительные системы

Судаков А.А.

“Параллельные и распределенные вычисления” Лекция 9

Слайд 2План

Типы высокопроизводительных систем

Однопроцессорные системы

SMP

Векторные процессоры

Массивно-параллельные системы

NUMA системы

Кластеры

Метакомпьютеры

Основные характеристики

Слайд 3Литература

http://www.intel.com

http://www.parallel.ru

Когерентность кэша http://www.update.uu.se/~gus/Misc/Compositions/cache_coherence.html

Слайд 4Высокопроизводительные системы

Основная цель – получение высокой скорости вычислений

Обработка больших объемов

данных

значительно превосходит широко распространенные вычислительные системыСлайд 5Пути повышения производительности

Использование новых физических эффектов

Увеличение тактовой частоты

Параллельные вычисления

Использование

большого количества вычислительных элементов на которых одновременно решаются различные части

задачиСлайд 6Типы высокопроизводительных систем

Однопроцессорные системы (UP)

Симметричные многопроцессорные системы (SMP)

Векторно-конвейерные системы (PVP)

NUMA

системы

Вычислительные кластеры

Метакомпьютры

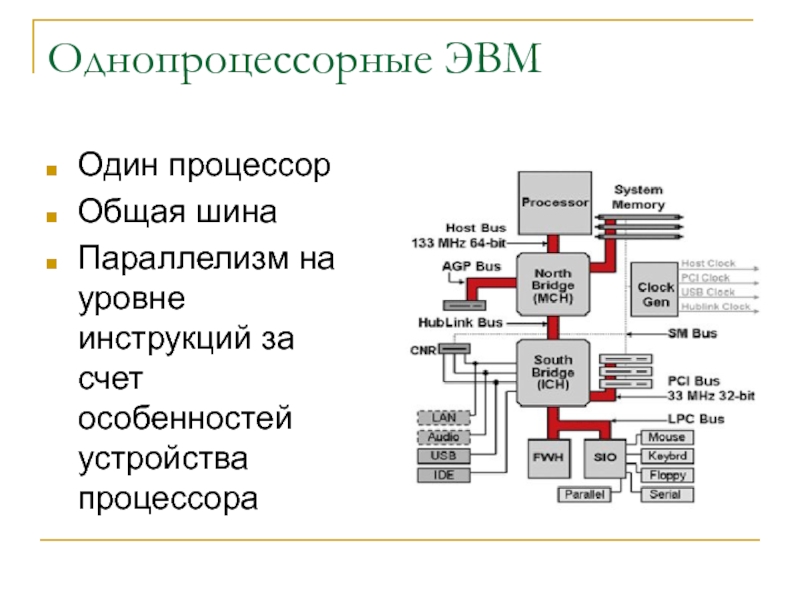

Слайд 7Однопроцессорные ЭВМ

Один процессор

Общая шина

Параллелизм на уровне инструкций за счет особенностей

устройства процессора

Слайд 8Скалярная обработка

Один поток инструкций

Одно функциональное устройство

Все инструкции обрабатываются последовательно

Каждая инструкция

работает со скалярными данными

Скалярные данные – не массив

Intel 8086

Слайд 9Кэширование оперативной памяти

Кэш – память с быстрым доступом (быстрее, чем

из оперативной памяти)

Кэш инструкций – память для инструкций (8-64K)

Кэш данных

– память (8-64K)Кэш первого, второго, третьего уровня

L1 - 8-64K

L2 128K-2M

L3 4M

Процессор из кэша может считывать и записывать данные порциями (строка кэша) обычно 128 байт

Процессор может выполнять действия с кэшем не обращаясь к шине

Возможна параллельная обработка данных процессором и передача по шине

Слайд 10Предварительная выборка

Если данные и инструкции находятся в кэше, то операции

с ними выполняются очень быстро

В процессорах используется различные методы, чтобы

увеличить вероятность того, что необходимые данные находятся в кэше – prefetchПредварительная загрузка

Предсказание ветвлений

Для максимального быстродействия

Данные/код должны считываться/записываться порциями кратными размеру сроки кэша

Данные/код должны помещаться в кэш и кэш должен быть загружен по максимому

Слайд 11Пример замедления за счет не попадания в кэш

Умножение двух матриц

C=AB

Cij=AikBkj

for(i=0;

i

элементы сроки находятся в соседних адресах памятиСоседние элементы столбца находятся «далеко» друг от друга

Необходимые элементы матриц A и C будут в кэше

Необходимый элемент матрицы B там будут отсутствовать

11

12

13

21

…

С

A

B

Слайд 12Пример ускорения за счет кэширования

Умножение двух матриц

C=AB

Cij=AikBkj

for(i=0; i

k++)

for(j=0; j

находятся в соседних адресах памяти Если k и j поменять местами, то все необходимые элементы будут последовательно загружаться в кэш за счет prefetch

11

12

13

21

…

С

A

B

Слайд 13Конвейер (pipeline)

Одну сложную операцию можно разбить на несколько простых

Если сложную

операцию необходимо выполнить с большим количеством входных данных, то возможна

параллельная обработкаПервый результат получается за время сложной операции, а все остальные за время самой медленной стадии

Стадия A

Стадия B

Стадия C

Входные данные

d1,d2,d3,d4…

Выходные данные

o1,o2,o3,o4…

время

Слайд 14Пример конвейерной обработки

В платформе P5

4 стадии конвейера

IEEE сложение 6 стадий

Сравнение

порядков

Нормализация

Сложение мантисс

Нормализация результата

Проверка на исключительную ситуацию

Округление

При большом количестве входных данных

можно получить ускорение в 4-10 разPrefetch

Декодирование

сложение

Сохранение

Слайд 15Пример ускорения за счет конвейерной обработки loop unrolling

Цикл - разные

операции

for (i=0; i

циклов (loop unrolling)Вместо цикла выполняем последовательность

s+=a[1];

s+=a[2];

s+=a[3];

s+=a[4];

s+=a[5];

…

s+=a[n];

Получаем значительное ускорение за счет конвейерной обработки

Слайд 16Суперскалярная обработка

Один поток инструкций

Несколько функциональных устройств

Одновременно считывается несколько инструкций

Независимые инструкции

обрабатываются одновременно на нескольких функциональных устройствах

Все функциональные устройства работают со

скалярными даннымиЕсли инструкции зависимы друг от друга, то одно из функциональных устройств простаивает

Слайд 17Пример суперскалярной обработки

(a+jb)*(c+jd)=ac-bd+j(bc+ad)

Операции (10 последовательных операций)

Загрузка a в регистр

Загрузка b

в регистр

Загрузка c в регистр

Загрузка d в регистр

ac

bd

ac-bd

bc

ad

bc+ad

Параллелизм на уровне

инструкцийСуперскалярная обработка на 2-х функциональных устройствах (5 последовательных операций)

Загрузка a, загрузка b

Загрузка c, загрузка d

ac одновременно с bd

ad одновременно с bc

ac-bd одновременно с bc+ad

Слайд 18Векторная обработка

Функциональное устройство обрабатывает последовательно по одной инструкции

Инструкции могут быть

векторными – одна инструкция сразу обрабатывает массив данных

Массивы хранятся

в векторных регистрахОперации с двумя векторными регистрами можно выполнить с помощью одной команды

Слайд 19Пример векторной обработки

Сложение двух массивов

a[i]+b[i]=c[i]

Последовательный вариант

c[1]=a[1]+b[1]

c[2]=a[2]+b[2]

….

c[N]=a[N]+b[N]

Порядка 4N операций

Загрузка 2N

Сложение N

Присвоение

N

Векторная обработка

Загрузка a[] в векторный регистр 1

Загрузка b[] в векторный

регистр 2 Сложение a[]+b[] одной машинной инструкцией

Присвоение c[]=a[]+b[] одной машинной инструкцией

Порядка 2N+2 операции

Загрузка 2N

Сложение 1

Присвоение 1

Слайд 20Векторно-конвейерная обработка

Конвейер очень эффективен для векторных операций

c[]=a[]+b[]

Процессор всегда работает эффективно

для длинных последовательностей одинаковых операций

Слайд 21Современные микропроцессоры

Используются все рассмотренные подходы в комбинации

Каждый тип процессора имеет

свои особенности и требует своего подхода при программировании для получения

максимальной производительностиСлайд 22Intel Pentium

Суперскаляр

2 целочисленных конвейера

1 с плавающей точкой

Конвейер

5 стадий

pre-fetch (PF), Decode

stage 1(D1), Decode stage 2 (D2), Execute (E), and Write

back (WB).2 целочисленных операции за такт

Слайд 23Intel Pentium III

Reordering – перестановка порядка выполнения

SSE – streaming SIMD

extension

1-2 FPU операции

Слайд 24Intel Pentium 4

Кэш декодированных инструкций

Увеличение количества стадий конвейера да 20

SSE2

Слайд 25MMX, SSE, SSE2, SSE3

MMX – multimedia extension

8 64-х битных векторных

регистра (4 элемента вектора) для операций с целыми числами

Нельзя использовать

совместно с FPUSSE – streaming SIMD extension

8 128-и битных векторных регистра (4 элемента вектора) для операций с плавающей точкой одинарной точности

Можно использовать совместно с MMX

SSE2

Добавлены инструкции для интерпретации каждого регистра как 2 значения типа double

SSE3

Добавлены операции с комплексными числами и др.

Слайд 26Как работают SIMD расширения

Данные записываются в векторные регистры

Вызывается одна инструкция

для выполнения операции с этими регистрами

В зависимости от команды данные

интерпретируются как байты, слова, float, doubleОперация выполняет с помощью векторно-конвейерной обработки

Упаковка байтов

Упаковка слов

Упаковка float

Упаковка double

+

Параллельное

Сложение одной

инструкцией

Слайд 27Hyperthreading

В суперскалярных процессорах с большим количеством стадий конвейера (Pentium 4,

Xeon) на практике используется только 15% процентов функциональных элементов, остальные

простаиваютДля того, чтобы загрузить неиспользуемые стадии конвейеров было предложено на тех же функциональных элементах выполнять два потока команд

Эта технология называется Hyperthreading или Jackson Technology

Такие процессоры в системе видятся как два

Слайд 28Когда Hyperthreading эффективен?

Эффективен

Более эффективная обработка прерываний

Более эффективный ввод/вывод (дисковый, сетевой)

Подкачка

страниц (работа в условиях нехватки памяти)

Запуск приложений

Отображение на память

Более эффективное

одновременное выполнение различных задачMIMD, MISD многопоточность

Более эффективное использование кэша

Не эффективен

Одновременное выполнение одинаковых задач

SIMD многопоточность (математика)

При малом объеме кэша

Слайд 29RISC процессоры

RISC – reduced instruction set

Уменьшение количества сложных инструкций

За счет

этого увеличение производительности

Особенности

Увеличено количество регистров

Увеличение количества конвейеров и простых стадий

конвейеровОперации с памятью только чтение/запись

Вся ответственность за оптимизацию ложится на компилятор

Сложные операции выполняются медленно, но их мало

CISC – complex instruction set

Увеличение количества сложных инструкций

Особенности

Увеличение количества сложных функциональных устройств

Больше инструкций для работы с памятью

Меньше регистров

Повышение «интеллектуальности» процессора

Компилятор должен учитывать особенности процессора

Сложные операции выполняются быстрее, но их меньше

Слайд 30Характеристики UP процессоров

Тактовая частота

Количество операций за один такт

Обычно 1-3

Производительность

– количество операций в секунду

Пиковая: теоретически максимально-возможная

Измеренная: измеренная определенным тестом

Слайд 31Единицы производительности

MIPS - миллион инструкций в секунду

Характеристика для сравнения производительности

разных процессоров

FLOPS – количество операций с плавающей точкой в секунду

Характеристика

производительность при решении прикладных задачMFLOPS, GFLOPS, TFLOPS, PFLOPS

Слайд 32Пиковая производительность

Максимально теоретически возможная

Наиболее точная характеристика процессора

Слайд 33Пример расчета пиковой производительности

Intel Xeon

2 операции с числами с

плавающей точкой двойной точности (double) за одни такт

Тактовая частота

2.4 ГГц R=2*2.4 = 4.8 GFLOPS

Пиковой производительности достичь тяжело

Слайд 34Измеренная производительность

Измеренная производительность зависит от задачи

Процессор эффективен только для определенных

последовательностей команд

Для некоторых задач будет эффективнее одна система, а для

некоторых другаяСтандартные тесты

hpl

NAS

Слайд 35Как использовать возможности параллельной обработки UP систем

Машинные инструкции необходимо выполнять

в оптимальной последовательности

Компилятор должен учитывать особенности процессора

Слайд 36Симметричные многопроцессорные системы (SMP)

Несколько полностью эквивалентных процессоров, которые работают с

общей памятью и подключены к общей шине

Слайд 37Особенности

Преимущества

Параллелизм на уровне процедур

Многопоточные программы

Быстрая обработка прерываний

Повышение производительности ввода/вывода

Сложности

Обеспечение синхронизации

при обращениях к общей памяти

Обеспечение когерентности кэшей

Перестановка операций разными процессорами

Увеличение

количества существенно последовательных операций, таких как передача по общей шинеСнижение эффективности при увеличении количества процессоров

Слайд 38Синхронизация при обращениях к общей памяти

При обращениях к общей данным

возможны конфликты чтения-записи

Результат двух одновременных операций чтения и записи или

двух одновременных операций записи не определенДве операции чтения могут выполняться одновременно

Переменная а

Поток 2

Запись а=4

Поток 1

Запись а=3

Чему равно a?

3, или 4

Точно сказать нельзя

Слайд 39Синхронизация

Атомарные операции

Неделимые операции – если выполняется атомарная операция с некоторыми

данными, то другая атомарная операция с этими данными одновременно с

первой выполняться не можетОсуществляется специальными машинными инструкциями или блокировками

incl i

Спин-блокировка

Программынй код, который периодически в цикле проверяет условие доступности общей переменной

Спин-блокировка самый быстрый тип блокировки, но тратит процессорное время

Слайд 40Использование блокировок

Процессор 1

Захват блокировки, ждем если уже захвачена

Критический участок: обращение

к совместно используемым данным

Освобождение блокировки

Процессор 2

Захват блокировки, ждем если уже

захваченаКритический участок: обращение к совместно используемым данным

Освобождение блокировки

Слайд 41Проблема когерентности кэшей

Кэш каждого процессора хранит копию данных из общей

памяти

Если эти данные хранятся к кэшах разных процессоров, то каждый

процессор изменяет данные кэшаКакое значение является правильным?

Необходимо обеспечить непротиворечивость данных в кэшах и памяти (когерентность)

Процессор 1

Процессор 2

Память

a=1

Считал в кэш

Значение a=1

Считал в кэш

Значение a=1

Присвоил a=2

Присвоил a=3

Чему равно a и

что писать в память?

Слайд 42Обеспечение когерентности кэшей

Общий кэш

Несколько процессоров имеют общий кэш и все

данные в кэше синхронизированы

Перехват (мониторинг шины, bus snooping)

При любых обращениях

к данным по шине система мониторинга определяет какой процессор прочитал какие данные и нет ли соответствующих данных в кэше другого процессора, если есть, то возвращает ихКаталог кэшей (cache directory)

Обращения к памяти выполняются через каталог, в котором хранится информация о том, какие данные хранятся в кэше какого процессора

Через каталог выполняется передача информации

Слайд 43Перестановка порядка выполнения ввода-вывода

Перестановка порядка

Современные процессы могут переставлять местами операции

чтения записи или

Компилятор может сохранять копии данных в регистрах

и тоже переставлять порядокПерестановки порядка выполнения разными процессорами может привести к записи в память неправильных данных

Отсрочка операции записи может привести к неправильной работе программ на разных процессорах

На однопроцессорной системе такого произойти не может

Процессор 1

Процессор 2

Память a=1

Читаем a=1

Цикл:

a=a+1

Запись a в память

Продолжить

Умный процессор 1

Зачем писать

по нескольку

раз. Запишу, когда

цикл закончится

Читаем a

a=1

всегда

Слайд 44Барьеры

Барьер – вид блокировки, который гарантирует, что все операции, которые

идут до барьера гарантированно выполнятся после перехода через барьер

Барьер памяти

Барьер

чтения Барьер записи

Обычно используется специальная машинная инструкция

Операции до барьера

Чтение 1

Запись 2

Запись 3

Чтение 3

Операции могут переставляться или откладываться

Барьер – выполняем

все предыдущие операции

Операции после барьера

Слайд 45Обеспечение совместимости за счет компилятора

Компилятору можно указывать инструкции в каких

случаях можно переставлять данные, а в каких – нет

С помощью

специально скомпилированного кода можно обеспечить также когерентность кэшейСлайд 46Работа с общей шиной

Данные между памятью и процессорами передаются по

одной общей шине

Захват шины

Передача/прием данных

Отпускание шины

Передача по шине – существенно

последовательная операция и снижает эффективность параллелизмаПри увеличении количества процессоров увеличивается количество захватов и вероятность того, что шина будет захвачена, когда она нужна – процессоры простаивают

Слайд 47Уменьшение эффективности SMP при увеличении количества процессоров

Больше процессоров

Больше одновременно работающий

потоков

Более интенсивное взаимодействие между процессорами

Больше конфликтов при захвате шины

Больше операций

для обеспечения когерентности кэшаЭффективность SMP системы снижается при увеличении количества процессоров

Количество

процессоров

ускорение

8-16

![Высокопроизводительные системы Пример векторной обработкиСложение двух массивовa[i]+b[i]=c[i]Последовательный вариантc[1]=a[1]+b[1]c[2]=a[2]+b[2]….c[N]=a[N]+b[N]Порядка 4N операцийЗагрузка 2NСложение NПрисвоение NВекторная Пример векторной обработкиСложение двух массивовa[i]+b[i]=c[i]Последовательный вариантc[1]=a[1]+b[1]c[2]=a[2]+b[2]….c[N]=a[N]+b[N]Порядка 4N операцийЗагрузка 2NСложение NПрисвоение NВекторная обработкаЗагрузка a[] в векторный регистр 1Загрузка](/img/tmb/2/154356/6be5abcab29fc78579673d65a0b9e064-800x.jpg)

![Высокопроизводительные системы Векторно-конвейерная обработкаКонвейер очень эффективен для векторных операцийc[]=a[]+b[]Процессор всегда работает эффективно для длинных последовательностей одинаковых операций Векторно-конвейерная обработкаКонвейер очень эффективен для векторных операцийc[]=a[]+b[]Процессор всегда работает эффективно для длинных последовательностей одинаковых операций](/img/thumbs/53b09ee640ce733d0d0ff781aec42f60-800x.jpg)