Physics Faculty, Electronic Devices & Systems, 7th semester,2011

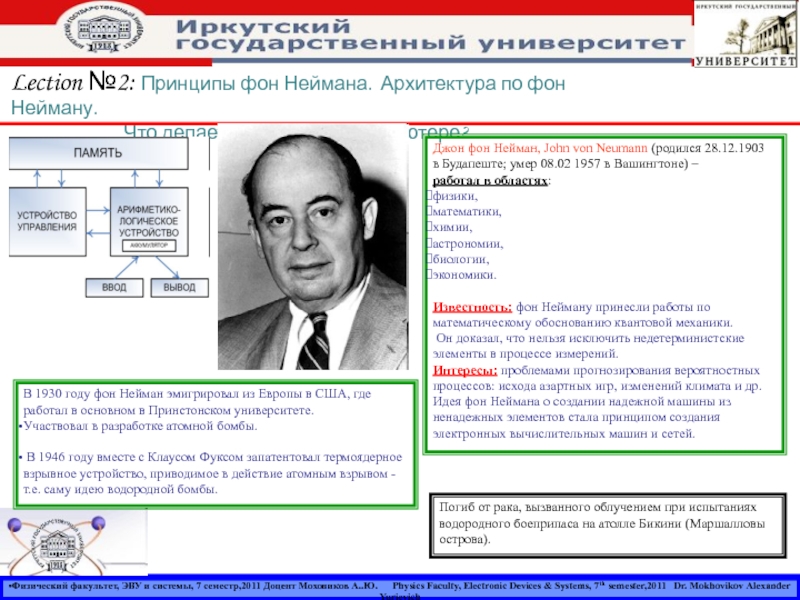

Dr. Mokhovikov Alexander YurievichLection №2: Принципы фон Неймана. Архитектура по фон Нейману.

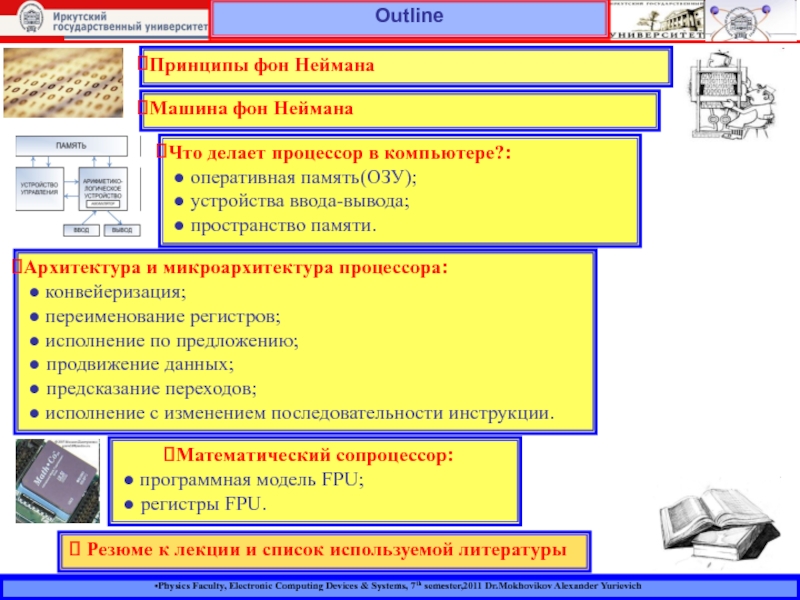

Что делает процессор в компьютере?

Джон фон Нейман, John von Neumann (родился 28.12.1903 в Будапеште; умер 08.02 1957 в Вашингтоне) –

работал в областях:

физики,

математики,

химии,

астрономии,

биологии,

экономики.

Известность: фон Нейману принесли работы по математическому обоснованию квантовой механики.

Он доказал, что нельзя исключить недетерминистские элементы в процессе измерений.

Интересы: проблемами прогнозирования вероятностных процессов: исхода азартных игр, изменений климата и др.

Идея фон Неймана о создании надежной машины из ненадежных элементов стала принципом создания электронных вычислительных машин и сетей.

В 1930 году фон Нейман эмигрировал из Европы в США, где работал в основном в Принстонском университете.

Участвовал в разработке атомной бомбы.

В 1946 году вместе с Клаусом Фуксом запатентовал термоядерное взрывное устройство, приводимое в действие атомным взрывом - т.е. саму идею водородной бомбы.

Погиб от рака, вызванного облучением при испытаниях водородного боеприпаса на атолле Бикини (Маршалловы острова).