Слайд 1Архитектура фон Неймана и Гарварда презентация

Слайд 2В 1946 году Д. фон Нейман, Г. Голдстайн и А.

Беркс в своей совместной статье изложили новые принципы построения и

функционирования ЭВМ.

В последствие на основе этих принципов производились первые два поколения компьютеров. В более поздних поколениях происходили некоторые изменения, хотя принципы Неймана актуальны и сегодня.

Слайд 31. Использование двоичной системы счисления в вычислительных машинах.

Преимущество перед десятичной

системой счисления заключается в том, что устройства можно делать достаточно

простыми, арифметические и логические операции в двоичной системе счисления также выполняются достаточно просто.

Слайд 42. Программное управление ЭВМ

Работа ЭВМ контролируется программой, состоящей из набора

команд. Команды выполняются последовательно друг за другом. Созданием машины с

хранимой в памяти программой было положено начало тому, что мы сегодня называем программированием.

Слайд 53. Память компьютера используется не только для хранения данных, но

и программ.

При этом и команды программы и данные кодируются в

двоичной системе счисления, т.е. их способ записи одинаков. Поэтому в определенных ситуациях над командами можно выполнять те же действия, что и над данными.

Слайд 64. Ячейки памяти ЭВМ имеют адреса, которые последовательно пронумерованы

В любой

момент можно обратиться к любой ячейке памяти по ее адресу.

Этот принцип открыл возможность использовать переменные в программировании.

Слайд 75. Возможность условного перехода в процессе выполнения программы.

Не смотря на

то, что команды выполняются последовательно, в программах можно реализовать возможность

перехода к любому участку кода.

Слайд 10Поколения компьютеров - история развития вычислительной техники

Слайд 11Нулевое поколение. Механические вычислители

счетная машина блеза паскаля, 1642 г. эта

машина могла выполнять лишь операции сложения и вычитания.

Слайд 12Первое поколение. Компьютеры на электронных лампах (194х-1955)

Быстродействие: несколько десятков тысяч

операций в секунду.

Особенности:

Поскольку лампы имеют существенные размеры и их тысячи,

то машины имели огромные размеры.

Поскольку ламп много и они имеют свойство перегорать, то часто компьютер простаивал из-за поиска и замены вышедшей из строя лампы.

Лампы выделяют большое количество тепла, следовательно, вычислительные машины требуют специальные мощные охладительные системы.

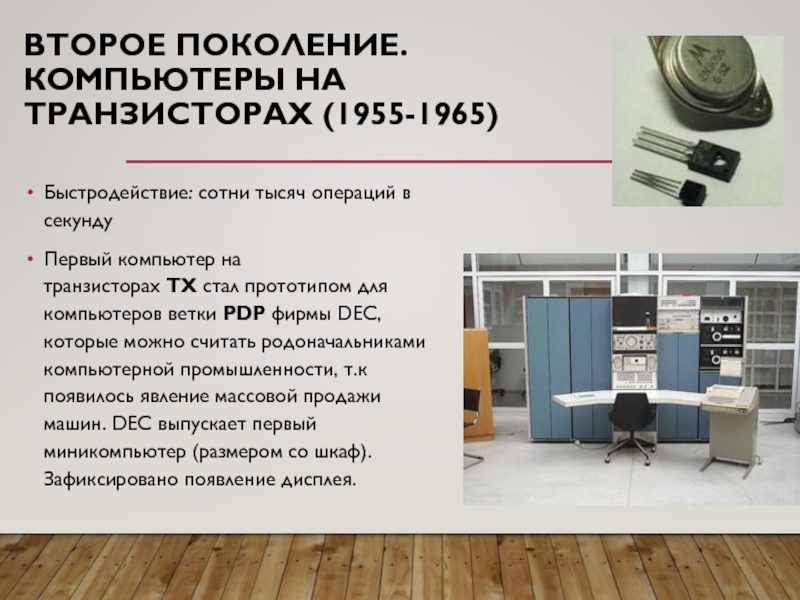

Слайд 14Второе поколение. Компьютеры на транзисторах (1955-1965)

Быстродействие: сотни тысяч операций в

секунду

Первый компьютер на транзисторах TX стал прототипом для компьютеров ветки PDP фирмы DEC, которые

можно считать родоначальниками компьютерной промышленности, т.к появилось явление массовой продажи машин. DEC выпускает первый миникомпьютер (размером со шкаф). Зафиксировано появление дисплея.

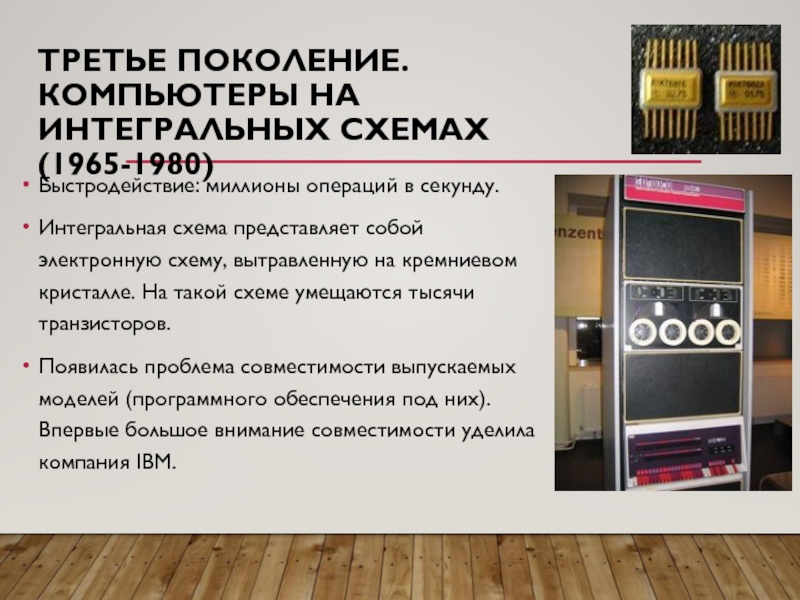

Слайд 15Третье поколение. Компьютеры на интегральных схемах (1965-1980)

Быстродействие: миллионы операций в

секунду.

Интегральная схема представляет собой электронную схему, вытравленную на кремниевом кристалле.

На такой схеме умещаются тысячи транзисторов.

Появилась проблема совместимости выпускаемых моделей (программного обеспечения под них). Впервые большое внимание совместимости уделила компания IBM.

Слайд 16Четвертое поколение. Компьютеры на больших (и сверхбольших) интегральных схемах (1980-…)

Быстродействие:

сотни миллионов операций в секунду.

Появилась возможность размещать на одном кристалле

не одну интегральную схему, а тысячи. Быстродействие компьютеров увеличилось значительно.

В конце 70-х – начале 80-х популярностью пользовался компьютера Apple, разработанный Стивом Джобсом и Стивом Возняком. Позднее в массовое производство был запущен персональный компьютер IBM PC на процессоре Intel.

Слайд 19Характеристики шестого поколения

Слайд 20Гарвардская архитектура и её достоинства

При реализации микропроцессоров традиционно используется два

подхода к построению архитектуры:

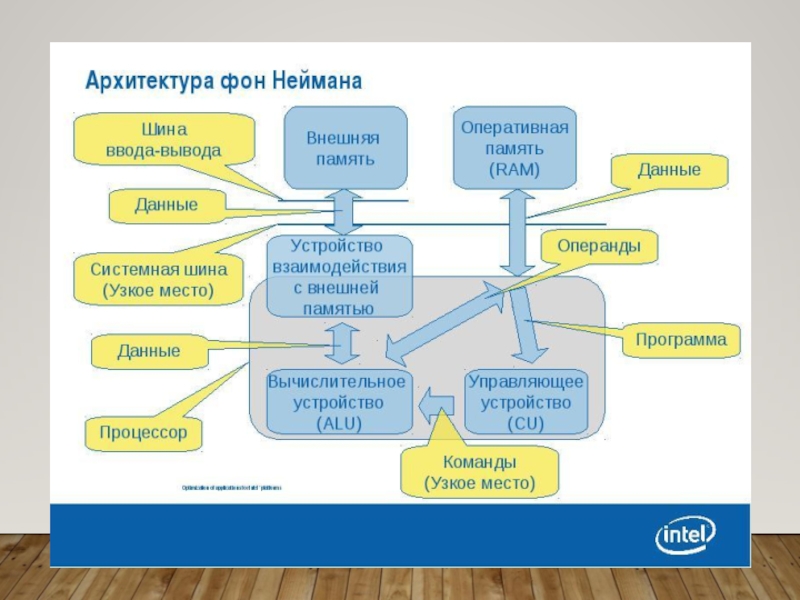

Архитектура фон Неймана

Гарвардская архитектура

В архитектуре фон Неймана

применяется однородная память микропроцессора. В эту память могут записываться различные программы. При этом специальная программа-загрузчик работает с ними как с данными. Затем управление может быть передано этим программам и они уже начинают выполнять свой алгоритм. При подобном подходе к управлению микропроцессором удается достигнуть максимальной гибкости микропроцессорной системы.

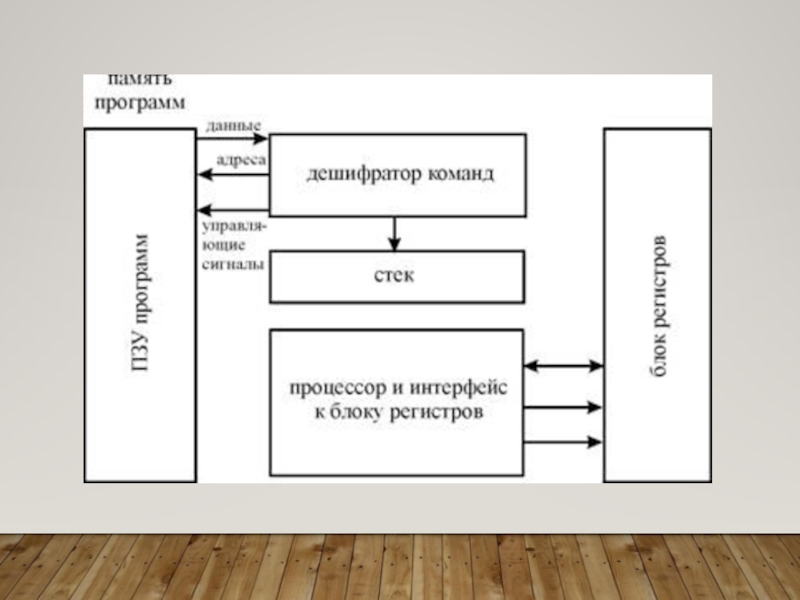

Слайд 21В качестве недостатка архитектуры фон Неймана можно назвать возможность непреднамеренного

нарушения работоспособности системы (программные ошибки) и преднамеренное уничтожение ее работы

(вирусные атаки). В Гарвардской архитектуре принципиально различаются два вида памяти микропроцессора:

Память программ (для хранения инструкций микропроцессора)

Память данных (для временного хранения и обработки переменных)

В гарвардской архитектуре принципиально невозможно осуществить операцию записи в память программ, что исключает возможность случайного разрушения управляющей программы в случае ошибки программы при работе с данными или атаки третьих лиц. Кроме того, для работы с памятью программ и с памятью данных организуются отдельные шины обмена данными (системные шины), как это показано на структурной схеме, приведенной на рисунке 1.

Слайд 23Эти особенности определили области применения гарвардской архитектуры. Гарвардская архитектура применяется

в микроконтролерах и в сигнальных процессорах , где требуется обеспечить высокую надёжность

работы аппаратуры. В сигнальных процессорах Гарвардская архитектура дополняется применением трехшинного операционного блока микропроцессора. Трехшинная архитектура операционного блока позволяет совместить операции считывания двух операндов с записью результата выполнения команды в оперативную память микропроцессора. Это значительно увеличивает производительность сигнального микропроцессора без увеличения его тактовой частоты.

Слайд 24В Гарвардской архитектуре характеристики устройств памяти программ и памяти данных

не всегда выполняются одинаковыми. В памяти данных и команд могут

различаться разрядность шины данных и распределение адресов памяти. Часто адресные пространства памяти программ и памяти данных выполняют различными. Это приводит к различию разрядности шины адреса для этих видов памяти. В микроконтроллерах память программ обычно реализуется в виде постоянного запоминающего устройства, а память данных — в виде ОЗУ. В сигнальных процессорах память программ вынуждены выполнять в виде ОЗУ. Это связано с более высоким быстродействием оперативного запоминающего устройства, однако при этом в процессе работы осуществляется защита от записи в эту область памяти.

Слайд 25Применение двух системных шин для обращения к памяти программ и

памяти данных в гарвадской архитектуре имеет два недостатка — высокую стоимость

и большое количество внешних выводов микропроцессора. При использованиии двух шин для передачи команд и данных, микропроцессор должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Для уменьшения количества выводов кристалла микропроцессора фирмы-производители микросхем объединили шины данных и шины адреса для внешней памяти данных и программ, оставив только различные сигналы управления (WR, RD, IRQ) а внутри микропроцессора сохранили классическую гарвардскую архитектуру. Такое решение получило названиемодифицированная гарвардская архитектура.

Слайд 26В сигнальных процессорах для реализации таких алгоритмах как быстрое преобразование Фурье и

цифровая фильтрация часто требуется еще большее количество внутренних шин. Обычно

применяются две шины для чтения данных, одна шина для записи данных и одна шина для чтения инструкций. Подобная структура микропроцессора получила название расширенной гарвардской архитектуры. Этот подход практикуют производители сигнальных процессоров — фирмы Analog Devices (семейства сигнальных процессоров BlackFin и Tiger Shark), Texas Instrunents (семейства сигнальных процессоров C5000™ DSPs и C6000™ DSPs), Freescale (семейства сигнальных процессоров MSC8251 и DSP56K).