шины LOCK;

префиксы размера;

префиксы замены сегмента.

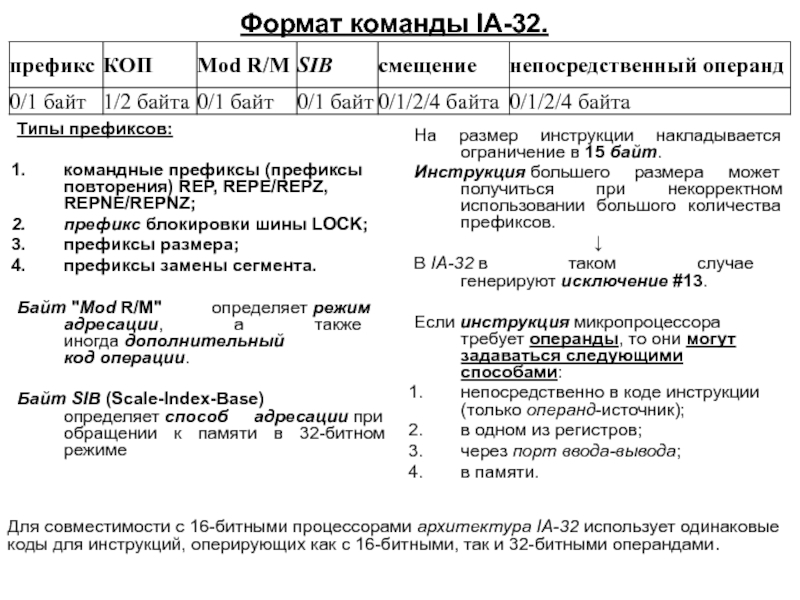

Байт "Mod R/M" определяет режим адресации, а также иногда дополнительный

код операции. Байт SIB (Scale-Index-Base) определяет способ адресации при обращении к памяти в 32-битном режиме

На размер инструкции накладывается ограничение в 15 байт.

Инструкция большего размера может получиться при некорректном использовании большого количества префиксов.

↓

В IA-32 в таком случае генерируют исключение #13.

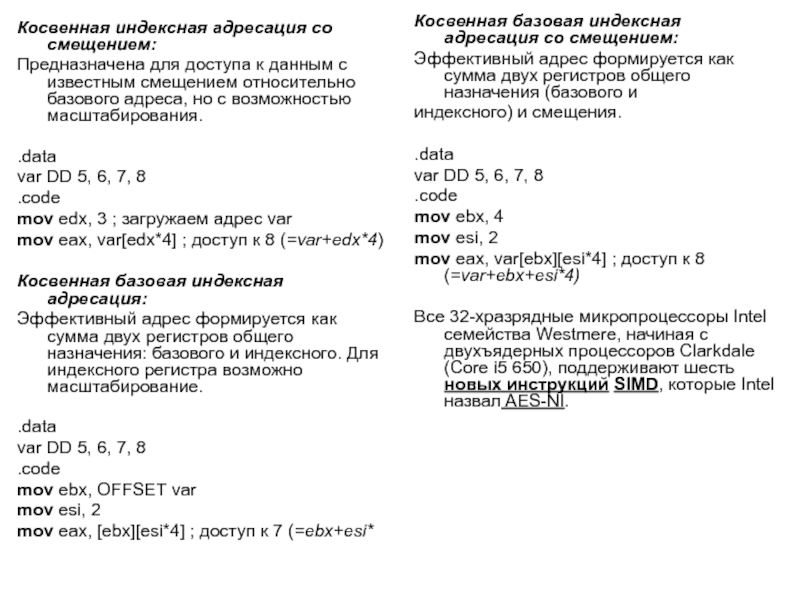

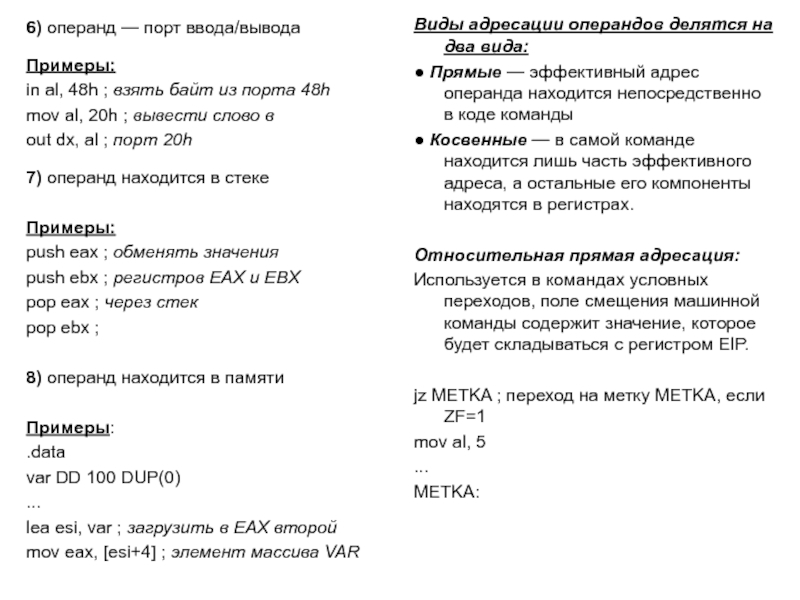

Если инструкция микропроцессора требует операнды, то они могут задаваться следующими способами:

непосредственно в коде инструкции (только операнд-источник);

в одном из регистров;

через порт ввода-вывода;

в памяти.

Для совместимости с 16-битными процессорами архитектура IA-32 использует одинаковые коды для инструкций, оперирующих как с 16-битными, так и 32-битными операндами.

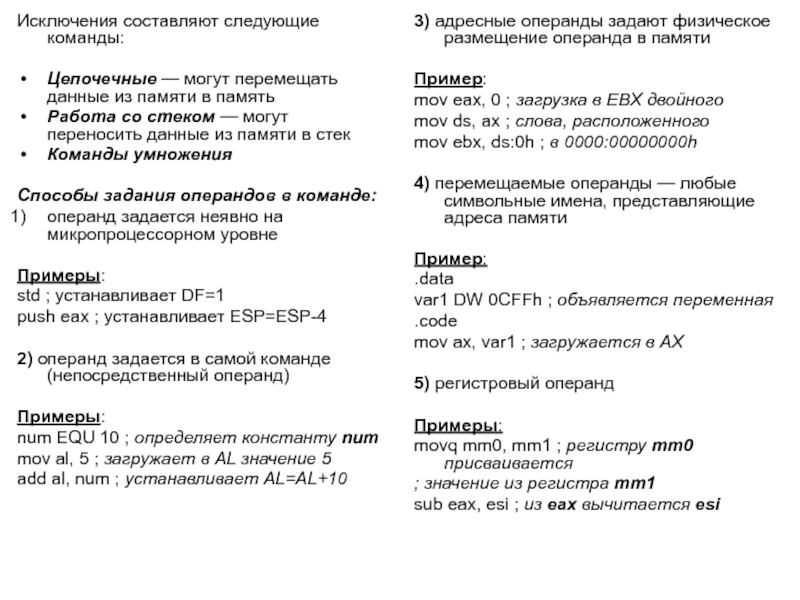

![Архитектура IA- 32 Абсолютная прямая адресация:Эффективный адрес операнда формируется из поля смещения команды.mov eax, Абсолютная прямая адресация:Эффективный адрес операнда формируется из поля смещения команды.mov eax, DWORD PTR [0h] ; загружает в](/img/thumbs/04bd6cd565bd1f8786ba90a538087240-800x.jpg)