Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Дополнение к лекции 2

Содержание

- 1. Дополнение к лекции 2

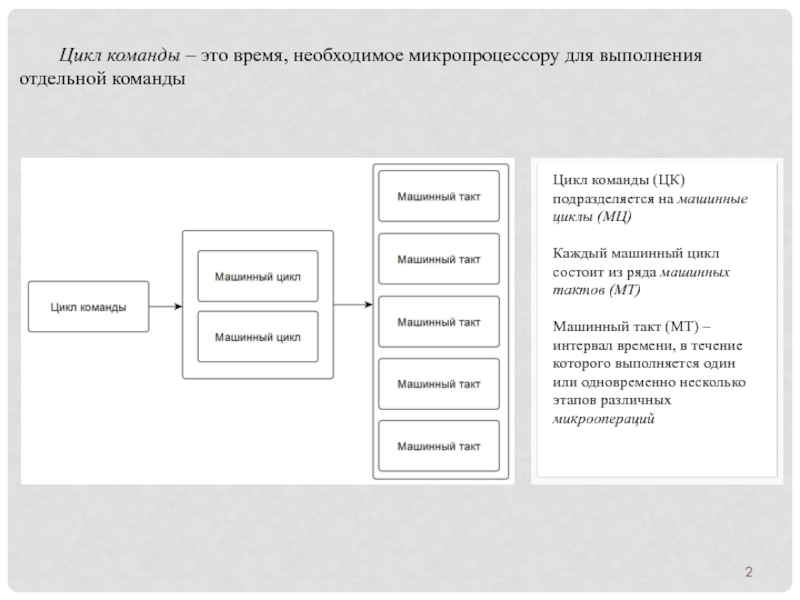

- 2. Цикл команды – это время, необходимое микропроцессору для выполнения отдельной команды

- 3. Лекция 3. Память МПСВыполнил: Провоторов Н.В. Москва 2018

- 4. Большинство современных микроконтроллеров имеют Гарвардскую архитектуру и

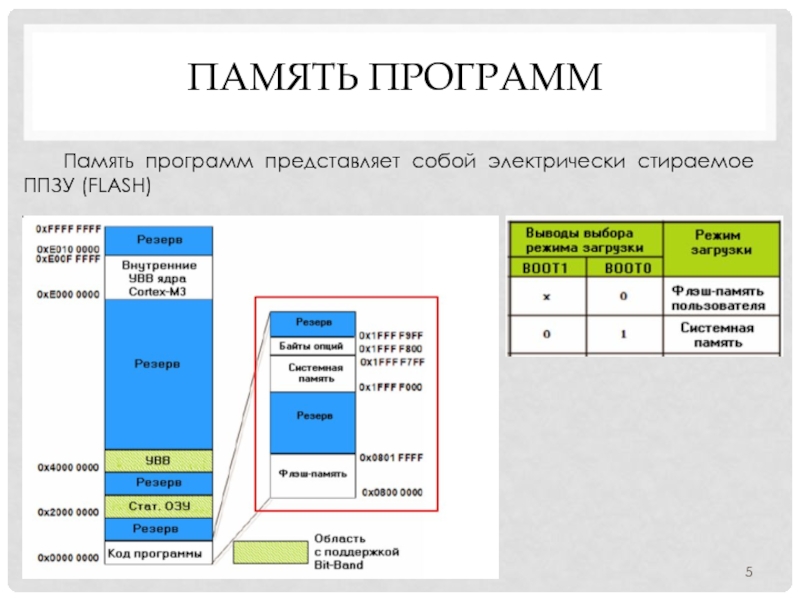

- 5. Память программ Память программ представляет собой электрически стираемое ППЗУ (FLASH)

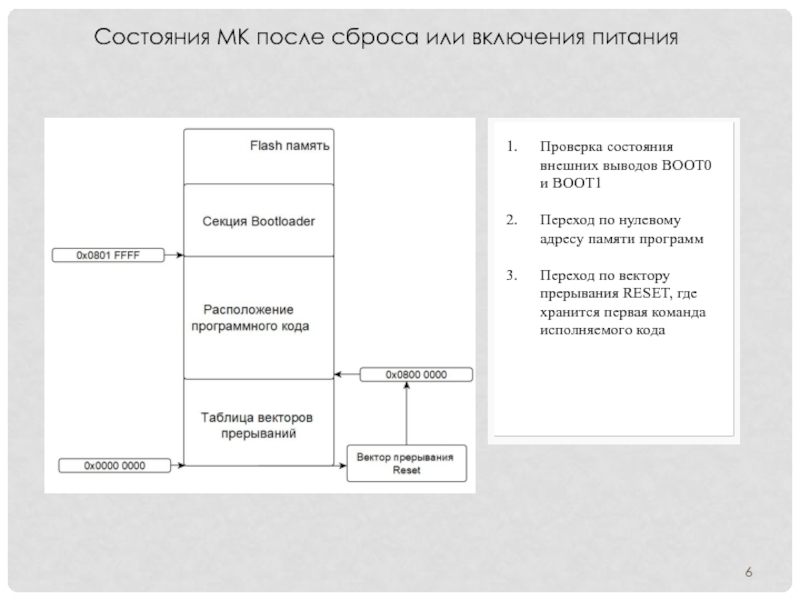

- 6. Состояния МК после сброса или включения питания

- 7. Физическая реализация ПЗУ В основе флэш памяти лежит особая модификация транзистора с изолированным затвором (МОП-транзистора).

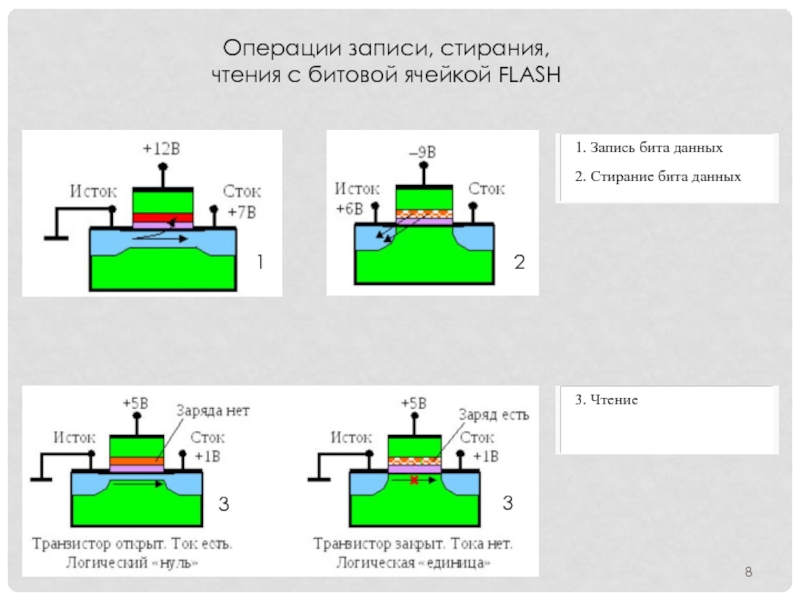

- 8. Операции записи, стирания, чтения с битовой ячейкой FLASH 1233

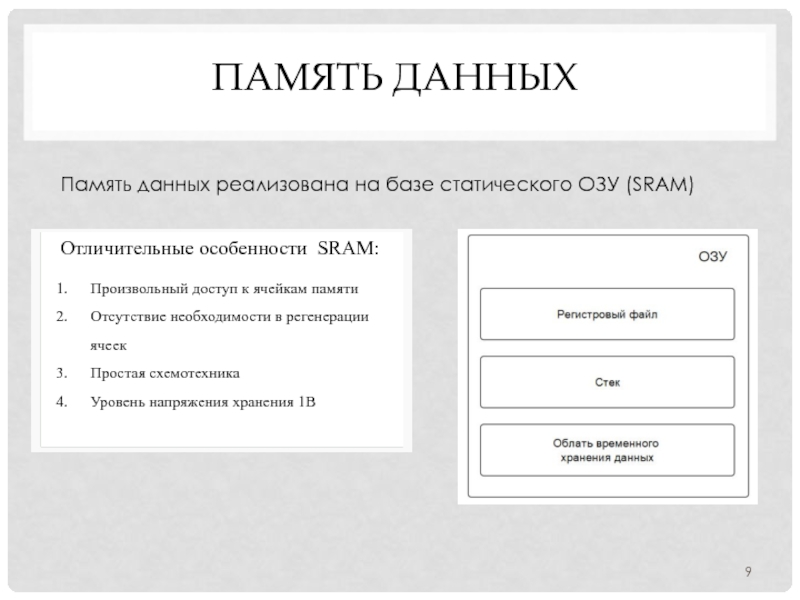

- 9. Память Данных Память данных реализована на базе статического ОЗУ (SRAM)

- 10. Физическая реализация ОЗУ Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии.

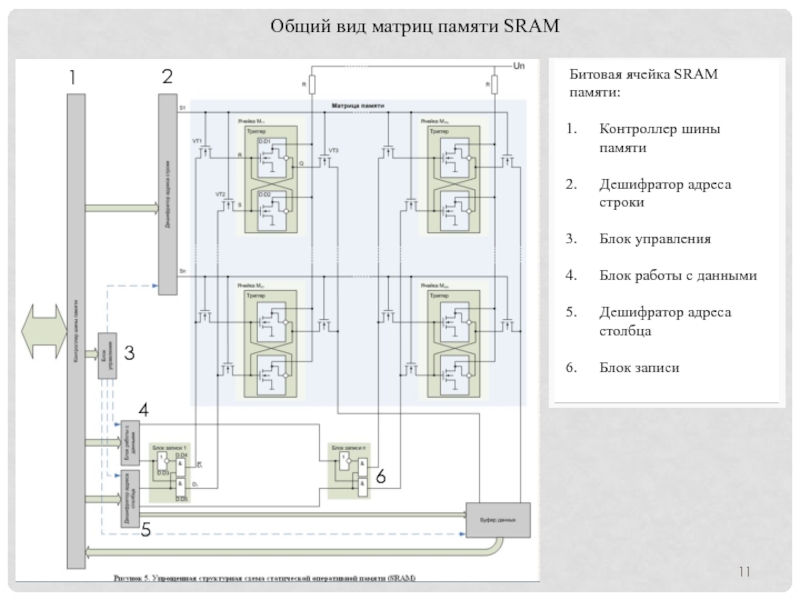

- 11. Общий вид матриц памяти SRAM 123456

- 12. Более подробная реализация ячейки статической двоичной памяти

- 13. Регистры МКРегистры МК также выступают в качестве

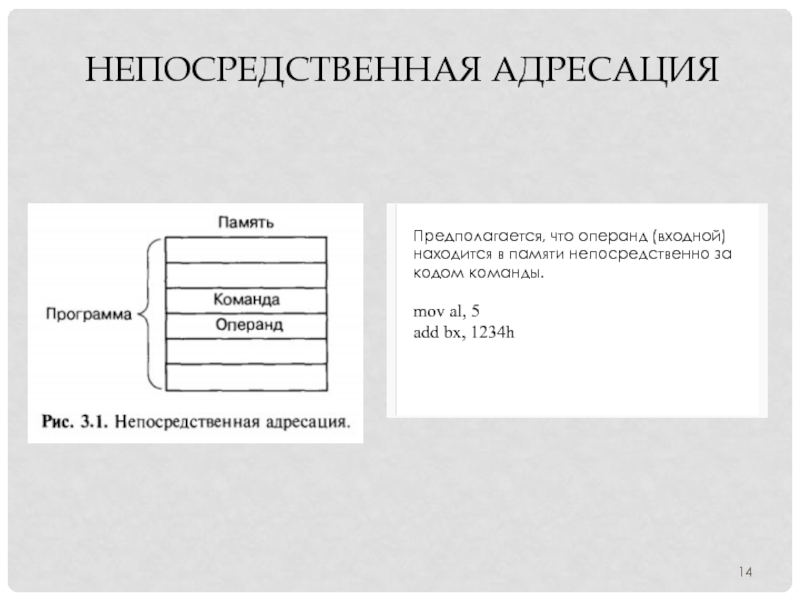

- 14. Непосредственная адресация

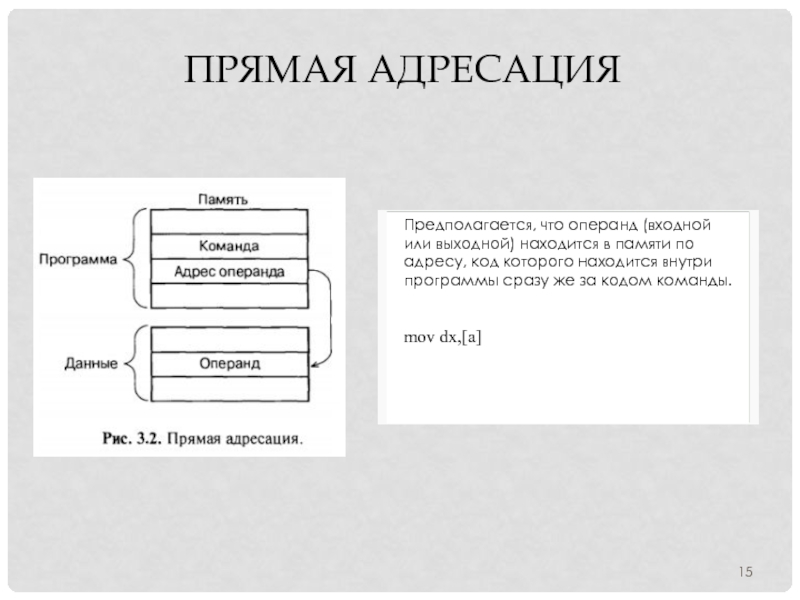

- 15. Прямая адресация

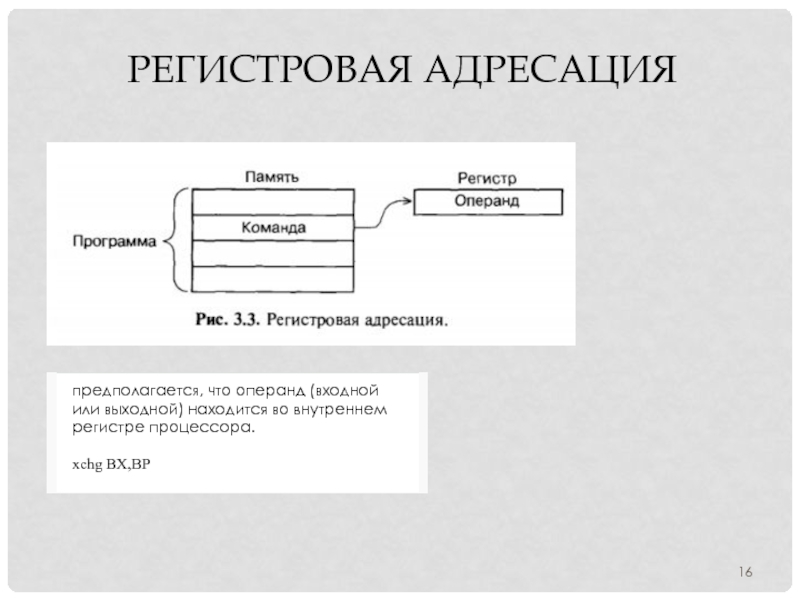

- 16. Регистровая адресация

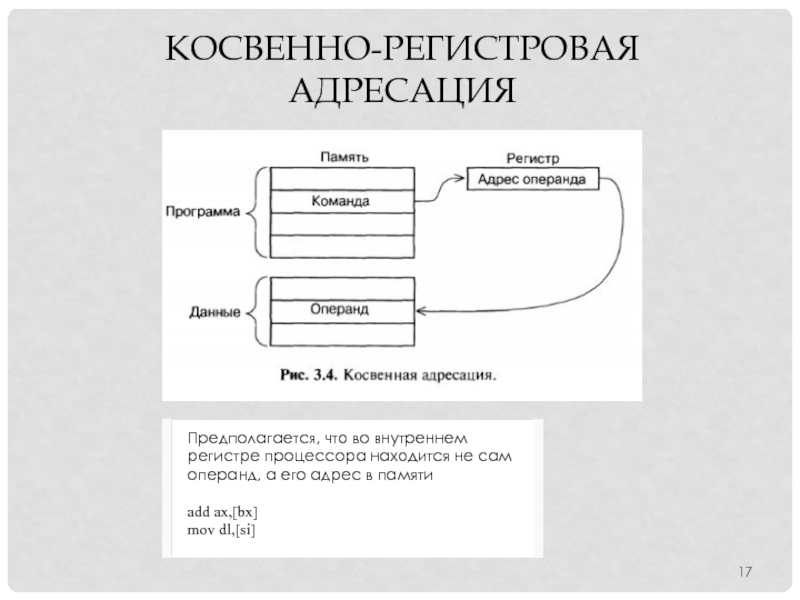

- 17. Косвенно-регистровая адресация

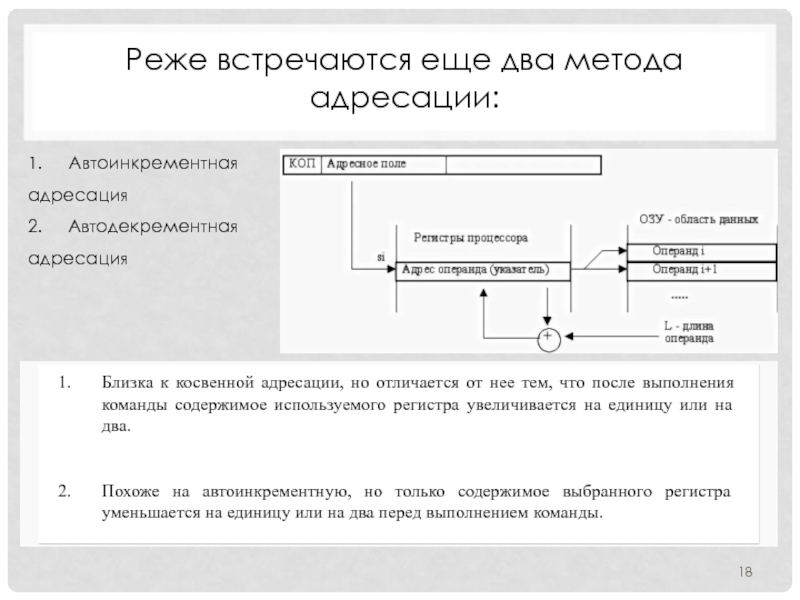

- 18. Реже встречаются еще два метода адресации:1. Автоинкрементная адресация2. Автодекрементная адресация

- 19. Скачать презентанцию

Цикл команды – это время, необходимое микропроцессору для выполнения отдельной команды

Слайды и текст этой презентации

Слайд 4 Большинство современных микроконтроллеров имеют Гарвардскую архитектуру и содержат 3 вида

памяти:

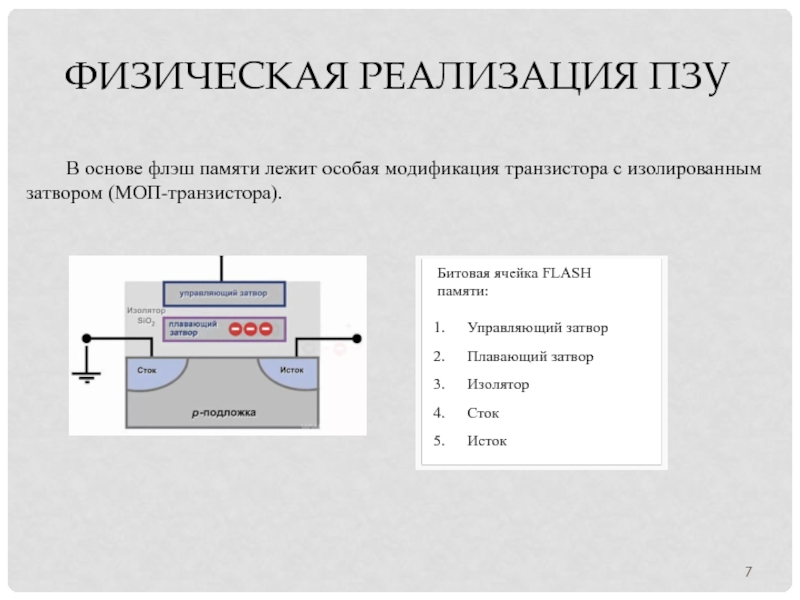

Регистры МКСлайд 7Физическая реализация ПЗУ

В основе флэш памяти лежит особая модификация транзистора

с изолированным затвором (МОП-транзистора).

Слайд 10Физическая реализация ОЗУ

Типичная ячейка статической двоичной памяти (двоичный триггер) на

КМОП-технологии.

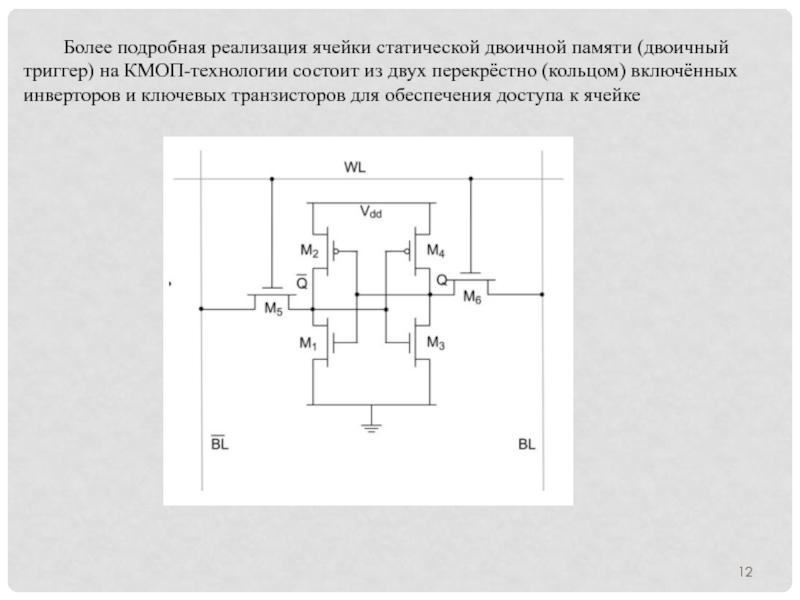

Слайд 12 Более подробная реализация ячейки статической двоичной памяти (двоичный триггер) на

КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых

транзисторов для обеспечения доступа к ячейкеСлайд 13Регистры МК

Регистры МК также выступают в качестве одного из видов

памяти

В число этих регистров входят обычно:

регистры процессора

регистры управления регистры, обеспечивающие ввод/вывод данных (регистры данных портов, регистры управления параллельным, последовательным или аналоговым вводом/выводом).