Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

hammer

Содержание

- 1. hammer

- 2. Блок-схема процессора AMD Hammer

- 3. Набор регистров процессора AMD Hammerдобавлено 8 регистров

- 4. Контроллер и туннельное устройство шины HyperTransportПереключатель в цепи устройств, объединенных шиной HyperTransportTMTM

- 5. Технология HyperTransportвысокоскоростная шина обмена данных между устройствами,

- 6. 1.Контроллер шины (host); является источником данных

- 7. Пример применения шины HyperTransportTMСостав чипсета AMD-8000AMD-8151; графический

- 8. Скачать презентанцию

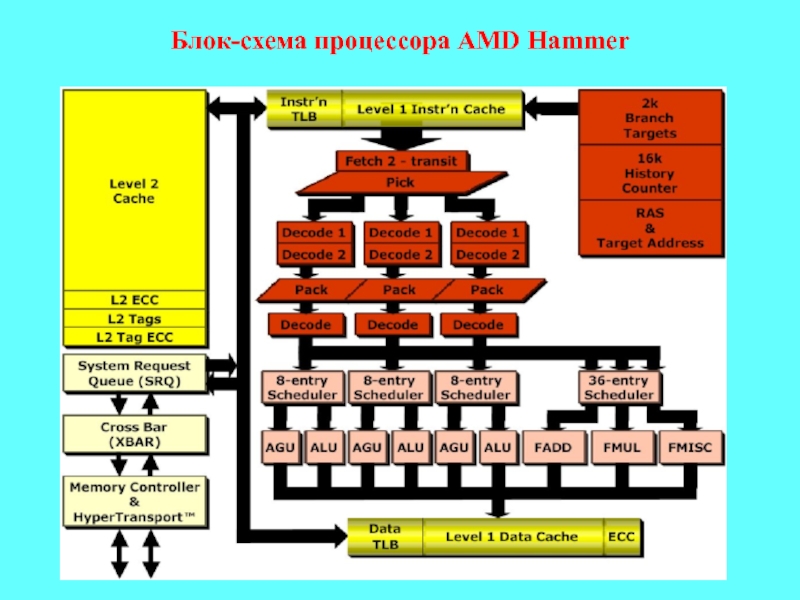

Блок-схема процессора AMD Hammer

Слайды и текст этой презентации

Слайд 1Архитектура процессора Hammer (сейчас «AMD64 Platform»)

Основные особенности

встроенный контроллер динамической памяти;

усовершенствованное

ядро микропроцессора;

Слайд 3Набор регистров процессора AMD Hammer

добавлено 8 регистров общего назначения (GPR)

R8-R15, используемых в 64-битном режиме;

расширены до 64 бит регистры EAX,

EBX и т. д.;добавлено 8 новых регистров в блок SSE (XMM8-XMM15).

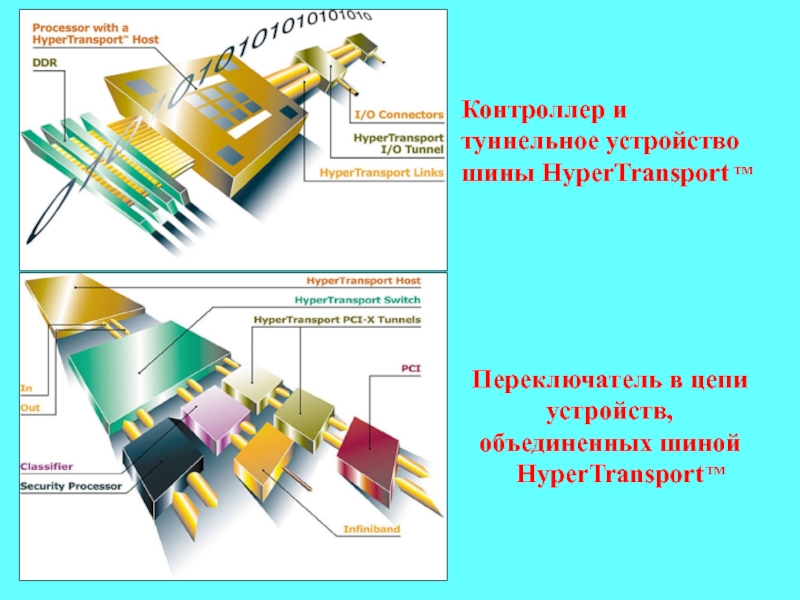

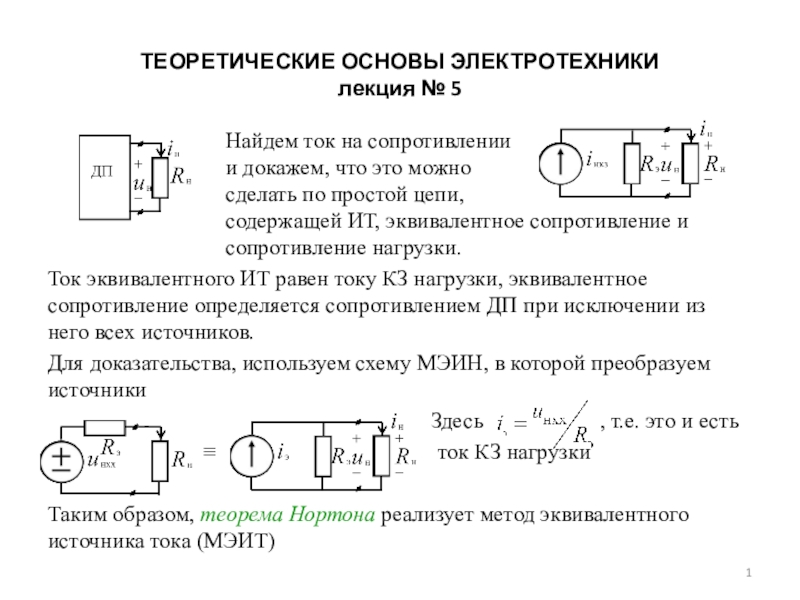

Слайд 4Контроллер и туннельное устройство шины HyperTransport

Переключатель в цепи устройств, объединенных

шиной HyperTransport

TM

TM

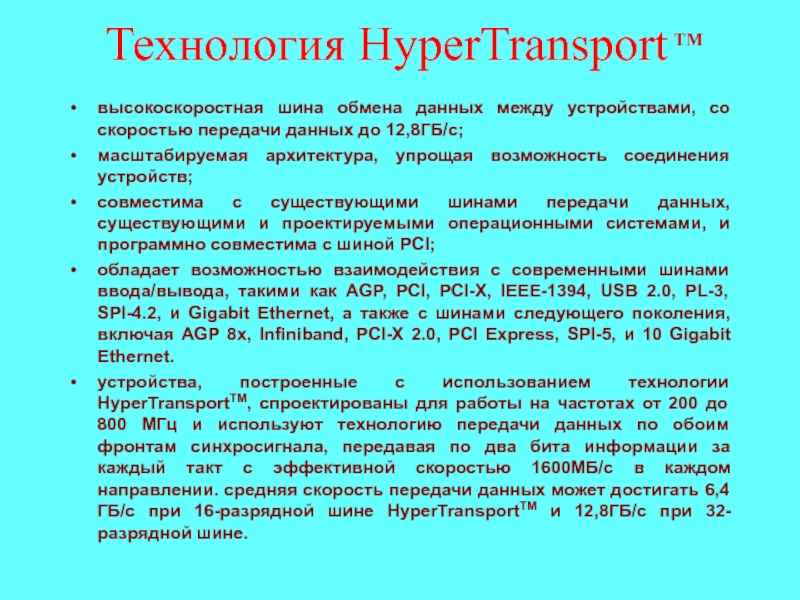

Слайд 5Технология HyperTransport

высокоскоростная шина обмена данных между устройствами, со скоростью передачи

данных до 12,8ГБ/с;

масштабируемая архитектура, упрощая возможность соединения устройств;

совместима с

существующими шинами передачи данных, существующими и проектируемыми операционными системами, и программно совместима с шиной PCI;обладает возможностью взаимодействия с современными шинами ввода/вывода, такими как AGP, PCI, PCI-X, IEEE-1394, USB 2.0, PL-3, SPI-4.2, и Gigabit Ethernet, а также с шинами следующего поколения, включая AGP 8x, Infiniband, PCI-X 2.0, PCI Express, SPI-5, и 10 Gigabit Ethernet.

устройства, построенные с использованием технологии HyperTransportTM, спроектированы для работы на частотах от 200 до 800 МГц и используют технологию передачи данных по обоим фронтам синхросигнала, передавая по два бита информации за каждый такт с эффективной скоростью 1600МБ/с в каждом направлении. средняя скорость передачи данных может достигать 6,4ГБ/с при 16-разрядной шине HyperTransportTM и 12,8ГБ/с при 32-разрядной шине.

TM

Слайд 6 1.Контроллер шины (host); является источником данных и сигналов для

других устройств – мостов, туннелей и конечных узлов. Обычно встраивается

в процессор (в северный мост).2.Туннель шины (tunnel); устройство с двумя контактами, входным и выходным, с функциональным устройством между ними. Туннель является основным соединительным блоком устройств HyperTransportTM. Команды, не адресованные туннельному устройству, транслируются через него далее по цепи.

3.Конечный узел (end device); образует конечную точку цепи HyperTransportTM. В шине HyperTransportTM конечные устройства не являются обязательными, так как в их качестве могут быть использованы туннельные устройства, что позволяет увеличить гибкость системы.

4.Концентратор (hub); микросхема южного моста, управляющая устройствами IDE и менее скоростными портами, включая последовательные и параллельные порты, USB, IEEE-1394 и т.д. С помощью моста к цепи устройств можно добавлять новые ветви, образуя древовидную структуру. Ветви могут иметь различную ширину входных и выходных каналов.

5.Переключатель (switch); управляет потоками ввода/вывода и организует внутреннее соединение подключенных к шине HyperTransportTM устройств. Контроллер непосредственно взаимодействует с переключателем, который обслуживает множество независимых подчиненных устройств, включая туннельные устройства, мосты и конечные устройства цепи, в порядке очередности. Для исходящих потоков данных переключатель является ведущим узлом этой цепи; переключатель может соединяться с несколькими контроллерами и логически разделять структуру на подмножества, доступные для различных контроллеров. Переключатель поддерживает “горячее” подключение устройств.

6.Мост (bridge).

Состав шины HyperTransportTM

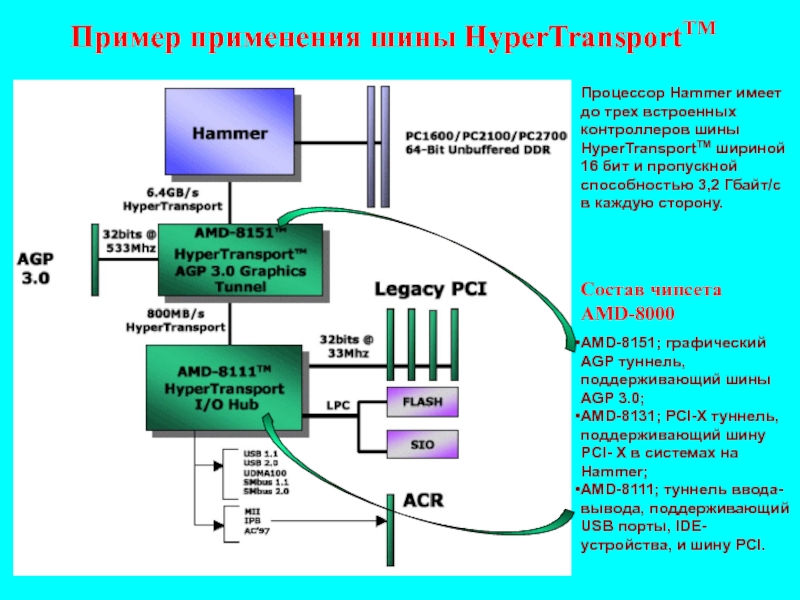

Слайд 7Пример применения шины HyperTransportTM

Состав чипсета AMD-8000

AMD-8151; графический AGP туннель, поддерживающий

шины AGP 3.0;

AMD-8131; PCI-X туннель, поддерживающий шину PCI- X

в системах на Hammer; AMD-8111; туннель ввода-вывода, поддерживающий USB порты, IDE-устройства, и шину PCI.

Процессор Hammer имеет до трех встроенных контроллеров шины HyperTransportTM шириной 16 бит и пропускной способностью 3,2 Гбайт/с в каждую сторону.