Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Лекция 4

Содержание

- 1. Лекция 4

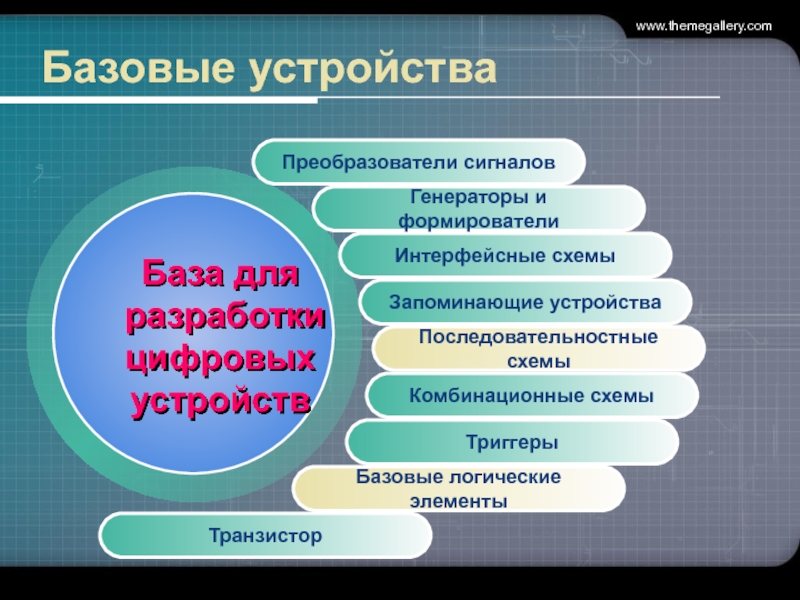

- 2. www.themegallery.comБазовые устройстваЗапоминающие устройстваПоследовательностные схемыКомбинационные схемыБазовые логические элементыТранзисторБаза для разработкицифровыхустройствИнтерфейсные схемыТриггерыГенераторы и формирователиПреобразователи сигналов

- 3. www.themegallery.comУсловное обозначение ЛЭ&Обозначение функцииИнверсияИ, ИЛИ, НЕ –

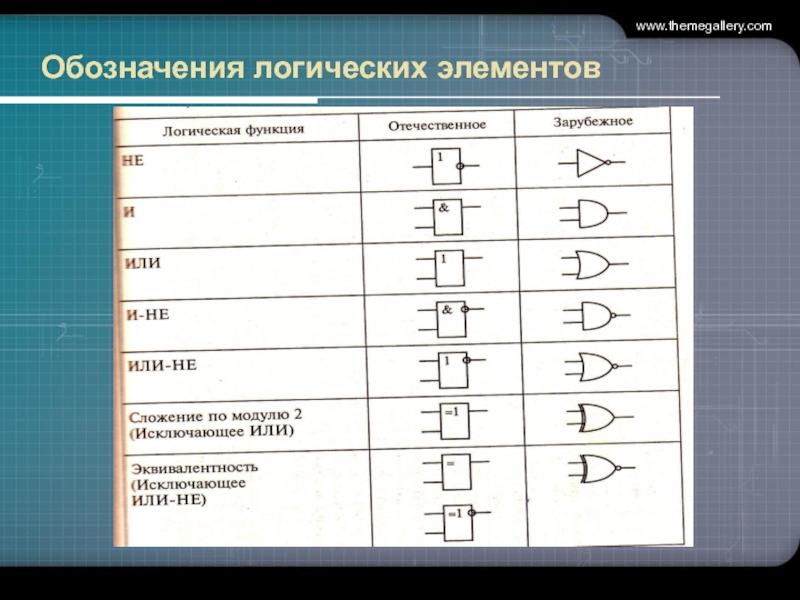

- 4. www.themegallery.comОбозначения логических элементов

- 5. www.themegallery.comСигналы отображающие логические переменныеБИТ 1

- 6. www.themegallery.comУчет задержек в логических схемахБыстродействие в ЛЭ

- 7. www.themegallery.comСтатические параметры ЛЭНапряжение питанияС определенным допускомЧетыре значения

- 8. www.themegallery.comТоковые статические параметры ЛЭТок потребляемый по входу

- 9. www.themegallery.comНагрузочная способность ЛЭЭто количество ЛЭ, которые можно

- 10. www.themegallery.comБыстродействие цифровых схемСкорость перехода из одного состояния

- 11. www.themegallery.comМощность потребления ЛЭВ справочниках обычно указывается значение

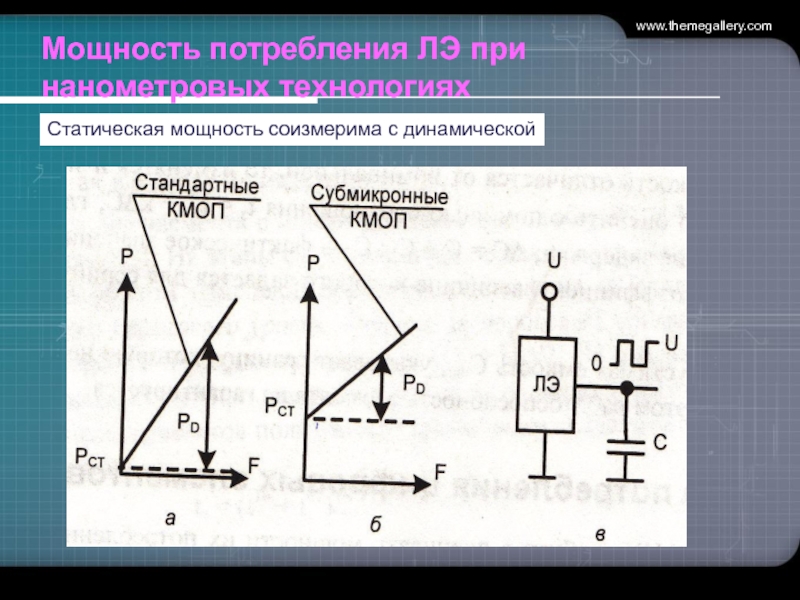

- 12. www.themegallery.comМощность потребления ЛЭ при нанометровых технологияхСтатическая мощность соизмерима с динамической

- 13. www.themegallery.comФормула оценки динамической мощностиПерепад логического уровняЧастота сигналов на входе и выходеЧисло переключаемых выходовЕмкость нагрузкиВнутренняя емкость схемы

- 14. www.themegallery.comПараметры ЛЭ ТТЛ

- 15. www.themegallery.comПараметры ЛЭ ТТЛК1344И-НЕ

- 16. www.themegallery.comЛогический элемент как основа интегральных схем

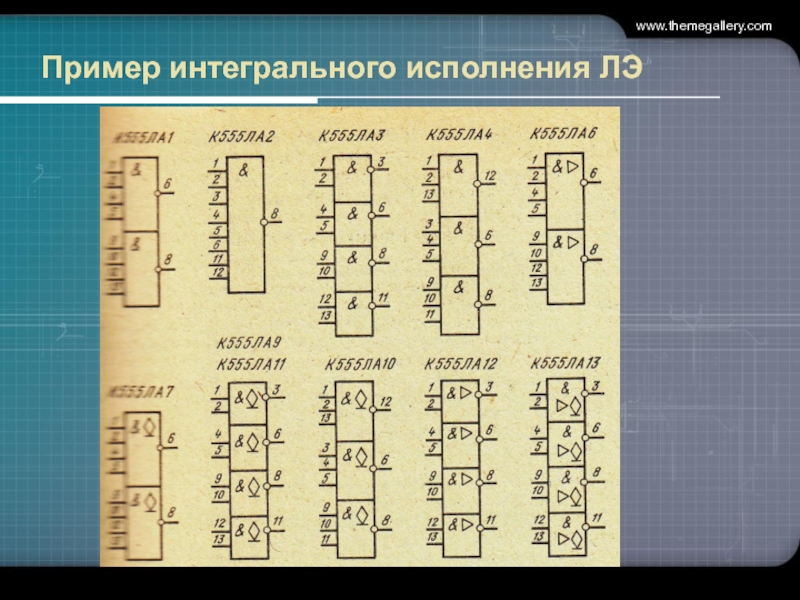

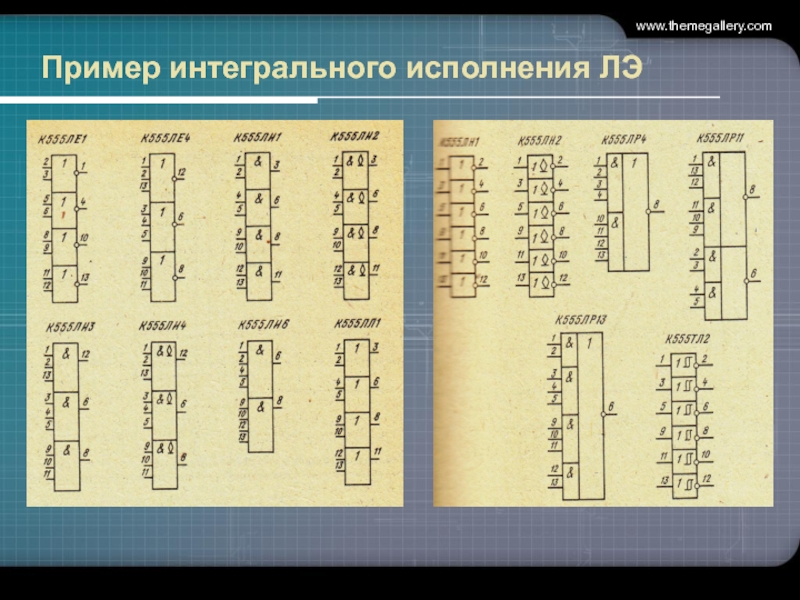

- 17. www.themegallery.comПример интегрального исполнения ЛЭ

- 18. www.themegallery.comПример интегрального исполнения ЛЭ

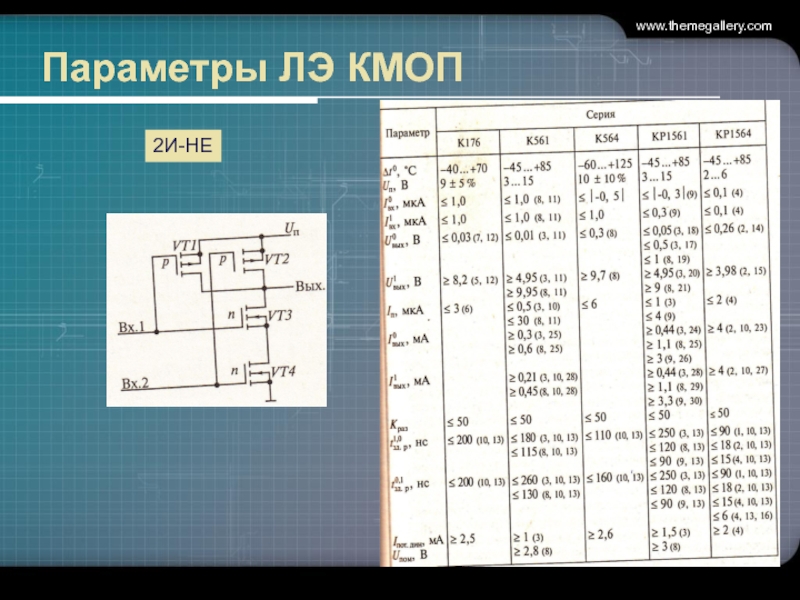

- 19. www.themegallery.comПараметры ЛЭ КМОП2И-НЕ

- 20. www.themegallery.comТипы выходов цифровых элементовЛогические;С третьим состоянием;Открытые (с

- 21. www.themegallery.comЛогический выходХорошо, когда он имеет малое сопротивление

- 22. www.themegallery.comВыход с тремя состояниямиПозволяют использовать одну линию

- 23. www.themegallery.comОткрытые выходыТребуется подключение внешних резисторов для исключения

- 24. www.themegallery.comКомбинационные схемыКС - это схемы без элементов памяти3. Мультиплексоры4. Демультиплексоры.1. Дешифраторы2. ШифраторыКСх1хny1yn5. Сумматоры.6. АЛУ.7. Компараторы

- 25. www.themegallery.comДешифратор Это устройство, при подаче на вход

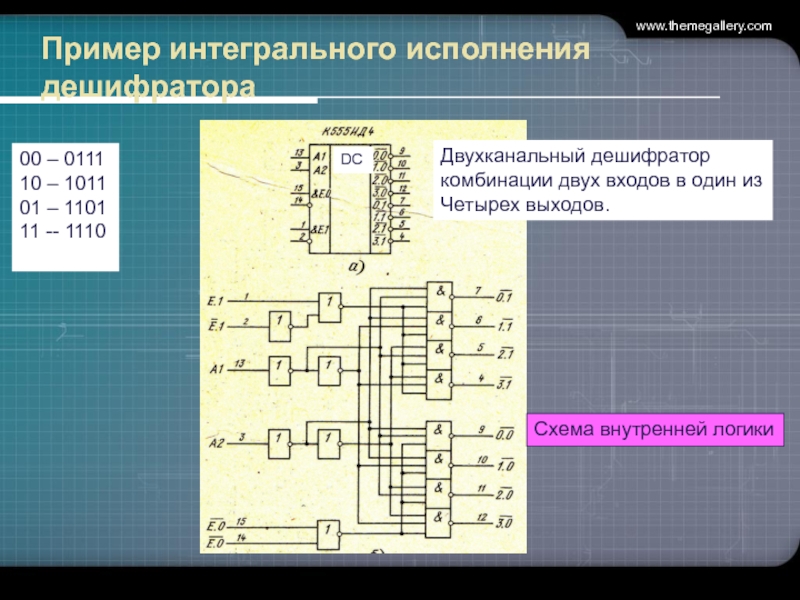

- 26. www.themegallery.comПример интегрального исполнения дешифратораDCСхема внутренней логикиДвухканальный дешифраторкомбинации

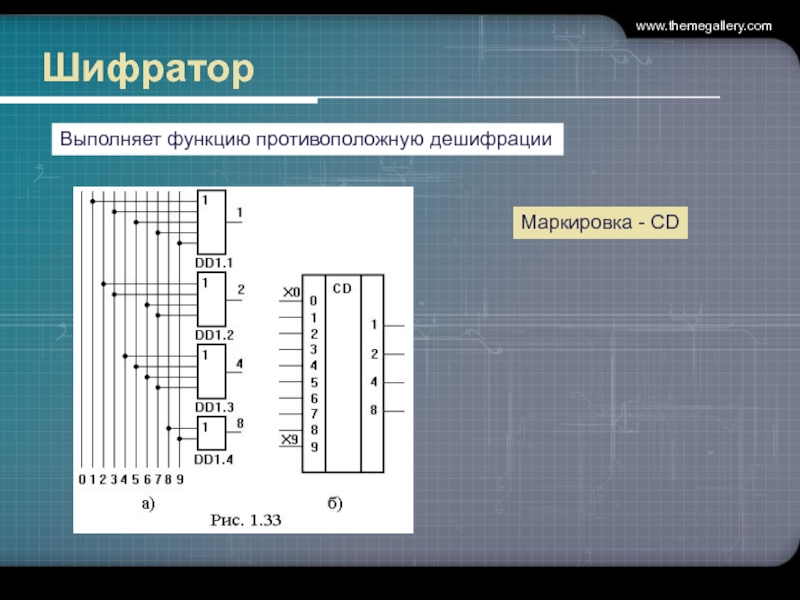

- 27. www.themegallery.comШифраторВыполняет функцию противоположную дешифрацииМаркировка - CD

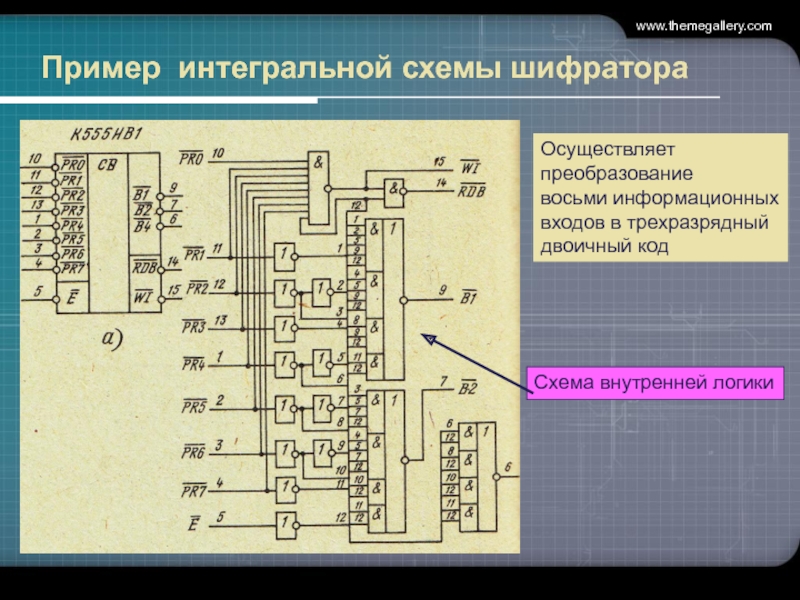

- 28. www.themegallery.comПример интегральной схемы шифратораОсуществляетпреобразованиевосьми информационныхвходов в трехразрядный двоичный кодСхема внутренней логики

- 29. www.themegallery.comМультиплексор и демультиплексорВход подключить к одному из N -выходовОдин из N входов подключить к выходу

- 30. www.themegallery.comПример интегрального исполнения мультиплексораСхема внутренней логики

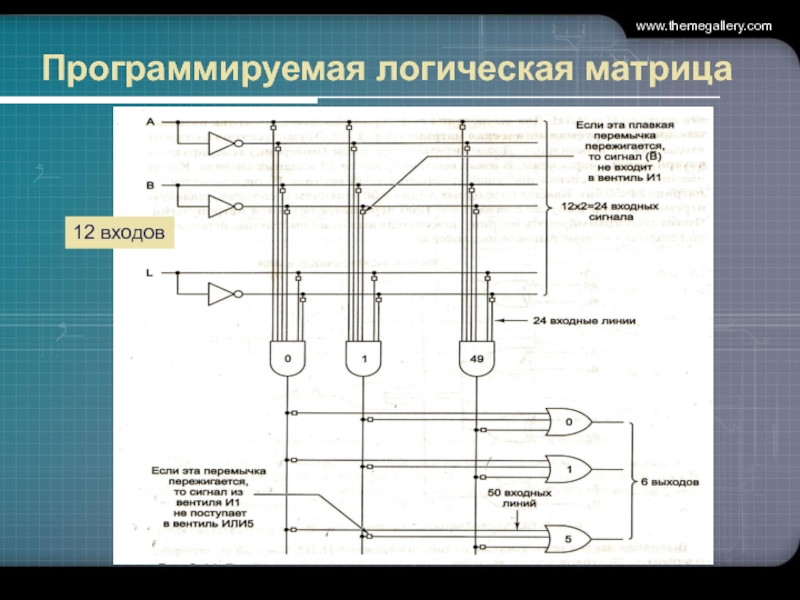

- 31. www.themegallery.comПрограммируемая логическая матрица12 входов

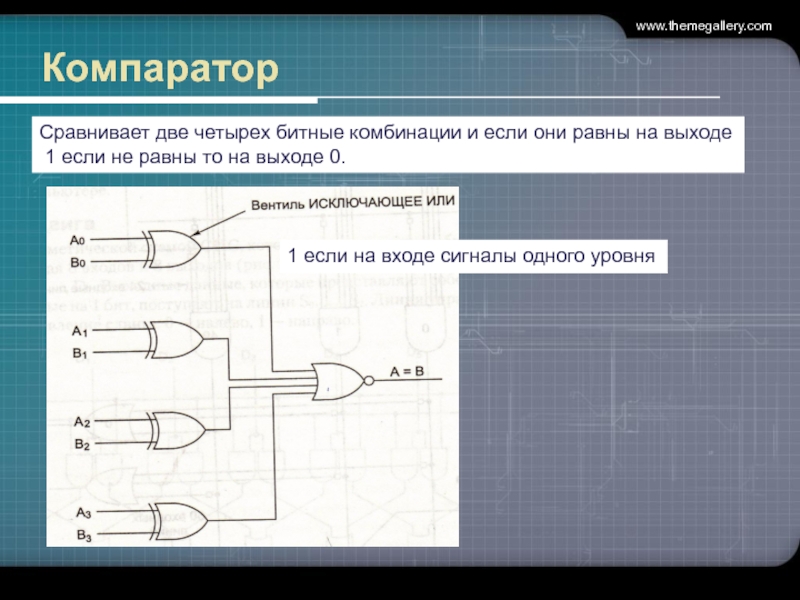

- 32. www.themegallery.comКомпараторСравнивает две четырех битные комбинации и если

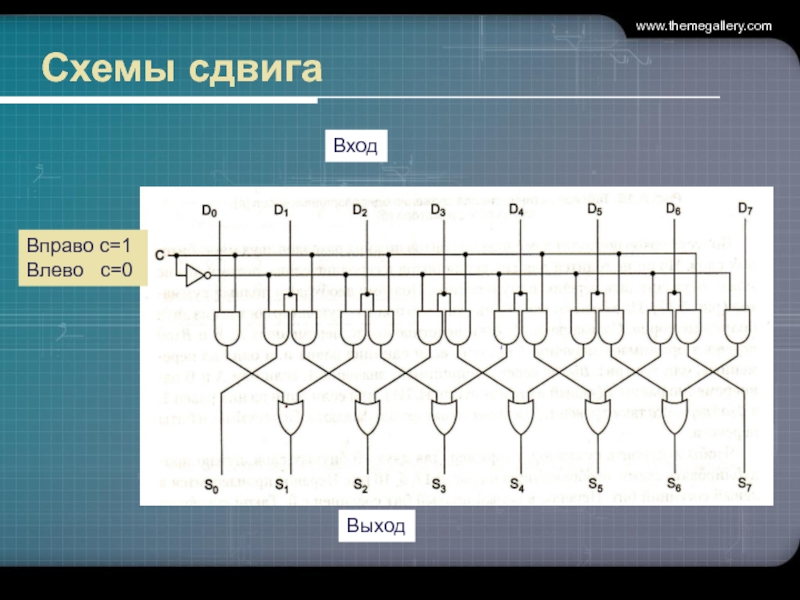

- 33. www.themegallery.comСхемы сдвигаВходВыходВправо с=1Влево с=0

- 34. www.themegallery.comСумматорАБВПолусумматорПолный сумматор

- 35. www.themegallery.comАЛУДанная схема может выполнять 4 функции: АВ, А+В, не В, А+ВЗадают типфункцииВходныеРазрешениеОдноразрядная микропроцессорнаясекция

- 36. www.themegallery.comВосьмиразрядное АЛУНа базе микропроцессорной секции

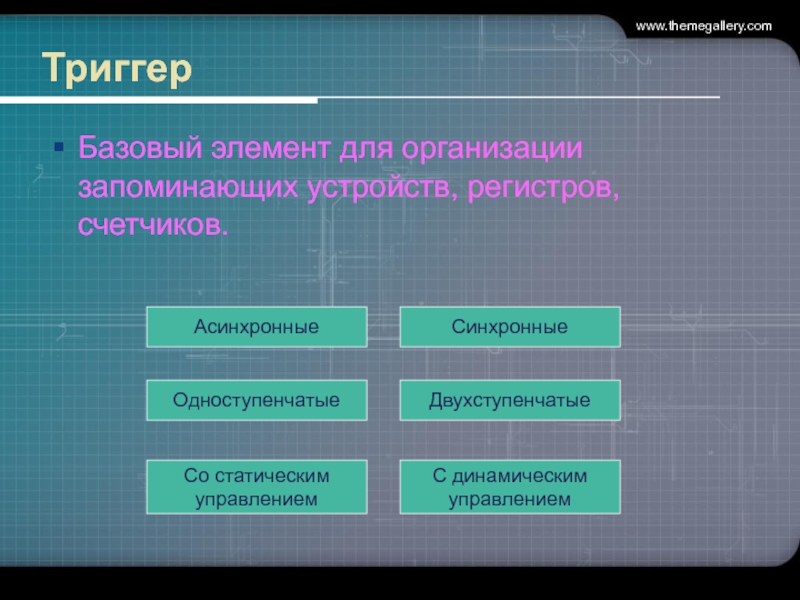

- 37. www.themegallery.comТриггерБазовый элемент для организации запоминающих устройств, регистров, счетчиков.АсинхронныеСинхронныеДвухступенчатыеОдноступенчатыеСо статическимуправлениемС динамическим управлением

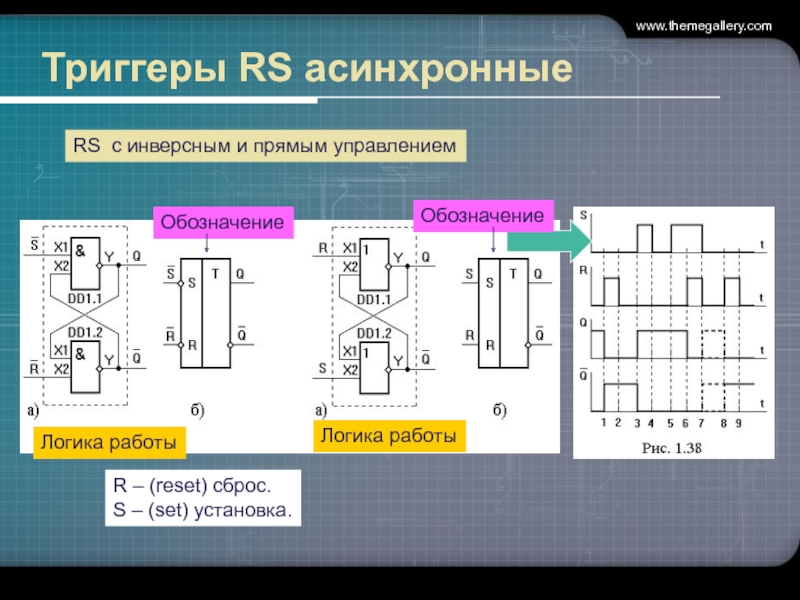

- 38. www.themegallery.comТриггеры RS асинхронныеRS с инверсным и прямым управлениемЛогика работыОбозначениеЛогика работыОбозначениеR – (reset) сброс.S – (set) установка.

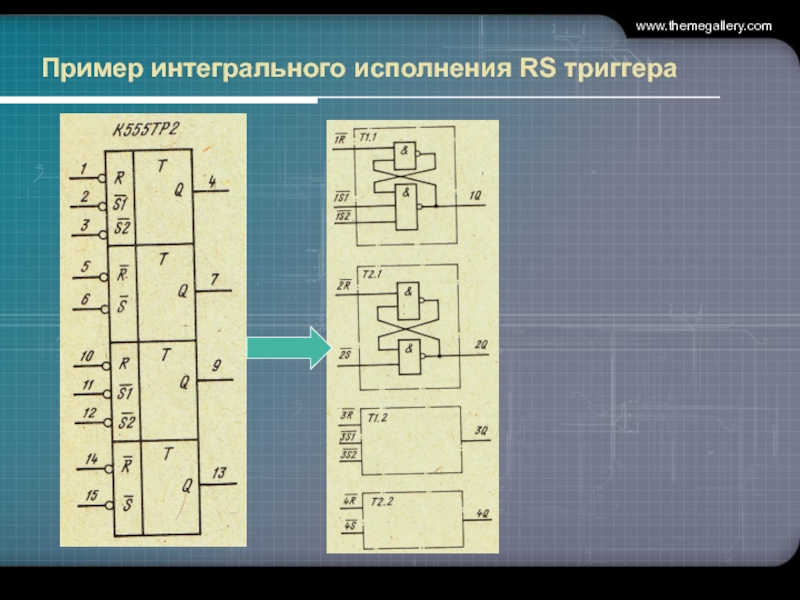

- 39. www.themegallery.comПример интегрального исполнения RS триггера

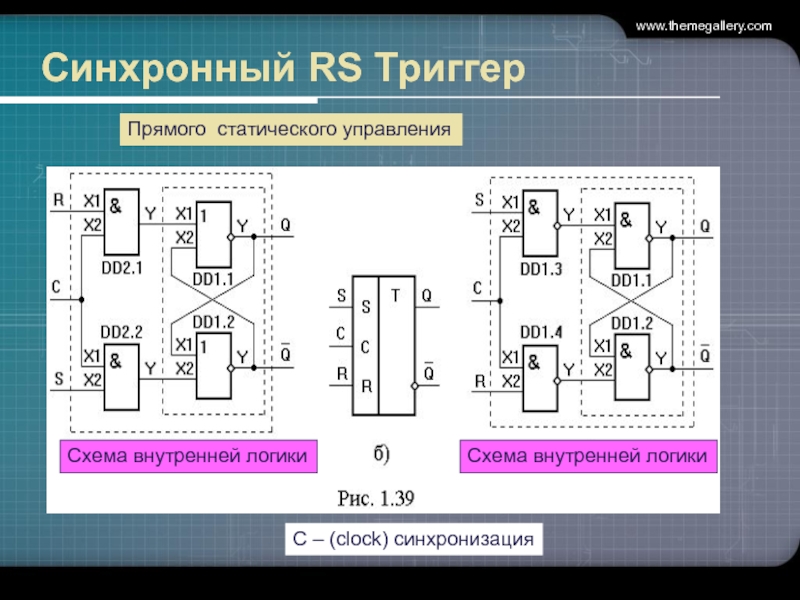

- 40. www.themegallery.comСинхронный RS ТриггерПрямого статического управленияСхема внутренней логикиСхема внутренней логикиC – (clock) синхронизация

- 41. www.themegallery.comСинхронный RS триггерС инверсным, динамическим управлением по переднему фронту сигнала ССхема внутренней логики

- 42. www.themegallery.comСинхронный RS с динамическим управлениемДинамическое управление по заднему фронту сигнала ССхема внутренней логики

- 43. www.themegallery.comD триггер - одноступенчатыйОснова построения регистров Ячейка памятиСхема внутренней логикиСхема внутренней логики

- 44. www.themegallery.comD триггер с входом условияСхема внутренней логики

- 45. www.themegallery.comD триггер с динамическим управлениемС управлением по переднему фронтуСчетный триггер – основа построениясчетчиков.

- 46. www.themegallery.comДвухтактные RS триггерыСчетный триггерМастер - masterИсполнитель - slaveMS триггер

- 47. www.themegallery.comУниверсальный JK триггерУстраняет неопределенность возникающую при одновременном снятиисигналов с входов R и S

- 48. www.themegallery.comJK с динамическим управлением

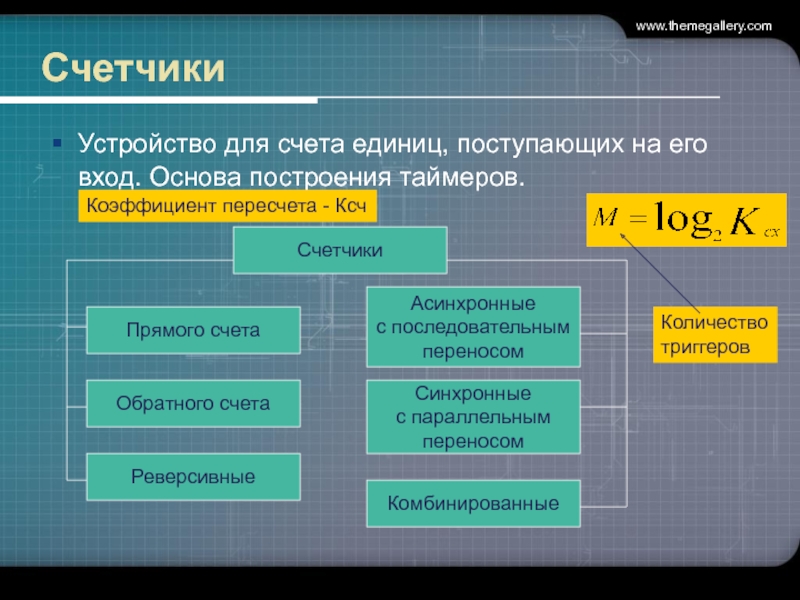

- 49. www.themegallery.comСчетчикиУстройство для счета единиц, поступающих на его

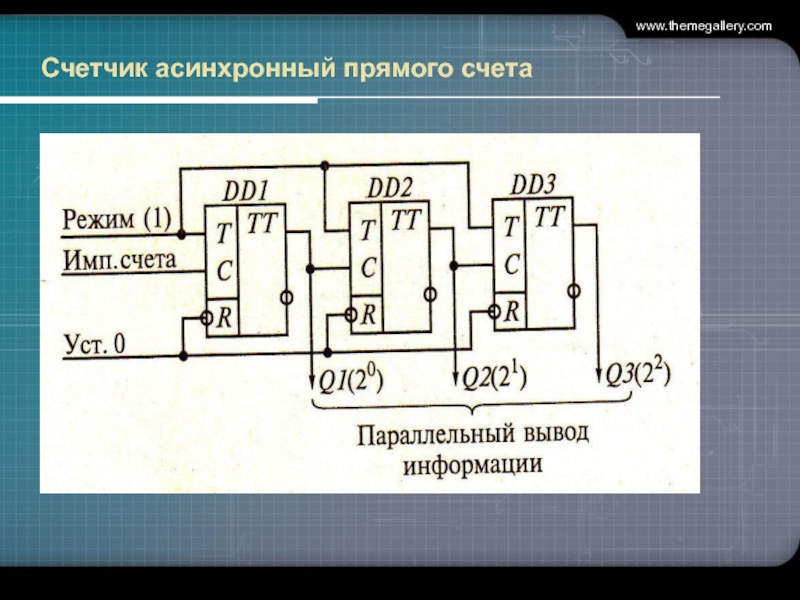

- 50. www.themegallery.comСчетчик асинхронный прямого счета

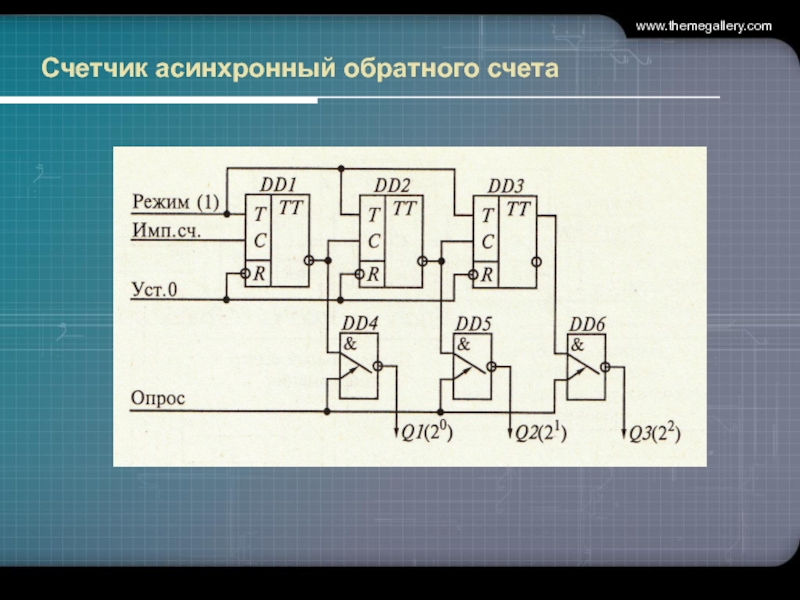

- 51. www.themegallery.comСчетчик асинхронный обратного счета

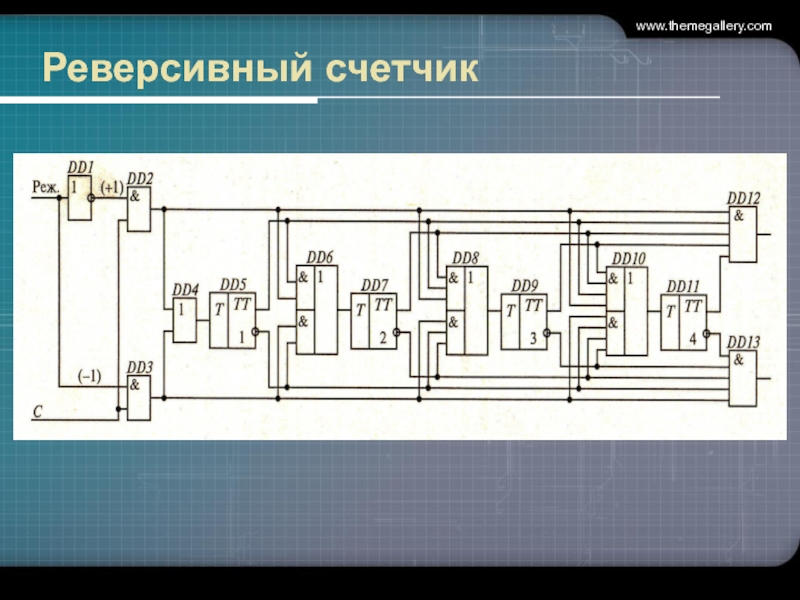

- 52. www.themegallery.comРеверсивный счетчик

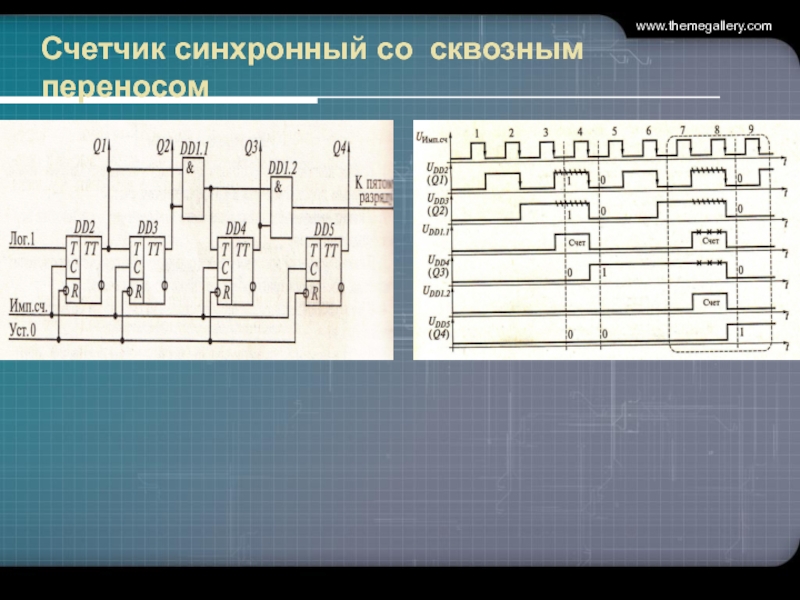

- 53. www.themegallery.comСчетчик синхронный со сквозным переносом

- 54. www.themegallery.comСинхронный счетчик с параллельным переносомОсуществляется выявление возможного состояния триггера старшегоразряда путем анализа младших разрядов.

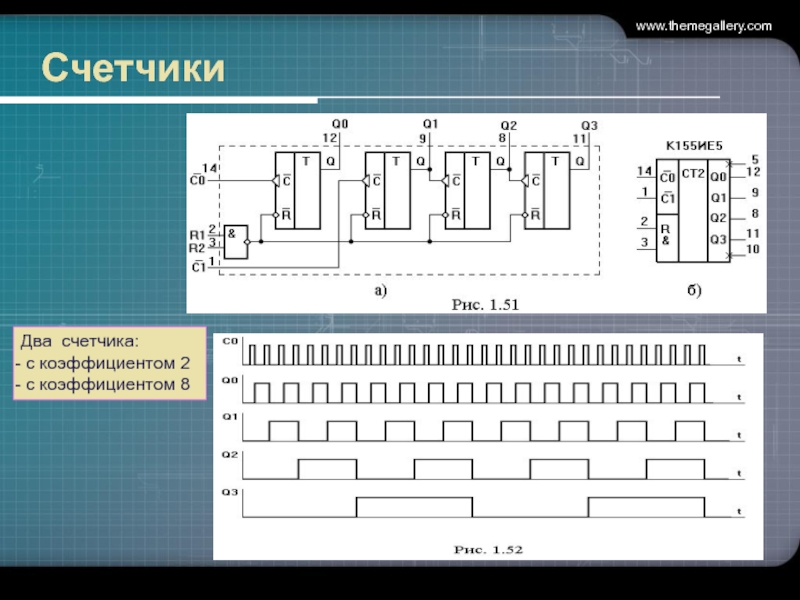

- 55. www.themegallery.comСчетчики Два счетчика: с коэффициентом 2 с коэффициентом 8

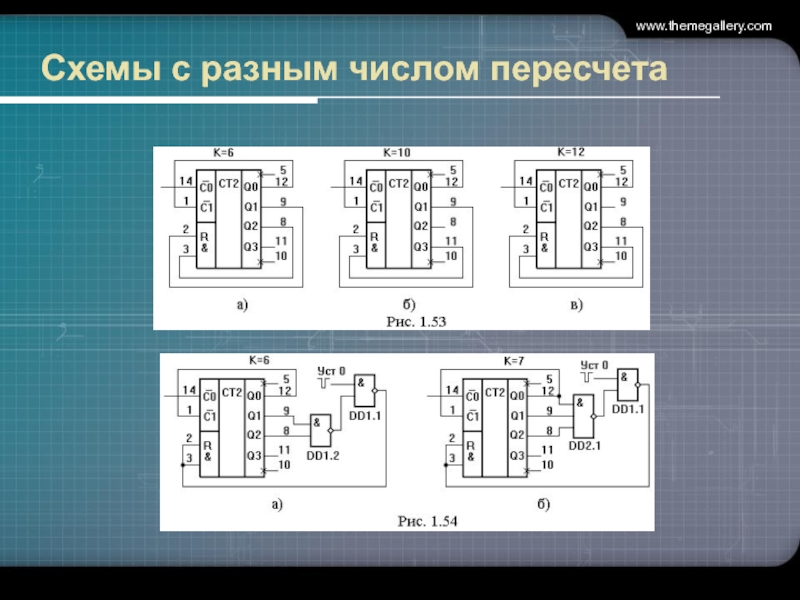

- 56. www.themegallery.comСхемы с разным числом пересчета

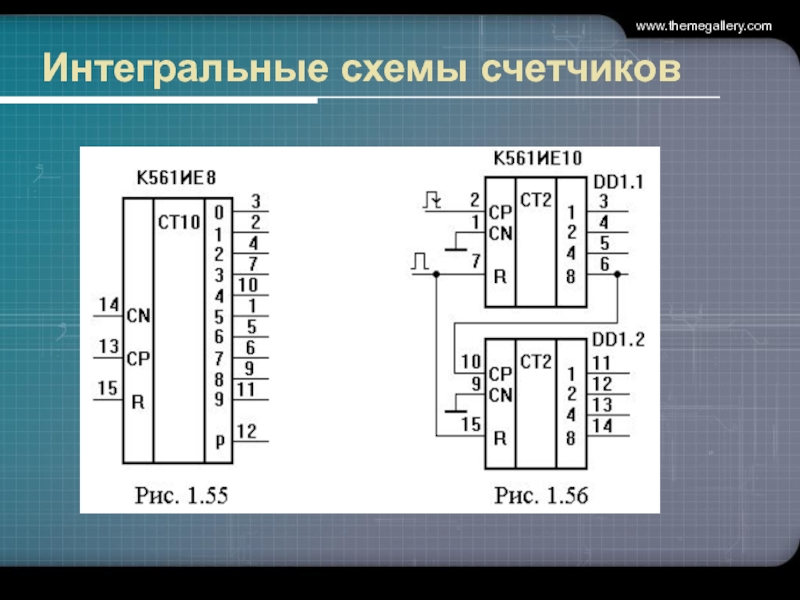

- 57. www.themegallery.comИнтегральные схемы счетчиков

- 58. www.themegallery.comРегистрыПредназначен для приема, хранения и передачи информации.ПоследовательныеПараллельныеПоследовательно-параллельные

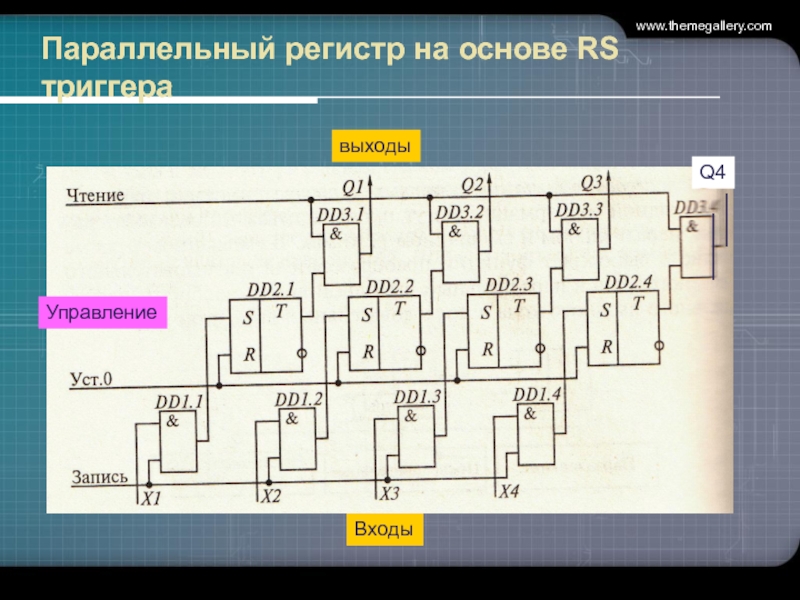

- 59. www.themegallery.comПараллельный регистр на основе RS триггеравыходыВходыQ4Управление

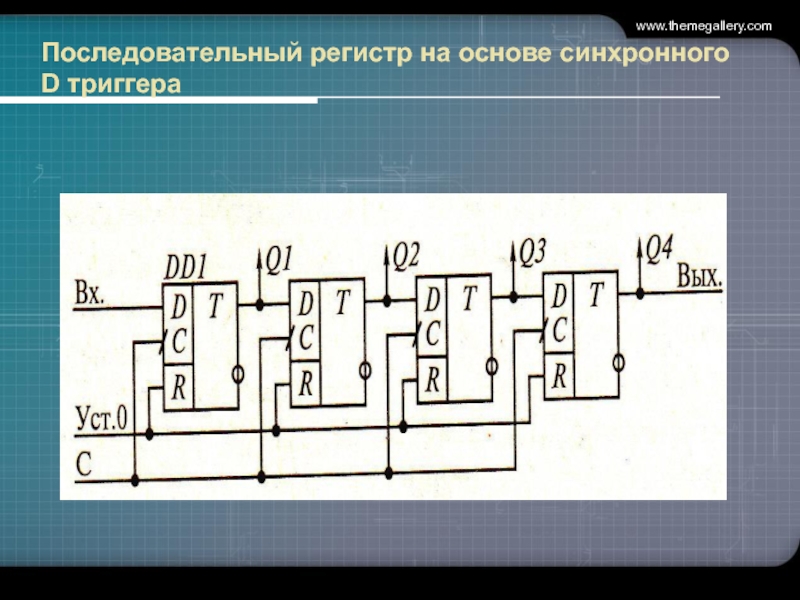

- 60. www.themegallery.comПоследовательный регистр на основе синхронного D триггера

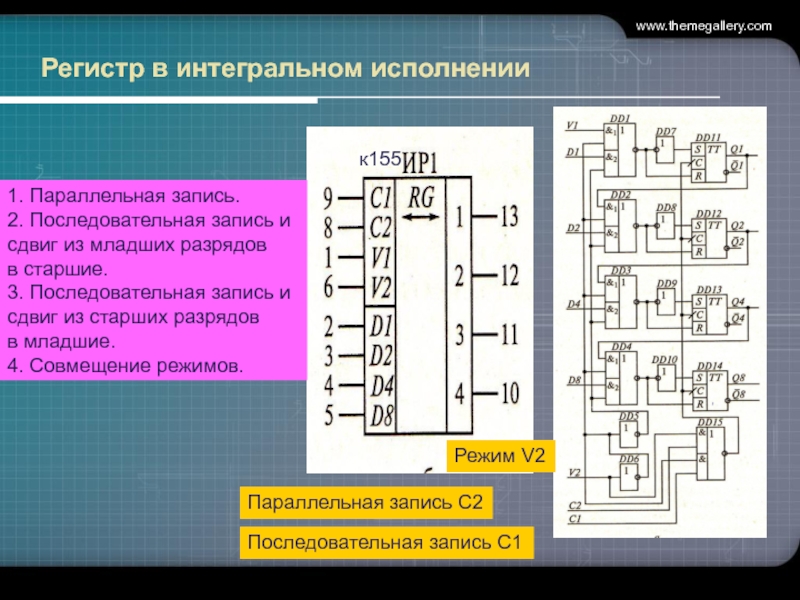

- 61. www.themegallery.comРегистр в интегральном исполнении1. Параллельная запись.2. Последовательная

- 62. Click to edit subtitle styleThank You !

- 63. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2www.themegallery.com

Базовые устройства

Запоминающие устройства

Последовательностные схемы

Комбинационные схемы

Базовые логические элементы

Транзистор

База для

разработки

цифровых

устройств

Интерфейсные схемы

Триггеры

Генераторы

и формирователи

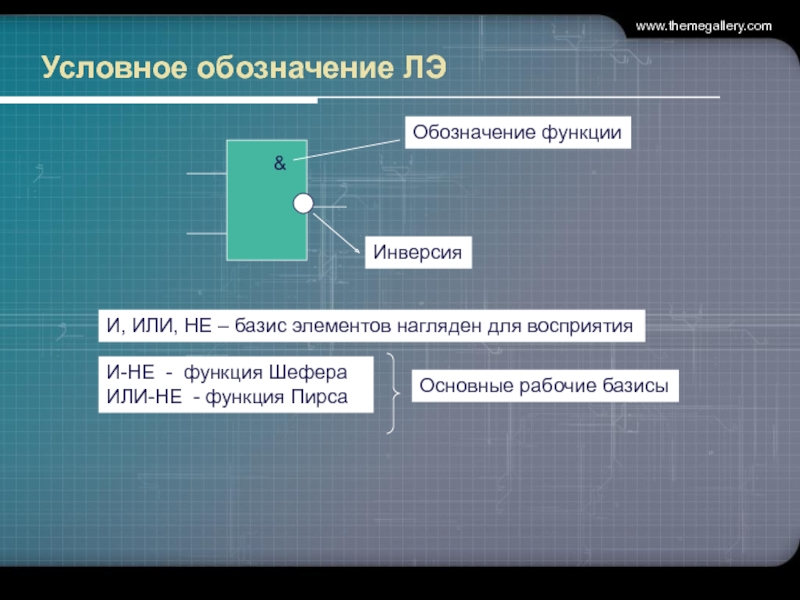

Слайд 3www.themegallery.com

Условное обозначение ЛЭ

&

Обозначение функции

Инверсия

И, ИЛИ, НЕ – базис элементов нагляден

для восприятия

И-НЕ - функция Шефера

ИЛИ-НЕ - функция Пирса

Основные

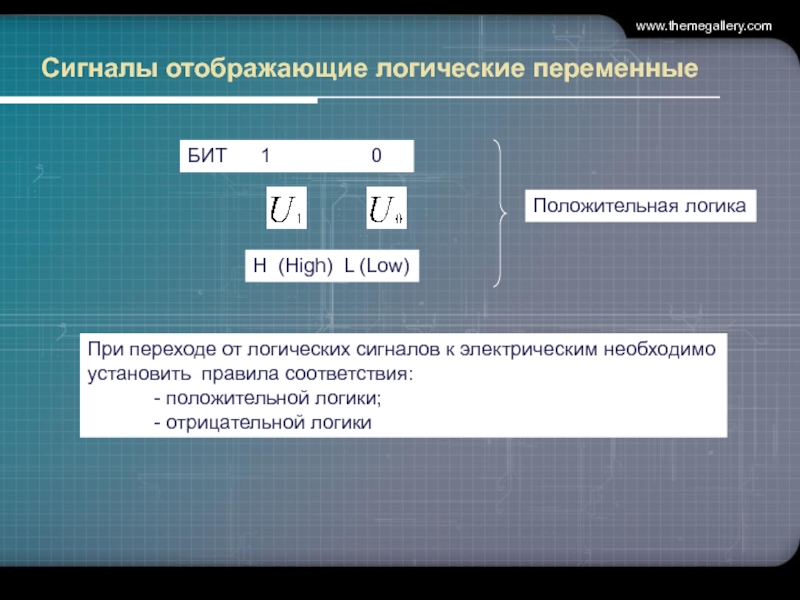

рабочие базисыСлайд 5www.themegallery.com

Сигналы отображающие логические переменные

БИТ 1

0

H (High) L

(Low)При переходе от логических сигналов к электрическим необходимо

установить правила соответствия:

- положительной логики;

- отрицательной логики

Положительная логика

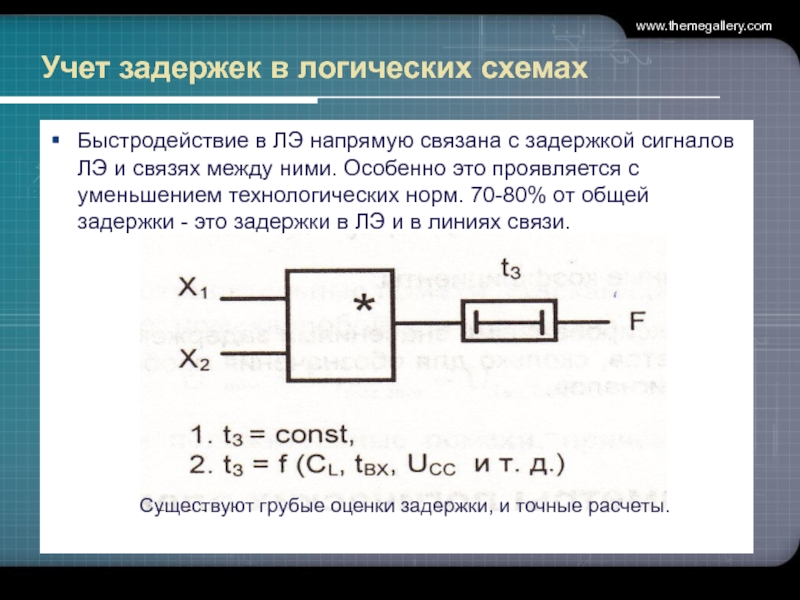

Слайд 6www.themegallery.com

Учет задержек в логических схемах

Быстродействие в ЛЭ напрямую связана с

задержкой сигналов ЛЭ и связях между ними. Особенно это проявляется

с уменьшением технологических норм. 70-80% от общей задержки - это задержки в ЛЭ и в линиях связи.Существуют грубые оценки задержки, и точные расчеты.

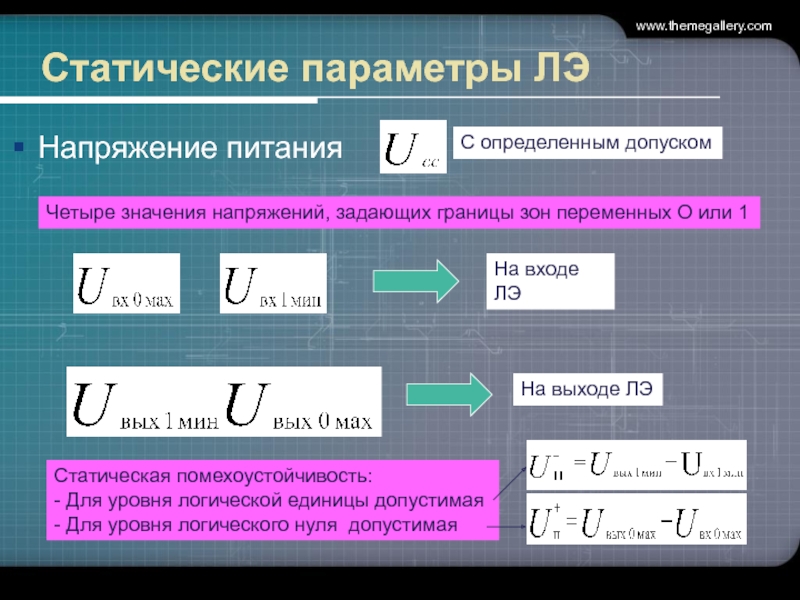

Слайд 7www.themegallery.com

Статические параметры ЛЭ

Напряжение питания

С определенным допуском

Четыре значения напряжений, задающих границы

зон переменных О или 1

На входе ЛЭ

На выходе ЛЭ

Статическая помехоустойчивость:

-

Для уровня логической единицы допустимая - Для уровня логического нуля допустимая

Слайд 8www.themegallery.com

Токовые статические параметры ЛЭ

Ток потребляемый по входу при вх=1

Ток потребляемый

по входу при вх=0

Ток потребляемый по выходу при вых=1

Ток потребляемый

по выходу при вых=0Например: для КМОП ЛЭ ток вых.1= току вых.0

для ТТЛШ ЛЭ ток вых.1 в 20 раз меньше тока вых.0

Слайд 9www.themegallery.com

Нагрузочная способность ЛЭ

Это количество ЛЭ, которые можно подключить одному выходу

ЛЭ.

Иногда применяют термин:

Разветвление по выходу

Объединение по входу

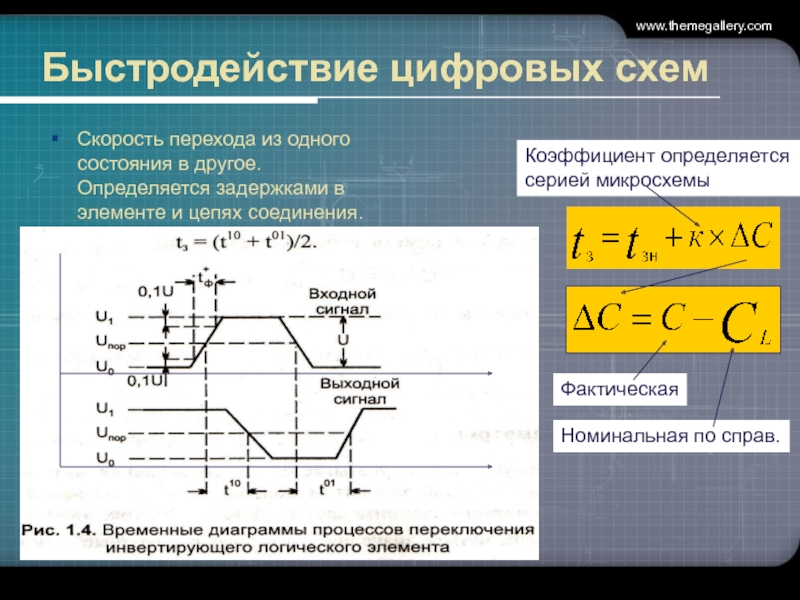

Слайд 10www.themegallery.com

Быстродействие цифровых схем

Скорость перехода из одного состояния в другое. Определяется

задержками в элементе и цепях соединения.

Коэффициент определяется

серией микросхемы

Фактическая

Номинальная по справ.

Слайд 11www.themegallery.com

Мощность потребления ЛЭ

В справочниках обычно указывается значение тока потребляемого микросхемой

– I потр. * U пит.= P

Мощность ЛЭ делят на

статическую и динамическуюРст. – мощность потребляемая в пассивном состоянии.

Рдин. – мощность потребляемая при переключении.

Рст. делится на Рст. 0 и Рст. 1 Рст.

и расчитывается Рст. =(Рст.0 + Рст.1)/2

Р = Рст. + Рдин.

Слайд 12www.themegallery.com

Мощность потребления ЛЭ при нанометровых технологиях

Статическая мощность соизмерима с динамической

Слайд 13www.themegallery.com

Формула оценки динамической мощности

Перепад логического уровня

Частота сигналов на входе и

выходе

Число переключаемых выходов

Емкость нагрузки

Внутренняя емкость схемы

Слайд 20www.themegallery.com

Типы выходов цифровых элементов

Логические;

С третьим состоянием;

Открытые (с открытым стоком или

коллектором).

Применение объясняется различными условиями работы элементов

в логических цепях, магистральных

системах.Слайд 21www.themegallery.com

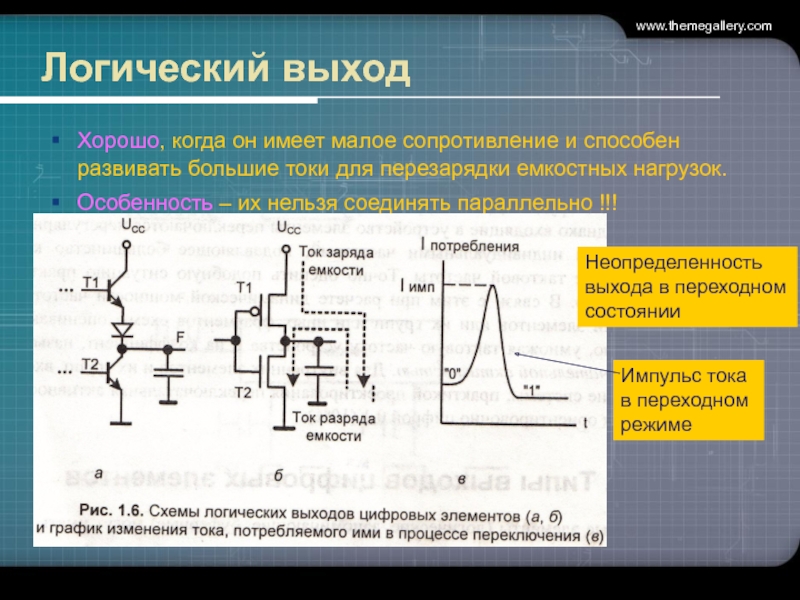

Логический выход

Хорошо, когда он имеет малое сопротивление и способен развивать

большие токи для перезарядки емкостных нагрузок.

Особенность – их нельзя соединять

параллельно !!!Неопределенность

выхода в переходном

состоянии

Импульс тока

в переходном

режиме

Слайд 22www.themegallery.com

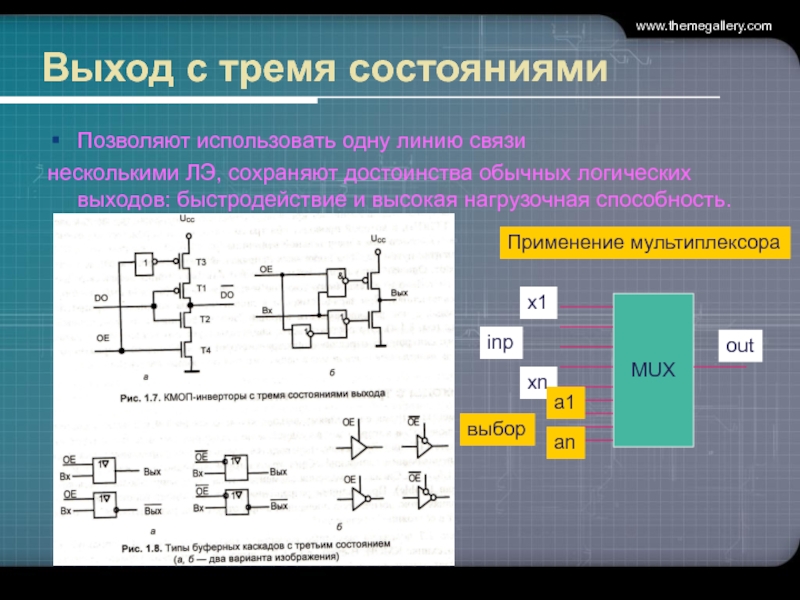

Выход с тремя состояниями

Позволяют использовать одну линию связи

несколькими ЛЭ, сохраняют

достоинства обычных логических выходов: быстродействие и высокая нагрузочная способность.

MUX

x1

xn

a1

an

out

inp

выбор

Применение мультиплексора

Слайд 23www.themegallery.com

Открытые выходы

Требуется подключение внешних резисторов для исключения плавающего состояния выхода.

Реализуется

схема монтажной логики – высокое напряжение на выходе возникает только

при запирании всех транзисторов.Может заменить схему с тремя состояниями при работе на магистраль – вместо сигнала ОЕ используют один из входов.

Достоинства – защищенность

от повреждений при ошибках

Управления.

Недостаток – большая

задержка переключения.

Обозначение

Слайд 24www.themegallery.com

Комбинационные схемы

КС - это схемы без элементов памяти

3. Мультиплексоры

4. Демультиплексоры.

1.

Дешифраторы

2. Шифраторы

КС

х1

хn

y1

yn

5. Сумматоры.

6. АЛУ.

7. Компараторы

Слайд 25www.themegallery.com

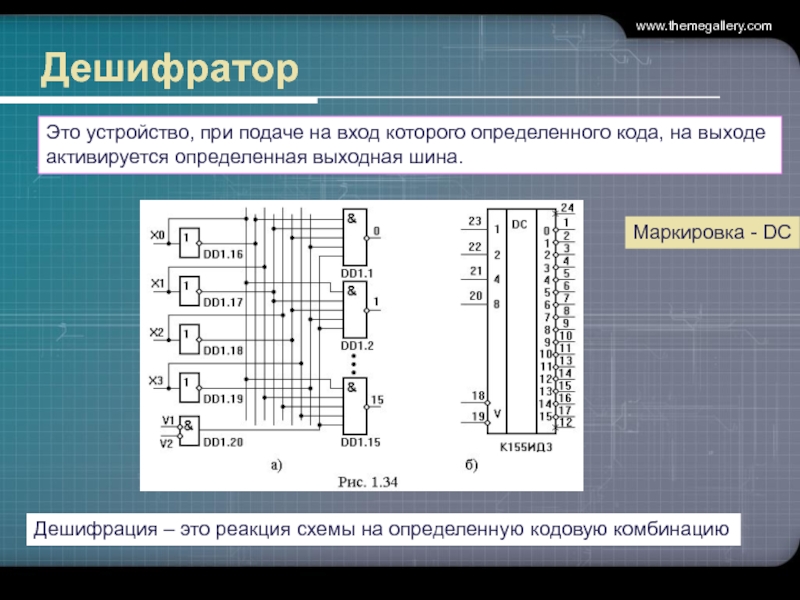

Дешифратор

Это устройство, при подаче на вход которого определенного кода,

на выходе

активируется определенная выходная шина.

Дешифрация – это реакция схемы на

определенную кодовую комбинациюМаркировка - DC

Слайд 26www.themegallery.com

Пример интегрального исполнения дешифратора

DC

Схема внутренней логики

Двухканальный дешифратор

комбинации двух входов в

один из

Четырех выходов.

00 – 0111

10 – 1011

01 – 1101

11 --

1110Слайд 28www.themegallery.com

Пример интегральной схемы шифратора

Осуществляет

преобразование

восьми информационных

входов в трехразрядный

двоичный код

Схема внутренней

логики

Слайд 29www.themegallery.com

Мультиплексор и демультиплексор

Вход подключить к одному из N -выходов

Один из

N входов подключить к выходу

Слайд 32www.themegallery.com

Компаратор

Сравнивает две четырех битные комбинации и если они равны на

выходе

1 если не равны то на выходе 0.

1

если на входе сигналы одного уровняСлайд 35www.themegallery.com

АЛУ

Данная схема может выполнять 4 функции: АВ, А+В, не В,

А+В

Задают тип

функции

Входные

Разрешение

Одноразрядная

микропроцессорная

секция

Слайд 37www.themegallery.com

Триггер

Базовый элемент для организации запоминающих устройств, регистров, счетчиков.

Асинхронные

Синхронные

Двухступенчатые

Одноступенчатые

Со статическим

управлением

С динамическим

управлением

Слайд 38www.themegallery.com

Триггеры RS асинхронные

RS с инверсным и прямым управлением

Логика работы

Обозначение

Логика работы

Обозначение

R

– (reset) сброс.

S – (set) установка.

Слайд 40www.themegallery.com

Синхронный RS Триггер

Прямого статического управления

Схема внутренней логики

Схема внутренней логики

C –

(clock) синхронизация

Слайд 41www.themegallery.com

Синхронный RS триггер

С инверсным, динамическим управлением по переднему фронту сигнала

С

Схема внутренней логики

Слайд 42www.themegallery.com

Синхронный RS с динамическим управлением

Динамическое управление по заднему фронту сигнала

С

Схема внутренней логики

Слайд 43www.themegallery.com

D триггер - одноступенчатый

Основа построения регистров

Ячейка памяти

Схема внутренней логики

Схема

внутренней логики

Слайд 45www.themegallery.com

D триггер с динамическим управлением

С управлением по переднему фронту

Счетный триггер

–

основа построения

счетчиков.

Слайд 46www.themegallery.com

Двухтактные RS триггеры

Счетный триггер

Мастер - master

Исполнитель - slave

MS триггер

Слайд 47www.themegallery.com

Универсальный JK триггер

Устраняет неопределенность возникающую при одновременном снятии

сигналов с

входов R и S

Слайд 49www.themegallery.com

Счетчики

Устройство для счета единиц, поступающих на его вход. Основа построения

таймеров.

Счетчики

Прямого счета

Обратного счета

Реверсивные

Асинхронные

с последовательным

переносом

Синхронные

с параллельным

переносом

Комбинированные

Количество

триггеров

Коэффициент пересчета - Ксч

Слайд 54www.themegallery.com

Синхронный счетчик с параллельным переносом

Осуществляется выявление возможного состояния триггера старшего

разряда

путем анализа младших разрядов.

Слайд 58www.themegallery.com

Регистры

Предназначен для приема, хранения и передачи информации.

Последовательные

Параллельные

Последовательно-

параллельные

Слайд 61www.themegallery.com

Регистр в интегральном исполнении

1. Параллельная запись.

2. Последовательная запись и

сдвиг

из младших разрядов

в старшие.

3. Последовательная запись и

сдвиг из старших

разрядов в младшие.

4. Совмещение режимов.

Режим V2

Последовательная запись С1

Параллельная запись С2

к155