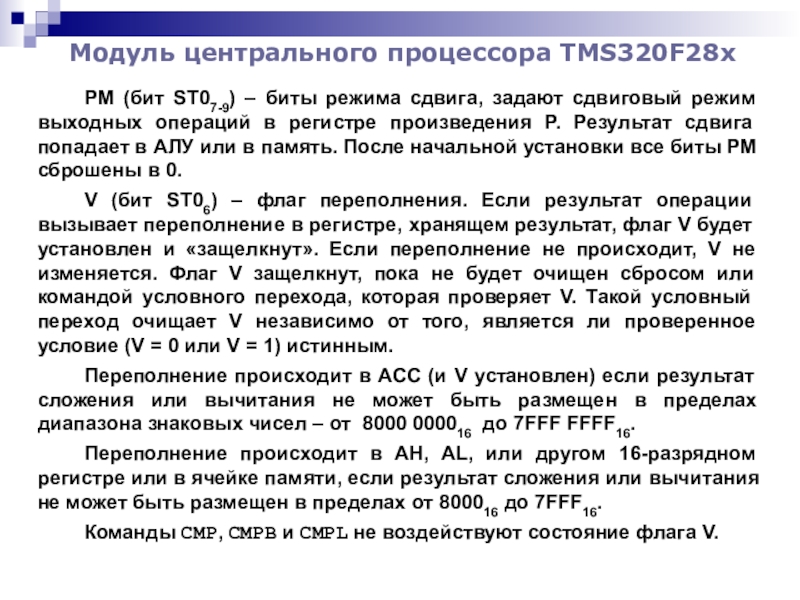

Слайд 1Модуль центрального процессора TMS320F28x

PM (бит ST07-9) – биты режима

сдвига, задают сдвиговый режим выходных операций в регистре произведения P.

Результат сдвига попадает в АЛУ или в память. После начальной установки все биты PM сброшены в 0.

V (бит ST06) – флаг переполнения. Если результат операции вызывает переполнение в регистре, хранящем результат, флаг V будет установлен и «защелкнут». Если переполнение не происходит, V не изменяется. Флаг V защелкнут, пока не будет очищен сбросом или командой условного перехода, которая проверяет V. Такой условный переход очищает V независимо от того, является ли проверенное условие (V = 0 или V = 1) истинным.

Переполнение происходит в ACC (и V установлен) если результат сложения или вычитания не может быть размещен в пределах диапазона знаковых чисел – от 8000 000016 до 7FFF FFFF16.

Переполнение происходит в АH, AL, или другом 16-разрядном регистре или в ячейке памяти, если результат сложения или вычитания не может быть размещен в пределах от 800016 до 7FFF16.

Команды CMP, CMPB и CMPL не воздействуют состояние флага V.

Слайд 2Модуль центрального процессора TMS320F28x

N (бит ST05) – флаг знака.

N установлен, если результат операции – отрицательное число или сброшен,

если результат – положительное число. После сброса N сброшен в 0. Если бит 31 ACC равен 0, ACC – положителен; если бит 31 равен 1, ACC отрицателен. Результат АH, AL, и других 16-разрядных регистров или данных в ячейках памяти также проверяются на отрицательное условие. Тогда значение бита 15 – знаковый разряд (1 указывает на отрицательное, 0 указывает на положительное число). Команда TEST ACC устанавливает флаг N, если значение в ACC отрицательно. Иначе команда сбрасывает флаг N.

Z (ST04) – флаг нуля. Z установлен, если результат некоторых операций – 0 или сброшен, если результат отличается от нуля. Это применяется к результатам, которые получены в ACC, АH, AL, другом регистре, или в ячейке памяти. После сброса, Z сброшен.

Команда TEST ACC устанавливает Z, если значение в ACC – 0, иначе сбрасывает Z.

Слайд 3Модуль центрального процессора TMS320F28x

C (бит ST03) – флаг переноса.

Этот флаг показывает, когда сложение, инкремент генерируют перенос, или когда

вычитание, сравнение, декремент генерируют заем. Этот флаг также устанавливают операции программного сдвига ACC (команды ROR, ROL) и аппаратные сдвиги (barrel shift) в ACC, АH, и AL. В результате сложения/инкремента, C будет установлен, если генерируется перенос; иначе C будет сброшен. Имеется одно исключение: если используется команда ADD со сдвигом 16 (ADD ACC,loc16<В результате вычитания/декремента/сравнения, C будет сброшен, если вычитание генерирует перенос; иначе C будет установлен. Имеется одно исключение: если используется команда SUB со сдвигом 16 (SUB ACC,loc16<Этот бит может быть индивидуально установлен и очищен командами SETC C и CLRC C соответственно. После начального сброса, C сброшен в 0.

Слайд 4Модуль центрального процессора TMS320F28x

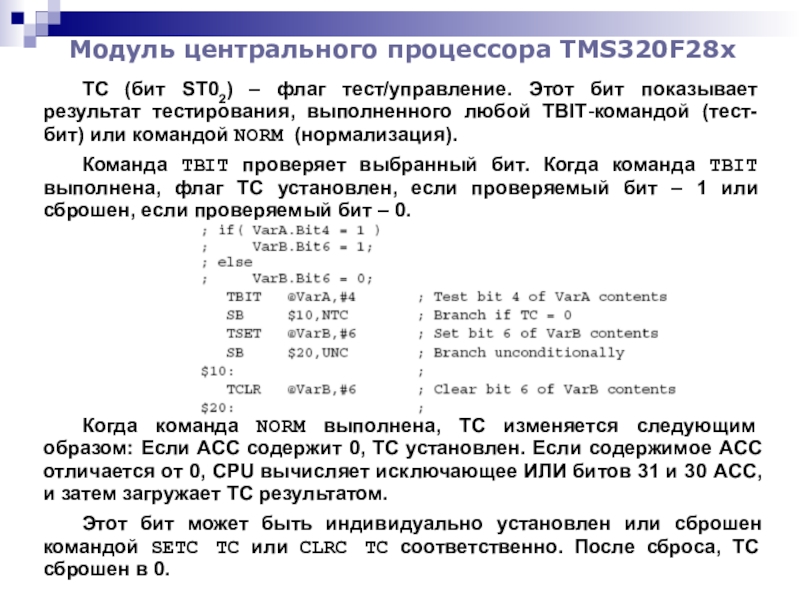

TC (бит ST02) – флаг тест/управление.

Этот бит показывает результат тестирования, выполненного любой TBIT-командой (тест- бит)

или командой NORM (нормализация).

Команда TBIT проверяет выбранный бит. Когда команда TBIT выполнена, флаг TC установлен, если проверяемый бит – 1 или сброшен, если проверяемый бит – 0.

Когда команда NORM выполнена, TC изменяется следующим образом: Если ACC содержит 0, TC установлен. Если содержимое ACC отличается от 0, CPU вычисляет исключающее ИЛИ битов 31 и 30 ACC, и затем загружает TC результатом.

Этот бит может быть индивидуально установлен или сброшен командой SETC TC или CLRC TC соответственно. После сброса, TC сброшен в 0.

Слайд 5Модуль центрального процессора TMS320F28x

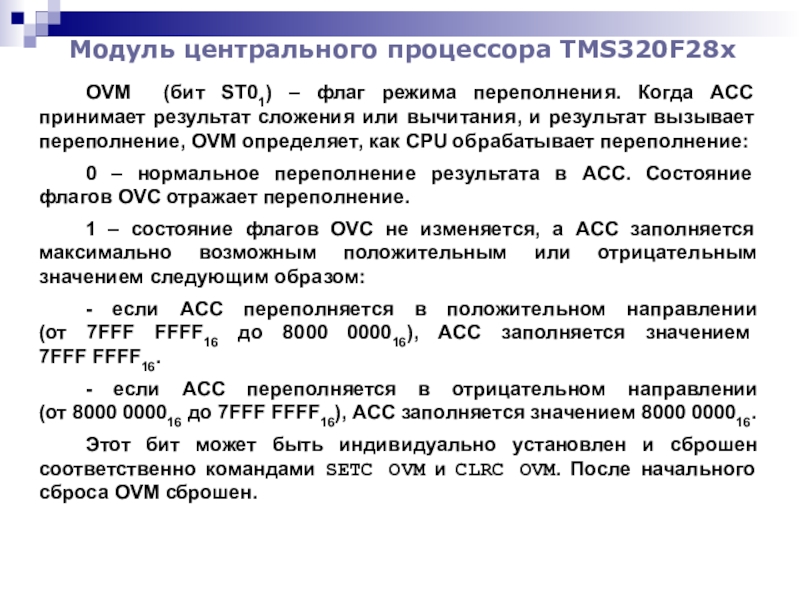

OVM (бит ST01) – флаг режима

переполнения. Когда ACC принимает результат сложения или вычитания, и результат

вызывает переполнение, OVM определяет, как CPU обрабатывает переполнение:

0 – нормальное переполнение результата в ACC. Состояние флагов OVC отражает переполнение.

1 – состояние флагов OVC не изменяется, а ACC заполняется максимально возможным положительным или отрицательным значением следующим образом:

- если ACC переполняется в положительном направлении

(от 7FFF FFFF16 до 8000 000016), ACC заполняется значением

7FFF FFFF16.

- если ACC переполняется в отрицательном направлении

(от 8000 000016 до 7FFF FFFF16), ACC заполняется значением 8000 000016.

Этот бит может быть индивидуально установлен и сброшен соответственно командами SETC OVM и CLRC OVM. После начального сброса OVM сброшен.

Слайд 6Модуль центрального процессора TMS320F28x

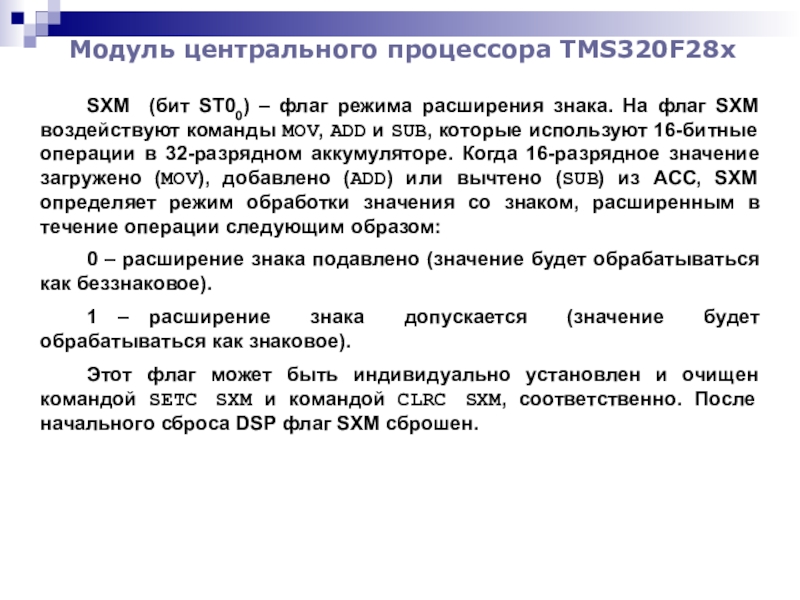

SXM (бит ST00) – флаг режима

расширения знака. На флаг SXM воздействуют команды MOV, ADD и

SUB, которые используют 16-битные операции в 32-разрядном аккумуляторе. Когда 16-разрядное значение загружено (MOV), добавлено (ADD) или вычтено (SUB) из ACC, SXM определяет режим обработки значения со знаком, расширенным в течение операции следующим образом:

0 – расширение знака подавлено (значение будет обрабатываться как беззнаковое).

1 – расширение знака допускается (значение будет обрабатываться как знаковое).

Этот флаг может быть индивидуально установлен и очищен командой SETC SXM и командой CLRC SXM, соответственно. После начального сброса DSP флаг SXM сброшен.

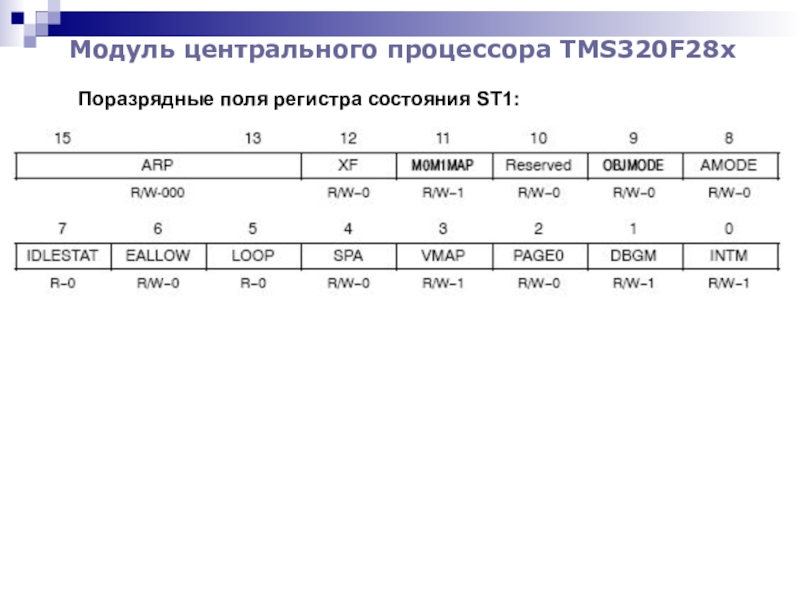

Слайд 7Модуль центрального процессора TMS320F28x

Поразрядные поля регистра состояния ST1:

Слайд 8Модуль центрального процессора TMS320F28x

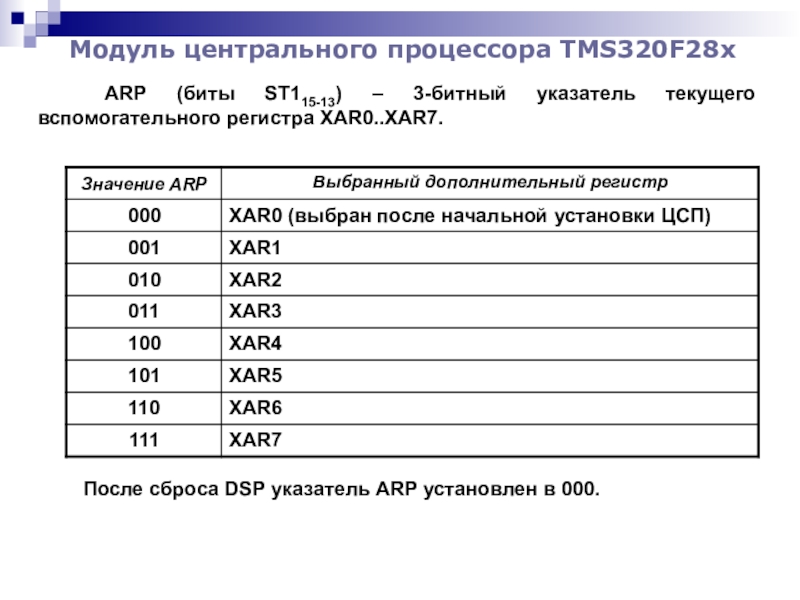

ARP (биты ST115-13) – 3-битный

указатель текущего вспомогательного регистра XAR0..XAR7.

После сброса DSP указатель ARP

установлен в 000.

Слайд 9Модуль центрального процессора TMS320F28x

XF (бит ST112) – флаг,

отражающий текущее состояние вывода /XF_XPLLDIS.

Программная установка флага – SETC

XF;

сброс – CLRC XF.

При использовании этих команд конвейер выполнения команд не может быть прерван. Бит XF (в составе регистра ST1) сохраняется и восстанавливается при обработке прерываний.

M0M1MAP (бит ST111) – флаг режима карты памяти. Он всегда равен 1 в объектном режиме C28x (это значение флаг имеет после начальной установки DSP). Когда необходимо использовать С27x-совместимый режим, этот флаг может быть установлен в 0. При этом адреса областей памяти M0 и M1 меняются местами (только в памяти программ, но не в памяти данных) и указатель стека по умолчанию имеет значение 0x000.

Бит ST110 – резервный бит.

OBJMODE (бит ST19) – флаг режима объектной совместимости (0 для C27x-режима и 1 для C28x-режима).

Программная установка флага – команды SETC OBJMODE; C28OBJ;

сброс – CLRC OBJMODE; C27OBJ.

Бит OBJMODE (в составе регистра ST1) сохраняется и восстанавливается при обработке прерываний. После начальной установки ЦСП флаг имеет нулевое значение.

Слайд 10Модуль центрального процессора TMS320F28x

AMODE (бит ST18) – флаг

режима адресации. Этот бит, в сочетании с битом PAGE0 используется

для выбора соответствующего режима адресации:

AMODE=0 – в режиме прямой адресации DP дополняется

6-битным смещением, и некоторые режимы косвенной адресации не поддерживаются (C28x-режим);

AMODE=1 – в режиме прямой адресации DP дополняется

7-битным смещением, и поддерживаются все режимы косвенной адресации.

Программная установка флага – команды SETC AMODE; LPADDR;

сброс – CLRC AMODE; C28ADDR.

При использовании этих команд конвейер выполнения команд не может быть прерван. Бит AMODE (в составе регистра ST1) сохраняется и восстанавливается при обработке прерываний. После начальной установки DSP флаг имеет нулевое значение.

IDLESTAT (бит ST17) – флаг-индикатор выполненной инструкции IDLE. Доступен только по чтению. Флаг может быть сброшен по факту обслуживания прерывания и после начального сброса ЦСП. После обслуживания прерывания значение бита IDLESTAT из стека не восстанавливается.

Слайд 11Модуль центрального процессора TMS320F28x

EALLOW (бит ST16) – этот

флаг после установки разрешает доступ к эмуляционным и другим защищенным

регистрам.

Программная установка флага – EALLOW;

сброс – EDIS.

Когда ЦСП обслуживает прерывание, текущее значение флага EALLOW сохраняется в стеке и затем обнуляется. Поэтому после начала подпрограммы обслуживания прерывания доступ к эмуляционным и другим защищенным регистрам запрещен. Если в подпрограмме требуется доступ к таким регистрам, необходимо внутри использовать команду EALLOW. По окончании подпрограммы обслуживания прерывания, флаг EALLOW может быть восстановлен при помощи команды IRET.

LOOP (бит ST15) – бит инструкции «LOOP». Этот флаг устанавливается, когда инструкция LOOPNZ или LOOPZ достигает фазы D2 конвейера. Эти инструкции продолжают выполняться, пока не встретится указанное в команде условие. После выполнения условия флаг LOOP сбрасывается. Этот бит не может быть программно установлен, может быть только считан.

Слайд 12Модуль центрального процессора TMS320F28x

SPA (бит ST14) – бит выравнивания

указателя стека. Этот флаг показывает, выполнял ли процессор выравнивание указателя

стека на четный адрес инструкцией ASP:

SPA=1 – выравнивание выполнялось;

SPA=0 – выравнивание не выполнялось.

После выполнения инструкции ASP, если SP указывал на нечетный адрес, он инкрементируется, а флаг SPA устанавливается в 1. Если SP уже был установлен на четный адрес, флаг SPA сбрасывается в 0.

После выполнения инструкции NASP, если флаг SPA был установлен в 1, SP декрементируется и флаг SPA сбрасывается в 0. Если SPA был сброшен в 0, SP не изменяется.

Слайд 13Модуль центрального процессора TMS320F28x

VMAP (бит ST13) – бит карты

векторов прерываний. VMAP определяет, где в программной памяти располагаются вектора

прерываний:

VMAP=0 – вектора прерываний располагаются в нижней части программной памяти, по адресам 00 000016 − 00 003F16;

VMAP=1 – вектора прерываний располагаются в верхней части программной памяти, по адресам 3F FFC016− 3F FFFF16.

В C28x – устройствах бит VMAP имеет аппаратное «подтягивание» к уровню лог. 1, что обеспечивает установку этого бита в «1» после начальной установки.

Программная установка флага – команда SETC VMAP;

сброс – CLRC VMAP.

Слайд 14Модуль центрального процессора TMS320F28x

PAGE0 (бит ST12) – бит конфигурации

режима адресации PAGE0. Этот бит определяет два взаимоисключающих режима адресации:

режим прямой адресации PAGE0 (1) и режим стековой адресации PAGE0 (0). Одновременная установка битов PAGE0 и AMODE в 1 недопустима.

Установка PAGE0 в 1 включает совместимость с

C27x-устройствами. Для C28x-устройств рекомендуется сбросить PAGE0 в 0.

Программная установка флага – команда SETC PAGE0;

сброс – CLRC PAGE0.

После начальной установки ЦСП бит PAGE0 сброшен в 0.

Слайд 15Модуль центрального процессора TMS320F28x

DBGM (бит ST11) – бит

маскирования разрешения отладки. Если флаг DBGM установлен, эмулятор не имеет

доступа к регистрам и памяти в реальном масштабе времени. CPU не воспринимает запросы останова, пока DBGM не будет сброшен. Перед началом выполнения подпрограммы DBGM всегда устанавливается в 1, и для возможности реализации пошагового режима и реализации точек останова, необходимо добавить команду CLRC DBGM в начале текста подпрограммы.

Программная установка флага – команда SETC DBGM;

сброс – CLRC DBGM.

После начальной установки DSP бит DBGM установлен в 1.

Слайд 16Модуль центрального процессора TMS320F28x

INTM (бит ST10) – бит общего

маскирования прерываний. Этот бит глобально разрешает или запрещает все маскируемые

прерывания:

INTM = 0 – общее разрешение прерываний (индивидуально –

в регистре IER);

INTM = 1 – общий запрет прерываний.

Флаг INTM не оказывает влияния на обработку немаскируемых прерываний.

Программная установка флага – команда SETC INTM;

сброс – CLRC INTM.

После начальной установки ЦСП бит INTM установлен в 1.

Слайд 1732-битные таймеры ядра ЦСП TMS320F28x

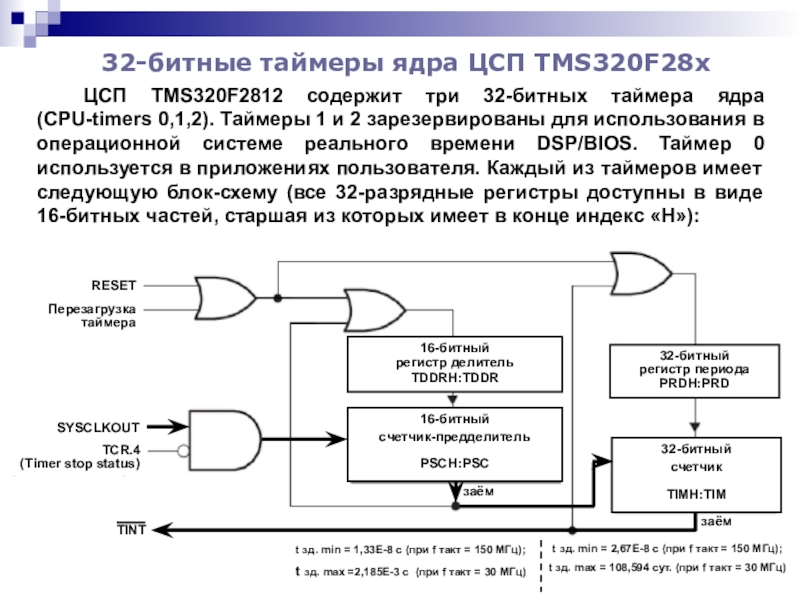

ЦСП TMS320F2812 содержит три 32-битных

таймера ядра (CPU-timers 0,1,2). Таймеры 1 и 2 зарезервированы для

использования в операционной системе реального времени DSP/BIOS. Таймер 0 используется в приложениях пользователя. Каждый из таймеров имеет следующую блок-схему (все 32-разрядные регистры доступны в виде 16-битных частей, старшая из которых имеет в конце индекс «H»):

Слайд 1832-битные таймеры ядра ЦСП TMS320F28x

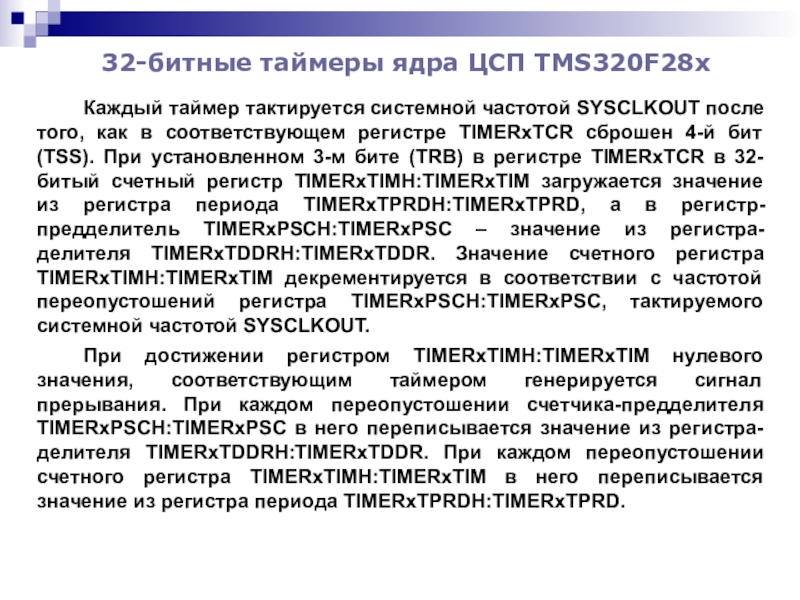

Каждый таймер тактируется системной частотой

SYSCLKOUT после того, как в соответствующем регистре TIMERxTCR сброшен 4-й

бит (TSS). При установленном 3-м бите (TRB) в регистре TIMERxTCR в 32-битый счетный регистр TIMERxTIMH:TIMERxTIM загружается значение из регистра периода TIMERxTPRDH:TIMERxTPRD, а в регистр-предделитель TIMERxPSCH:TIMERxPSC – значение из регистра-делителя TIMERxTDDRH:TIMERxTDDR. Значение счетного регистра TIMERxTIMH:TIMERxTIM декрементируется в соответствии с частотой переопустошений регистра TIMERxPSCH:TIMERxPSC, тактируемого системной частотой SYSCLKOUT.

При достижении регистром TIMERxTIMH:TIMERxTIM нулевого значения, соответствующим таймером генерируется сигнал прерывания. При каждом переопустошении счетчика-предделителя TIMERxPSCH:TIMERxPSC в него переписывается значение из регистра-делителя TIMERxTDDRH:TIMERxTDDR. При каждом переопустошении счетного регистра TIMERxTIMH:TIMERxTIM в него переписывается значение из регистра периода TIMERxTPRDH:TIMERxTPRD.

Слайд 1932-битные таймеры ядра ЦСП TMS320F28x

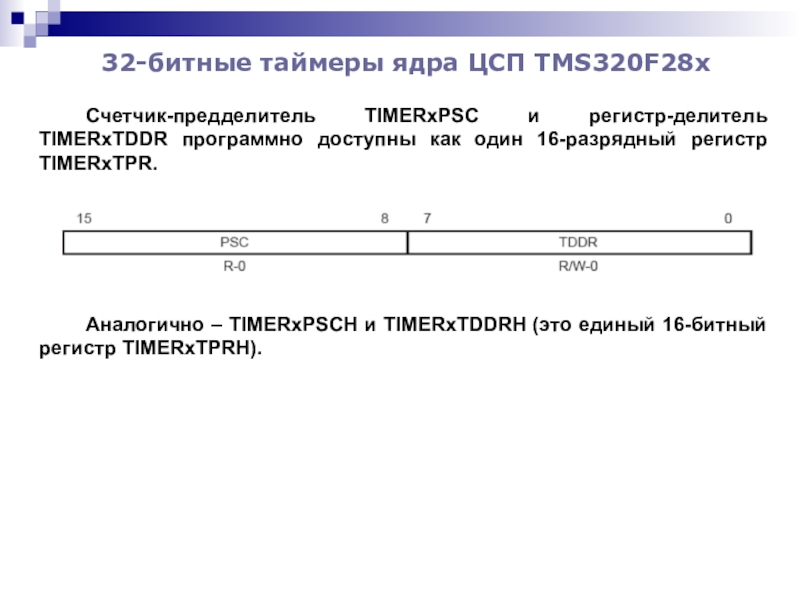

Счетчик-предделитель TIMERxPSC и регистр-делитель TIMERxTDDR

программно доступны как один 16-разрядный регистр TIMERxTPR.

Аналогично – TIMERxPSCH

и TIMERxTDDRH (это единый 16-битный регистр TIMERxTPRH).

Слайд 20Система прерываний DSP TMS320F2812

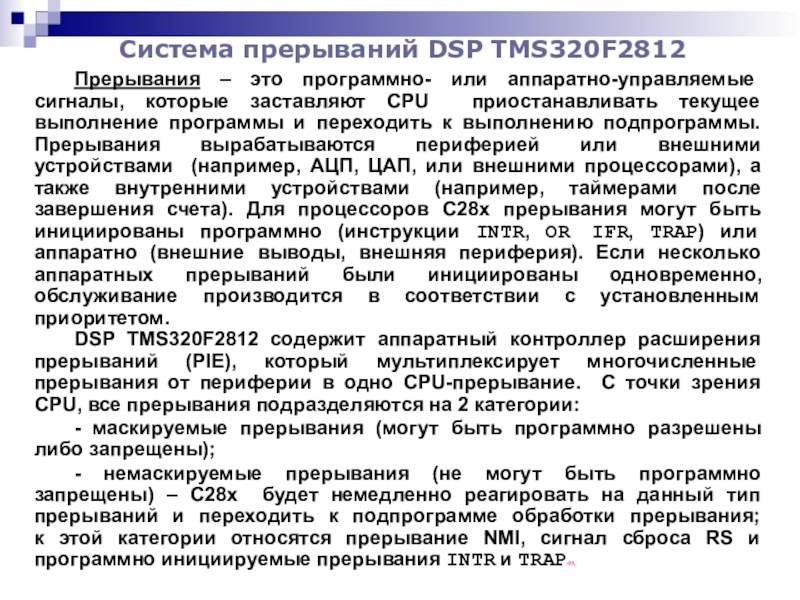

Прерывания – это программно- или аппаратно-управляемые

сигналы, которые заставляют CPU приостанавливать текущее выполнение программы и переходить

к выполнению подпрограммы. Прерывания вырабатываются периферией или внешними устройствами (например, АЦП, ЦАП, или внешними процессорами), а также внутренними устройствами (например, таймерами после завершения счета). Для процессоров C28x прерывания могут быть инициированы программно (инструкции INTR, OR IFR, TRAP) или аппаратно (внешние выводы, внешняя периферия). Если несколько аппаратных прерываний были инициированы одновременно, обслуживание производится в соответствии с установленным приоритетом.

DSP TMS320F2812 содержит аппаратный контроллер расширения прерываний (PIE), который мультиплексирует многочисленные прерывания от периферии в одно CPU-прерывание. С точки зрения CPU, все прерывания подразделяются на 2 категории:

- маскируемые прерывания (могут быть программно разрешены либо запрещены);

- немаскируемые прерывания (не могут быть программно запрещены) – C28x будет немедленно реагировать на данный тип прерываний и переходить к подпрограмме обработки прерывания;

к этой категории относятся прерывание NMI, сигнал сброса RS и программно инициируемые прерывания INTR и TRAP-??.

Слайд 21Система прерываний DSP TMS320F2812

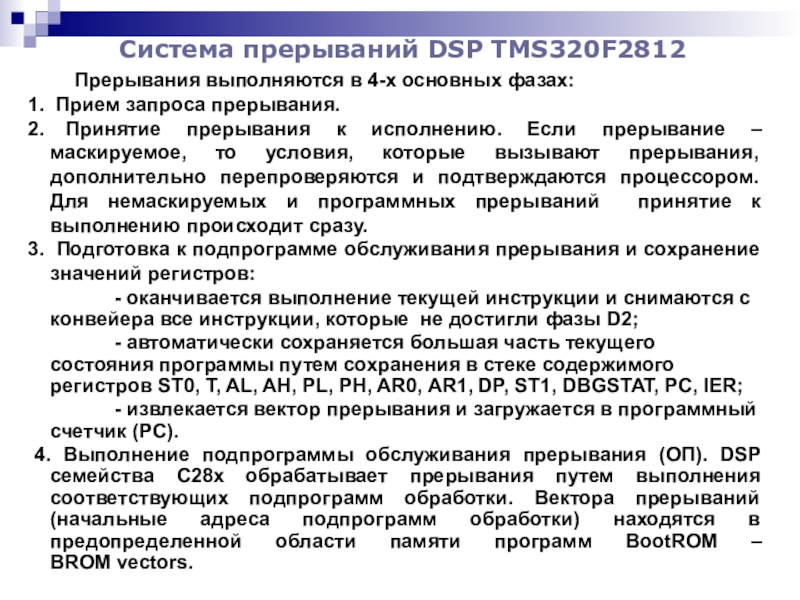

Прерывания выполняются в 4-х основных фазах:

Прием запроса прерывания.

Принятие прерывания к исполнению. Если прерывание –

маскируемое, то условия, которые вызывают прерывания, дополнительно перепроверяются и подтверждаются процессором. Для немаскируемых и программных прерываний принятие к выполнению происходит сразу.

Подготовка к подпрограмме обслуживания прерывания и сохранение значений регистров:

- оканчивается выполнение текущей инструкции и снимаются с конвейера все инструкции, которые не достигли фазы D2;

- автоматически сохраняется большая часть текущего состояния программы путем сохранения в стеке содержимого регистров ST0, T, AL, AH, PL, PH, AR0, AR1, DP, ST1, DBGSTAT, PC, IER;

- извлекается вектор прерывания и загружается в программный счетчик (PC).

4. Выполнение подпрограммы обслуживания прерывания (ОП). DSP семейства C28x обрабатывает прерывания путем выполнения соответствующих подпрограмм обработки. Вектора прерываний (начальные адреса подпрограмм обработки) находятся в предопределенной области памяти программ BootROM –

BROM vectors.

Слайд 22Система прерываний DSP TMS320F2812

Слайд 23Система прерываний DSP TMS320F2812

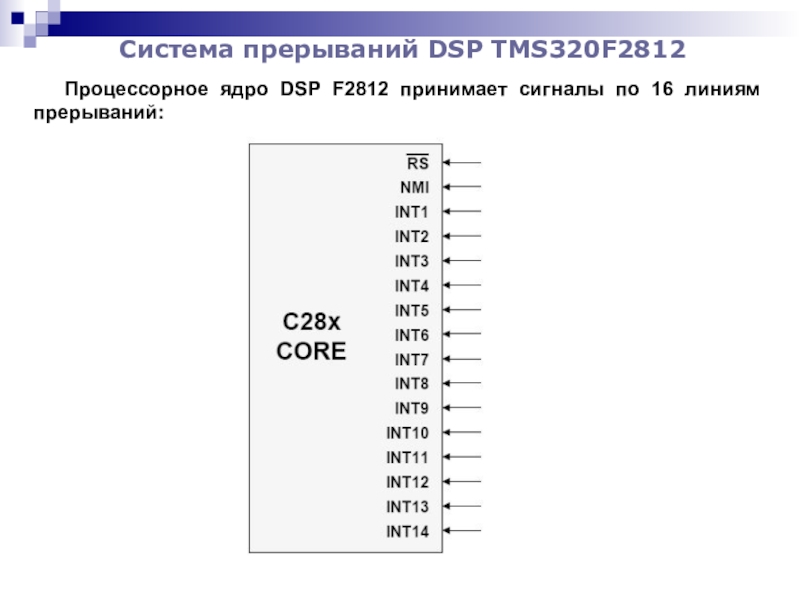

Процессорное ядро DSP F2812 принимает сигналы

по 16 линиям прерываний:

Слайд 24Система прерываний DSP TMS320F2812

Источники прерываний в DSP F2812:

Слайд 2532-битные таймеры ядра ЦСП TMS320F28x

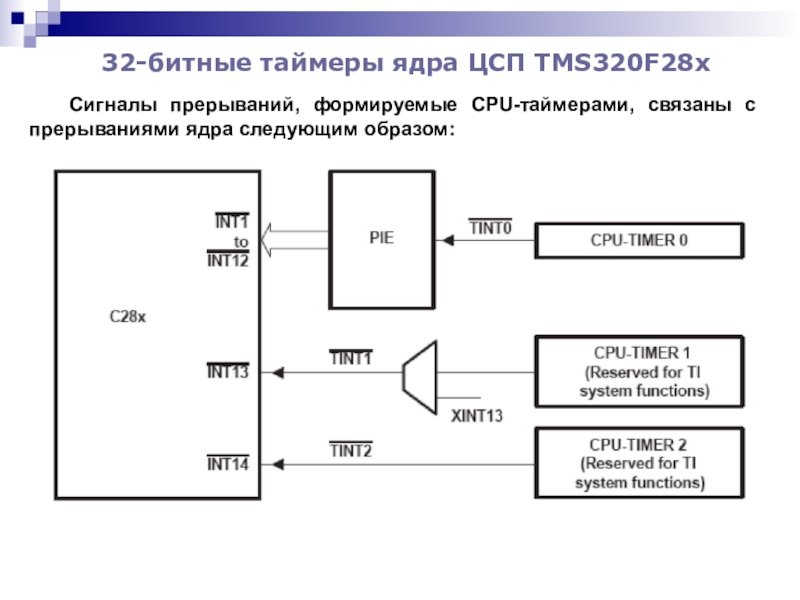

Сигналы прерываний, формируемые CPU-таймерами, связаны

с прерываниями ядра следующим образом: