Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

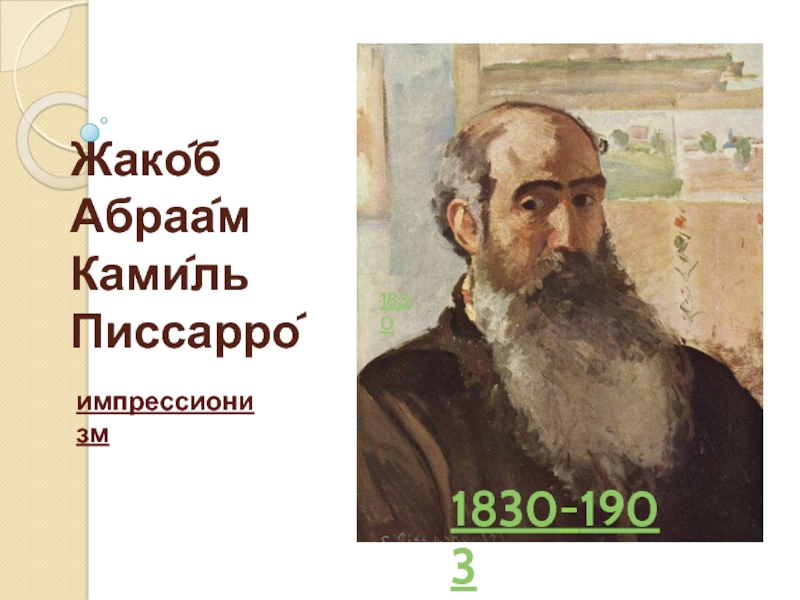

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

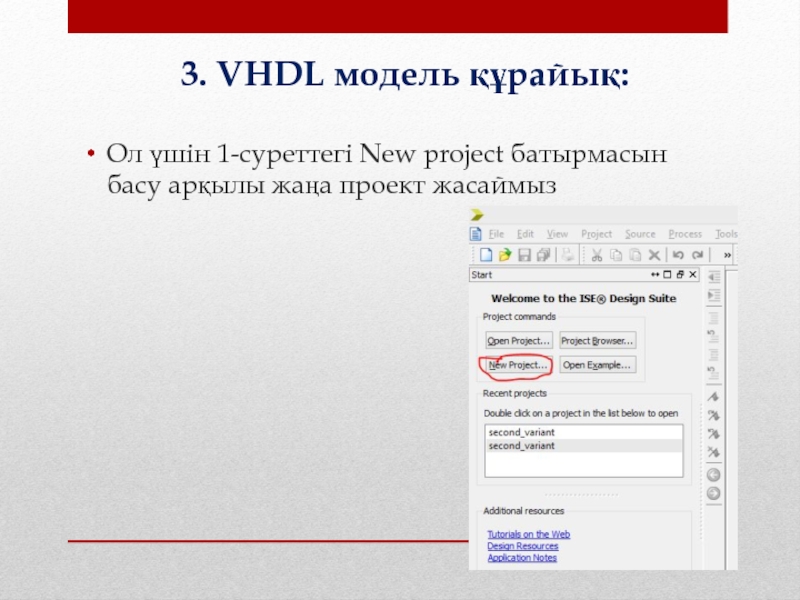

Ол үшін 1-суреттегі New project батырмасын басу арқылы жаңа проект жасаймыз 3

Содержание

- 1. Ол үшін 1-суреттегі New project батырмасын басу арқылы жаңа проект жасаймыз 3

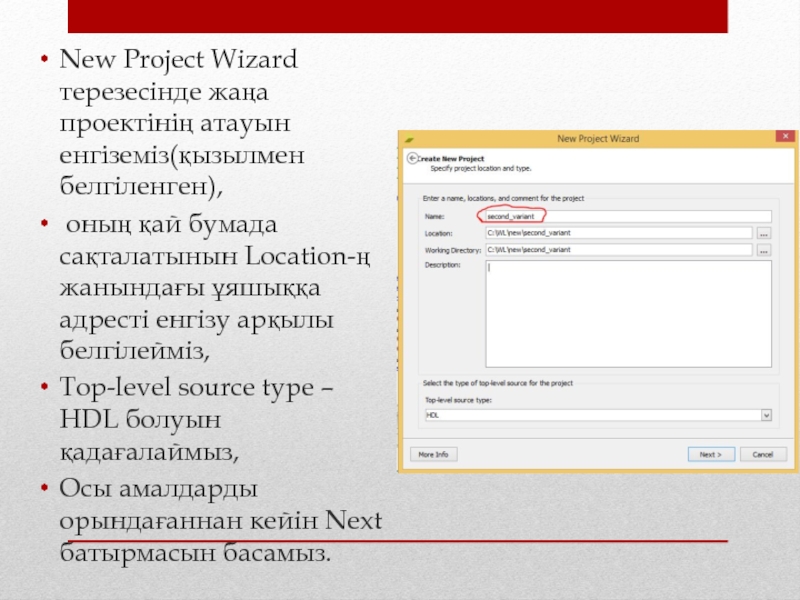

- 2. New Project Wizard терезесінде жаңа проектінің атауын

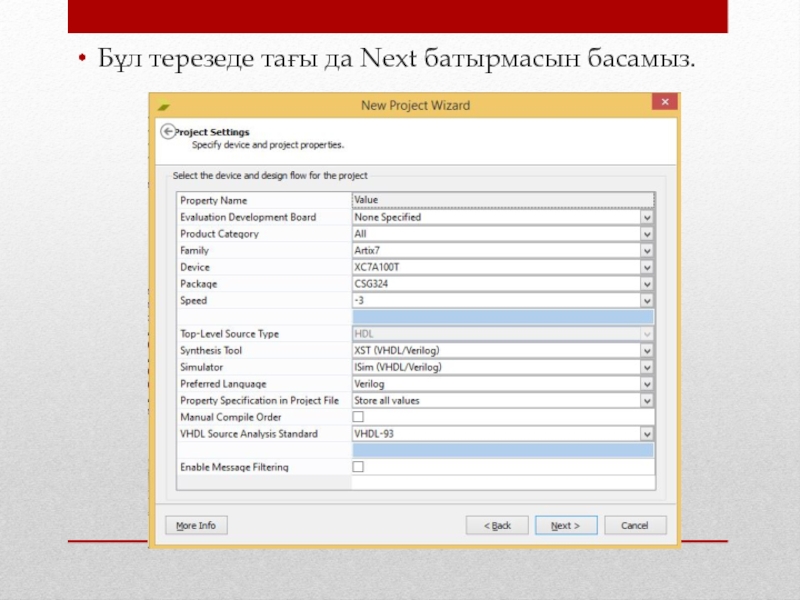

- 3. Бұл терезеде тағы да Next батырмасын басамыз.

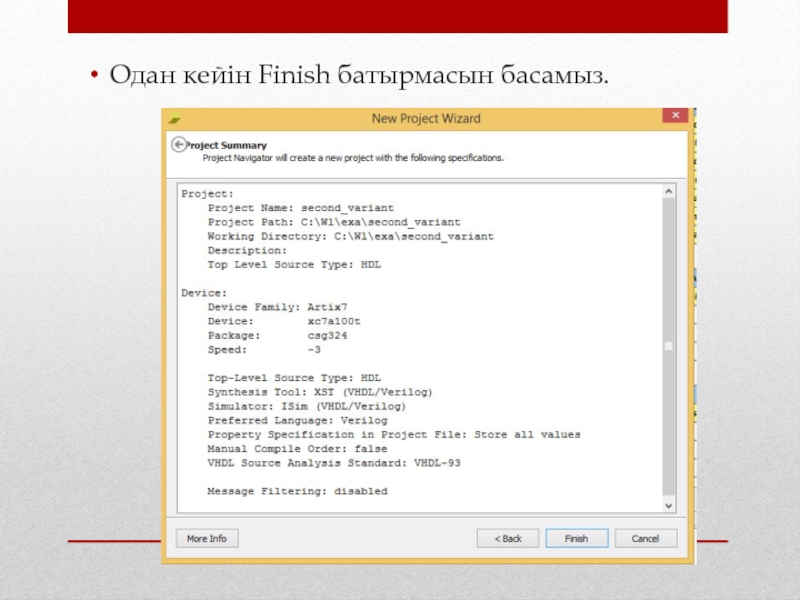

- 4. Одан кейін Finish батырмасын басамыз.

- 5. Иерархия терезесіндегі Second_variant атауының үстінен тышқанның оң

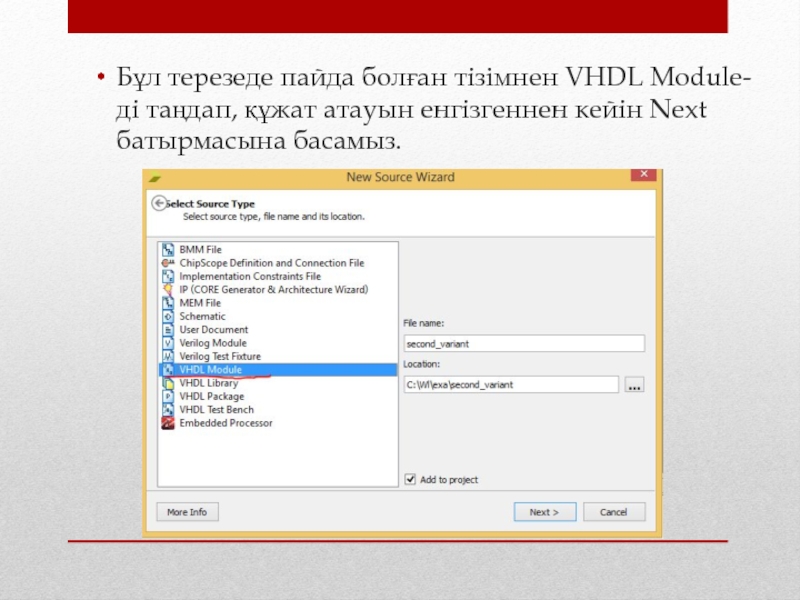

- 6. Бұл терезеде пайда болған тізімнен VHDL Module-ді таңдап, құжат атауын енгізгеннен кейін Next батырмасына басамыз.

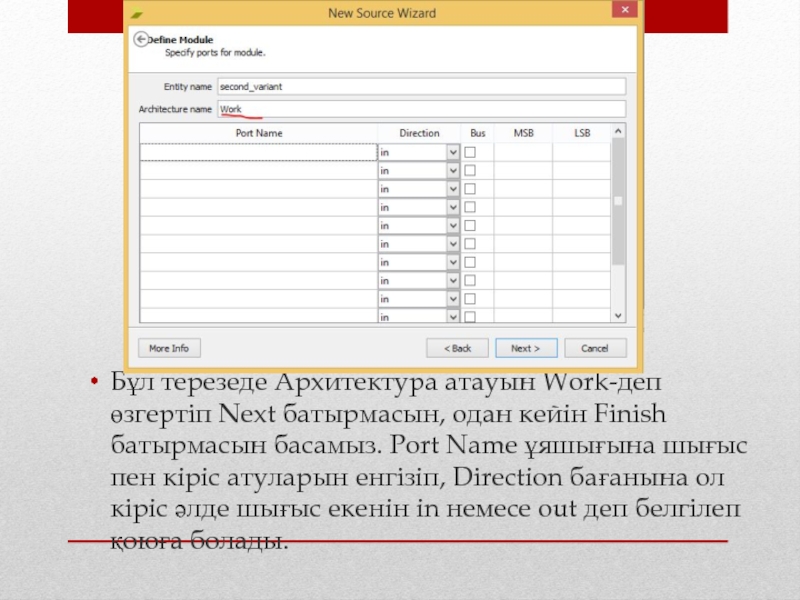

- 7. Бұл терезеде Архитектура атауын Work-деп өзгертіп Next

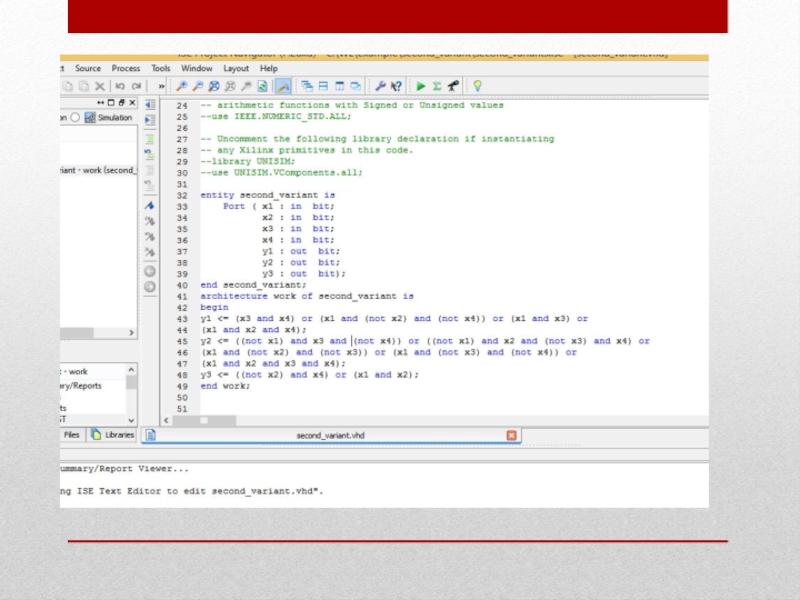

- 8. Бұл суретте көрсетілгендей VHDL тілінде жоғарыда алынған функцияны енгіземіз.

- 9. Суретте көрсетілген барыманы басу арқылы Synthesize-тексереміз. Егер ол дұрыс болса оның жанында жасыл белгі пайда болады.

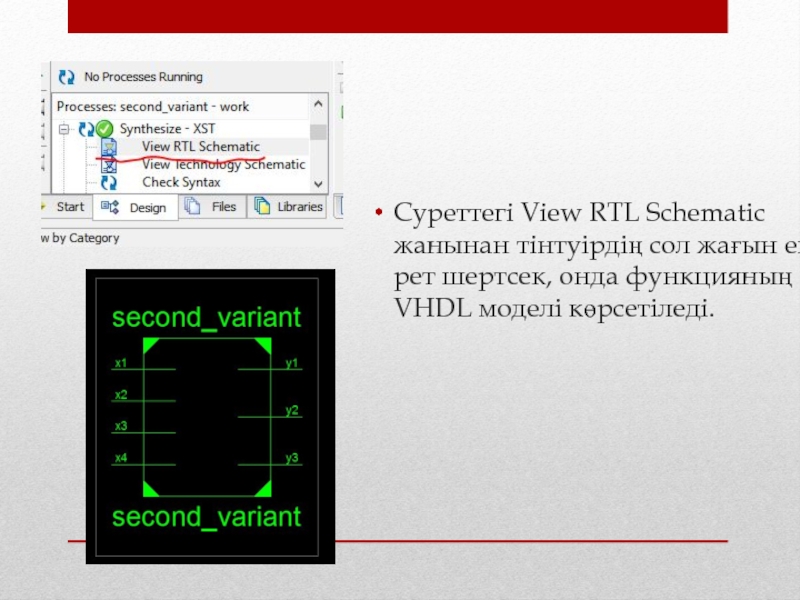

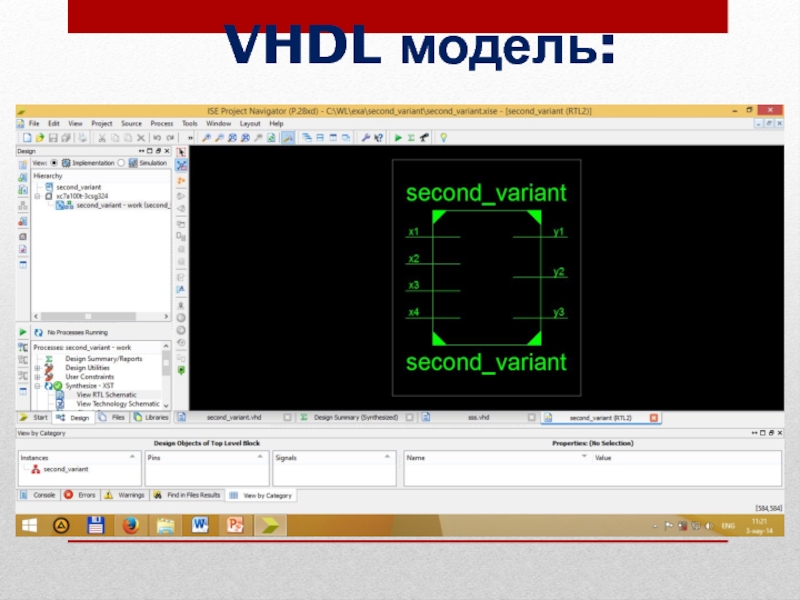

- 10. Суреттегі View RTL Schematic жанынан тінтуірдің сол жағын екі рет шертсек, онда функцияның VHDL моделі көрсетіледі.

- 11. VHDL модель:

- 12. Осы суреттің үстінен екі рет шерсек VHDL модельдің кең жайылған түрін аламыз.

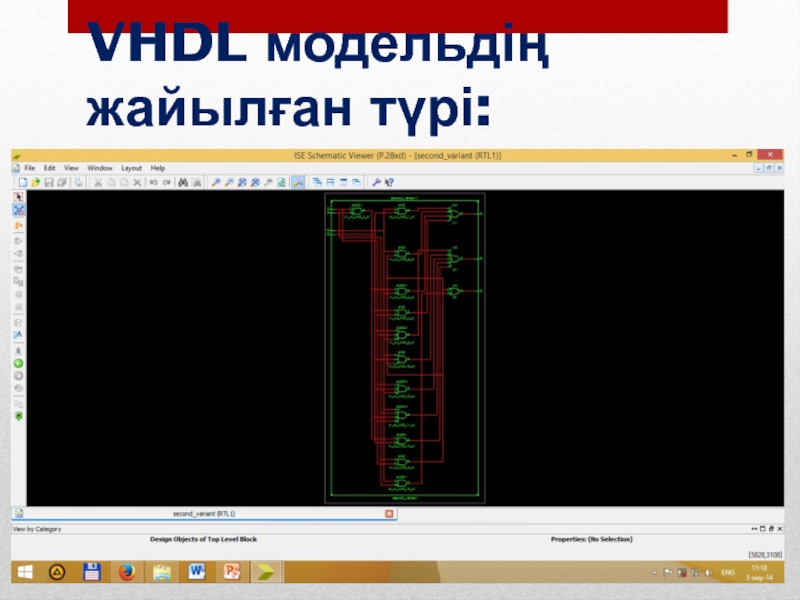

- 13. VHDL модельдің жайылған түрі:

- 14. Скачать презентанцию

New Project Wizard терезесінде жаңа проектінің атауын енгіземіз(қызылмен белгіленген), оның қай бумада сақталатынын Location-ң жанындағы ұяшыққа адресті енгізу арқылы белгілейміз,Top-level source type – HDL болуын қадағалаймыз, Осы амалдарды орындағаннан кейін Next

Слайды и текст этой презентации

Слайд 2New Project Wizard терезесінде жаңа проектінің атауын енгіземіз(қызылмен белгіленген),

оның

қай бумада сақталатынын Location-ң жанындағы ұяшыққа адресті енгізу арқылы белгілейміз,

Top-level

source type – HDL болуын қадағалаймыз, Осы амалдарды орындағаннан кейін Next батырмасын басамыз.