Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Оптимизирующая двоичная трансляция как путь к архитектуре будущего Дмитрий

Содержание

- 1. Оптимизирующая двоичная трансляция как путь к архитектуре будущего Дмитрий

- 2. План Что такое ДТПрименение/типы ДТОбзор ДТ-проектовПринципиальная схема ДТУровни трансляцииОтличия/преимущества ДТ от традиционной трансляцииДТ и архитектуры будущего

- 3. Что такое Двоичная Трансляция (ДТ)Английское название: Binary

- 4. Применение двоичной трансляцииДТ может применяться для различных

- 5. Типы СДТ для Architecture enablingСДТ уровня приложений(ABTS

- 6. JIT – это не ДТJust-In-Time Compilation (JIT)

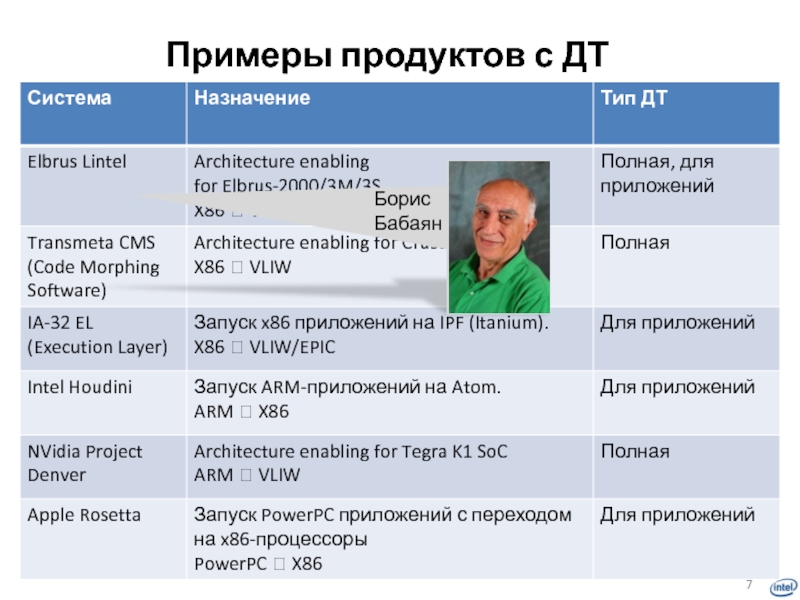

- 7. Примеры продуктов с ДТ

- 8. Принципиальная схема СДТСистема Двоичной ТрансляцииКэш Трансляций

- 9. Уровни оптимизацииИнтерпретаторЧтобы не транслировать «одноразовый» кодНачало профилированияБыстрый

- 10. Отличия от традиционной трансляцииОграничения, присущие ДТ:Вместо языка

- 11. Отличия от традиционной трансляцииОграничения, присущие ДТ:Вместо языка

- 12. Преимущества ДТ: знание конкретной целевой архитектурыВнутри одного

- 13. Преимущества ДТ: знание динамического поведения программыПрофильная информацияИнформация

- 14. Преимущества ДТ: отсутствие границ для оптимизацииЕдиницы трансляции

- 15. Преимущества ДТ: адаптация + право на ошибкуСДТ

- 16. Исчерпанные резервы производительности:Тактовая частотаКонвейеризацияИзбыточность (неоптимальность) кодаАктуальные резервы:Параллелизм.Современные

- 17. КристаллCPUСК1CPU СК3CPU СК2СК1 code BСК3 code 1СК2

- 18. ЛитератураJames Smith, Ravi Nair. “Virtual Machines :

- 19. Слайд 19

- 20. Скачать презентанцию

Слайды и текст этой презентации

Слайд 1Оптимизирующая двоичная трансляция как путь к архитектуре будущего Дмитрий Масленников Андрей

Чудновец

Сергей Щербинин

Слайд 2План

Что такое ДТ

Применение/типы ДТ

Обзор ДТ-проектов

Принципиальная схема ДТ

Уровни трансляции

Отличия/преимущества ДТ от

традиционной трансляции

ДТ и архитектуры будущего

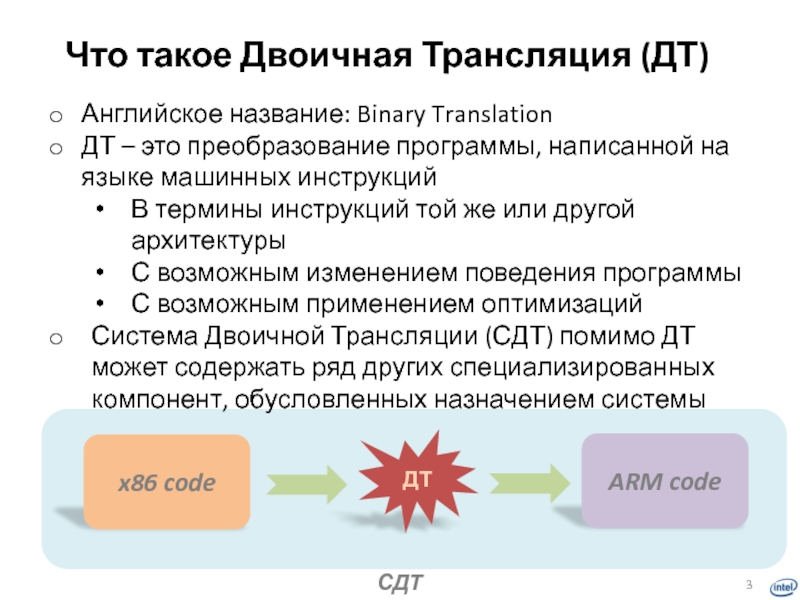

Слайд 3Что такое Двоичная Трансляция (ДТ)

Английское название: Binary Translation

ДТ – это

преобразование программы, написанной на языке машинных инструкций

В термины инструкций той

же или другой архитектурыС возможным изменением поведения программы

С возможным применением оптимизаций

Система Двоичной Трансляции (СДТ) помимо ДТ может содержать ряд других специализированных компонент, обусловленных назначением системы

x86 code

ARM code

ДТ

СДТ

Слайд 4Применение двоичной трансляции

ДТ может применяться для различных целей в разных

областях:

Межплатформенная совместимость

Динамическая оптимизация

Симуляция процессора/платформы

Инструментирование

Виртуализация

Architecture Enabling

Виртуализация CPU

Самое «продвинутое» применение.

Включает черты других

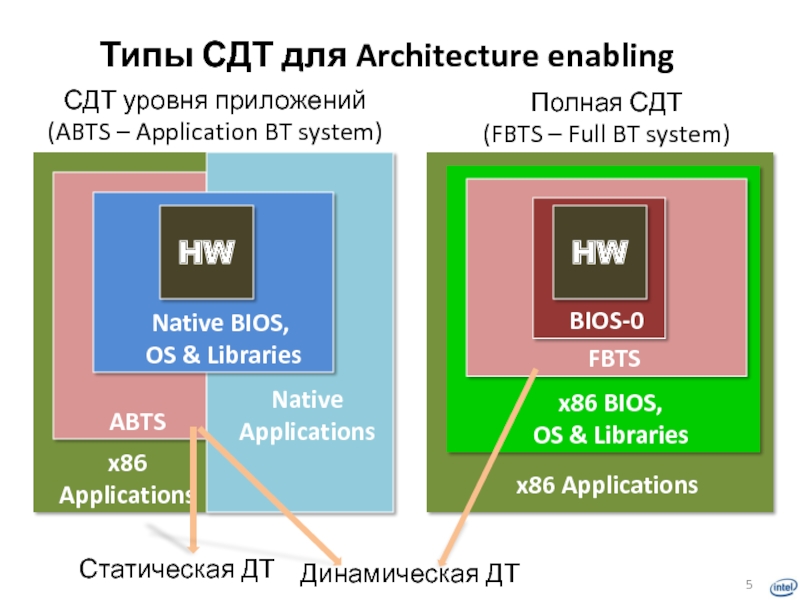

областей применения ДТСлайд 5Типы СДТ для Architecture enabling

СДТ уровня приложений

(ABTS – Application BT

system)

x86 Applications

x86 BIOS,

OS & Libraries

x86

Applications

ABTS

Native

Applications

Native BIOS,

OS & Libraries

HW

FBTS

BIOS-0

HW

Полная СДТ

(FBTS

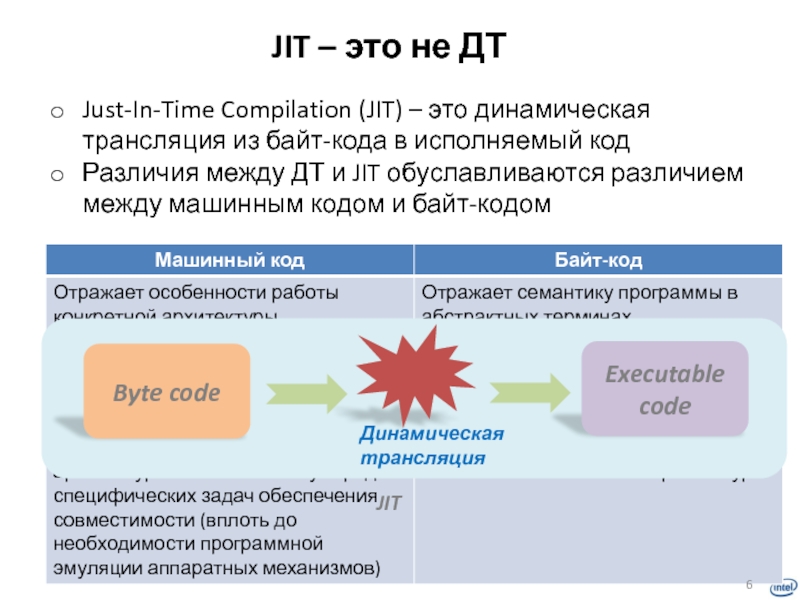

– Full BT system)Слайд 6JIT – это не ДТ

Just-In-Time Compilation (JIT) – это динамическая

трансляция из байт-кода в исполняемый код

Различия между ДТ и JIT

обуславливаются различием между машинным кодом и байт-кодомByte code

Executable code

JIT

Динамическая трансляция

Слайд 8Принципиальная схема СДТ

Система Двоичной Трансляции

Кэш Трансляций

………

Таблица Трансляции Адресов

……….Профильная

Информация

Уровни Оптимизации

……….

Агрессивный Оптимизатор

Быстрый Транслятор

Адрес Региона

Адрес входного кода

Код Региона

Интерпретатор

Наборщик регионов

Адрес Региона

Адрес входного кода

Драйвер трансляции

Регион - единица трансляции ДТ

Профильная информация - статистика динамического поведения программы

Код Региона

Слайд 9Уровни оптимизации

Интерпретатор

Чтобы не транслировать «одноразовый» код

Начало профилирования

Быстрый транслятор

Быстрая трансляция –

низкое качество кода

Трансляция по одной инструкции

Продолжение профилирования

Промежуточный оптимизатор

Трансляция более одной

инструкцииПростейшие / важнейшие оптимизации

Оптимизированное профилирование

Агрессивный оптимизатор

Профилирование только для событий, которые не должны случаться часто

1

2

3

4

Optimization overhead

Performance

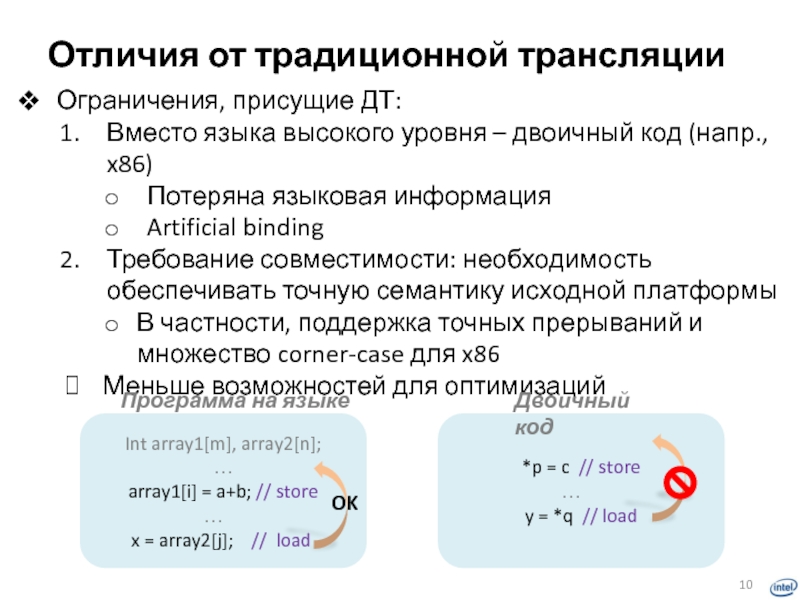

Слайд 10Отличия от традиционной трансляции

Ограничения, присущие ДТ:

Вместо языка высокого уровня –

двоичный код (напр., x86)

Потеряна языковая информация

Artificial binding

Требование совместимости: необходимость обеспечивать

точную семантику исходной платформыВ частности, поддержка точных прерываний и множество corner-case для x86

Меньше возможностей для оптимизаций

Слайд 11Отличия от традиционной трансляции

Ограничения, присущие ДТ:

Вместо языка высокого уровня –

двоичный код (напр., x86)

Потеряна языковая информация

Artificial binding

Требование совместимости: необходимость обеспечивать

точную семантику исходной платформыВ частности, поддержка точных прерываний и множество corner-case для x86

Меньше возможностей для оптимизаций

Жёсткие требования к скорости трансляции

Время трансляции входит в общее время исполнения программы

Высочайшие требования по надёжности СДТ

Должна быть сравнима с надёжностью HW

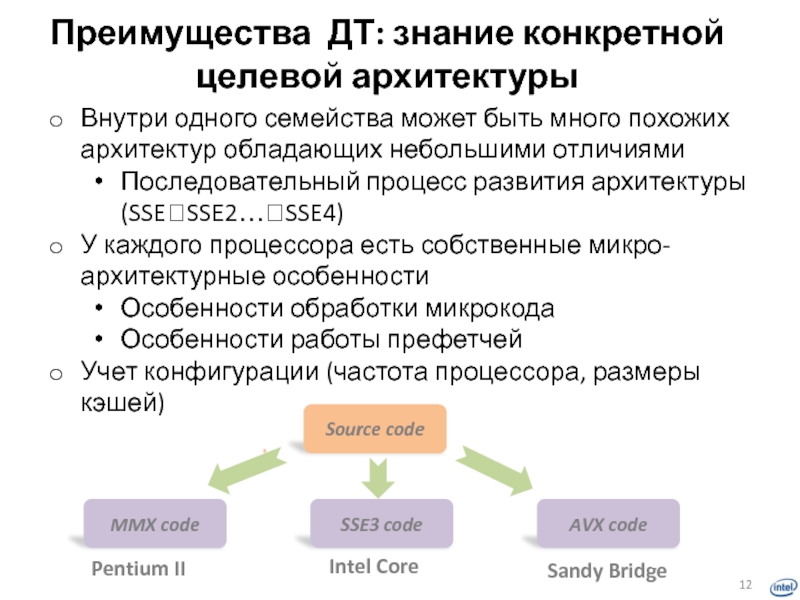

Слайд 12Преимущества ДТ: знание конкретной целевой архитектуры

Внутри одного семейства может быть

много похожих архитектур обладающих небольшими отличиями

Последовательный процесс развития архитектуры

(SSESSE2…SSE4)У каждого процессора есть собственные микро-архитектурные особенности

Особенности обработки микрокода

Особенности работы префетчей

Учет конфигурации (частота процессора, размеры кэшей)

Source code

MMX code

SSE3 code

AVX code

Sandy Bridge

Intel Core

Pentium II

Слайд 13Преимущества ДТ: знание динамического поведения программы

Профильная информация

Информация о горячих и

холодных дугах графа управления программы

Самый важный вид профиля

Позволяет оптимизировать горячие

области кода возможно в ущерб более холоднымЗначения адресов динамических переходов

Информация о значении конкретных переменных в конкретных местах кода (Value Profiling)

Профиль естественно доступен при динамической трансляции

Получение адекватного профиля при статической компиляции не всегда возможно и требует усилий

Динамическая трансляция может адаптироваться к изменению профиля

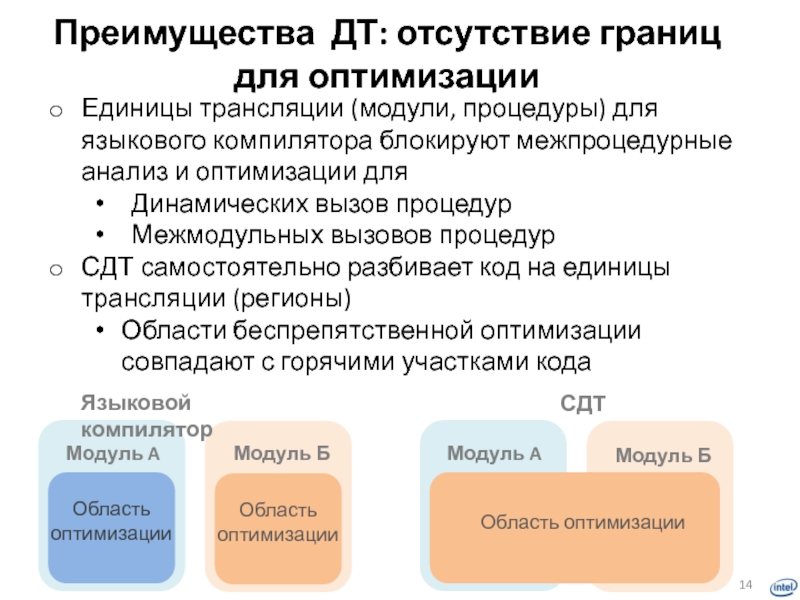

Слайд 14Преимущества ДТ: отсутствие границ для оптимизации

Единицы трансляции (модули, процедуры) для

языкового компилятора блокируют межпроцедурные анализ и оптимизации для

Динамических вызов процедур

Межмодульных

вызовов процедурСДТ самостоятельно разбивает код на единицы трансляции (регионы)

Области беспрепятственной оптимизации совпадают с горячими участками кода

Модуль A

Область оптимизации

Модуль Б

Область оптимизации

Модуль A

Область оптимизации

Модуль Б

СДТ

Языковой компилятор

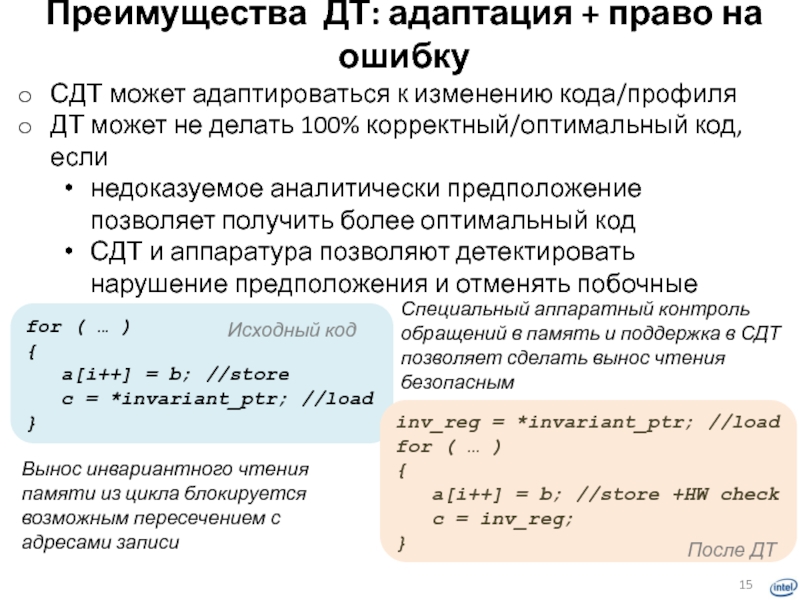

Слайд 15Преимущества ДТ: адаптация + право на ошибку

СДТ может адаптироваться к

изменению кода/профиля

ДТ может не делать 100% корректный/оптимальный код, если

недоказуемое аналитически

предположение позволяет получить более оптимальный кодСДТ и аппаратура позволяют детектировать нарушение предположения и отменять побочные эффекты нарушения

for ( … )

{

a[i++] = b; //store

c = *invariant_ptr; //load

}

inv_reg = *invariant_ptr; //load

for ( … )

{

a[i++] = b; //store +HW check

c = inv_reg;

}

Вынос инвариантного чтения памяти из цикла блокируется возможным пересечением с адресами записи

Специальный аппаратный контроль обращений в память и поддержка в СДТ позволяет сделать вынос чтения безопасным

Исходный код

После ДТ

Слайд 16Исчерпанные резервы производительности:

Тактовая частота

Конвейеризация

Избыточность (неоптимальность) кода

Актуальные резервы:

Параллелизм.

Современные процессоры обнаруживают параллельность

в последовательности кода на лету. Эти возможности сильно ограничены.

ДТ сыграет

решающую роль в enabling’е новых высокопараллельных архитектурПуть к новым архитектурам

Алг.широкий

x86 код

Узкий код

на исполн.

x86

CPU

New

CPU

Алг.широкий

x86 код

Широкий код

на исполн.

New

CPU

+ДТ

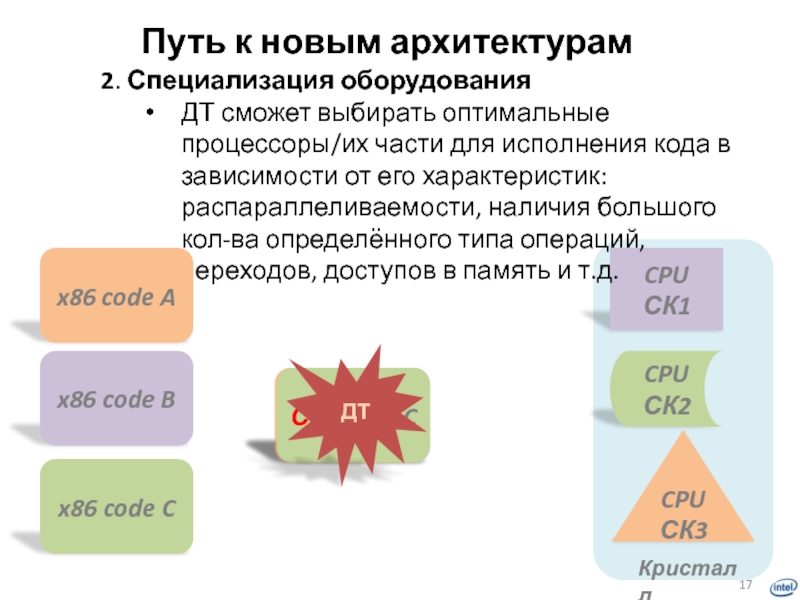

Слайд 17Кристалл

CPU

СК1

CPU СК3

CPU СК2

СК1 code B

СК3 code 1

СК2 code C

Путь к

новым архитектурам

2. Специализация оборудования

ДТ сможет выбирать оптимальные процессоры/их части для

исполнения кода в зависимости от его характеристик: распараллеливаемости, наличия большого кол-ва определённого типа операций, переходов, доступов в память и т.д.x86 code A

x86 code B

x86 code C

ДТ

Слайд 18Литература

James Smith, Ravi Nair. “Virtual Machines : Versatile Platforms for

Systems and Processes”, 2005 (book)

Richard L.Sites, Anton Chernoff, Matthew B.Kirk,

Maurice P.Marks, Scott G.Robinson, “Binary Translation”, 1992Kristy Andrews, Duane Sand, “Migrating a CISC Computer Family onto RISC via Object Code Translation”, 1992

Cristina Cifuentes, Vishv Malhotra, “Binary Translation: Static, Dynamic, Retargetable?”, 1996

Leonid Baraz, Tevi Devor, Orna Etzion, Shalom Goldenberg, Alex Skaletsky, Yun Wang, Yigal Zemach, “IA-32 Execution Layer: a two-phase dynamic translator designed to support IA-32 applications on Itanium-based systems”, 2003

Rob Hughes, Transmeta's Crusoe Microprocessor, 2000, web.archive.org/web/20080417010516/http://www.geek.com/procspec/features/transmeta/crusoe.htm

Jon Hannibal Stokes, Crusoe explored, 2000, arstechnica.com/articles/paedia/cpu/crusoe.ars/4

Darrell Boggs, Gary Brown, Nathan Tuck and K.S.Venkatraman, “Denver: NVIDIA’s First 64-bit ARM Processor”, 2015

www.elbrus.ru/2-3.htm

software.intel.com/en-us/articles/pintool

en.wikipedia.org/wiki/Rosetta_%28software%29

en.wikipedia.org/wiki/Binary_translation