Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Проектирование на ПЛИС

Содержание

- 1. Проектирование на ПЛИС

- 2. Классификация цифровых интегральных схем

- 3. МИС, СИС, БИС, СБИС – микросхемы малого,

- 4. ИСПС – интегральные схемы с программируемой структурой

- 5. Стандартные ИС – это готовые изделия, производимые

- 6. Стандартные цифровые ИСМИС и СИС используются и

- 7. Стандартные ЦИС (прод.)ИСПС – дают возможность использовать

- 8. До создания ПЛИС специализирован-ные проекты, в зависимости

- 9. Полностью заказные схемы целиком проектируются под требования

- 10. Схемы на стандартных ячейках разрабатываются на основе

- 11. БМК представляют собой стандартный полуфабрикат, который доводится

- 12. Проектирование на ПЛИС стало более дешевой альтернативой

- 13. Сравнительная таблица вариантов создания специализированных проектов на ИС

- 14. Базовые Матричные КристаллыБМК – полузаказная ИС. БМК

- 15. В БМК канальной структуры между строками и

- 16. Структура БМК

- 17. Классификация логических схем программируемой логикипо уровню интеграции

- 18. Классификация логических схем программируемой логикиРассмотрим классификацию по

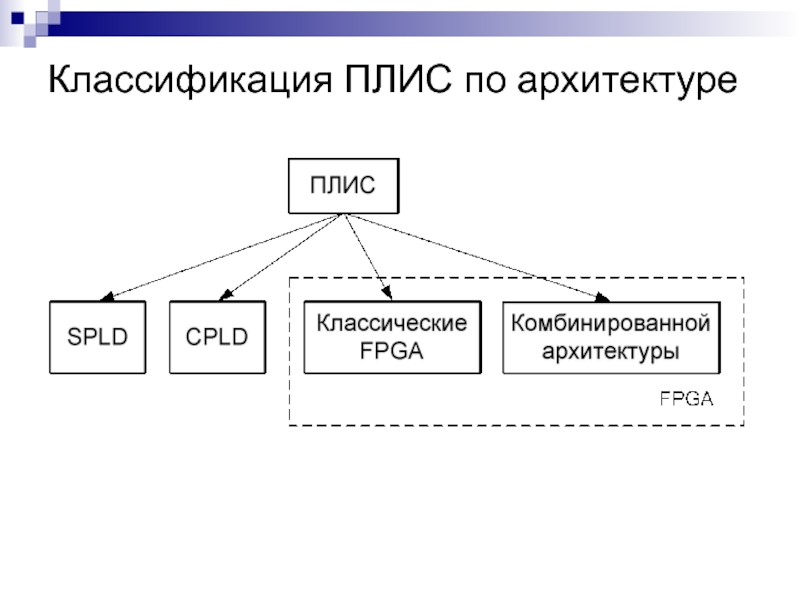

- 19. Классификация ПЛИС по архитектуре

- 20. SPLD – Simple Programmable Logic Device, простые

- 21. SPLD реализуют дизъюнктивные нормальные формы (ДНФ) переключательных

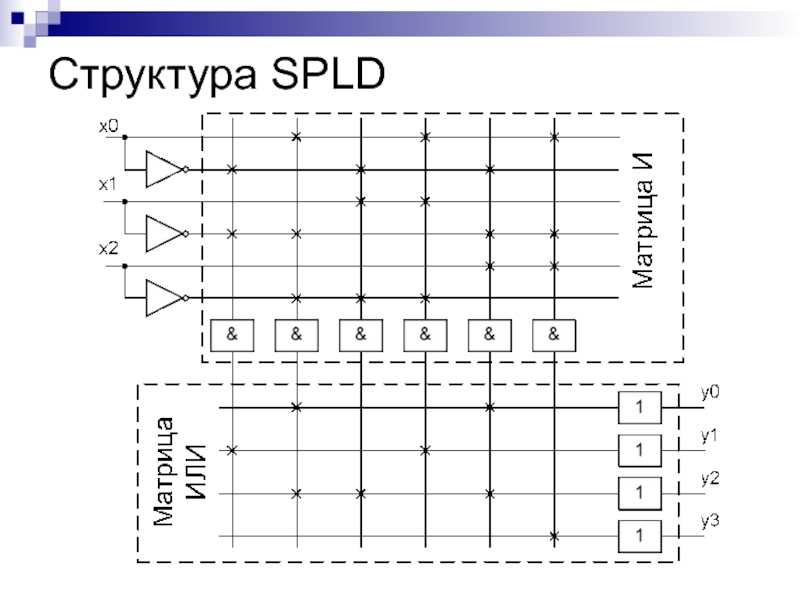

- 22. Структура SPLD

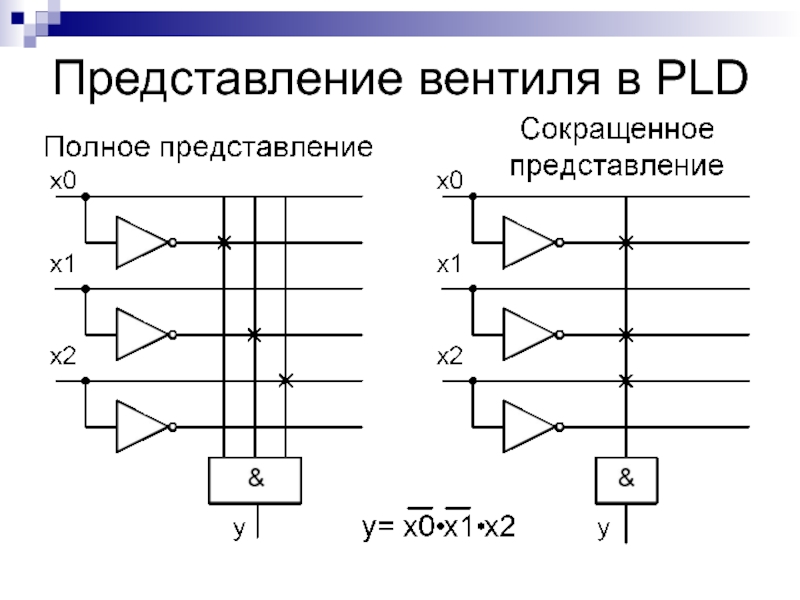

- 23. Представление вентиля в PLD

- 24. CPLD – состоят из нескольких блоков, подобных

- 25. Классические FPGAFPGA – состоят из большого числа

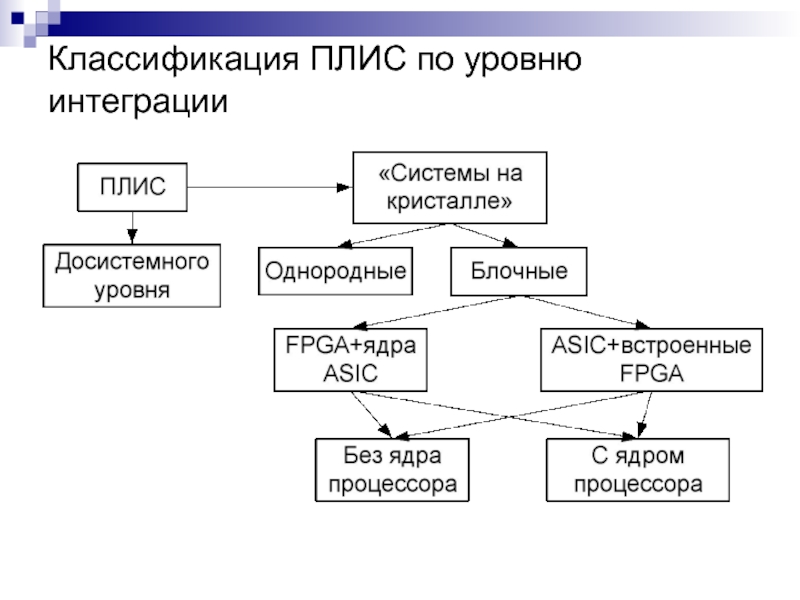

- 26. Классификация ПЛИС по уровню интеграции

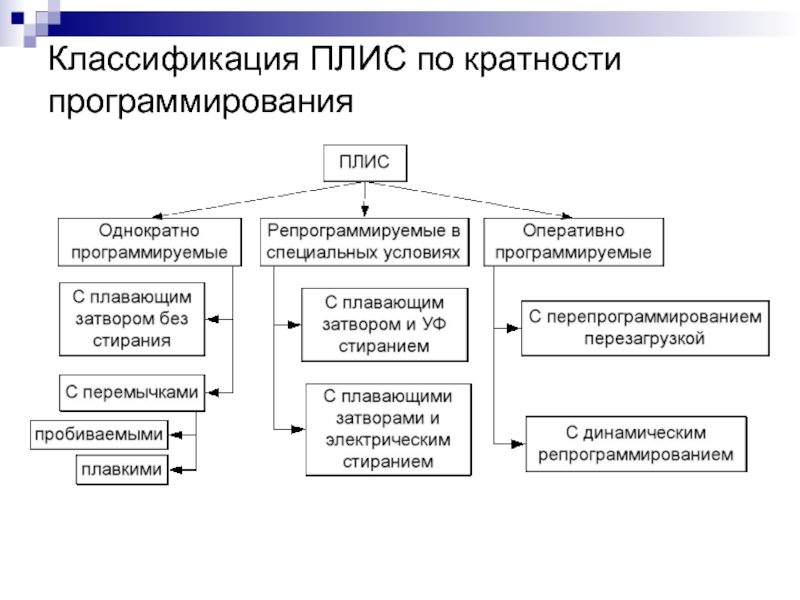

- 27. Классификация ПЛИС по кратности программирования

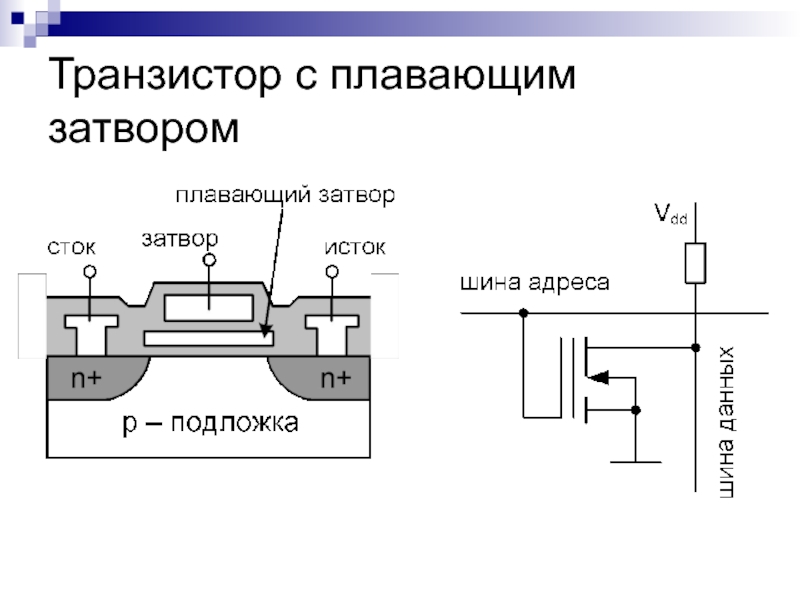

- 28. Транзистор с плавающим затвором

- 29. ПЛИС с динамическим репрограммированиемТакие ПЛИС открывают ряд

- 30. Общие (системные) свойства микросхем программируемой логикиУниверсальность и

- 31. Области применения ИСПС различных типовФормула стоимости ИС,

- 32. Слайд 32

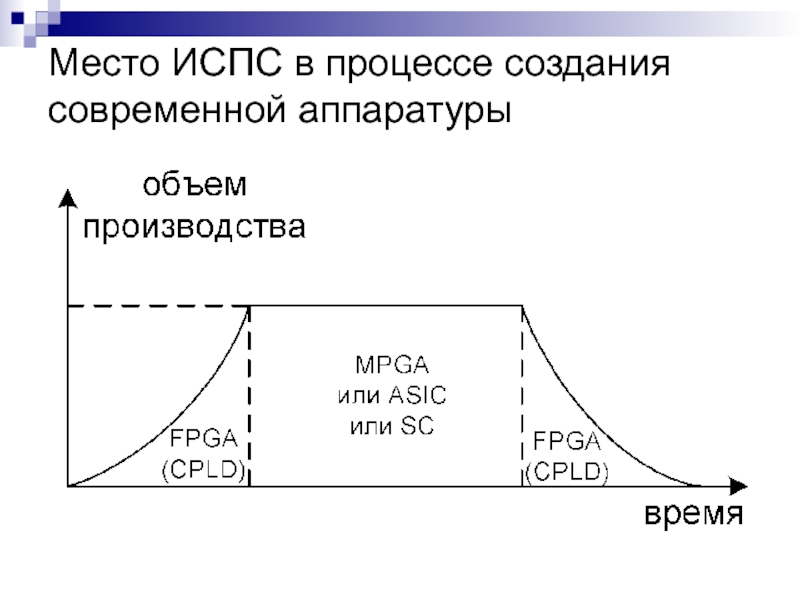

- 33. Место ИСПС в процессе создания современной аппаратурыЛьвиной

- 34. Место ИСПС в процессе создания современной аппаратуры

- 35. Скачать презентанцию

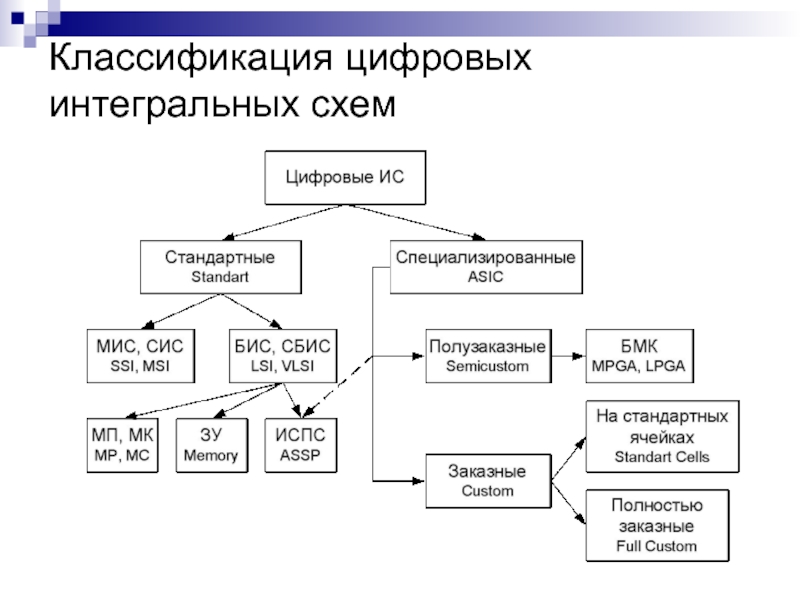

Классификация цифровых интегральных схем

Слайды и текст этой презентации

Слайд 1ЛЕКЦИЯ №13

Классификация ЦИС. Сравнение вариантов создания специализированных проектов.

Базовые Матричные Кристаллы

Классификация

ПЛИС.

Слайд 3МИС, СИС, БИС, СБИС – микросхемы малого, среднего, большого и

сверхбольшого уровня интеграции.

МП – микропроцессоры

МК – микроконтроллеры

ЗУ – запоминающие устройства

БМК

– базовый матричный кристалл Классификация цифровых интегральных схем (прод.)

Слайд 4ИСПС – интегральные схемы с программируемой структурой или ПЛИС –

программируемые логические интегральные схемы

SSI, MSI, VSI, VLSI – Small, Medium,

Large, Very Large Scale Integration.ASIC – Application Specific Integrated Circuit

ASSP – Application Specific Standard Products

MPGA – Mask Programmable Gate Array

LPGA – Laser Personalized Gate Array

Классификация цифровых интегральных схем (прод.)

Слайд 5Стандартные ИС – это готовые изделия, производимые массовыми тиражами, затраты

на проектирование мало влияют на конечную стоимость.

Специализированные ИС – проектируются

по конкретному заказу, затраты на проектирование составляют большую часть стоимости. Ограничена область применения.Классификация цифровых интегральных схем (прод.)

Слайд 6Стандартные цифровые ИС

МИС и СИС используются и сейчас для отдельных

задач, но сложные устройства делать на них не выгодно

МП и

МК широко используются для решения задач программной реализации алгоритмовБИС и СБИС запоминающих устройств массово применяются в различных системах.

Слайд 7Стандартные ЦИС (прод.)

ИСПС – дают возможность использовать ИС высокого уровня

интеграции не только в массовых (от сотен тысяч), но и

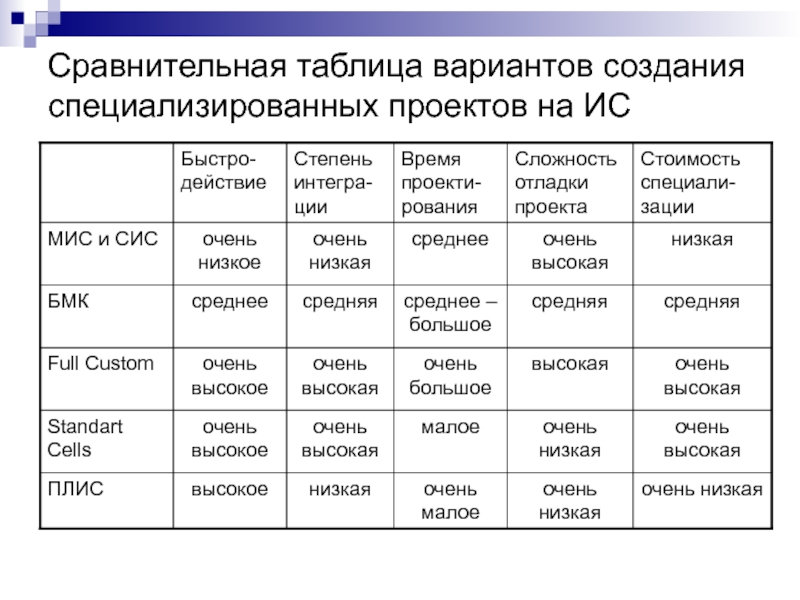

в проектах малой тиражности (вплоть до 1). Для потребителя ИСПС являются специализируемыми, а для промышленности – стандартными.Слайд 8До создания ПЛИС специализирован-ные проекты, в зависимости от сложности проекта,

его тиражности, требований к техническим и экономическим характеристикам и т.д.,

традиционно выполнялись в следующих вариантах:на МИС и СИС

на БМК

на заказных ИС спроектированных по методу стандартных ячеек

на полностью заказных ИС

Слайд 9Полностью заказные схемы целиком проектируются под требования конкретного заказчика. Проектировщик

имеет полную свободу действий, определяя схему по своему усмотрению вплоть

до уровня отдельных транзисторов. Для изготовления схемы требуется разработка полного комплекта фотошаблонов, верификация и отладка всех схемных фрагментов. Такие схемы очень дороги и имеют длительные циклы проектирования.Слайд 10Схемы на стандартных ячейках разрабатываются на основе разработанной ранее библиотеки

стандартных ячеек, которая представляет собой набор хорошо отработанных схемных фрагментов,

выполняющих определенные элементарные функции. Так же необходимо разрабатывать полный набор фотошаблонов, а характеристики несколько хуже чем у полностью заказных, но время проектирования схем на стандартных ячейках значительно меньше чем полностью заказных схем.Слайд 11БМК представляют собой стандартный полуфабрикат, который доводится до готового изделия

с помощью разработки индивидуальных межсоединений. Для специализации требуется изготовление малого

числа фотошаблонов (MPGA) или проведения цикла операций разрушения межсоединений лазерным лучом (LPGA). Сходство методов проектирования на стандартных ячейках и БМК заключается в наличии библиотек функциональных элементов. Различие – в меньшем количестве необходимых фотошаблонов.Слайд 12Проектирование на ПЛИС стало более дешевой альтернативой методам проектирования с

использованием специализированных ИС и БМК. В настоящее время проектирование цифровых

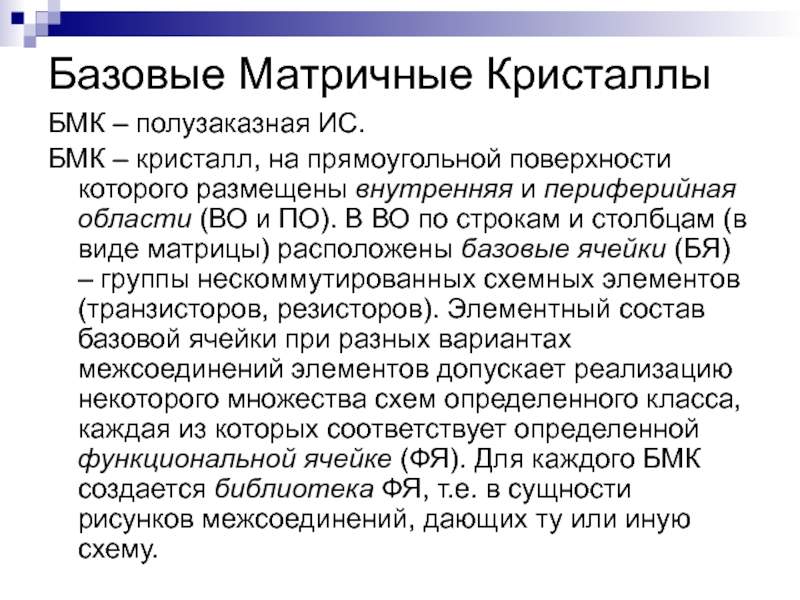

систем и логических устройств все больше перемещается в сторону широкого использования ПЛИС. ПЛИС сделали БИС/СБИС, предназначенные для решения специализированных задач, стандартной продукцией электронной промышленности.Слайд 14Базовые Матричные Кристаллы

БМК – полузаказная ИС.

БМК – кристалл, на

прямоугольной поверхности которого размещены внутренняя и периферийная области (ВО и

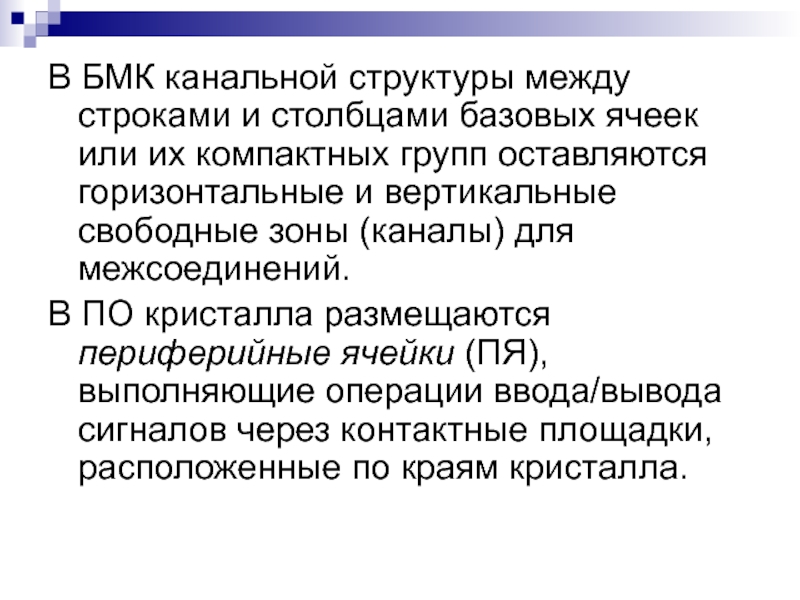

ПО). В ВО по строкам и столбцам (в виде матрицы) расположены базовые ячейки (БЯ) – группы нескоммутированных схемных элементов (транзисторов, резисторов). Элементный состав базовой ячейки при разных вариантах межсоединений элементов допускает реализацию некоторого множества схем определенного класса, каждая из которых соответствует определенной функциональной ячейке (ФЯ). Для каждого БМК создается библиотека ФЯ, т.е. в сущности рисунков межсоединений, дающих ту или иную схему.Слайд 15В БМК канальной структуры между строками и столбцами базовых ячеек

или их компактных групп оставляются горизонтальные и вертикальные свободные зоны

(каналы) для межсоединений.В ПО кристалла размещаются периферийные ячейки (ПЯ), выполняющие операции ввода/вывода сигналов через контактные площадки, расположенные по краям кристалла.

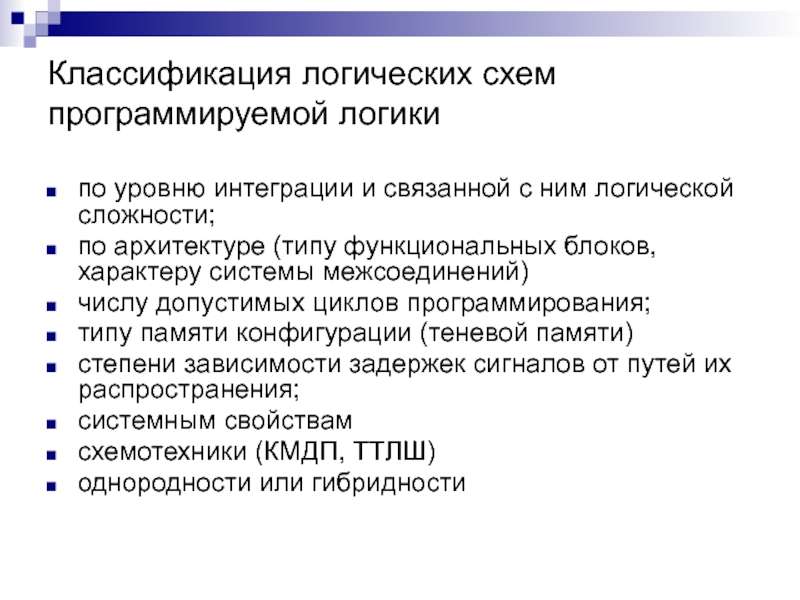

Слайд 17Классификация логических схем программируемой логики

по уровню интеграции и связанной с

ним логической сложности;

по архитектуре (типу функциональных блоков, характеру системы межсоединений)

числу

допустимых циклов программирования;типу памяти конфигурации (теневой памяти)

степени зависимости задержек сигналов от путей их распространения;

системным свойствам

схемотехники (КМДП, ТТЛШ)

однородности или гибридности

Слайд 18Классификация логических схем программируемой логики

Рассмотрим классификацию по 3-м основным признакам:

архитектуре

уровню

интеграции и однородности/гибридности

числу допустимых циклов программирования и типу памяти конфигурации

Слайд 20SPLD – Simple Programmable Logic Device, простые программируемые устройства.

ПЛМ, PLA

– программируемые логические матрицы, Programmable Logic Arrays

ПМЛ, PAL –

программируемая матричная логика, Programmable Array LogicСлайд 21SPLD реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций.

Структура:

Включенные

последовательно две матрицы элементов: И, ИЛИ.

Техническая реализация:

И-НЕ, ИЛИ-НЕ

2 матрицы И-ИЛИСлайд 24

CPLD – состоят из нескольких блоков, подобных ПМЛ, которые объединяются

с помощью программируемой коммутационной матрицы.

Фирмы выпускающие CPLD: Altera, Atmel,

Lattice Semiconductors, Cypress Semiconductors, Xilinx и др.Слайд 25Классические FPGA

FPGA – состоят из большого числа конфигурируемых логических блоков

(ЛБ), расположенных по строкам и столбцам в виде матрицы, и

трассировочных ресурсов, обеспечивающих их межсоединения.FPGA схожи с MPGA, только для специализации не требуется обращаться к производителю ИМС.

Слайд 29ПЛИС с динамическим репрограммированием

Такие ПЛИС открывают ряд новых возможностей в

области построения устройств и систем с многофункциональным использованием аппаратных ресурсов

для решения сложных задач при из разбиении на последовательные этапы и реализации разных этапов на одних и тех же быстроперестраиваемых ПЛИССлайд 30Общие (системные) свойства микросхем программируемой логики

Универсальность и связанные с нею

высокий спрос со стороны потребителей, что обеспечивает массовое производство.

Низкая стоимость,

обусловленная массовым производством и высоким процентом выхода годных при производстве вследствие регулярной структуры.Высокое быстродействие и надежность как следствие реализации на базе передовых технологий и интеграции сложных устройств на одном кристалле.

Разнообразие конструктивного исполнения.

Разнообразие в выборе напряжений питания и параметров сигналов ввода/вывода, а также режимов снижения мощности.

Наличие эффективных САПР, малое время проектирования и отладки проектов, а также выхода продукции на рынок.

Простота модификации проектов на любых стадиях их разработки

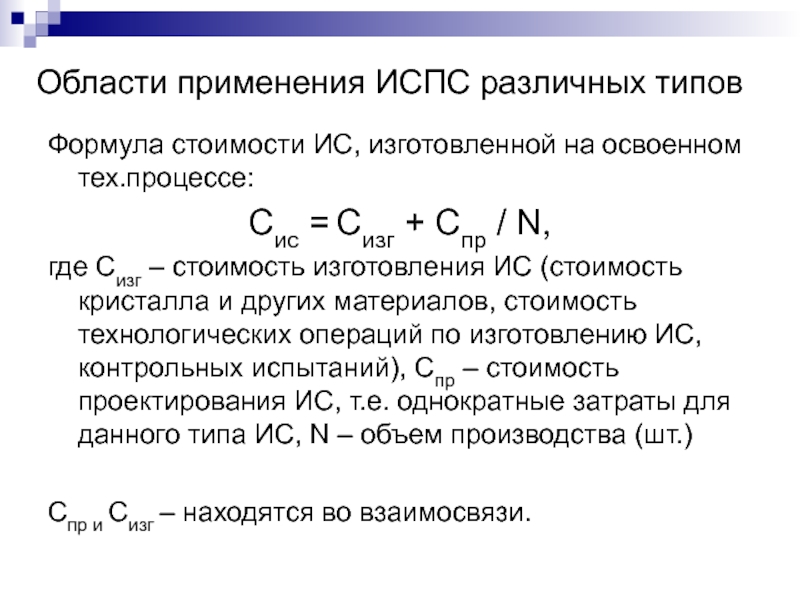

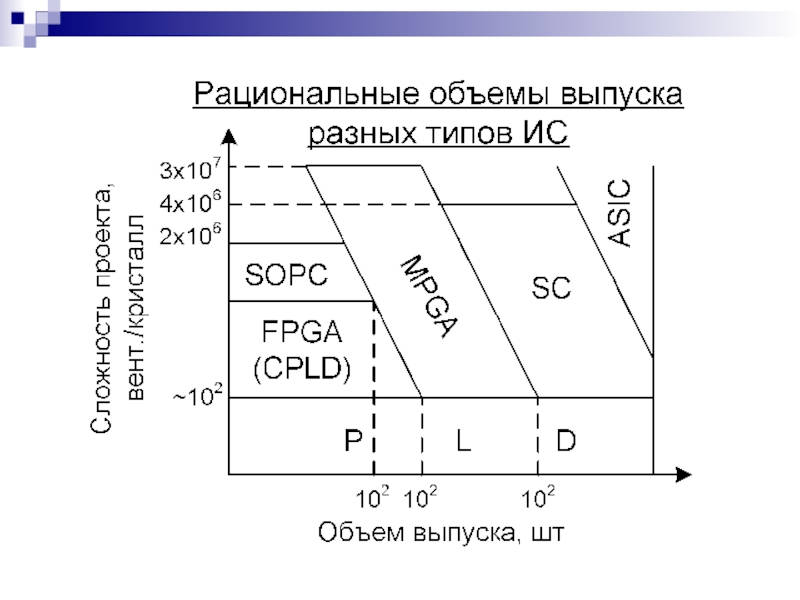

Слайд 31Области применения ИСПС различных типов

Формула стоимости ИС, изготовленной на освоенном

тех.процессе:

Сис = Сизг + Спр / N,

где Сизг – стоимость

изготовления ИС (стоимость кристалла и других материалов, стоимость технологических операций по изготовлению ИС, контрольных испытаний), Спр – стоимость проектирования ИС, т.е. однократные затраты для данного типа ИС, N – объем производства (шт.)Спр и Сизг – находятся во взаимосвязи.

Слайд 33Место ИСПС в процессе создания современной аппаратуры

Львиной долей инженерных разработок

в современной России является использование ПЛИС и МП(МК), а также

систем, включающих в себя и то и другое.Целесообразность использования того или иного типа СпИС определяется в основном минимальным временем выхода конечного изделия на рынок (time-to-market).