Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Раздел 3 Классификации параллельных ВС 1

Содержание

- 1. Раздел 3 Классификации параллельных ВС 1

- 2. Классификации параллельных системКлассификация Флинна – самая старая

- 3. Классификация Флинна (1966-72, IBM)ОКОД — Вычислительная система с одиночным

- 4. SISD, Single Instruction Single Data

- 5. SIMD, Single Instruction, Multiple Data

- 6. MISD, Multiple Instruction Single Data

- 7. MIMD, Multiple Instruction Multiple Data

- 8. Классификация Хокни (Roger W. Hockney)Он расширил группу

- 9. Классификация ФенгаКлассификационные признаки:число n бит в машинном

- 10. Классификация ХэндлераВ основу классификации В.Хендлер закладывает явное описание возможностей параллельной и конвейерной обработки информации вычислительной системой.

- 11. Классификация Скилликорна (1989)Основывается на следующих характеристиках:Количество процессоров

- 12. Резюме по классификациям 1960…90 ггВсе они в

- 13. Симметричные мультипроцессоры SMP(1)

- 14. Симметричные мультипроцессоры SMP(2)а) Все процессоры и общая

- 15. Симметричные мультипроцессоры SMP(3)Узкое место SMP – магистраль

- 16. Симметричные мультипроцессоры SMP(4)SMP-система с доступом к памяти через коммуни-кационную систему (например, AMD HyperTransport)

- 17. Что такое SMP -- резюме Несколько процессоров

- 18. Системы MPP(1) (Massively Parallel Processors)Основной классификационный признак

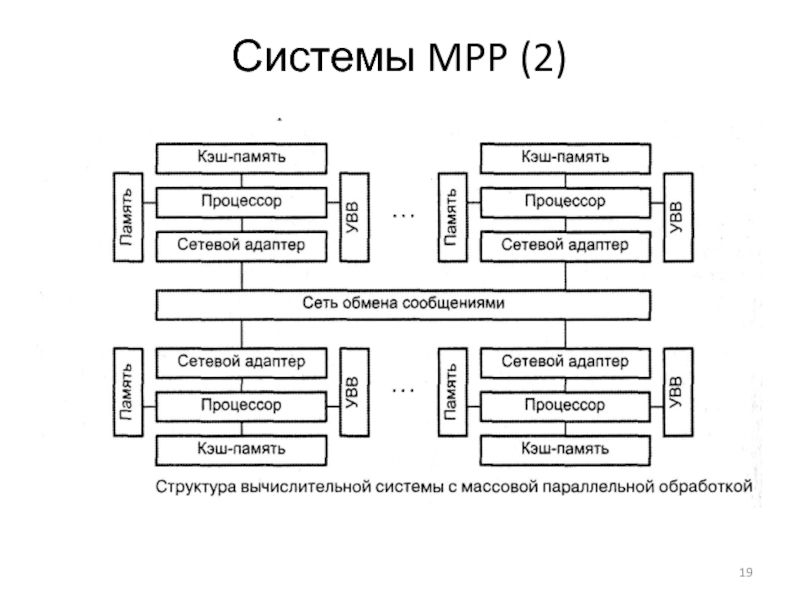

- 19. Системы MPP (2)

- 20. Что такое MPP?Узлы на стандартных процессорах (часто

- 21. Что такое кластеры?Кластер – группа взаимно соединенных

- 22. Преимущества кластеризацииАбсолютная масштабируемость.Наращиваемая масштабируемость.Высокий коэффициент готовности (надежность)Хорошее соотношение цена/производительность.

- 23. Можно почитать учебники:Архитектура компьютера. 5-е изд. /

- 24. Скачать презентанцию

Классификации параллельных системКлассификация Флинна – самая старая и известная.Другие классификации параллельных ВС: – Хокни – Фенга – Хэндлера – Шнайдера – Шора – СкилликорнаСовременное состояние – три вида параллельных

Слайды и текст этой презентации

Слайд 2Классификации параллельных систем

Классификация Флинна – самая старая и известная.

Другие классификации

параллельных ВС: – Хокни – Фенга – Хэндлера – Шнайдера – Шора – Скилликорна

состояние – три вида параллельных ВССлайд 3Классификация Флинна (1966-72, IBM)

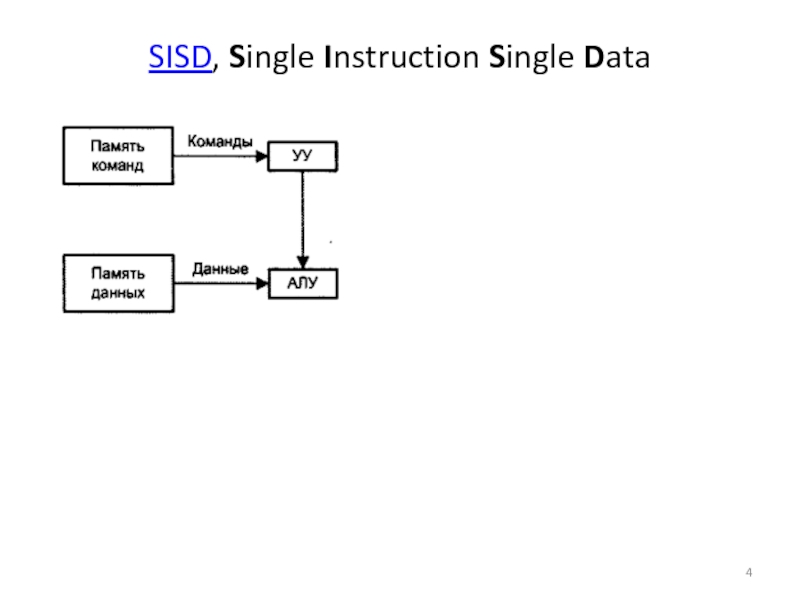

ОКОД — Вычислительная система с одиночным потоком команд и одиночным потоком

данных

(SISD, Single Instruction stream over a Single Data stream).

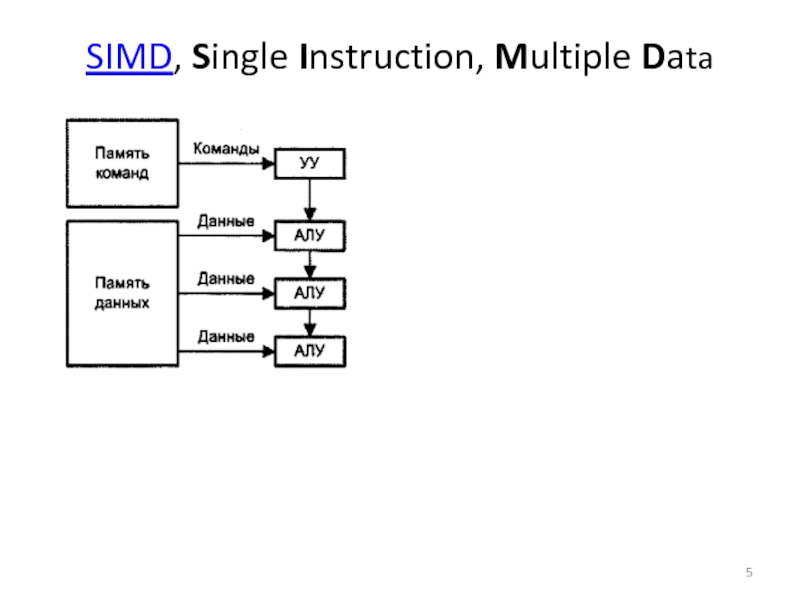

ОКМД — Вычислительная система с одиночным потоком команд и множественным

потокомданных

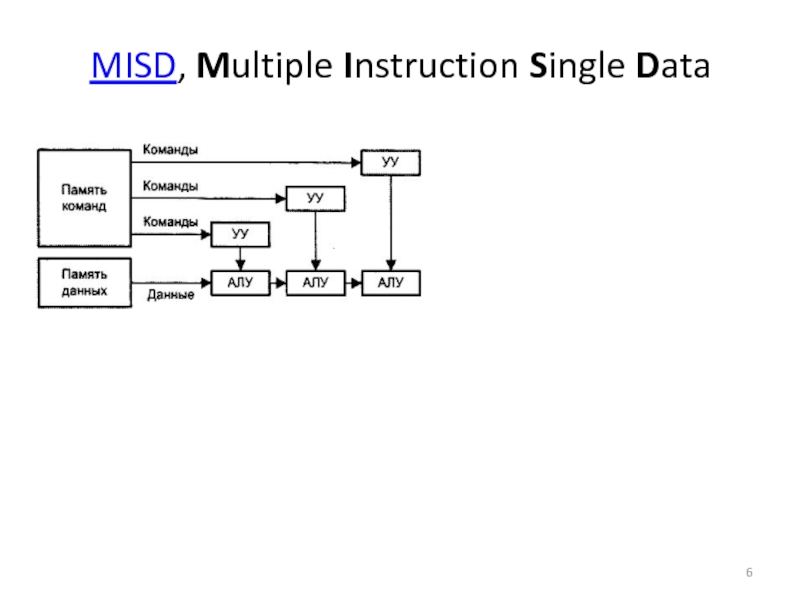

(SIMD, Single Instruction, Multiple Data).МКОД — Вычислительная система со множественным потоком команд и одиночным потокомданных (MISD, Multiple Instruction Single Data).

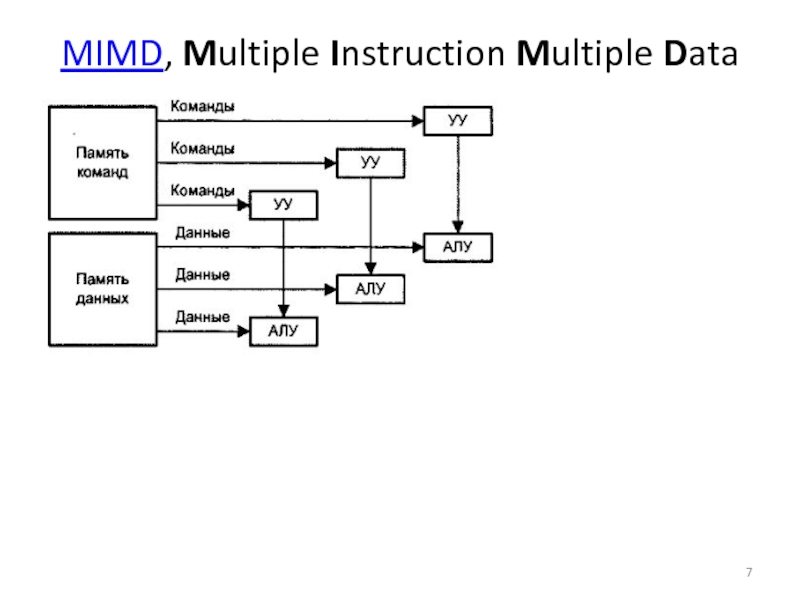

МКМД — Вычислительная система со множественным потоком команд и множественным потоком данных (MIMD, Multiple Instruction Multiple Data).

(переделать , чтобы на слайде для одного класса – словесное описание и картинка)

Слайд 8Классификация Хокни (Roger W. Hockney)

Он расширил группу МИМД:

Переключаемые — с общей

памятью и с распре-делённой памятью.

Конвейерные.

Сети — регулярные решётки, гиперкубы, иерар-хические структуры,

изменяющие конфигурацию.В класс переключаемых машин попадают машины, в которых возможна связь каждого процессора с каждым, реализуемая с помощью переключателей

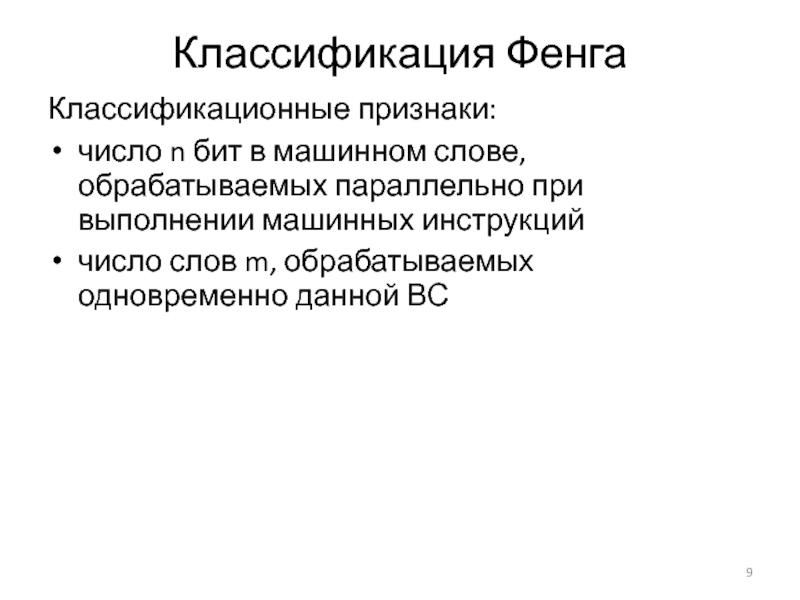

Слайд 9Классификация Фенга

Классификационные признаки:

число n бит в машинном слове, обрабатываемых параллельно

при выполнении машинных инструкций

число слов m, обрабатываемых одновременно данной ВС

Слайд 10Классификация Хэндлера

В основу классификации В.Хендлер закладывает явное описание возможностей параллельной

и конвейерной обработки информации вычислительной системой.

Слайд 11Классификация Скилликорна (1989)

Основывается на следующих характеристиках:

Количество процессоров команд IP (Устр

Упр)

Число ЗУ команд IM

Тип переключателя между IP и IM

Количество процессоров

данных DP (АЛУ)Число ЗУ данных DM

Тип переключателя между DP и DM

Тип переключателя между IP и DP

Тип переключателя между DP и DP

Слайд 12Резюме по классификациям 1960…90 гг

Все они в настоящее время неактуальны,

посколь-ку используют разные наборы классификационных признаков.

Современные параллельные системы все могут

быть отнесены только к классу MIMD (Флинн).В настоящее время используется классификация, содержащая три класса:

SMP – Симметричные мультипроцессоры

MPP (Massively Parallel Processors) – Массивно-паралаллельные системы

Кластерные системы

Слайд 14Симметричные мультипроцессоры SMP(2)

а) Все процессоры и общая память связаны через

единственную параллельную адресуемую магистраль

б) Каждый процессор имеет локальную КЭШ-память, и

они связаны с общей основной памятью через един-ственную параллельную адресуемую магистральв) Каждый процессор имеет локальные блоки основ-ной памяти (и может быть, КЭШ), все процессоры связаны с общей памятью через параллельную адресуемую магистраль.

Каждый из процессоров имеет равноправный доступ к общей памяти, но не имеет доступа к локальной памяти и к КЭШам других процессоров.

Слайд 15Симметричные мультипроцессоры SMP(3)

Узкое место SMP – магистраль доступа к памяти.

Все процессоры конкурируют за доступ к ней. Способ ослабления: индивидуальная

память для отдельных процессоров (рис.SMP1-(в))Максимальное количество процессоров в SMP не удается сделать больше 32-х.

Для уменьшения конкуренции за общую память: может быть организован множественный доступ к памяти через коммуникационную подсистему, сложно, но к памяти могут обращаться одновре-менно несколько процессоров (см. след. слайд).

Слайд 16Симметричные мультипроцессоры SMP(4)

SMP-система с доступом к памяти через коммуни-кационную систему

(например, AMD HyperTransport)

Слайд 17Что такое SMP -- резюме

Несколько процессоров используют общую память

Каждый

процессор имеет КЭШ (и, может быть, локальную память)

Процессоры и разделяемая

память связаны общей параллельной адресуемой магистралью.Магистраль разделяется всеми процессорами, и поэтому является «узким» местом.

Число процессоров не превышает 32.

На многопроцессорном узле SMP работает локальная многозадачная ОС.

Несколько узлов SMP могут быть связаны коммуника-ционной сетью (напр Infiniband) – гибридная система.

Слайд 18Системы MPP(1)

(Massively Parallel Processors)

Основной классификационный признак – организа-ция системного ПО:

на совокупности узлов работа-ет одна ОС с поддержкой многопроцессорности.

Узел нельзя

использовать как отдельный компьютер.Физически распределенная память.

Сеть соединений между узлами с высокой пропуск-ной способностью и малыми задержками

Высокая масштабируемость (сотни тысяч узлов)

Слайд 20Что такое MPP?

Узлы на стандартных процессорах (часто это SMP)

Узлы связаны

сетью с высокой пропускной способнос-тью и малыми задержками (Infiniband, Ethernet

10 Гбит) Система MPP – «сильно связанная система»Высокая масштабируемость (105++ узлов)

Каждый из узлов НЕ может быть использован в качестве самостоятельного компьютера.

Характерная черта МРР-систем — наличие единст-венного управляющего устройства (процессора, узла), на большое число подчиненных узлов.

Узлы SMP и/или MPP часто используются как блоки для построения сверхмощных суперкомпьютеров.

Слайд 21Что такое кластеры?

Кластер – группа взаимно соединенных вычисли-тельных узлов, работающих

совместно

В качестве узла кластера может выступать как одно-процессорная ВМ,

так и ВС типа SMP или МРР.В качестве узлов кластеров могут использоваться как одинаковые ВС (гомогенные кластеры), так и разные (гетерогенные кластеры).

Узел кластера можно использовать как отдельный компьютер

Задержка при обмене между узлами гораздо выше, нежели при обмене между процессором и памятью внутри узла.

По своей архитектуре кластерная ВС является слабо связанной системой.

Слайд 22Преимущества кластеризации

Абсолютная масштабируемость.

Наращиваемая масштабируемость.

Высокий коэффициент готовности (надежность)

Хорошее соотношение цена/производительность.

Слайд 23Можно почитать учебники:

Архитектура компьютера. 5-е изд. / Танненбаум Э. ‑

СПб.: Питер, 2007,

Глава 8

Организация ЭВМ. 5 е изд. /

К. Хамахер, З. Вранешич, С. Заки. ‑ СПб.: Питер; 2003.

Глава 12Организация ЭВМ и систем: учебник для вузов. 2-е изд./ Б.Я. Цилькер, С.А. Орлов. – СПб.: Питер, 2007. Главы 10…14