Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Тестирование интегральных схем

Содержание

- 1. Тестирование интегральных схем

- 2. НеобходимостьТестирование ИС необходимо из-за несовершенства производственного процесса.

- 3. Цели и задачиЦель тестирования – выявление отказов

- 4. Способ обнаружения неисправностейСуществует единственный способ обнаружения неисправностей:На

- 5. Категории неисправностейЛогические – неисправности, влияющие на логику

- 6. Типы логических неисправностейКонстантные неисправности с залипанием в

- 7. Константные неисправности с залипанием в 1 или

- 8. Константные неисправности с залипанием в открытом состоянииНеисправности,

- 9. Константные неисправности типа обрывНеисправности, приводящие к слабому

- 10. Неисправности типа замыканиеПриводят к передаче на ветвь

- 11. Моделирование неисправностейИспользуется модель константной неисправности:ПростотаОписывает влияние физической неисправности на входные/выходные сигналы

- 12. Модель 2х-входового вентиля И

- 13. Количество неисправностейДля k сигнальных линий существует 2k

- 14. Множественные неисправностиЧисло комбинаций ошибок может быть очень

- 15. Места возникновения неисправностейВсего в схеме возможно 10

- 16. Тестирование ИСВходные комбинации, используемые для обнаружения неисправностей

- 17. Методы поиска неисправностейТабличный (по таблице истинности). Подходит

- 18. Прямой проход активизации путиВ точку с предположительной

- 19. Обратный проход активизации путиУстанавливаются входные значения для

- 20. Упрощение поиска неисправностейДля упрощения поиска неисправностей вводится

- 21. Алгоритм РотаИспользование D подразумевает, что ни один

- 22. Поиск неисправностей по D-алгоритмуКаждый вентиль на пути

- 23. Эквивалентные неисправностиЭквивалентные неисправности – это неисправности, которые

- 24. Не обнаруживаемые неисправностиСуществуют схемы, в которых нельзя

- 25. Причина не обнаружения неисправностейИзбыточность схемы – фактор в результате которого схемы не чувствительны к тестированияF=AB+AC+BC=AB+BCВСАВСАВАС

- 26. Тестирование последовательных схемДля тестирования последовательных схем необходимо:Установить

- 27. Метод сканирования путиИспользуется для обнаружения переменных состоянийРежимы

- 28. Модель Мура для тестирования по методу сканирования пути

- 29. Проверка работоспособности последовательных схемТестирование триггеровТестирование комбинационной логики следующего состоянияТестирование комбинационной логики текущего состояния

- 30. Тестирование триггеровОсуществляется через тестирование регистра сдвигаMode_select=1Через мультиплексор

- 31. Тестирование комбинационной логики следующего состоянияДля тестирования комбинационной

- 32. Тестирование комбинационной логики текущего состоянияЗадается тестовая последовательность

- 33. Встроенное самотестированиеИспользуются внутренние генераторы последовательностей, а весь алгоритм тестирования соответствует методу сканирования пути

- 34. Периферийное сканированиеСдвиговый регистр подключается ко входам микросхемы

- 35. Скачать презентанцию

НеобходимостьТестирование ИС необходимо из-за несовершенства производственного процесса. Схемы могут иметь физические дефекты, называемые отказами, которые появляются на этапе производства и непредвиденным образом меняют поведение устройства

Слайды и текст этой презентации

Слайд 2Необходимость

Тестирование ИС необходимо из-за несовершенства производственного процесса. Схемы могут иметь

Слайд 3Цели и задачи

Цель тестирования – выявление отказов и идентификация неисправных

микросхем

Тестирование – важная задача, поскольку в схеме может происходить огромное

количество неисправностейСлайд 4Способ обнаружения неисправностей

Существует единственный способ обнаружения неисправностей:

На первичные входы (входные

выводы микросхемы) поднимаются известные тестовые сигналы

Результат снимается на первичных выходах

(выходные выводы микросхемы) Если эти сигналы отличаются от ожидаемых, то возможны неисправности или ошибки проектирования

Слайд 5Категории неисправностей

Логические – неисправности, влияющие на логику работы схемы (выходные

логические функции принимают значения отличные от требуемых)

Параметрические – неисправности, влияющие

на параметры схемы (напряжение, ток, сопротивление, период, частота и т.д.) (рассматриваться не будет)Слайд 6Типы логических неисправностей

Константные неисправности с залипанием в единице или в

нуле (stuck-at-0, stuck-at-1)

Константные неисправности с залипанием в открытом состоянии (stuck-on-fault),

или неисправности транзисторного уровняКонстантные неисправности типа обрыв (stuck-open-fault)

Неисправности типа замыкание (bridging fault)

Слайд 7Константные неисправности с залипанием в 1 или в 0

Неисправности, когда

на входе или на выходе схемы устанавливается постоянный уровень логической

единицы или уровень логического нуляПроисходит в результате соединения соответствующего выхода или соответствующего входа с питанием или землей схемы

Слайд 8Константные неисправности с залипанием в открытом состоянии

Неисправности, приводящие к установке

на выходе схемы среднего значения между логическим нулем или логической

единицейВозникают в результате установки одного из транзисторов в постоянно открытом состоянии

Слайд 9Константные неисправности типа обрыв

Неисправности, приводящие к слабому изменению состояния схемы,

в момент изменения внешних состояний

Возникают в результате нахождения одного

из транзисторов в закрытом режиме (разомкнутая цепь – большой импеданс)Слайд 10Неисправности типа замыкание

Приводят к передаче на ветвь сигналов, соответствующих другим

логическим переменным

Возникают в результате короткого замыкания входных, выходных или внутренних

ветвей схемы (между двумя различными частями схемы)Слайд 11Моделирование неисправностей

Используется модель константной неисправности:

Простота

Описывает влияние физической неисправности на входные/выходные

сигналы

Слайд 13Количество неисправностей

Для k сигнальных линий существует 2k различных комбинаций одиночных

неисправностей

Для каждой сигнальной линии существует три возможных состояния:

Свободное от неполадок

С

постоянной логической 1С постоянным логическим 0

Следовательно для k сигнальных линий существует 3k комбинаций возможных состояний

Слайд 14Множественные неисправности

Число комбинаций ошибок может быть очень велико

Анализ множественных неисправностей

– задача весьма сложная, и невыполнимая

Большинство множественных неисправностей обнаруживаются при

поиске одиночных ошибокСлайд 15Места возникновения неисправностей

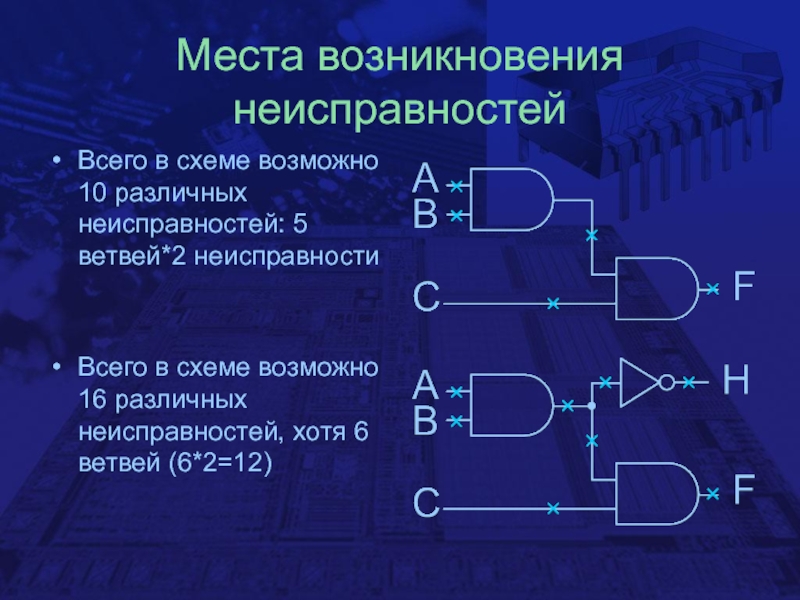

Всего в схеме возможно 10 различных неисправностей: 5

ветвей*2 неисправности

Всего в схеме возможно 16 различных неисправностей, хотя 6

ветвей (6*2=12)Слайд 16Тестирование ИС

Входные комбинации, используемые для обнаружения неисправностей называются тестовыми векторами

Набор

тестовых векторов, обеспечивающий проверку всех возможных состояний называется тестовым набором

Относительное

число ошибок, которое можно найти с помощью теста называется покрытием неисправностейСлайд 17Методы поиска неисправностей

Табличный (по таблице истинности). Подходит только для простых

схем.

Алгебраический (по выходной функции). Подходит только для простых схем.

Метод активизации

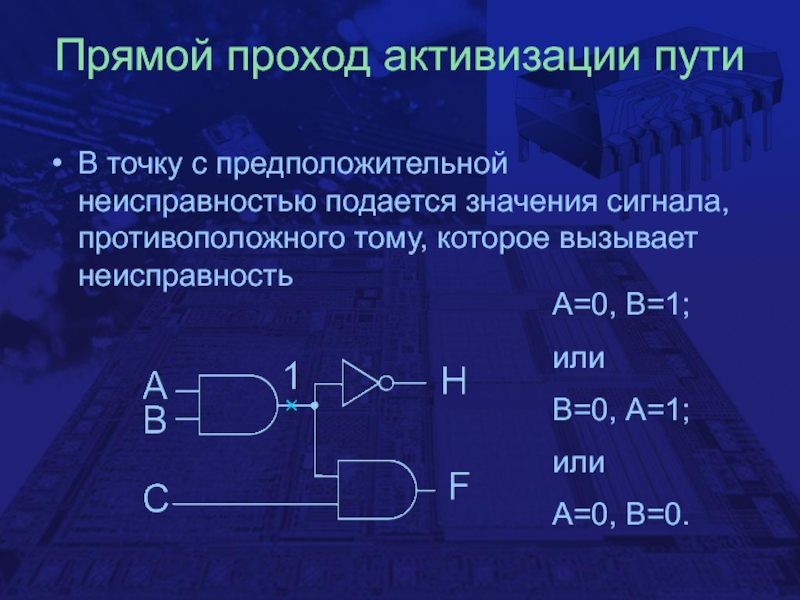

пути (Path sensitization metod). Подходит для схем любого уровня сложности.Слайд 18Прямой проход активизации пути

В точку с предположительной неисправностью подается значения

сигнала, противоположного тому, которое вызывает неисправность

А=0, B=1;

или

В=0, A=1;

или

A=0, B=0.

Слайд 19Обратный проход активизации пути

Устанавливаются входные значения для передачи логического уровня

сигнала в точке неисправности сквозь схему до выхода, где его

можно наблюдать Если Н – ненаблюдаемый выход, то чтобы на F обнаружить неисправность внутренней ветви необходимо установить

С=1

Слайд 20Упрощение поиска неисправностей

Для упрощения поиска неисправностей вводится обозначение сигнала

D показывает,

что сигнал =1, если схема исправна и =0, если нет

D

показывает, что сигнал =0, если схема исправна и =1, если нетДанный метод носит название D-алгоритма, или алгоритма Рота

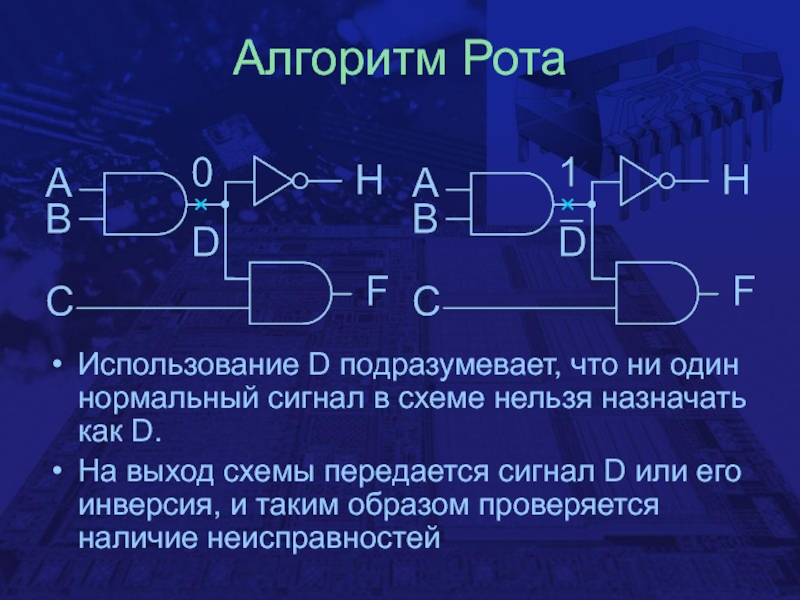

Слайд 21Алгоритм Рота

Использование D подразумевает, что ни один нормальный сигнал в

схеме нельзя назначать как D.

На выход схемы передается сигнал D

или его инверсия, и таким образом проверяется наличие неисправностейСлайд 22Поиск неисправностей по D-алгоритму

Каждый вентиль на пути до первичного выхода

должен быть активизирован

Если схема имеет неисправность внутри, то:

Сначала устанавливаются состояния

для получения D на выходеА затем состояния, для обнаружения неисправности

Слайд 23Эквивалентные неисправности

Эквивалентные неисправности – это неисправности, которые детектируются одними и

теми же тестовыми воздействиями (тестовыми векторами)

Если существует хотя бы один

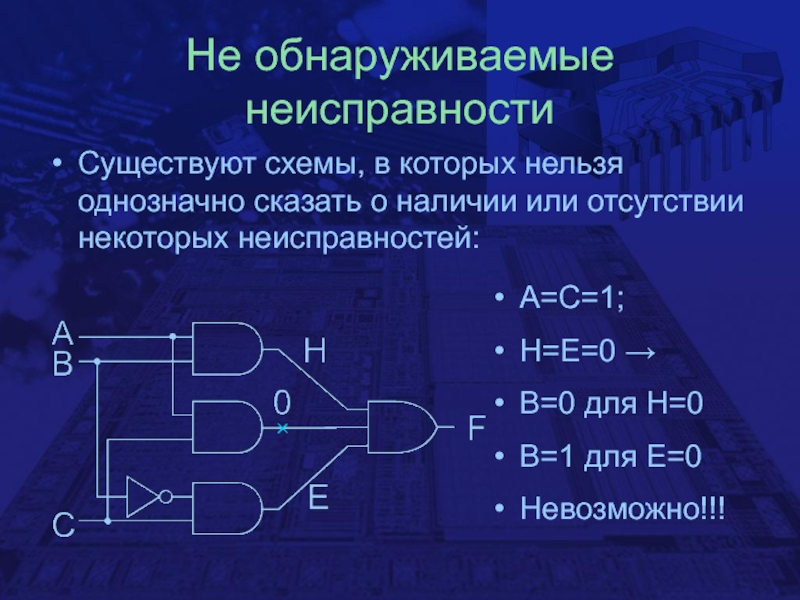

тестовый вектор, обнаруживающий одну неисправность и не обнаруживающий другую, то неисправности не эквивалентныСлайд 24Не обнаруживаемые неисправности

Существуют схемы, в которых нельзя однозначно сказать о

наличии или отсутствии некоторых неисправностей:

А=С=1;

H=E=0 →

B=0 для H=0

B=1 для E=0

Невозможно!!!

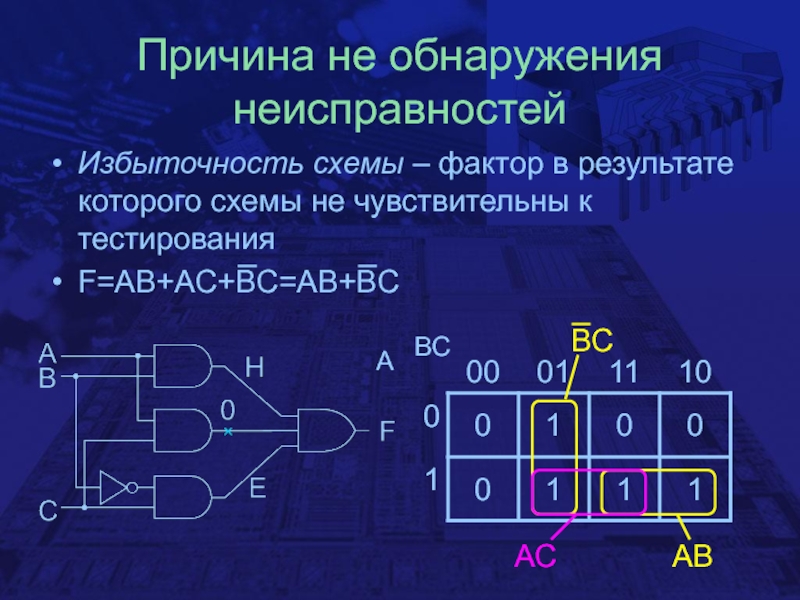

Слайд 25Причина не обнаружения неисправностей

Избыточность схемы – фактор в результате которого

схемы не чувствительны к тестирования

F=AB+AC+BC=AB+BC

ВС

А

ВС

АВ

АС

Слайд 26Тестирование последовательных схем

Для тестирования последовательных схем необходимо:

Установить схему в известное

состояние

После подачи сигналов состояние должно измениться в другое известное состояние

При

этом оба состояния (текущее и следующее) должны поддаваться наблюдениюСлайд 27Метод сканирования пути

Используется для обнаружения переменных состояний

Режимы работы схемы:

Нормальный режим

– схема работает согласно ТЗ

Режим сканирования пути – триггеры подключаются

как сдвиговый регистр с последовательным входом и последовательным выходомСлайд 29Проверка работоспособности последовательных схем

Тестирование триггеров

Тестирование комбинационной логики следующего состояния

Тестирование комбинационной

логики текущего состояния

Слайд 30Тестирование триггеров

Осуществляется через тестирование регистра сдвига

Mode_select=1

Через мультиплексор триггеры подключаются последовательно

и выстраиваются в сдвиговый регистр, по которому двигается известная последовательность

кода и проводится его сравнение с кодом, полученным на выходеСлайд 31Тестирование комбинационной логики следующего состояния

Для тестирования комбинационной логики следующего состояния

необходим доступ ко входам и выходам участка схемы

Входы доступны на

прямую, а выходы частично доступны, через выходы триггеровЗначения загружаются в триггеры и дальше переключается в режим тестирования, когда полученная последовательность на выходах триггеров сдвигается и считывается

Слайд 32Тестирование комбинационной логики текущего состояния

Задается тестовая последовательность на триггеры в

режиме тестирования и затем проверяется в какое состояние они перейдут

Фактически происходит тестирование таблицы состояний

Слайд 33Встроенное самотестирование

Используются внутренние генераторы последовательностей, а весь алгоритм тестирования соответствует

методу сканирования пути

Слайд 34Периферийное сканирование

Сдвиговый регистр подключается ко входам микросхемы и её выходам

и строится большая длинная последовательность полученных сигналов

Метод является стандартом тестирования

электронных плат IEEE 1149.1По данному стандарту в состав каждой микросхемы входит не только регистр сдвига, но и дополнительная логика, которая позволяет контролировать сам процесс тестирования