Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Типы корпусов радиоэлектронных компонентов

Содержание

- 1. Типы корпусов радиоэлектронных компонентов

- 2. Организации занимающиеся стандартизацией в САПРСТАНДАРТИ-ЗАЦИЯ ПОСАДОЧНЫХ МЕСТ

- 3. Стандарт IPC 7351Определяет размеры контактных площадок

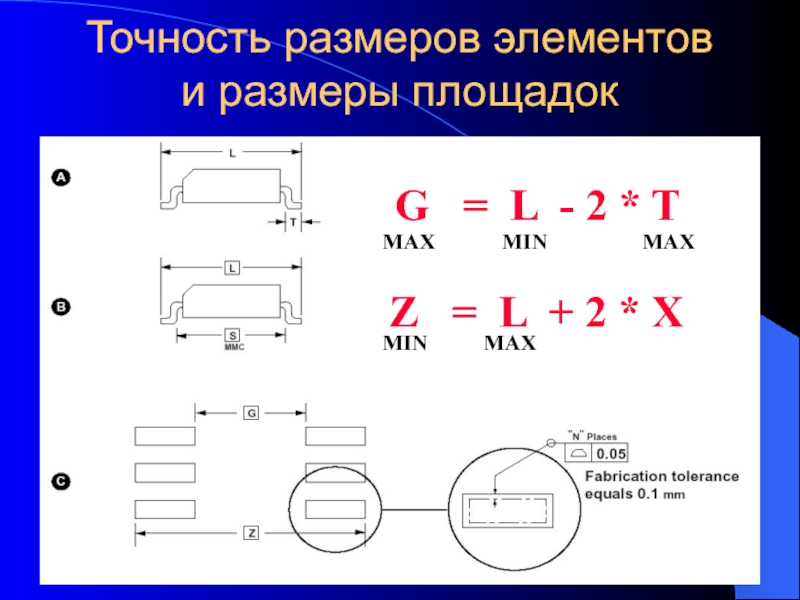

- 4. Точность размеров элементов и размеры площадокG

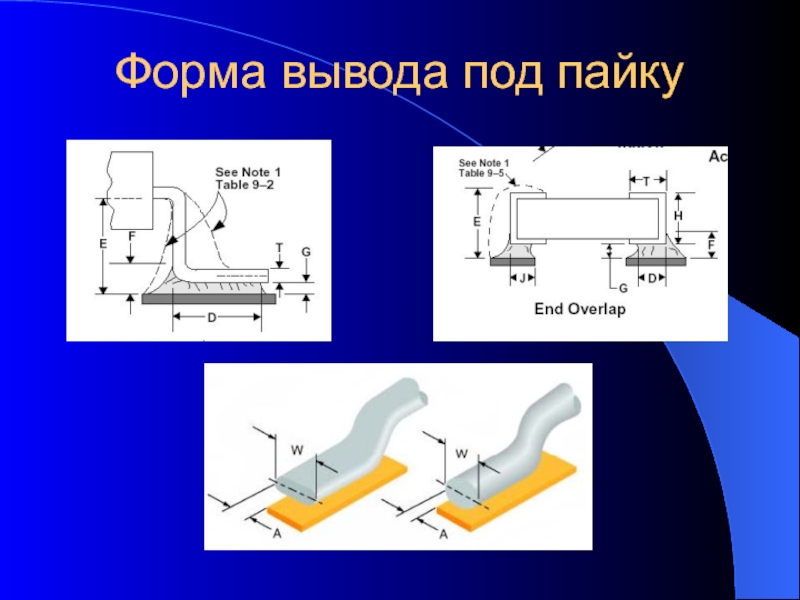

- 5. Форма вывода под пайку

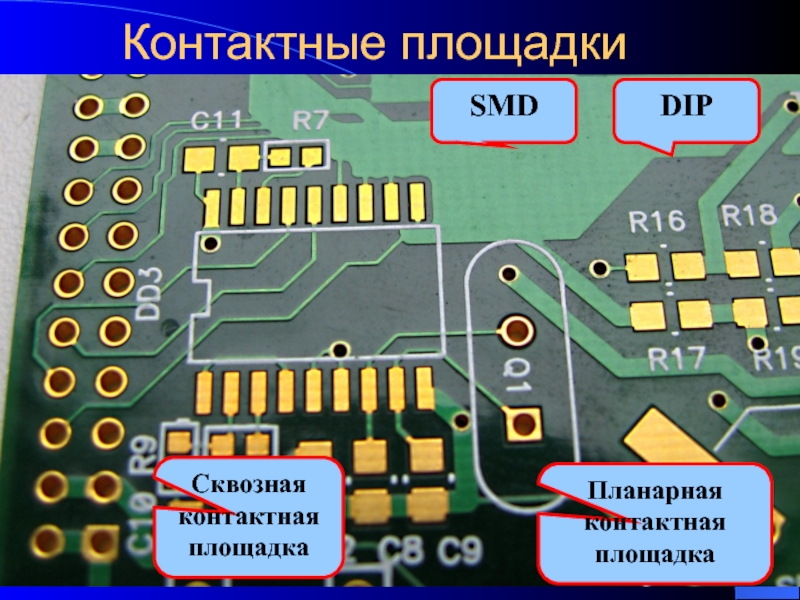

- 6. Контактные площадкиSMDDIPПланарная контактная площадкаСквозная контактная площадка

- 7. Типы посадочных местПЛАНАРНЫЕ – без переходов на

- 8. Вскрытие маскиТ = 0,05 – 0,1

- 9. Чип резисторы0402 ? 0,04” x 0,02” 1” = 25, 4 mm

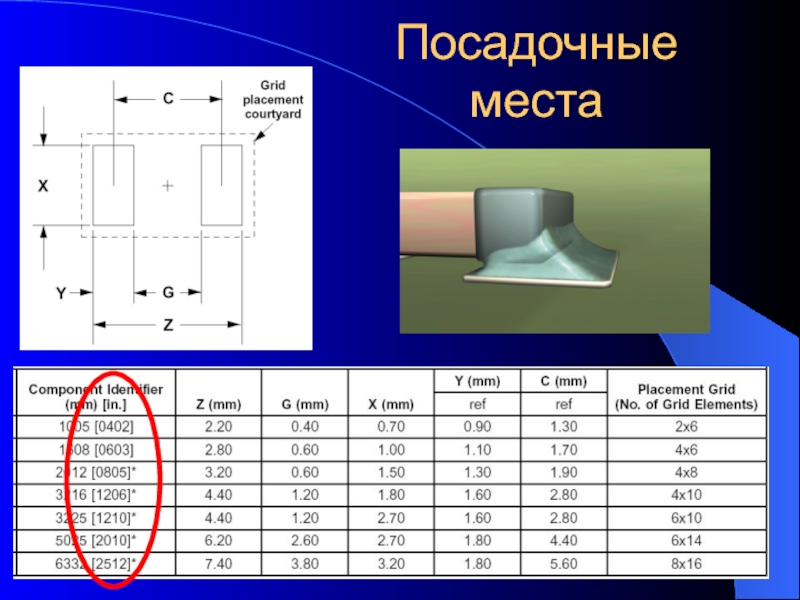

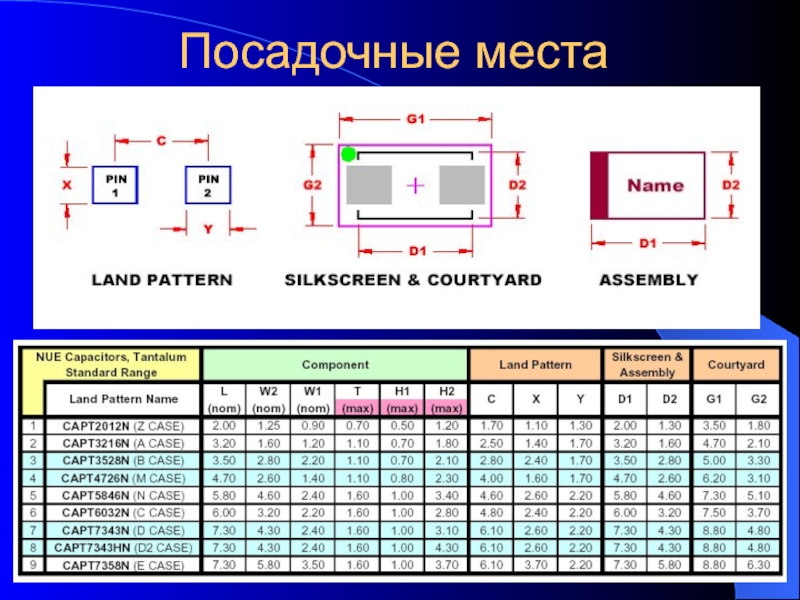

- 10. Посадочные места

- 11. Чип-Конденсаторы

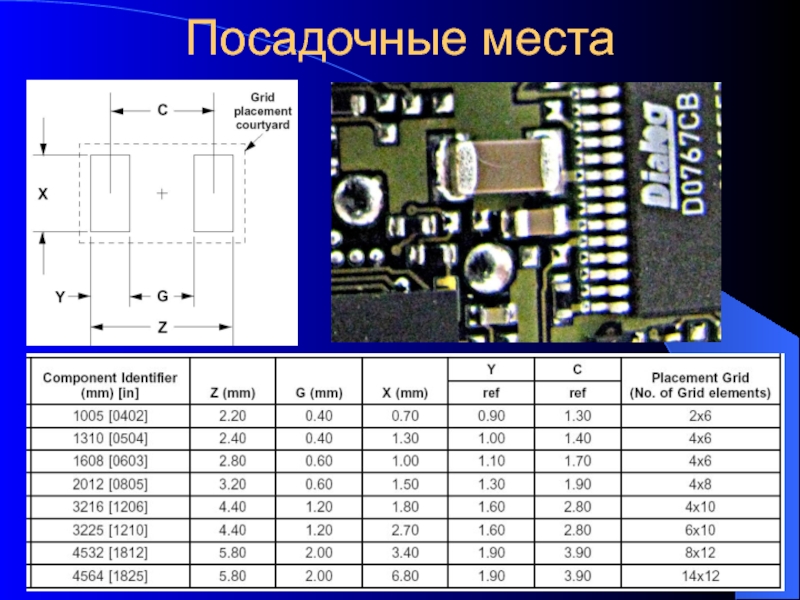

- 12. Посадочные места

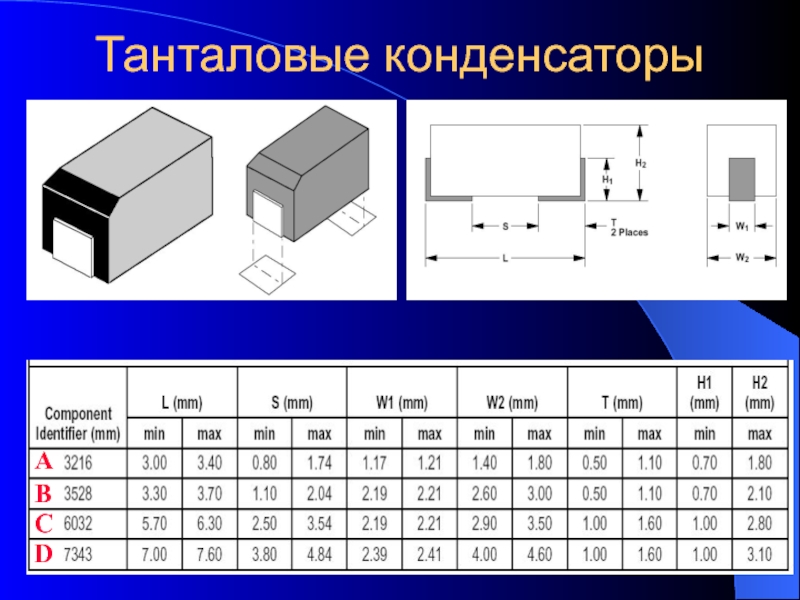

- 13. Танталовые конденсаторыABCD

- 14. Посадочные места

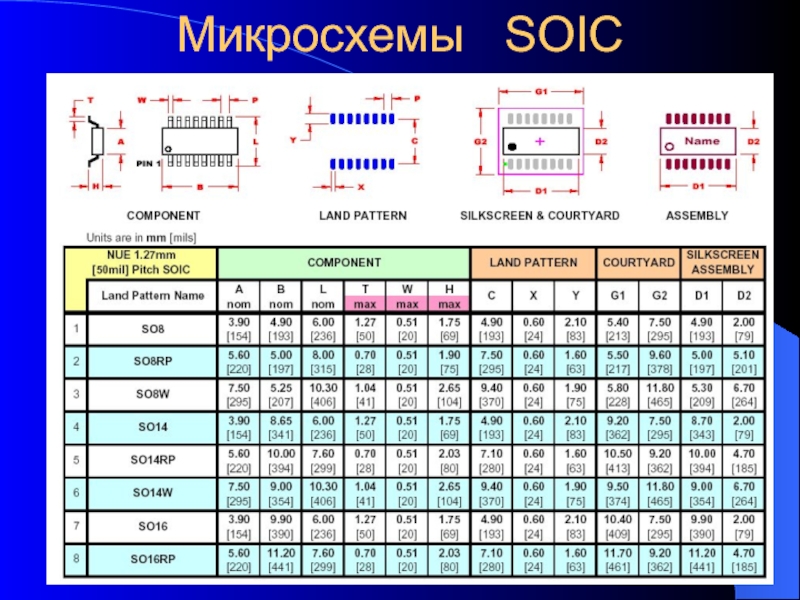

- 15. Корпуса микросхемSOICTSOPSSOICШаг =1,27 ммШаг =0,635 ммШаг =0,3

- 16. Названия корпусовSOIC – Small Outline Integral CircuitSSOP

- 17. Микросхемы SOIC

- 18. SOT-23, SOT-23-6

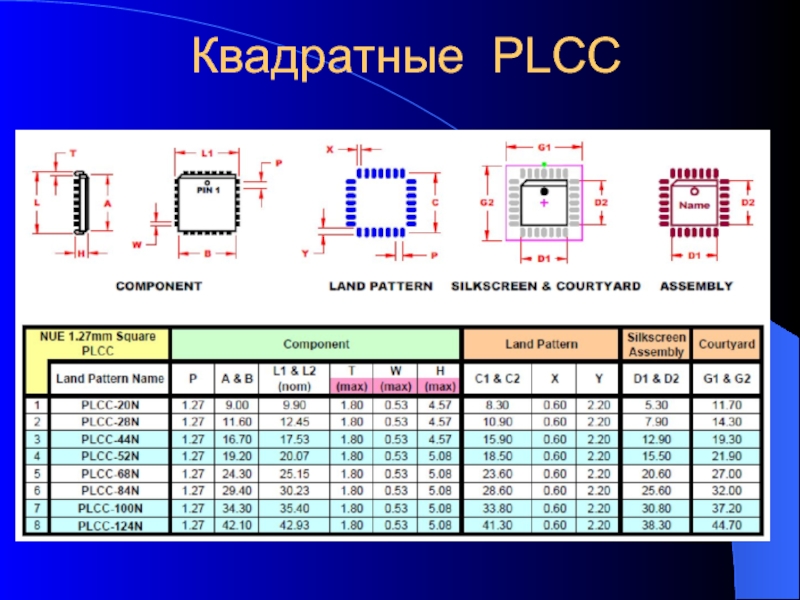

- 19. Квадратные PLCC

- 20. Корпуса DIP

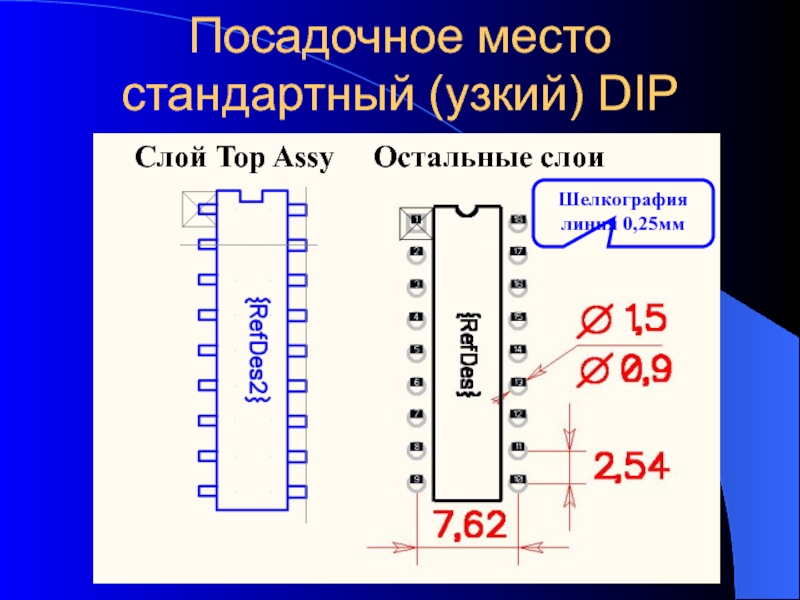

- 21. Посадочное место стандартный (узкий) DIPСлой Top Assy Остальные слоиШелкография линия 0,25мм

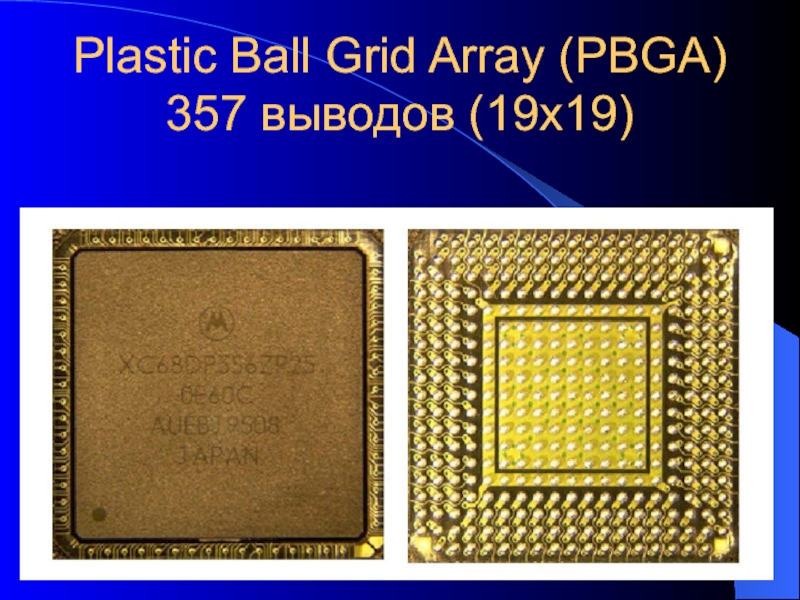

- 22. Plastic Ball Grid Array (PBGA) 357 выводов (19х19)

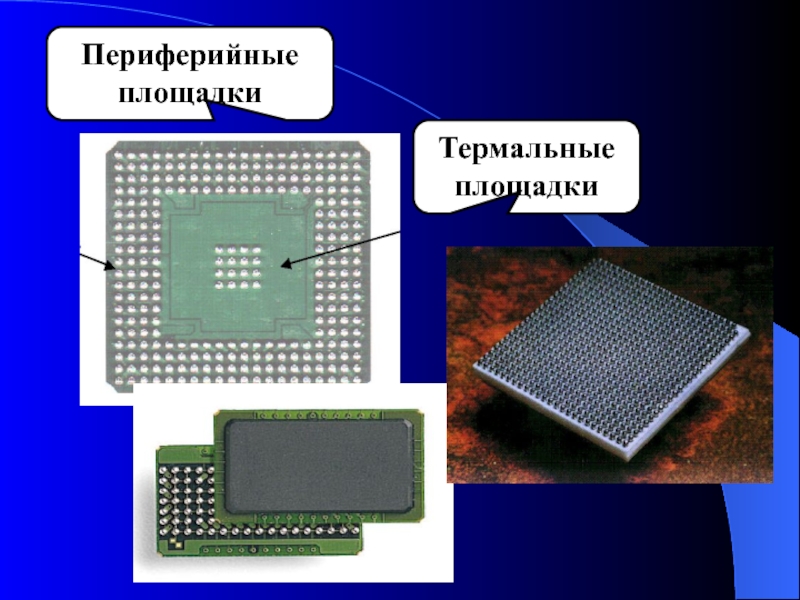

- 23. Термальные площадкиПериферийные площадки

- 24. Преимущества BGA корпусов

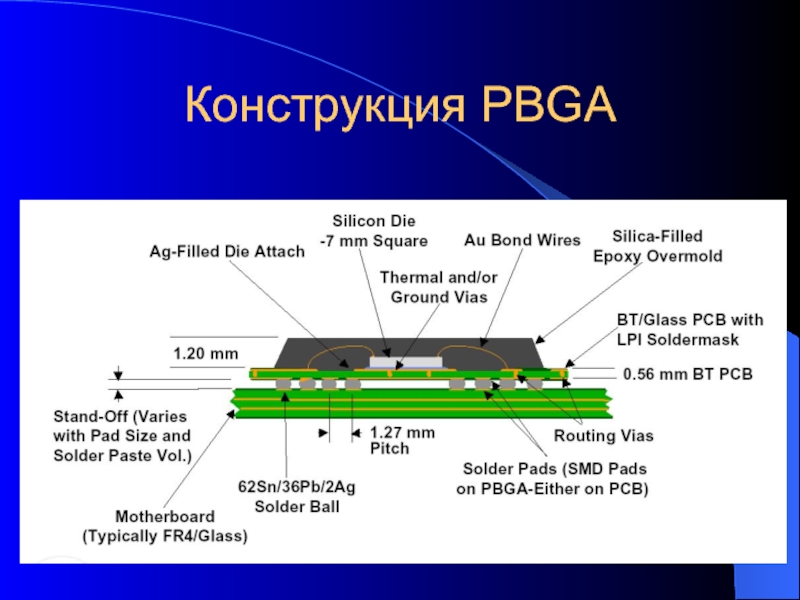

- 25. Конструкция PBGA

- 26. Два варианта площадок BGA

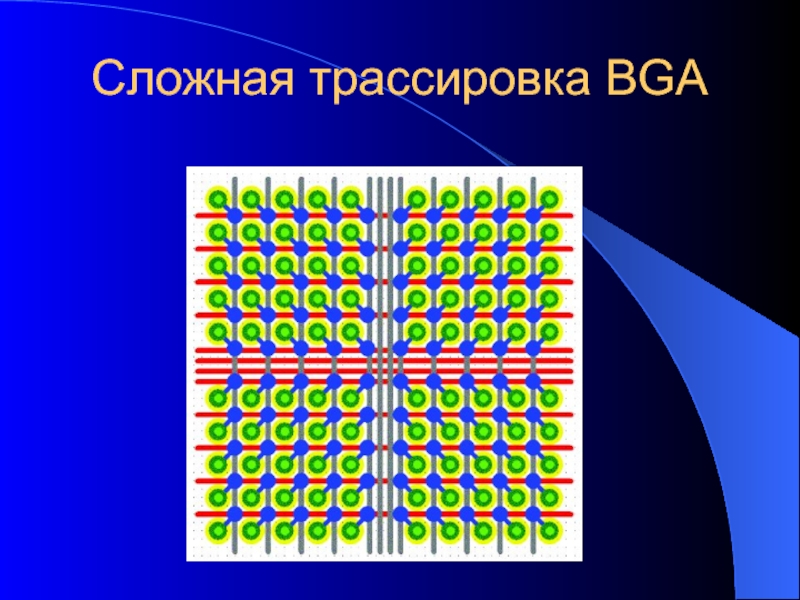

- 27. Сложная трассировка BGA

- 28. Конструктивные особенностиСложная форма вывода или площадки

- 29. Дополнительные выводы и точки крепления Конструктивные особенности9.

- 30. Пропущенные выводыКонструктивные особенности 1

- 31. CPLD, FPGAFPGA - field-programmable gate array (ПЛМ

- 32. Архитектура ПЛИС Virtex

- 33. BGA Корпус 1148 выводовБАНК 1БАНК 2БАНК 3БАНК 4БАНК 5БАНК 6БАНК 7БАНК 0

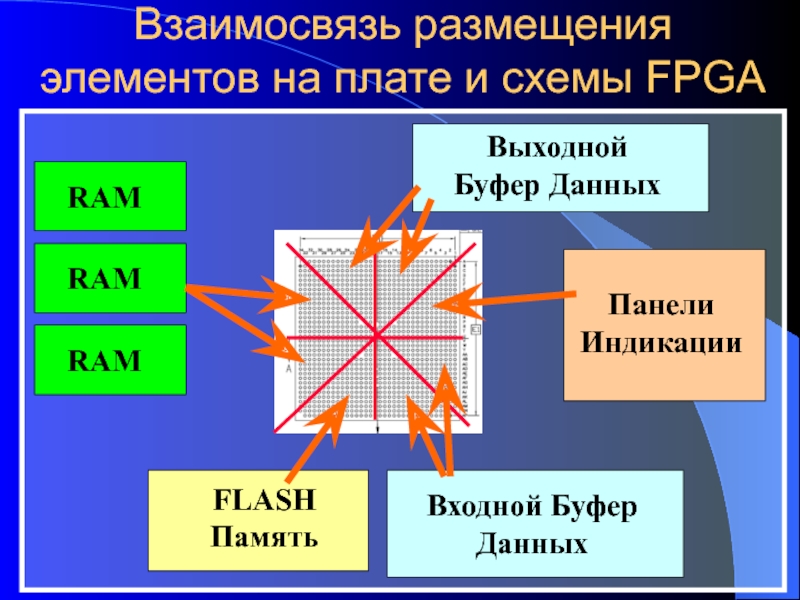

- 34. Взаимосвязь размещения элементов на плате и схемы FPGA RAMRAMRAMFLASH ПамятьВходной Буфер ДанныхВыходной Буфер ДанныхПанели Индикации

- 35. Скачать презентанцию

Организации занимающиеся стандартизацией в САПРСТАНДАРТИ-ЗАЦИЯ ПОСАДОЧНЫХ МЕСТ

Слайды и текст этой презентации

Слайд 3Стандарт IPC 7351

Определяет размеры контактных площадок для стандартных типов

корпусов чип-резисторов, чип-кондекнсаторов, диодов, транзисторов, индуктивностей и микросхем.

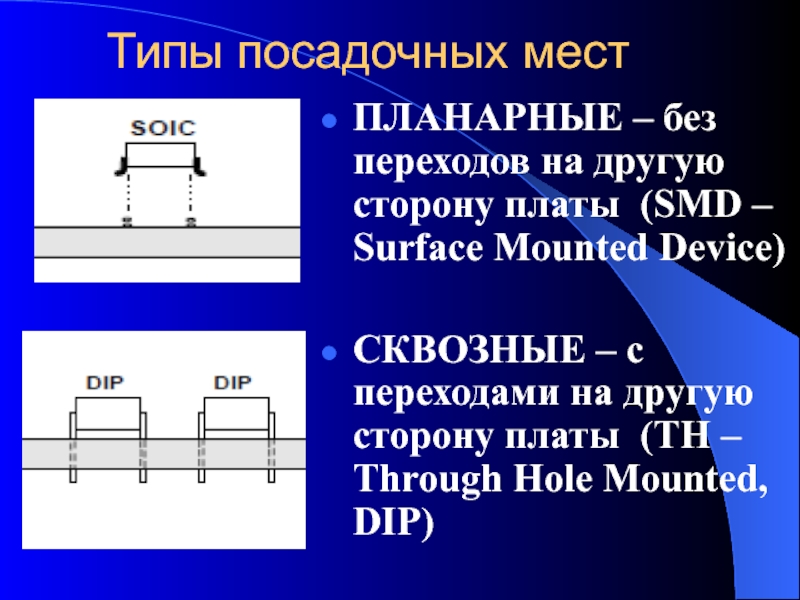

Слайд 7Типы посадочных мест

ПЛАНАРНЫЕ – без переходов на другую сторону платы

(SMD – Surface Mounted Device)

СКВОЗНЫЕ – с переходами на другую

сторону платы (TH – Through Hole Mounted, DIP)

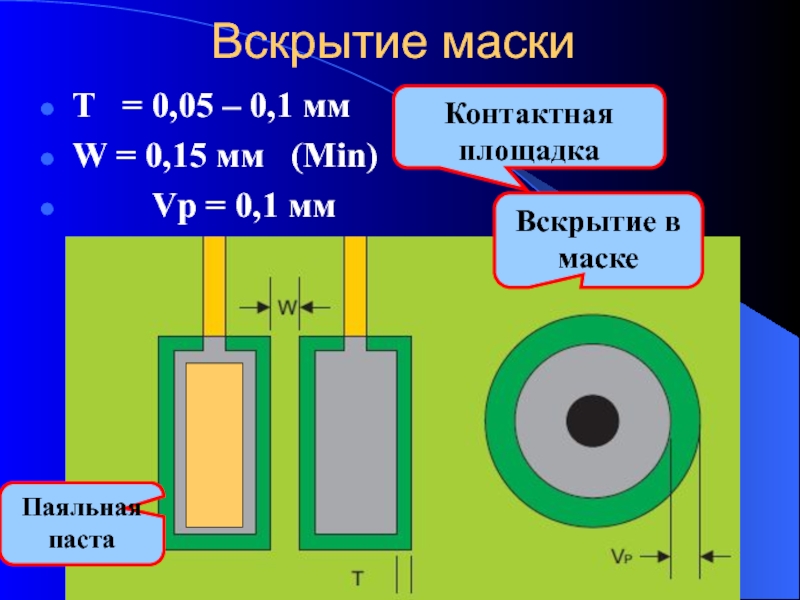

Слайд 8Вскрытие маски

Т = 0,05 – 0,1 мм

W = 0,15

мм (Min)

Vp =

0,1 ммПаяльная паста

Контактная площадка

Вскрытие в маске

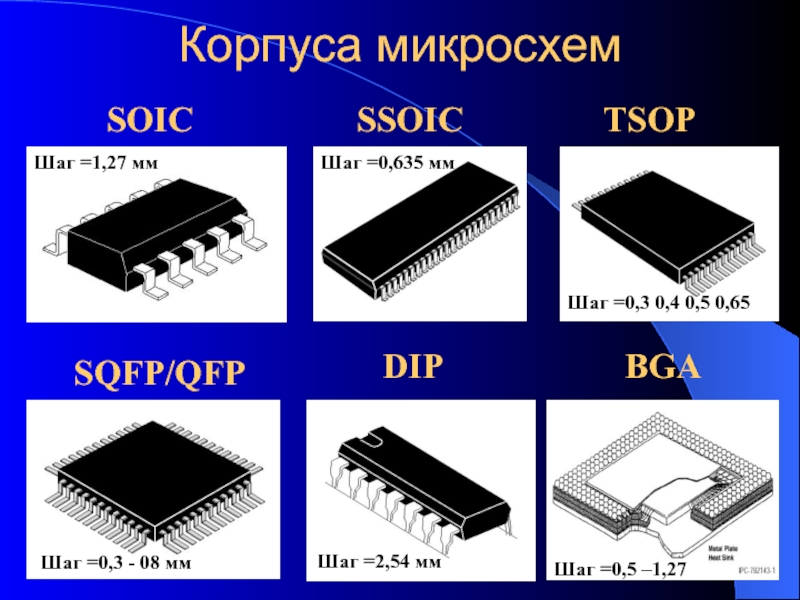

Слайд 15Корпуса микросхем

SOIC

TSOP

SSOIC

Шаг =1,27 мм

Шаг =0,635 мм

Шаг =0,3 0,4 0,5 0,65

Шаг

=0,3 - 08 мм

SQFP/QFP

DIP

Шаг =2,54 мм

BGA

Шаг =0,5 –1,27

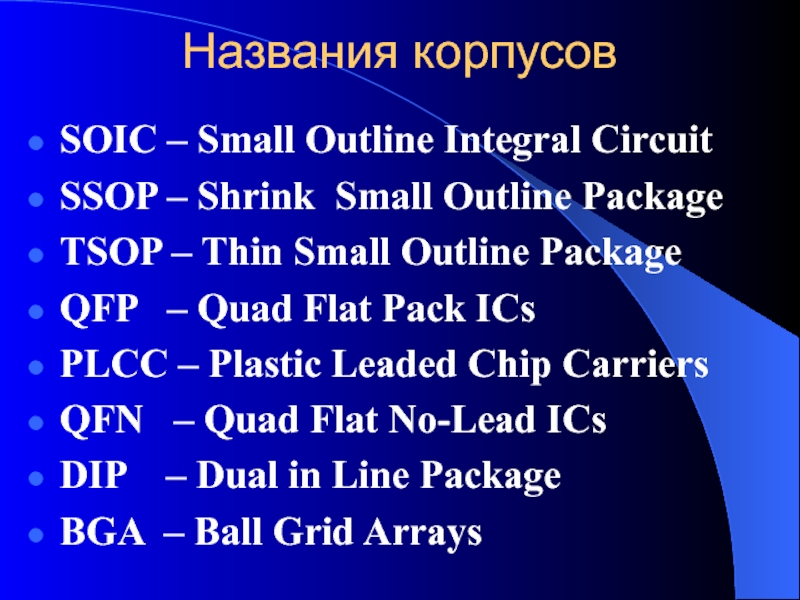

Слайд 16Названия корпусов

SOIC – Small Outline Integral Circuit

SSOP – Shrink Small

Outline Package

TSOP – Thin Small Outline Package

QFP

– Quad Flat Pack ICs PLCC – Plastic Leaded Chip Carriers

QFN – Quad Flat No-Lead ICs

DIP – Dual in Line Package

BGA – Ball Grid Arrays

Слайд 21Посадочное место стандартный (узкий) DIP

Слой Top Assy Остальные

слои

Шелкография линия 0,25мм

Слайд 28Конструктивные особенности

Сложная форма вывода или площадки

Слияние выводов

на топологии

1

2

3

4