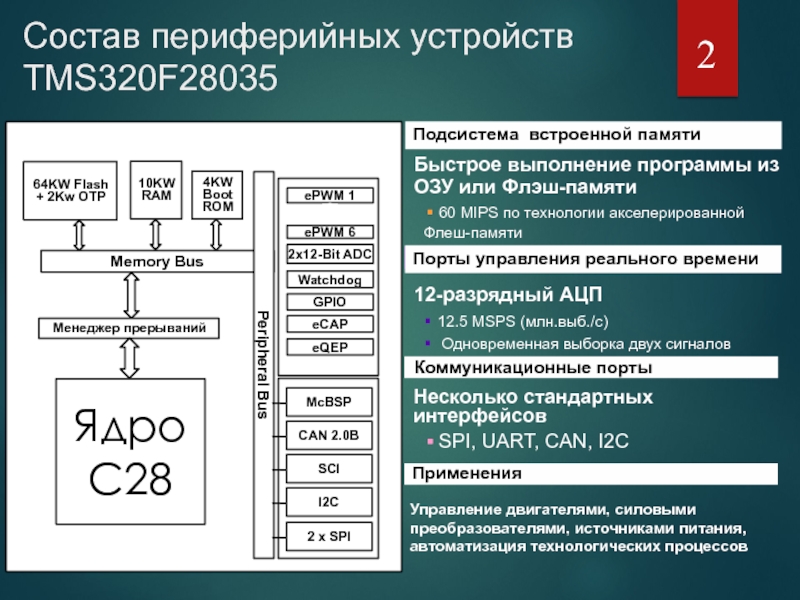

RAM

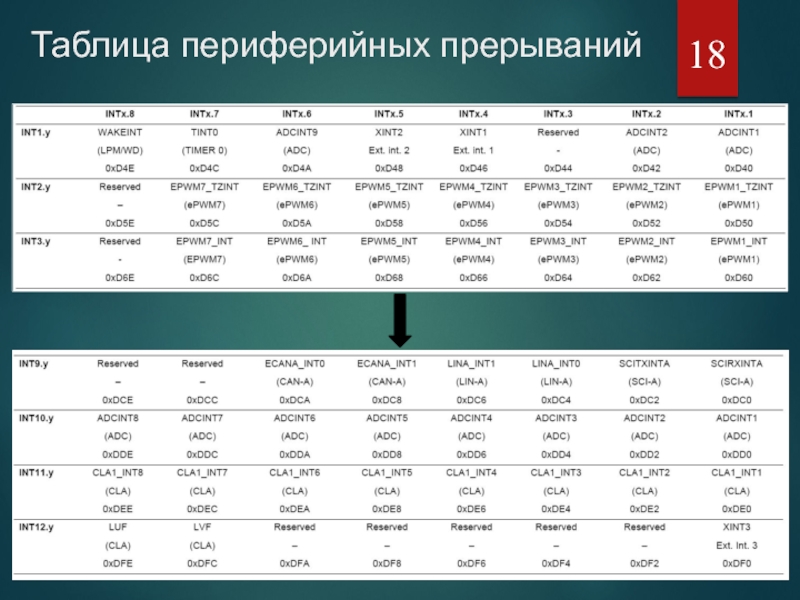

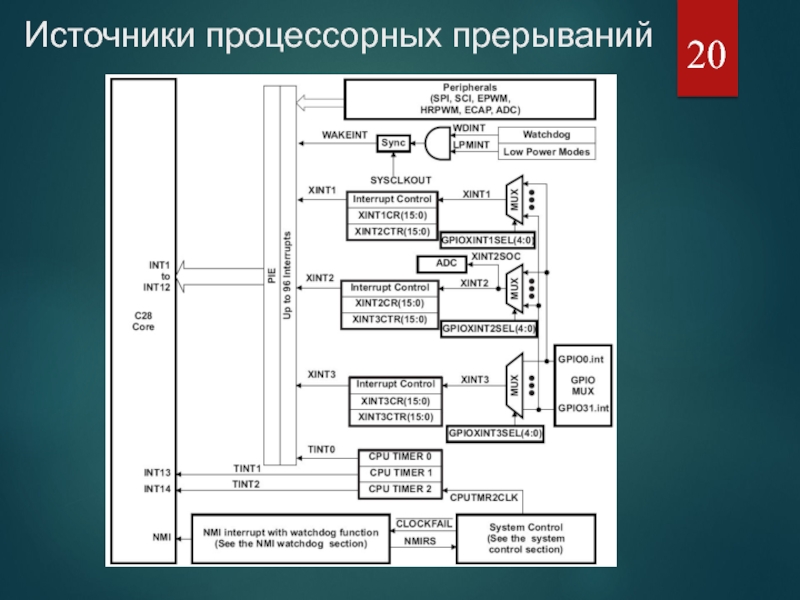

Менеджер прерываний

ePWM 1

ePWM 6

2x12-Bit ADC

Watchdog

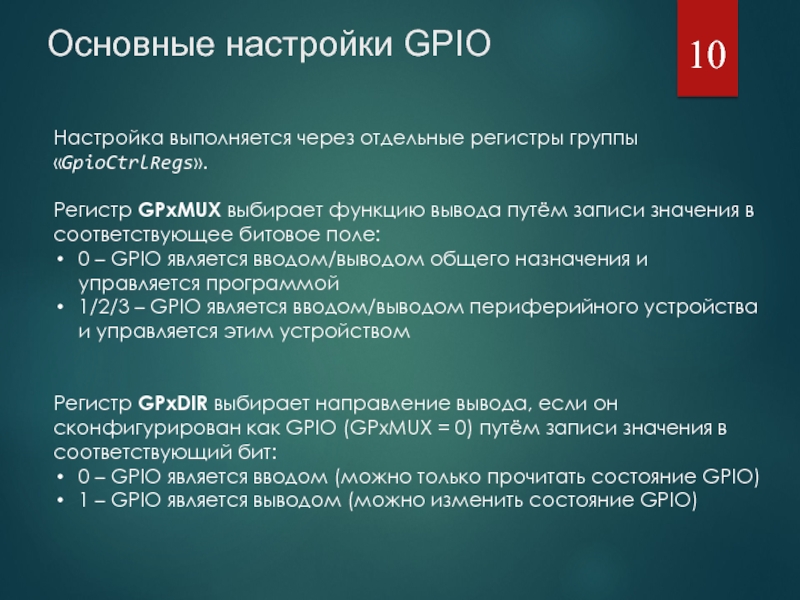

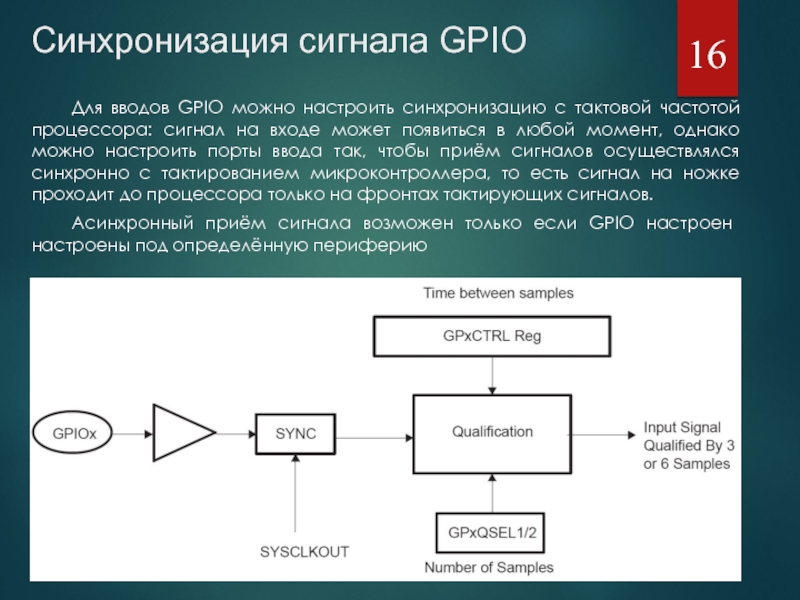

GPIO

Peripheral Bus

McBSP

CAN 2.0B

SCI

I2C

2 х SPI

Несколько стандартных

интерфейсовSPI, UART, CAN, I2C

Коммуникационные порты

Быстрое выполнение программы из ОЗУ или Флэш-памяти

60 MIPS по технологии акселерированной

Флеш-памяти

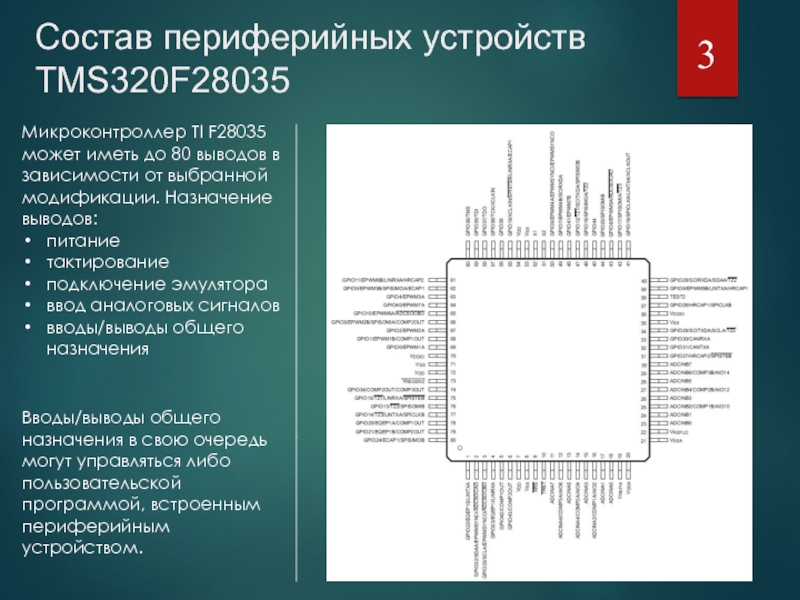

Состав периферийных устройств TMS320F28035

12-разрядный АЦП

12.5 MSPS (млн.выб./с)

Одновременная выборка двух сигналов

Control Peripherals

Порты управления реального времени

Применения

Управление двигателями, силовыми преобразователями, источниками питания, автоматизация технологических процессов

Ядро C28

eCAP

eQEP

Подсистема встроенной памяти