Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Триггеры синхронизация регистры счетчики

Содержание

- 1. Триггеры синхронизация регистры счетчики

- 2. Распространение сигналов. Быстродействие. Понятие о задержкеABF1= A.BЗадержкa

- 3. Распространение сигналов. Быстродействие. Понятие о задержкеКороткий по

- 4. Распространение сигналов. Быстродействие. Понятие о задержкеКороткий по

- 5. Распространение сигналов. Быстродействие. Понятие о задержкеПереход от

- 6. Распространение сигналов. Быстродействие.Понятие о задержке. Критические цепиЗадержка

- 7. Различные задержки в логическом устройствеРаспространение сигналов. Быстродействие.Понятие о задержке. Критические цепи.

- 8. Варианты реализации мультиплексора:где больше задержка?Распространение сигналов. Быстродействие.Понятие о задержке. Критические цепи.

- 9. Цепь переноса в сумматоре является критической: в

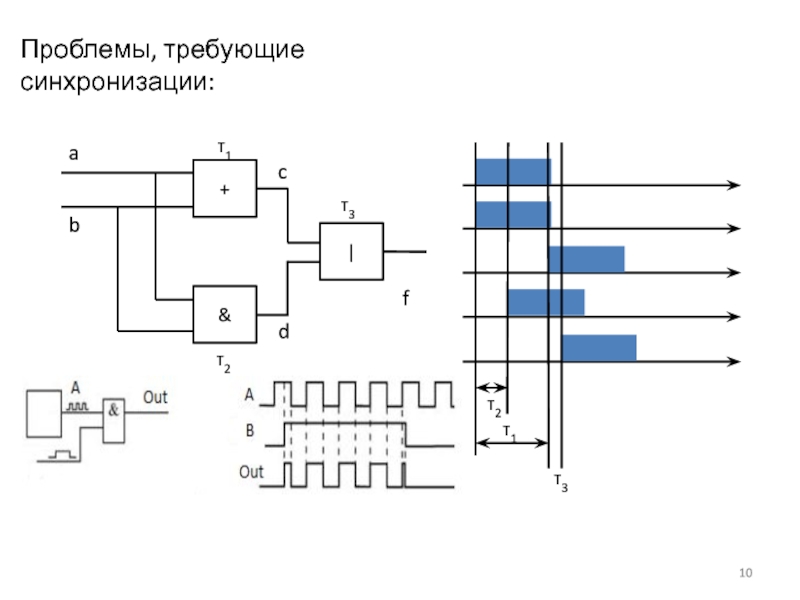

- 10. Проблемы, требующие синхронизации:f

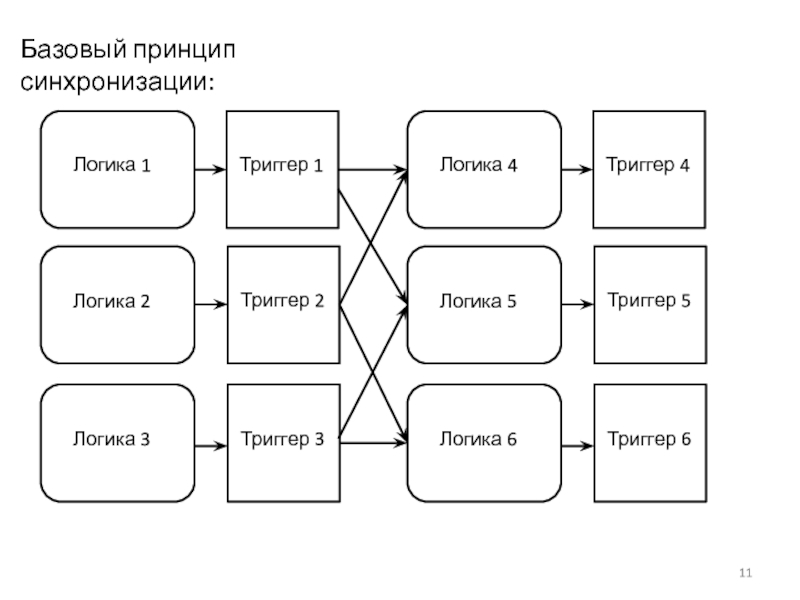

- 11. Базовый принцип синхронизации:

- 12. Динамическая дисциплина:Входы синхронной последовательной схемы должны быть

- 13. МетастабильностьСам фронт сигнала тактовой частоты немного растянут

- 14. МетастабильностьПопадание триггера в метастабильное состояние- вероятностный процесс,

- 15. Простой синхронизатор и временная диаграмма его

- 16. Вероятность сбоя синхронизатораЕсли D изменяется N раз

- 17. Дискретные устройства- триггерыДискретное (последовательное) цифровое устройство:Выходное состояние

- 18. Дискретные устройства- триггерыДискретное (последовательное) цифровое устройство:Выходное состояние

- 19. Случай 1: Q=0На вход поступает сигнал Q

- 20. R-S триггер Случай I: R=1, S=0На входе

- 21. R-S триггер Случай III: R=1, S=1Запрещенная комбинация

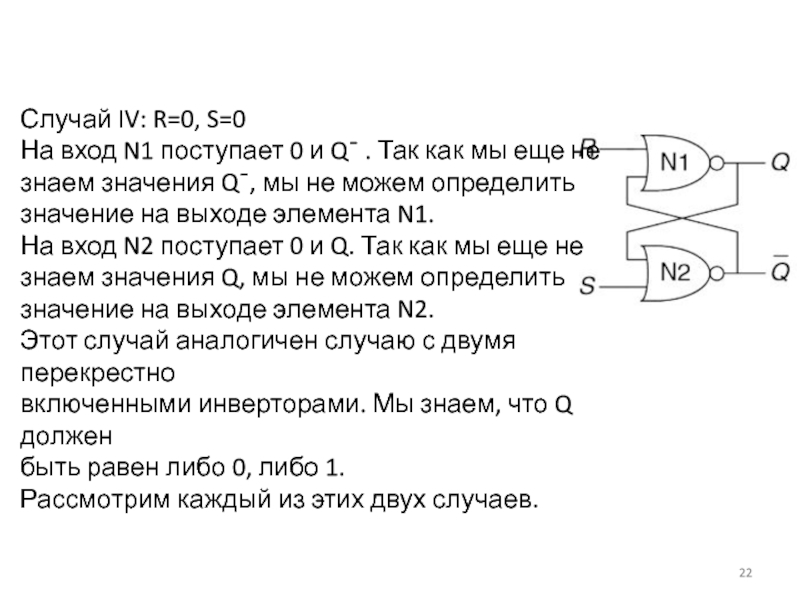

- 22. Случай IV: R=0, S=0На вход N1 поступает

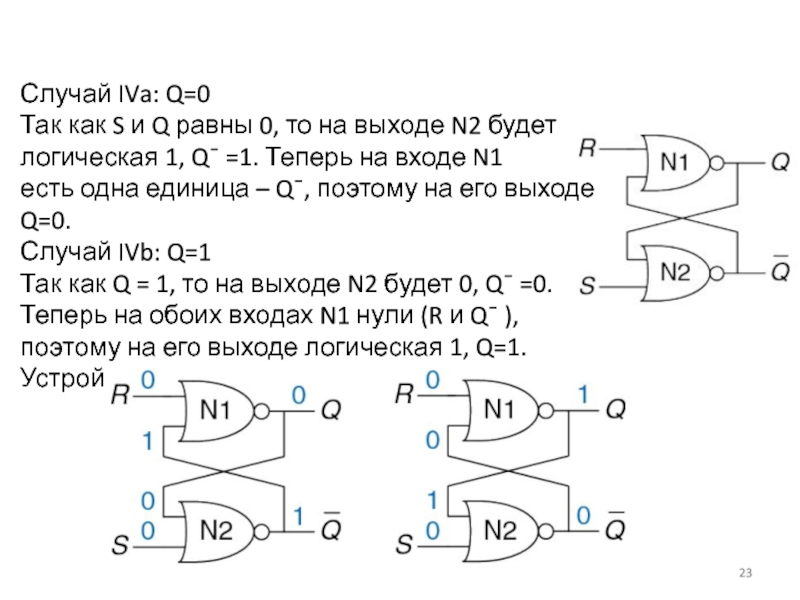

- 23. Случай IVa: Q=0Так как S и Q

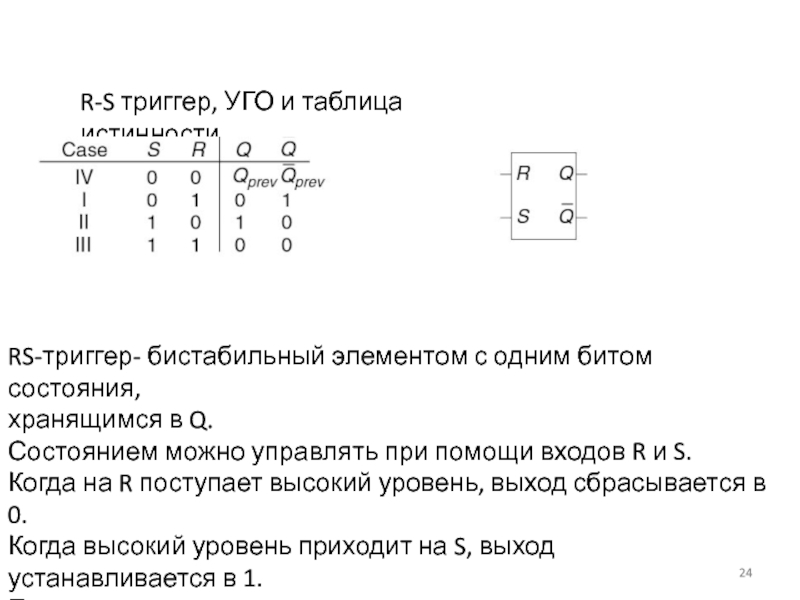

- 24. R-S триггер, УГО и таблица истинностиRS-триггер- бистабильный

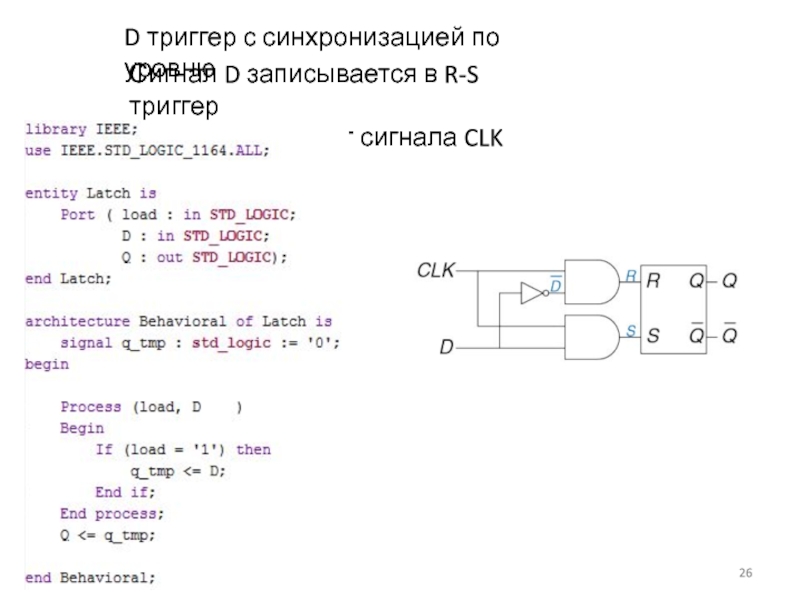

- 25. D триггер с синхронизацией по уровнюСигнал D записывается в R-S триггерпо разрешению от сигнала CLK

- 26. D триггер с синхронизацией по уровнюСигнал D записывается в R-S триггерпо разрешению от сигнала CLK

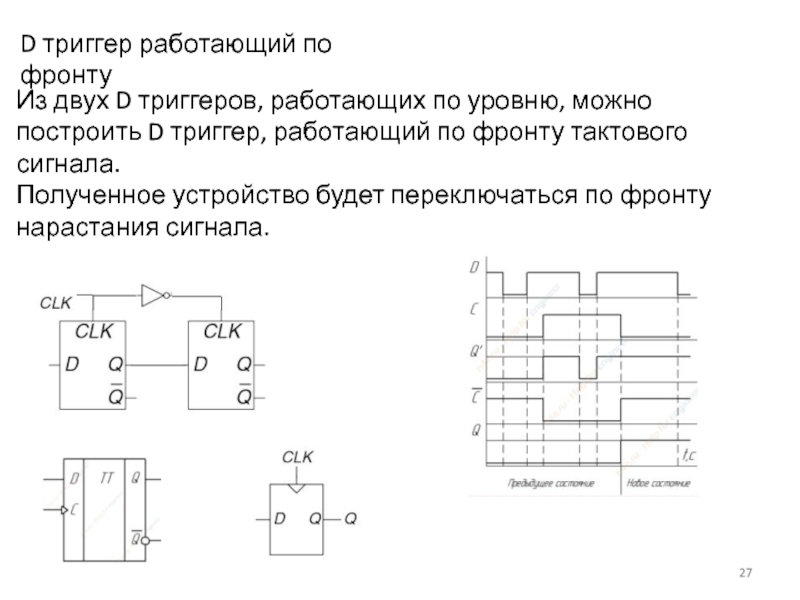

- 27. D триггер работающий по фронтуИз двух D

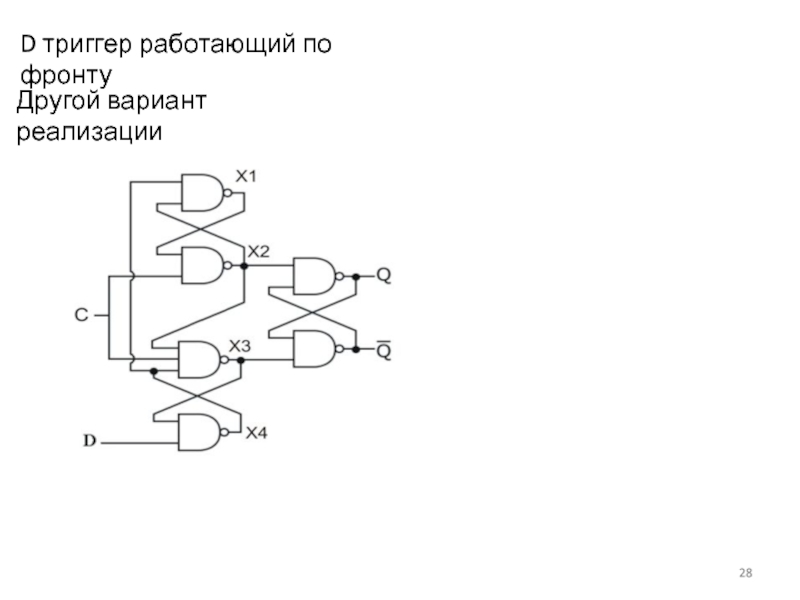

- 28. D триггер работающий по фронтуДругой вариант реализации

- 29. D триггер работающий по фронту, VHDL

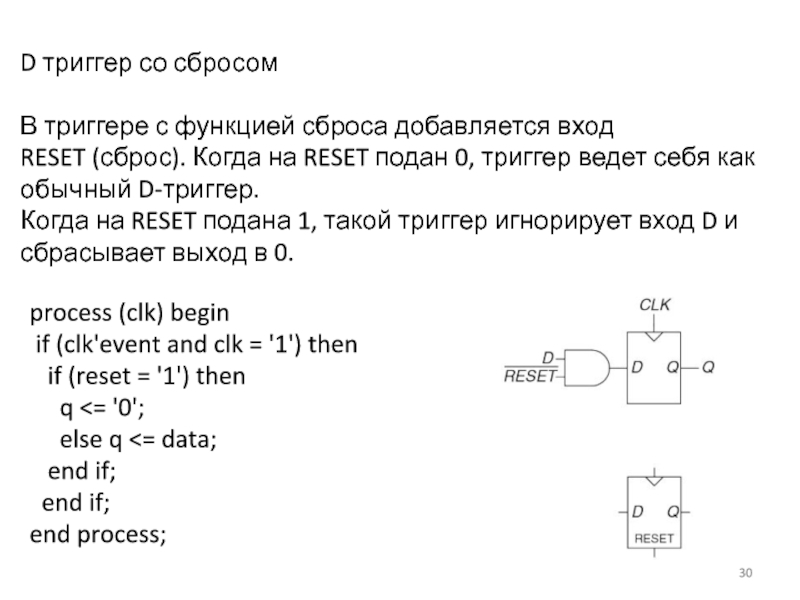

- 30. D триггер со сбросомВ триггере с функцией

- 31. D триггер со сбросом и установкойВ триггере

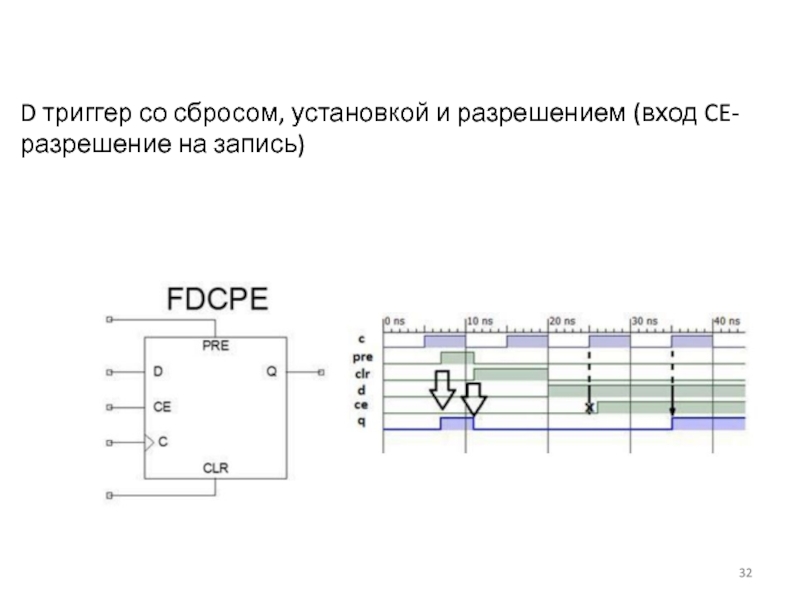

- 32. D триггер со сбросом, установкой и разрешением (вход CE-разрешение на запись)

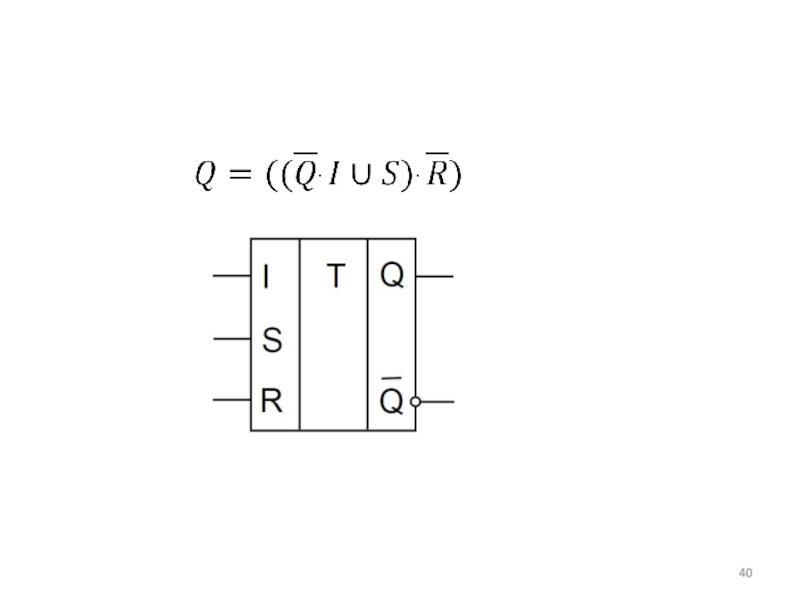

- 33. Счетный триггерD- триггер, у которого инверсный выход

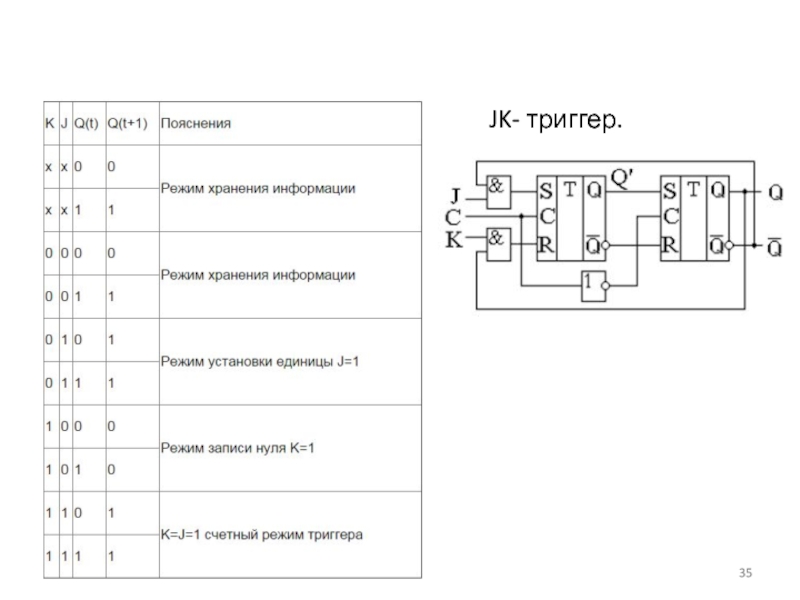

- 34. JK- триггер. Таблица истинности JK-триггера практически совпадает

- 35. JK- триггер.

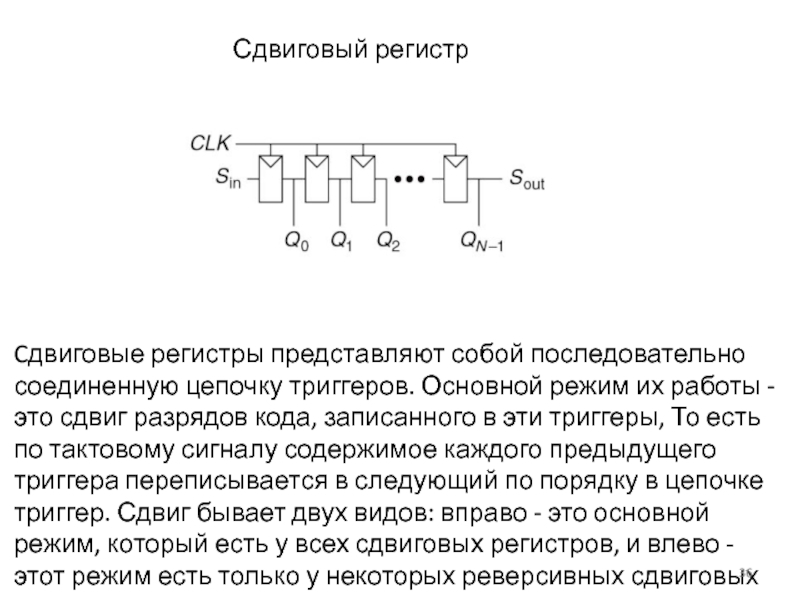

- 36. Сдвиговый регистрCдвиговые регистры представляют собой последовательно соединенную

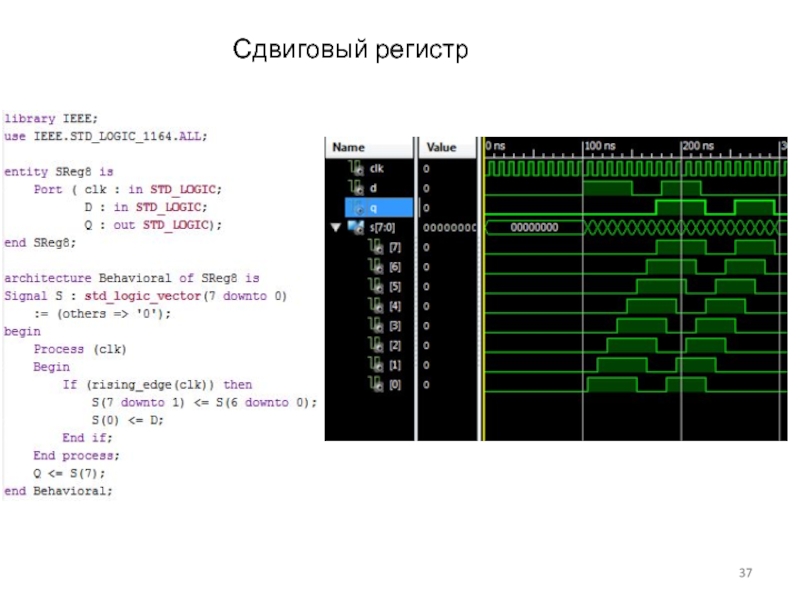

- 37. Сдвиговый регистр

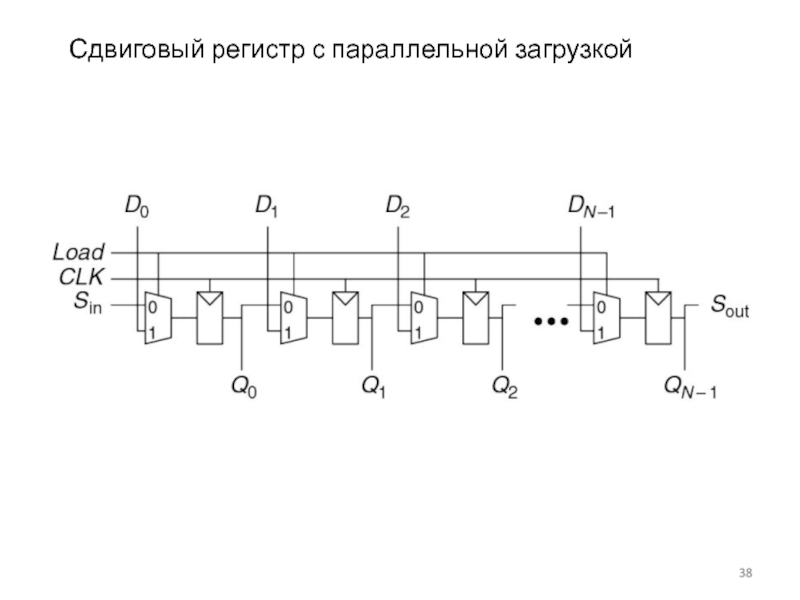

- 38. Сдвиговый регистр с параллельной загрузкой

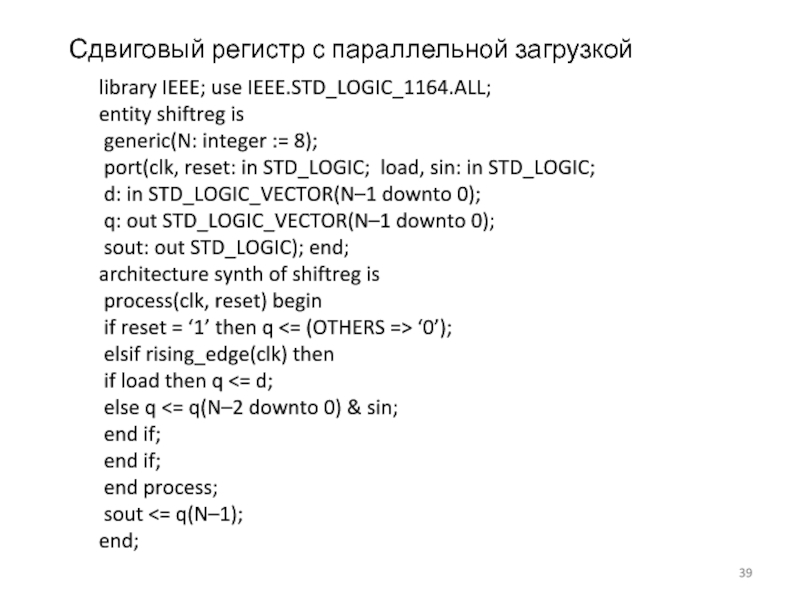

- 39. Сдвиговый регистр с параллельной загрузкойlibrary IEEE; use

- 40.

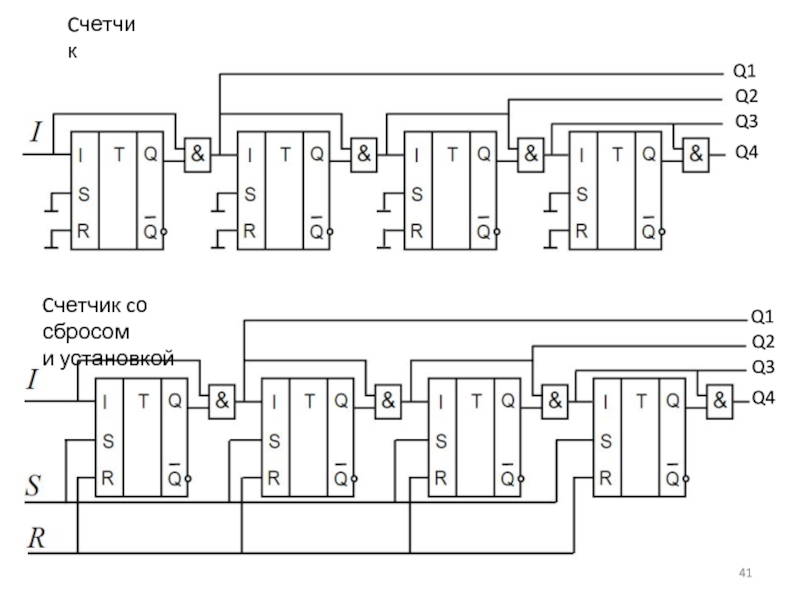

- 41. CчетчикQ1Q2Q3Q4Q2Q3Q4Q1Cчетчик cо сбросоми установкой

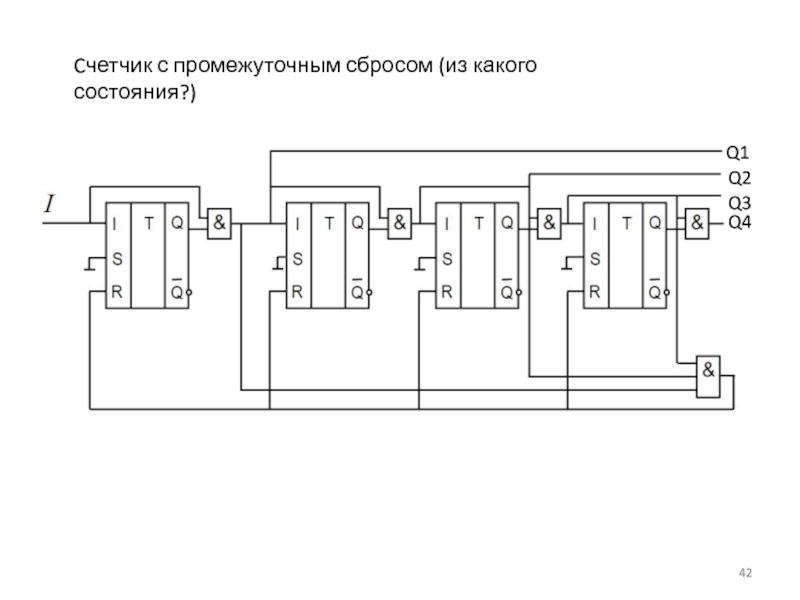

- 42. Cчетчик с промежуточным сбросом (из какого состояния?)Q1Q2Q3Q4

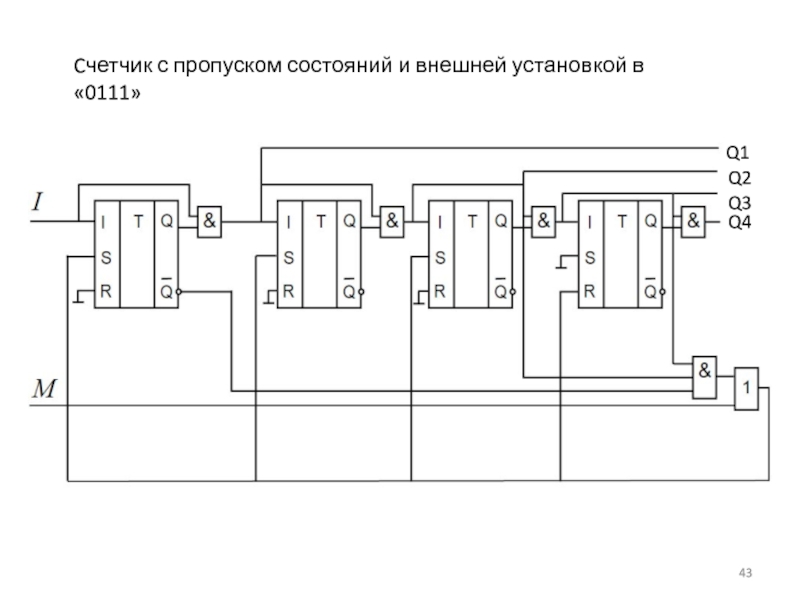

- 43. Cчетчик с пропуском состояний и внешней установкой в «0111»Q1Q2Q3Q4

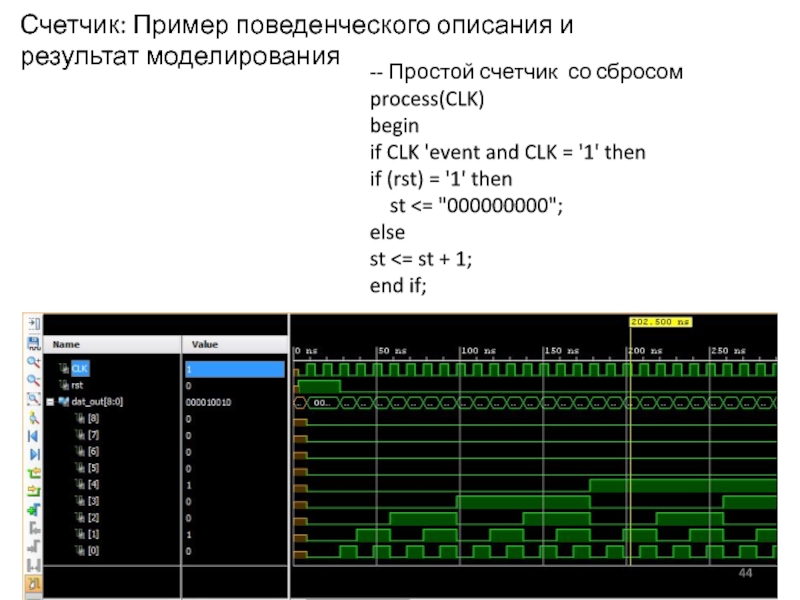

- 44. Счетчик: Пример поведенческого описания и результат моделирования--

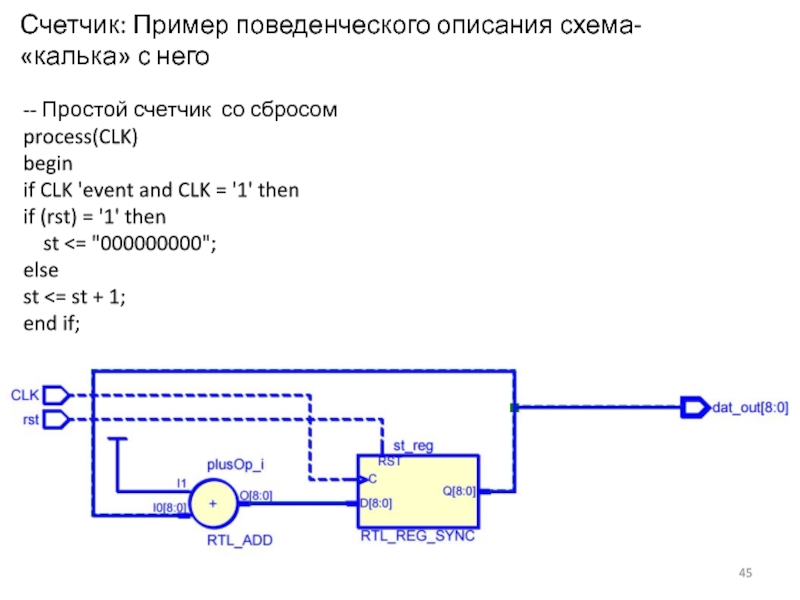

- 45. Счетчик: Пример поведенческого описания схема-«калька» с него--

- 46. Счетчик: поведенческое описание, переведенное САПР на элементы ПЛИС (фрагмент)

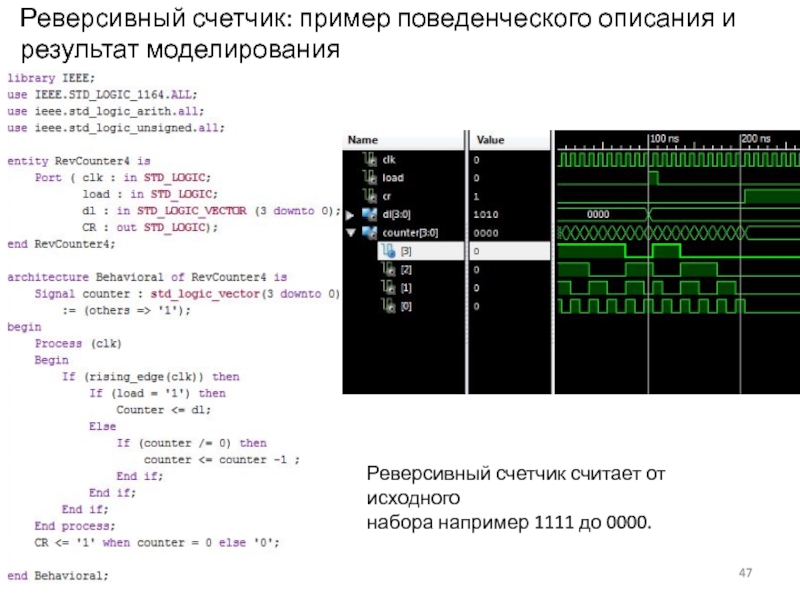

- 47. Реверсивный счетчик: пример поведенческого описания и результат

- 48. Благодарю за внимание!

- 49. Скачать презентанцию

Слайды и текст этой презентации

Слайд 2

Распространение сигналов. Быстродействие. Понятие о задержке

A

B

F1= A.B

Задержкa 1->0

C

F2= F1.C

D

F3= F2.C

Задержкa

0->1

F3 получаются из нихСлайд 3

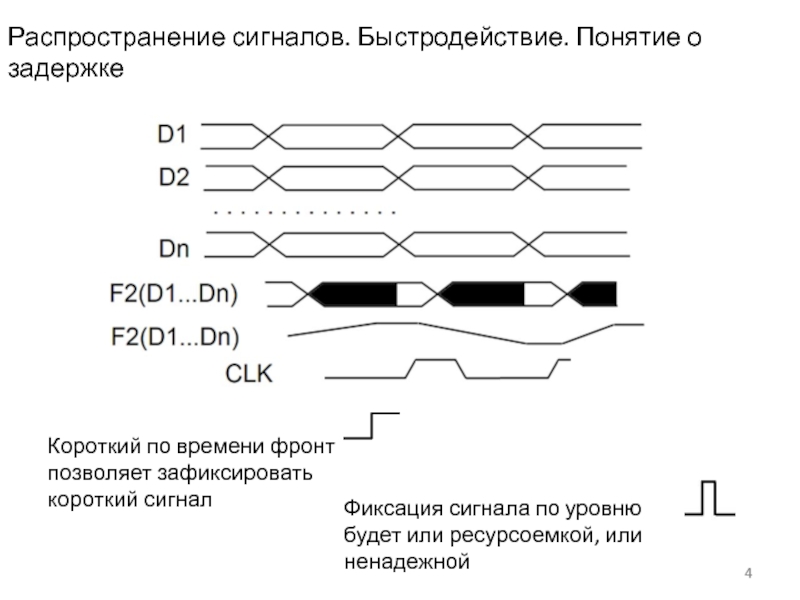

Распространение сигналов. Быстродействие. Понятие о задержке

Короткий по времени фронт

позволяет

зафиксировать короткий сигнал

Фиксация сигнала по уровню

будет или ресурсоемкой, или

ненадежнойСлайд 4

Распространение сигналов. Быстродействие. Понятие о задержке

Короткий по времени фронт

позволяет

зафиксировать короткий сигнал

Фиксация сигнала по уровню

будет или ресурсоемкой, или

ненадежнойСлайд 5

Распространение сигналов. Быстродействие. Понятие о задержке

Переход от НИЗКОГО уровня к

ВЫСОКОМУ называется положительным перепадом или фронтом. Аналогично, переход от ВЫСОКОГО

уровня к НИЗКОМУ называется соответственно отрицательным перепадом или срезом.Слайд 6

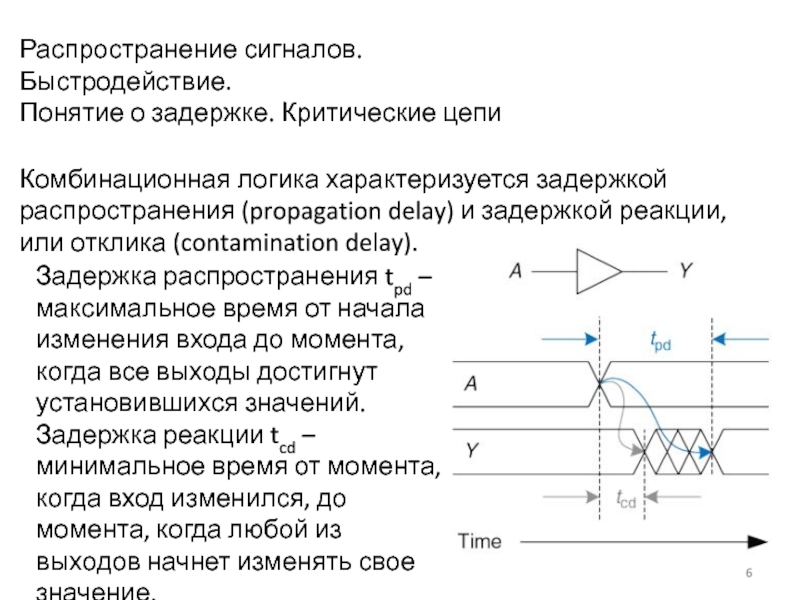

Распространение сигналов. Быстродействие.

Понятие о задержке. Критические цепи

Задержка распространения tpd –максимальное

время от начала изменения входа до момента, когда все выходы

достигнут установившихся значений. Задержка реакции tcd –минимальное время от момента, когда вход изменился, до момента, когда любой из выходов начнет изменять свое значение.Комбинационная логика характеризуется задержкой распространения (propagation delay) и задержкой реакции, или отклика (contamination delay).

Слайд 7

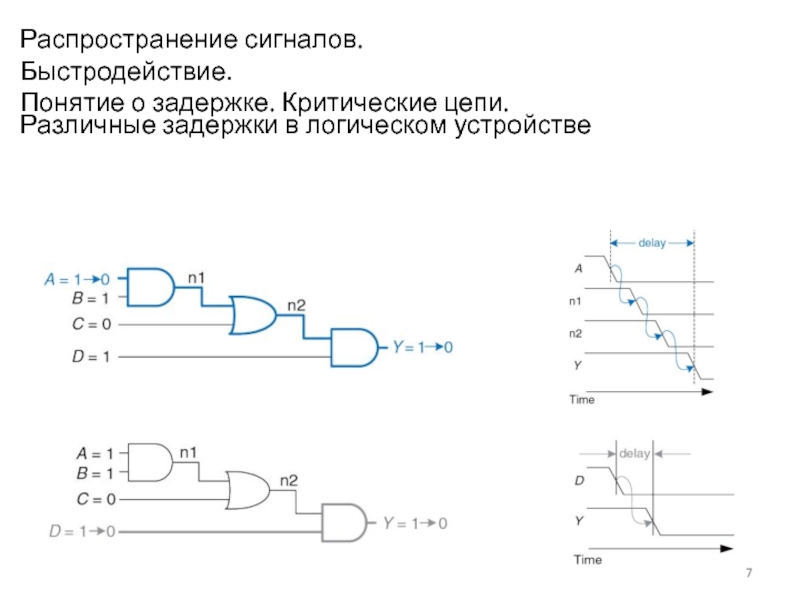

Различные задержки в логическом устройстве

Распространение сигналов. Быстродействие.

Понятие о задержке. Критические

цепи.

Слайд 8

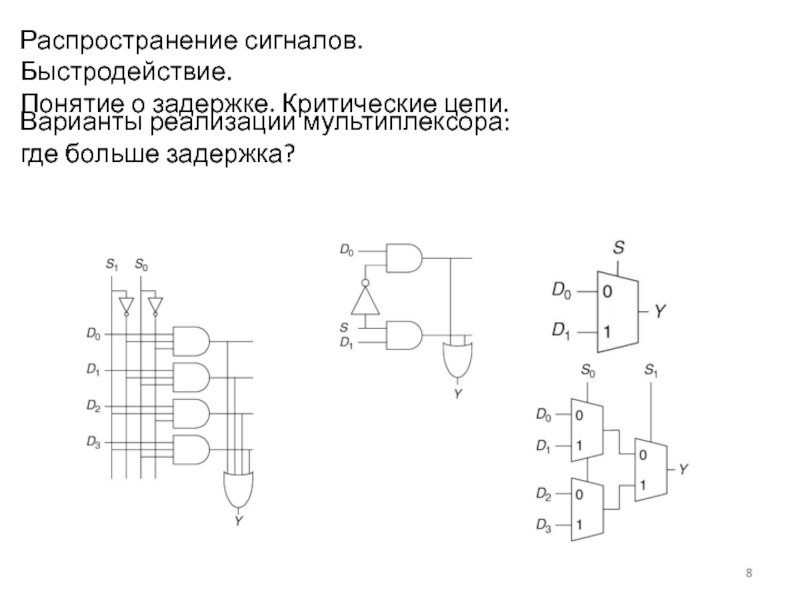

Варианты реализации мультиплексора:

где больше задержка?

Распространение сигналов. Быстродействие.

Понятие о задержке. Критические

цепи.

Слайд 9

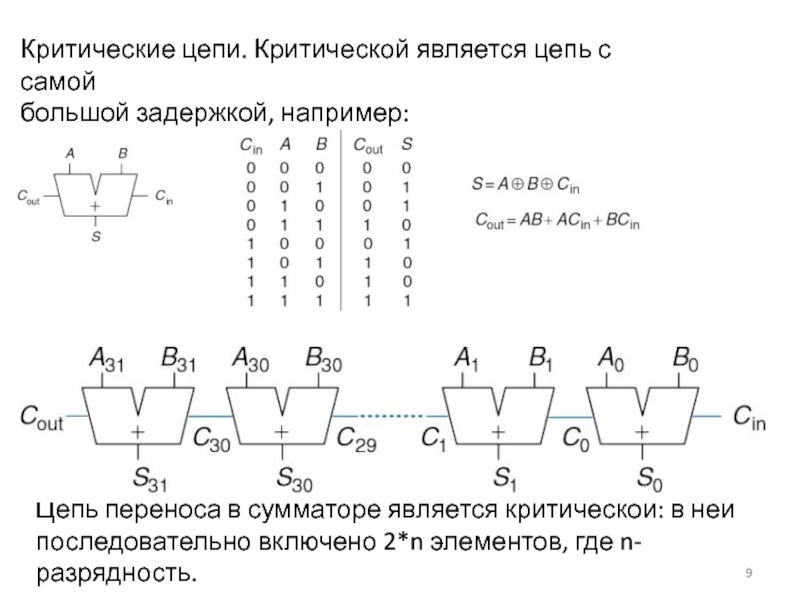

Цепь переноса в сумматоре является критической: в ней последовательно включено

2*n элементов, где n- разрядность.

Критические цепи. Критической является цепь

с самой

большой задержкой, например:Слайд 12

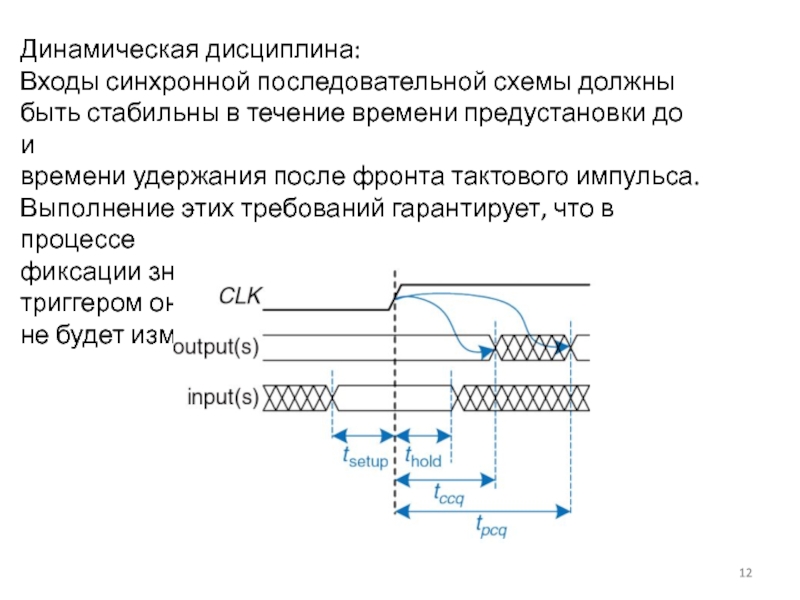

Динамическая дисциплина:

Входы синхронной последовательной схемы должны

быть стабильны в течение времени

предустановки до и

времени удержания после фронта тактового импульса.

Выполнение

этих требований гарантирует, что в процессе

фиксации значения информационного входа триггером он не будет изменяться.

Слайд 13

Метастабильность

Сам фронт сигнала тактовой частоты немного растянут во

времени, да

и триггер переключается не мгновенно, на его переключение требуется время.

Чтобы успешно зафиксировать входное значение в D-триггере,

входной сигнал должен быть стабилен некоторое время до фронта

и после фронта тактовой частоты.

Если этого не произошло, триггер может оказаться в «промежуточном» состоянии, называемом метастабильным.

Метастабильное состояние триггера не является устойчивым. После выхода из метастабильного состояния триггер оказывается в произвольном состоянии.

Слайд 14

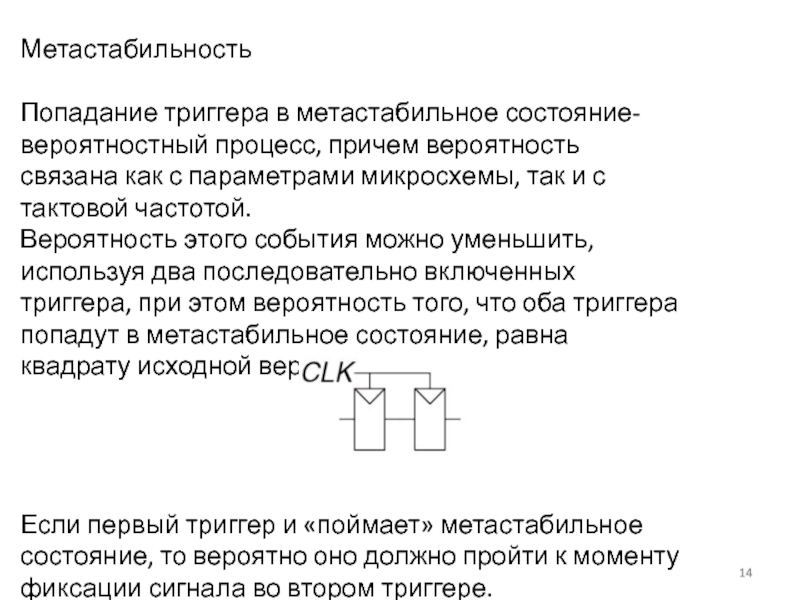

Метастабильность

Попадание триггера в метастабильное состояние- вероятностный процесс, причем вероятность связана

как с параметрами микросхемы, так и с тактовой частотой.

Вероятность этого

события можно уменьшить, используя два последовательно включенных триггера, при этом вероятность того, что оба триггера попадут в метастабильное состояние, равна квадрату исходной вероятности.Если первый триггер и «поймает» метастабильное состояние, то вероятно оно должно пройти к моменту фиксации сигнала во втором триггере.

Слайд 15

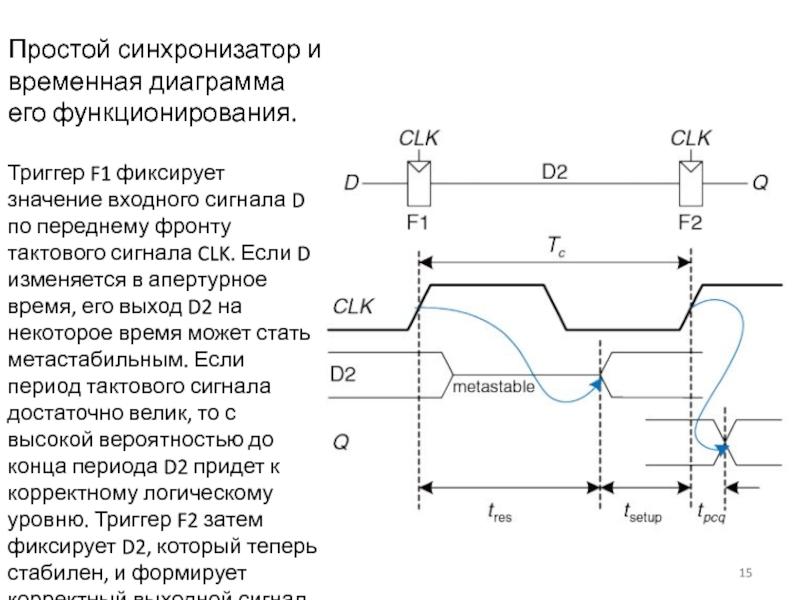

Простой синхронизатор и временная диаграмма

его функционирования.

Триггер F1 фиксирует значение

входного сигнала D по переднему фронту тактового сигнала CLK. Если

D изменяется в апертурное время, его выход D2 на некоторое время может стать метастабильным. Если период тактового сигнала достаточно велик, то с высокой вероятностью до конца периода D2 придет к корректному логическому уровню. Триггер F2 затем фиксирует D2, который теперь стабилен, и формирует корректный выходной сигнал.Слайд 16

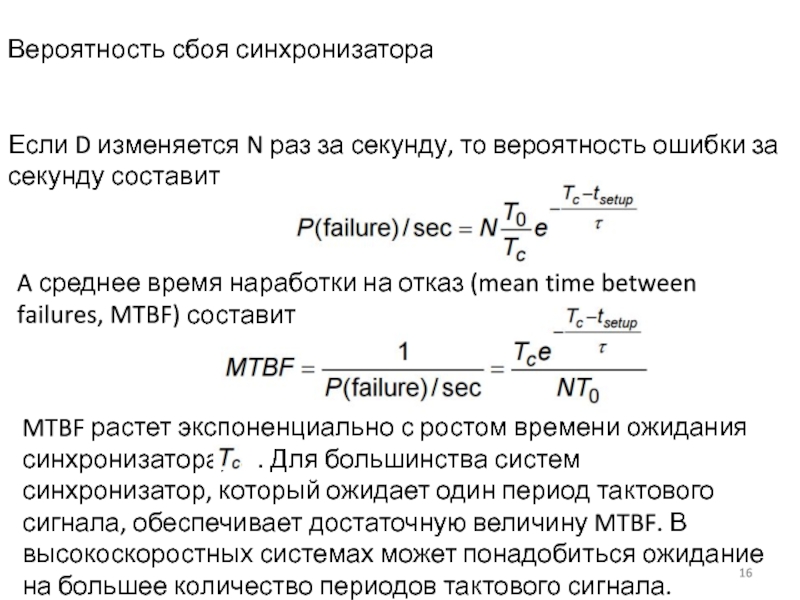

Вероятность сбоя синхронизатора

Если D изменяется N раз за секунду, то

вероятность ошибки за секунду составит

A среднее время наработки на отказ

(mean time between failures, MTBF) составитMTBF растет экспоненциально с ростом времени ожидания синхронизатора, . Для большинства систем синхронизатор, который ожидает один период тактового сигнала, обеспечивает достаточную величину MTBF. В высокоскоростных системах может понадобиться ожидание на большее количество периодов тактового сигнала.

Слайд 17

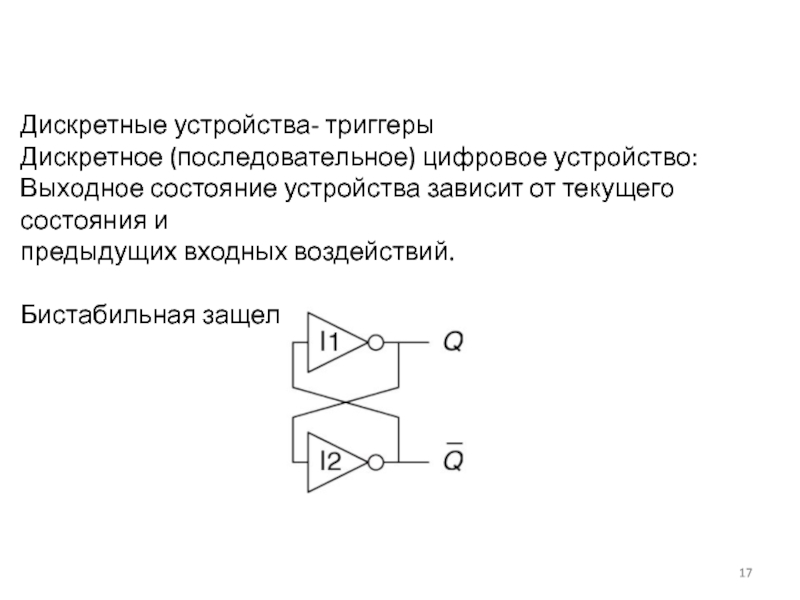

Дискретные устройства- триггеры

Дискретное (последовательное) цифровое устройство:

Выходное состояние устройства зависит от

текущего состояния и

предыдущих входных воздействий.

Бистабильная защелка:

Слайд 18

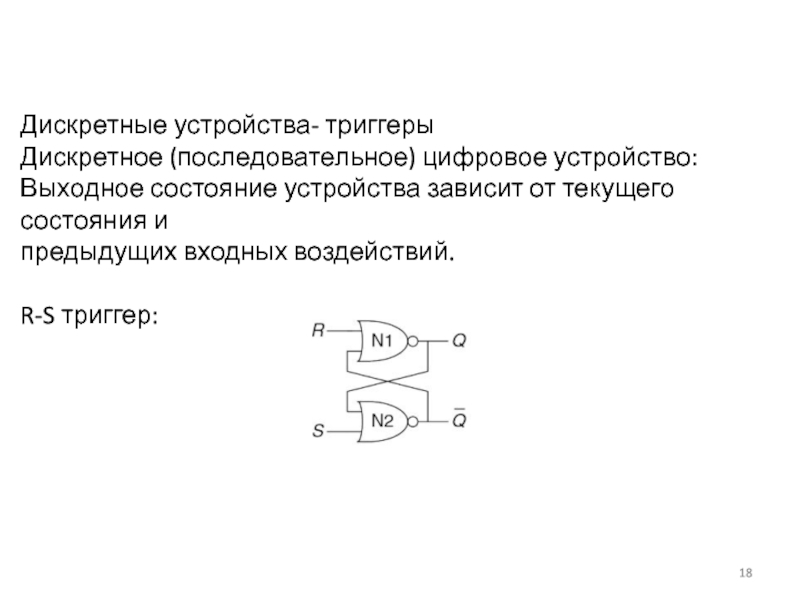

Дискретные устройства- триггеры

Дискретное (последовательное) цифровое устройство:

Выходное состояние устройства зависит от

текущего состояния и

предыдущих входных воздействий.

R-S триггер:

Слайд 19

Случай 1: Q=0

На вход поступает сигнал Q = 1. I2

инвертирует сигнал и подает на вход I1 сигнал Q¯ =

1. Соответственно, на выходе I1 – логический 0. В рассмотренном случае схема находится в стабильном состоянии.Случай II: Q=1

На вход I2 поступает 1 (Q). I2 инвертирует сигнал и и подает на вход I1 «0». Соответственно, на выходе I1 – логическая 1. В этом случае схема также находится в стабильном состоянии.

Так как инверторы, включенные перекрестно, имеют два стабильных состояния Q = 0 и Q = 1, то говорят, что схема бистабильна.

Попытка одновременно подать на входы одинаковые сигналы приведет к разрушению устройства.

Слайд 20

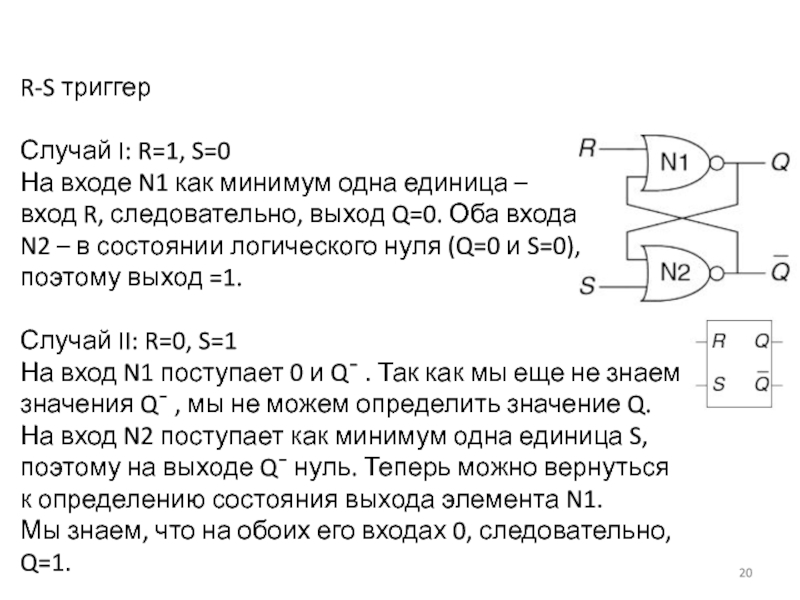

R-S триггер

Случай I: R=1, S=0

На входе N1 как минимум

одна единица – вход R, следовательно, выход Q=0. Оба входа

N2 – в состоянии логического нуля (Q=0 и S=0), поэтому выход =1.Случай II: R=0, S=1

На вход N1 поступает 0 и Q¯ . Так как мы еще не знаем

значения Q¯ , мы не можем определить значение Q.

На вход N2 поступает как минимум одна единица S, поэтому на выходе Q¯ нуль. Теперь можно вернуться к определению состояния выхода элемента N1. Мы знаем, что на обоих его входах 0, следовательно, Q=1.

Слайд 21

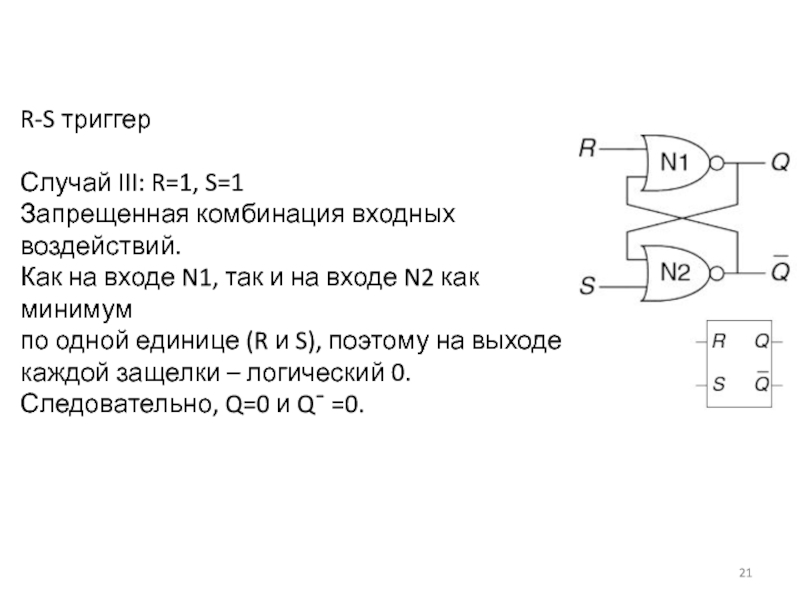

R-S триггер

Случай III: R=1, S=1

Запрещенная комбинация входных воздействий.

Как на

входе N1, так и на входе N2 как минимум по

одной единице (R и S), поэтому на выходе каждой защелки – логический 0.Следовательно, Q=0 и Q¯ =0.

Слайд 22

Случай IV: R=0, S=0

На вход N1 поступает 0 и Q¯

. Так как мы еще не знаем значения Q¯, мы

не можем определить значение на выходе элемента N1.На вход N2 поступает 0 и Q. Так как мы еще не знаем значения Q, мы не можем определить значение на выходе элемента N2. Этот случай аналогичен случаю с двумя перекрестно включенными инверторами. Мы знаем, что Q должен быть равен либо 0, либо 1. Рассмотрим каждый из этих двух случаев.

Слайд 23

Случай IVa: Q=0

Так как S и Q равны 0, то

на выходе N2 будет логическая 1, Q¯ =1. Теперь на

входе N1 есть одна единица – Q¯, поэтому на его выходе Q=0.Случай IVb: Q=1

Так как Q = 1, то на выходе N2 будет 0, Q¯ =0. Теперь на обоих входах N1 нули (R и Q¯ ), поэтому на его выходе логическая 1, Q=1.

Устройство остается в предыдущем состоянии.

Слайд 24

R-S триггер, УГО и таблица истинности

RS-триггер- бистабильный элементом с одним

битом состояния,

хранящимся в Q.

Состоянием можно управлять при помощи входов

R и S.

Когда на R поступает высокий уровень, выход сбрасывается в 0.

Когда высокий уровень приходит на S, выход устанавливается в 1.

Если ни на один вход не пришла логическая единица, триггер

сохраняет свое предыдущее состояние, значение выходов

не изменяется. Слайд 25

D триггер с синхронизацией по уровню

Сигнал D записывается в R-S

триггер

по разрешению от сигнала CLK

Слайд 26

D триггер с синхронизацией по уровню

Сигнал D записывается в R-S

триггер

по разрешению от сигнала CLK

Слайд 27

D триггер работающий по фронту

Из двух D триггеров, работающих по

уровню, можно построить D триггер, работающий по фронту тактового сигнала. Полученное

устройство будет переключаться по фронту нарастания сигнала.Слайд 29

D триггер работающий по фронту,

VHDL описание и временная диаграмма

Process

(clk)

Begin

if (clk='0' and c'event) then

q

End if;End process;

Слайд 30

D триггер со сбросом

В триггере с функцией сброса добавляется вход

RESET (сброс). Когда на RESET подан 0, триггер ведет себя

как обычный D-триггер. Когда на RESET подана 1, такой триггер игнорирует вход D и сбрасывает выход в 0.process (clk) begin

if (clk'event and clk = '1') then

if (reset = '1') then

q <= '0';

else q <= data;

end if;

end if;

end process;

Слайд 31

D триггер со сбросом и установкой

В триггере с функцией установки

добавляется вход SET. Когда на SET подан 0, триггер ведет

себя как обычный D-триггер. Когда на SET подан 1, такой триггер игнорирует вход D и устанавливает выход в 1.process (clk) begin

if (clk'event and clk = '1') then

if (reset = '1') then q <= '0';

if (set = '1') then q <= ‘1';

else q <= data;

-- r=q=0 – хранение данных

end if; end if; end if;

end process;

Слайд 33

Счетный триггер

D- триггер, у которого инверсный выход подключен к входу,

называется Т- триггером. После поступления на этот вход импульса, состояние

Т-триггера меняется на прямо противоположное. Счётным он называется потому, что подсчитывает количество импульсов, поступивших на его вход. Считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.Слайд 34

JK- триггер.

Таблица истинности JK-триггера практически совпадает с таблицей истинности

синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера

изменена таким образом, что при подаче двух единиц JK-триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов JK-триггер изменяет своё состояние на противоположное.Слайд 36

Сдвиговый регистр

Cдвиговые регистры представляют собой последовательно соединенную цепочку триггеров. Основной

режим их работы - это сдвиг разрядов кода, записанного в

эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Сдвиг бывает двух видов: вправо - это основной режим, который есть у всех сдвиговых регистров, и влево - этот режим есть только у некоторых реверсивных сдвиговых регистров.Слайд 39

Сдвиговый регистр с параллельной загрузкой

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

entity shiftreg is

generic(N: integer := 8);

port(clk, reset: in STD_LOGIC; load, sin:

in STD_LOGIC;d: in STD_LOGIC_VECTOR(N–1 downto 0);

q: out STD_LOGIC_VECTOR(N–1 downto 0);

sout: out STD_LOGIC); end;

architecture synth of shiftreg is

process(clk, reset) begin

if reset = ‘1’ then q <= (OTHERS => ‘0’);

elsif rising_edge(clk) then

if load then q <= d;

else q <= q(N–2 downto 0) & sin;

end if;

end if;

end process;

sout <= q(N–1);

end;

Слайд 44

Счетчик: Пример поведенческого описания и результат моделирования

-- Простой счетчик со

сбросом

process(CLK)

begin

if CLK 'event and CLK = '1' then

if (rst) =

'1' thenst <= "000000000";

else

st <= st + 1;

end if;

Слайд 45

Счетчик: Пример поведенческого описания схема-

«калька» с него

-- Простой счетчик со

сбросом

process(CLK)

begin

if CLK 'event and CLK = '1' then

if (rst) =

'1' thenst <= "000000000";

else

st <= st + 1;

end if;