Разделы презентаций

- Разное

- Английский язык

- Астрономия

- Алгебра

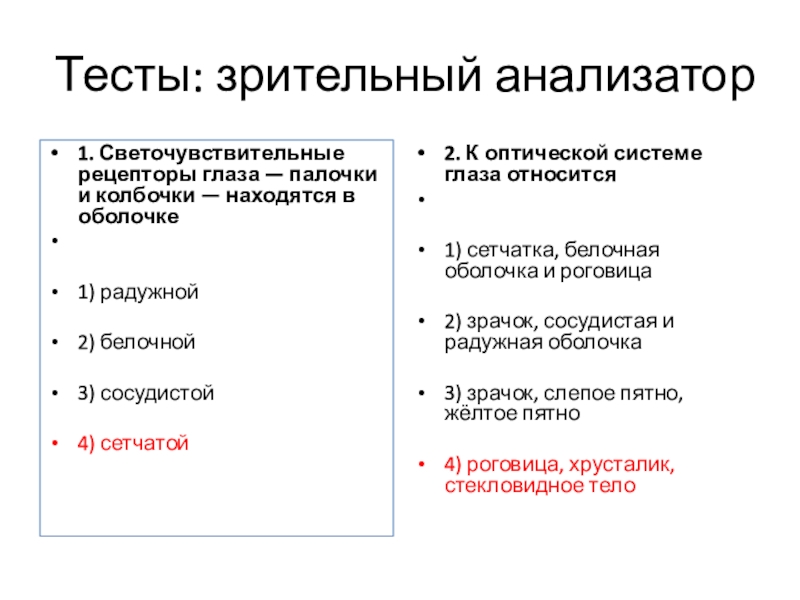

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Учебная дисциплина Схемотехника дискретных устройств Тема: Запоминающие

Содержание

- 1. Учебная дисциплина Схемотехника дискретных устройств Тема: Запоминающие

- 2. Постоянные запоминающие устройства (ПЗУ) ПЗУ представляет собой

- 3. Масочные ПЗУ Структура постоянной памяти образуется при её изготовлении и более перепрограммированию не подлежит.

- 4. Однократнопрограммируемые ПЗУ

- 5. Однократнопрограммируемые ПЗУРабота схемы: если все плавкие перемычки

- 6. Программируемые ПЗУ ППЗУ выпускаются заводом-изготовителем в

- 7. Перепрограммируемые ПЗУ Репрограммируемые ПЗУ позволяют, при необходимости,

- 8. ПЗУ с УФ стираниемНа функциональных и принципиальных

- 9. ПЗУ с УФ стираниемА - адресные входы;

- 10. ПЗУ с УФ стиранием Микросхема РПЗУ

- 11. ПЗУ с УФ стиранием ПЗУ со

- 12. ПЗУ с УФ стираниемЗатворы транзисторов при программировании

- 13. Флэш-память Флэш-память (Flash-Меmorу) по типу запоминающих

- 14. Флэш-память В схемах Флэш-памяти не предусмотрено

- 15. Флэш-памятьТермин Flash по одной из версий связан

- 16. Флэш-память Одновременное стирание всей информации ЗУ

- 17. Флэш-памятьСреди устройств с блочным стиранием выделяют схемы

- 18. Флэш-памятьМикросхемы для замены жестких магнитных дисков (Flash-File

- 19. Флэш-память

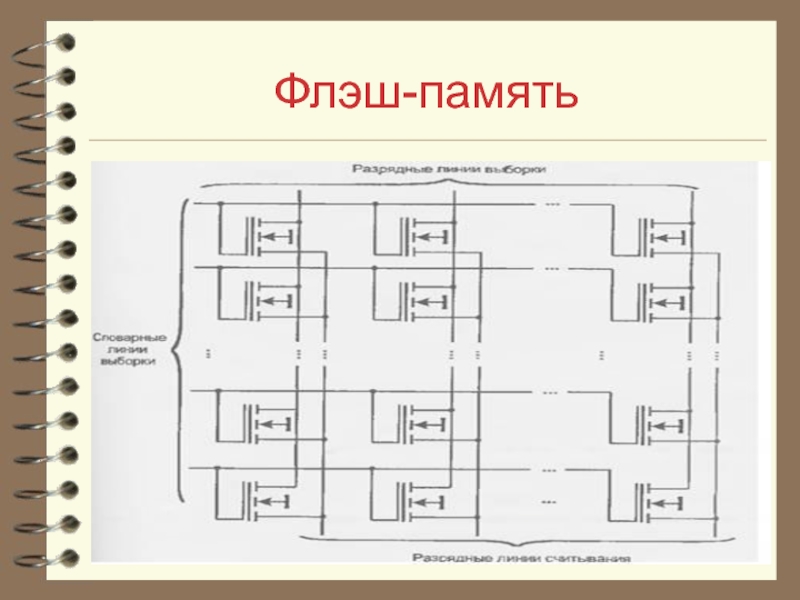

- 20. Флэш-памятьНакопители на основе ячеек ИЛИ-НЕ (с параллельным

- 21. Флэш-памятьКаждый столбец представляет собою совокупность параллельно соединенных

- 22. Флэш-памятьНакопители на основе ячеек ИЛИ-НЕ широко используются

- 23. Флэш-памятьФлэш-память с адресным доступом, ориентированная на хранение

- 24. Флэш-памятьИмея преемственность с ЗУ типов Е2РRОМ и

- 25. ПЗУ с электрическим стиранием

- 26. ПЗУ с электрическим стиранием Подача напряжения

- 27. Статические ОЗУ Рассматриваемые типы запоминающих устройств (ЗУ)

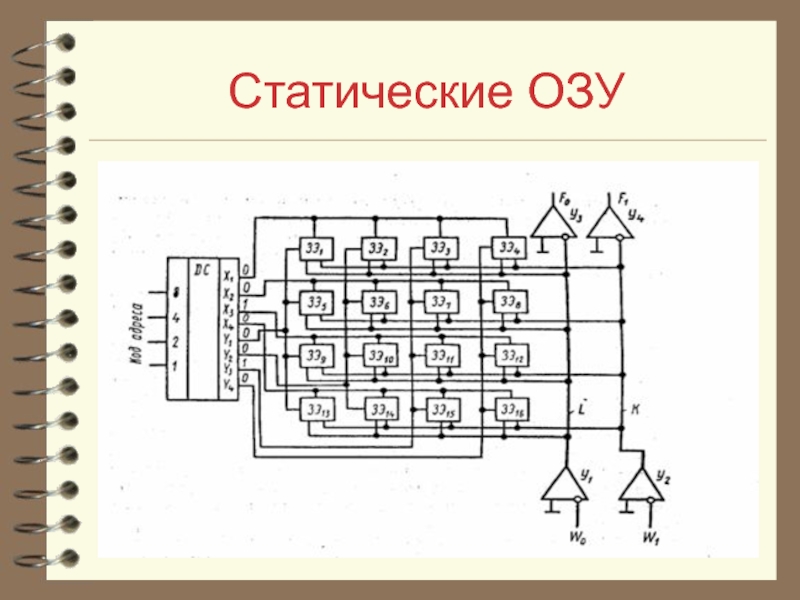

- 28. Статические ОЗУ

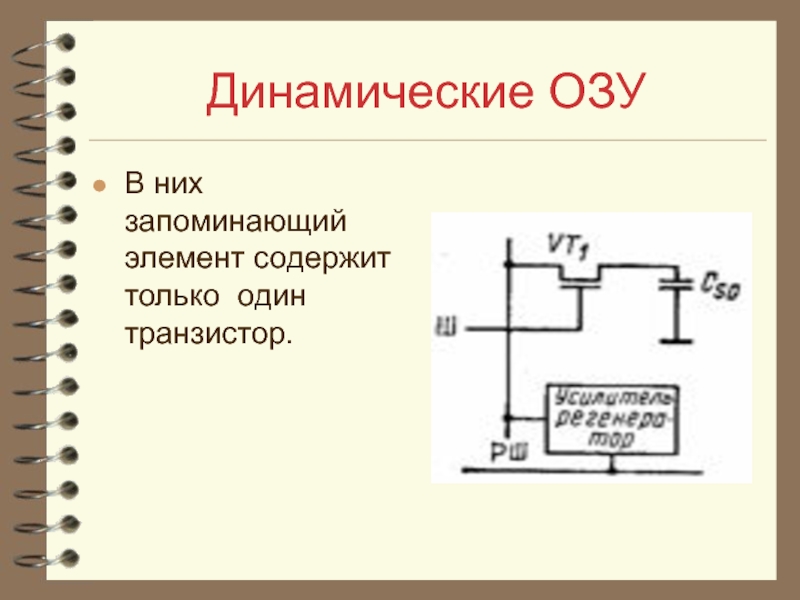

- 29. Динамические ОЗУ В них запоминающий элемент содержит только один транзистор.

- 30. Динамические ОЗУ Информация в

- 31. Динамические ОЗУПоследний, по существу является триггерным элементом

- 32. Динамические ОЗУВ режиме чтения триггер усилителя —

- 33. Динамические ОЗУПри этом в начале он потребляет

- 34. Динамические ОЗУВ режиме хранения информации необходимо периодически

- 35. Динамические ОЗУ Накопитель двухкоордииатпого

- 36. Динамические ОЗУВ ЗЭ одной матрицы записываются одноименные

- 37. Скачать презентанцию

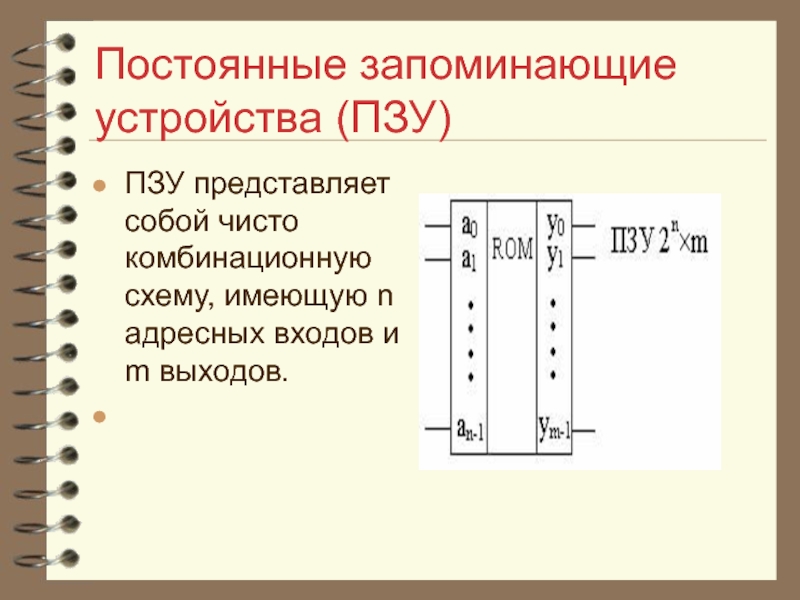

Постоянные запоминающие устройства (ПЗУ) ПЗУ представляет собой чисто комбинационную схему, имеющую n адресных входов и m выходов.

Слайды и текст этой презентации

Слайд 2Постоянные запоминающие устройства (ПЗУ)

ПЗУ представляет собой чисто комбинационную схему,

имеющую n адресных входов и m выходов.

Слайд 3Масочные ПЗУ

Структура постоянной памяти образуется при её

изготовлении и более перепрограммированию не подлежит.

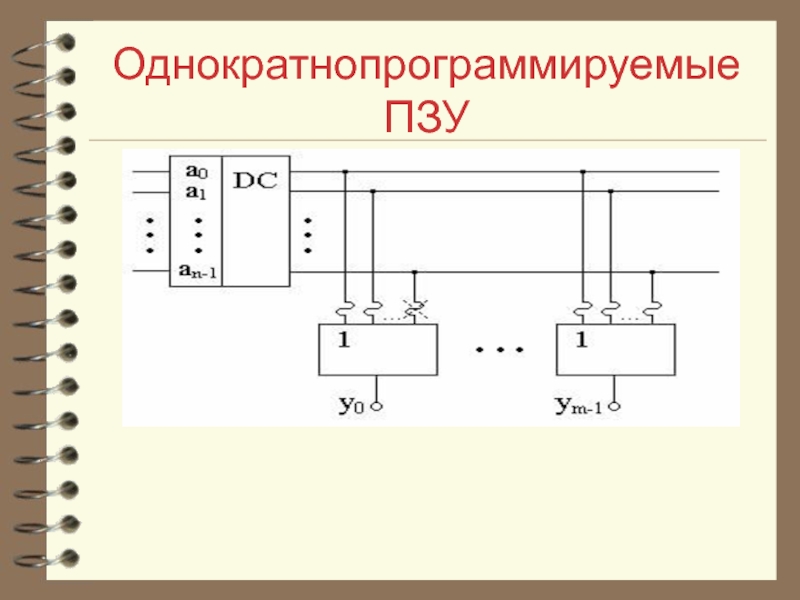

Слайд 5Однократнопрограммируемые ПЗУ

Работа схемы: если все плавкие перемычки целы, то при

выборе любого адреса на входы всех дизъюнкторов будет поступать хотя

бы по одной единице, поэтому y0 = y1=···= ym-1=1.Для занесения в схему какой-либо информации некоторые перемычки пережигаются (ПЗУ с прожиганием), тогда на некоторых дизъюнкторах на все входы поступают “0” и на выход подается “0”.

Слайд 6Программируемые ПЗУ

ППЗУ выпускаются заводом-изготовителем в "чистом виде", т.е.

по всем адресам записаны"0". Программирование ППЗУ осуществляется пользователем ППЗУ на

специальной установке, называемой программатором.В ППЗУ можно записать (его программировать) информацию только один раз.

Изменить записанную информацию или исправить ее нельзя.

ППЗУ нашли широкое применение в ЭВМ для хранения запускающих программ. Они обладают большим быстродействием, чем репрограммируемые ПЗУ

Слайд 7Перепрограммируемые ПЗУ

Репрограммируемые ПЗУ позволяют, при необходимости, перепрограммировать ПЗУ, т.е.

стереть ранее записанную информацию и записать новую.

По способу стирания

ранее записанной информации РПЗУ бывают с ультрафиолетовым (ультрафиолетовыми лучами) и электрическим стиранием. РПЗУ позволяют десятки (некоторые до 1000) раз перепрограммировать и сохранять записанную информацию десятки и сотни тысяч часов. Быстродействие РПЗУ несколько хуже быстродействия ППЗУ. Слайд 8ПЗУ с УФ стиранием

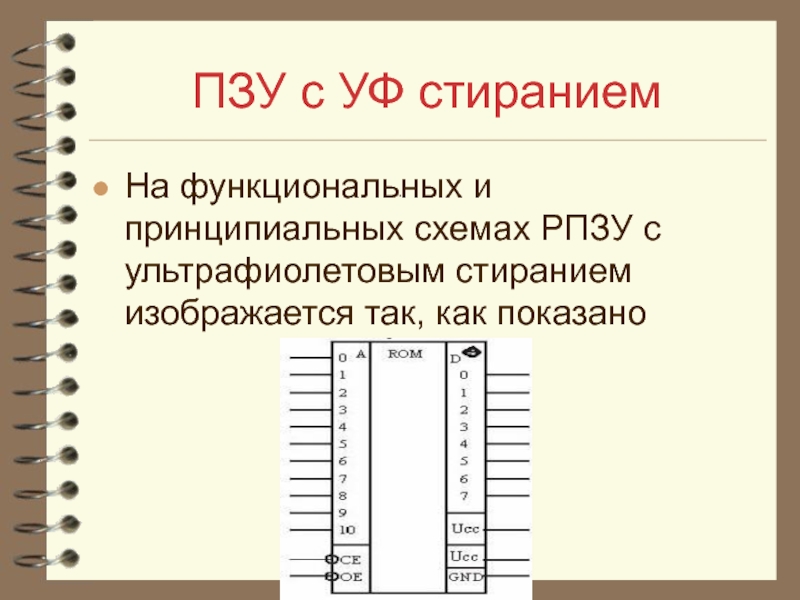

На функциональных и принципиальных схемах РПЗУ с

ультрафиолетовым стиранием изображается так, как показано

.

Слайд 9ПЗУ с УФ стиранием

А - адресные входы; D – информационные

выходы. Uce – вход подачи напряжения записи (в режиме хранения

на этот вход подается Ucc); Ucc – вывод для подачи напряжения питания. СЕ и ОЕ –входы управления состоянием выводов, если СЕ=ОЕ=1, входы D имеют высокоимпедансное состояние. При СЕ=ОЕ=0 вывод информации разрешен.Слайд 10ПЗУ с УФ стиранием

Микросхема РПЗУ К573РФ2 (РФ5) имеет

одиннадцатиразрядный дешифратор, выходы которого соединены с восьмиразрядной матрицей М2. В

процессе записи выходные элементы РПЗУ находятся в режиме приема информации через выводы D0 . . . D7 (на входе “ОЕ“ уровень “1”). В режиме считывания записанной информации выводы “Uce” и “Ucc” объединяются, и на них подается напряжение питания +5В.Слайд 11ПЗУ с УФ стиранием

ПЗУ со стиранием информации

ультрафиолетовым излучением в настоящее время наиболее широко используются в микропроцессорных

системах. В БИС таких ПЗУ каждый бит хранимой информации отображается состоянием соответствующего МОП-транзистора с плавающим затвором (у него нет наружного вывода для подключения).Слайд 12ПЗУ с УФ стиранием

Затворы транзисторов при программировании «1» заряжаются лавинной

инжекцией, т.е. обратимым пробоем изолирующего слоя, окружающего затвор под действием

электрического импульса напряжением 18 – 26 В. Заряд, накопленный в затворе, может сохраняться очень долго из-за высокого качества изолирующего слоя. Так, например, для ППЗУ серии К573 гарантируется сохранение информации не менее 15 – 25 тысяч часов во включенном состоянии и до 100 тысяч часов (более 10 лет) — в выключенном.Слайд 13Флэш-память

Флэш-память (Flash-Меmorу) по типу запоминающих элементов и

основным принципам работы подобна памяти типа Е2РROМ однако ряд архитектурных

и структурных особенностей позволяют выделить ее в отдельный класс. Разработка Флэш-памяти считается кульминацией десятилетнего развития схемотехники памяти с электрическим стиранием информации.Слайд 14Флэш-память

В схемах Флэш-памяти не предусмотрено стирание отдельных слов,

стирание информации осуществляется либо для всей памяти одновременно, либо для

достаточно больших блоков. Понятно, что это позволяет упростить схемы ЗУ, т. е. способствует достижению высокого уровня интеграции и быстродействия при снижении стоимости. Технологически схемы Флэш-памяти выполняются с высоким качеством и обладают очень хорошими параметрами.Слайд 15Флэш-память

Термин Flash по одной из версий связан с характерной особенностью

этого вида памяти — возможностью одновременного стирания всего ее объема

Согласно этой версии ещё до появления Флэш-памяти при хранении секретных данных использовались устройства, которые при попытках несанкционированного доступа к ним автоматически стирали хранимую информацию и назывались устройствами типа Flash(вспышка, мгновение). Это название перешло и к памяти, обладавшей свойством быстрого стирания всего массива данных одним сигналом.

Слайд 16Флэш-память

Одновременное стирание всей информации ЗУ реализуется наиболее просто,

но имеет тот недостаток, что даже замена одного слова в

ЗУ требует стирания и новой записи для всего ЗУ в целом. Для многих применений это неудобно. Поэтому наряду со схемами с одновременным стиранием всего содержимого имеются схемы с блочной структурой, в которых весь массив памяти делится на блоки, стираемые независимо друг от друга. Объем таких блоков сильно разнится: от 256 байт до 128 Кбайт.Слайд 17Флэш-память

Среди устройств с блочным стиранием выделяют схемы со специализированными блоками

(несимметричные блочные структуры). По имени так называемых Вооt-блоков, в которых

информация надежно защищена аппаратными средствами от случайного стирания, эти ЗУ называют Вооt Blосk Flash Метоrу. Вооt блоки хранят программы инициализации системы, позволяющие ввести ее в рабочее состояние после включения питания.Слайд 18Флэш-память

Микросхемы для замены жестких магнитных дисков (Flash-File Метоrу) содержат более

развитые средства перезаписи информации и имеют идентичные блоки (симметричные блочные

структуры).Одним из элементов структуры Флэш-памяти является накопитель (матрица запоминающих элементов). В схемотехнике накопителей развиваются два направления: на основе ячеек типа ИЛИ-НЕ (и на основе ячеек типа И-НЕ

Слайд 20Флэш-память

Накопители на основе ячеек ИЛИ-НЕ (с параллельным включением ЛИЗ-МОП-транзисторов с

двойным затвором) обеспечивают быстрый доступ к словам при произвольной выборке.

Они приемлемы для разных применений, но наиболее бесспорным считается их применение в памяти для хранении редко обновляемых данных. При этом возникает полезная преемственность с применявшимися ранее КОМ и ЕРКОМ, сохраняются типичные сигналы управления, обеспечивающие чтение с произвольной выборкой. Структура матрицы накопителя показана на рисунке 4.8.Слайд 21Флэш-память

Каждый столбец представляет собою совокупность параллельно соединенных транзисторов Разрядные линии

выборки находятся под высоким потенциалом. Все транзисторы невыбранных строк заперты.

В выбранной строке открываются и передают высокий уровень напряжения на разрядные линии считывания те транзисторы, в плавающих затворах которых отсутствует заряд электронов. и, следовательно, пороговое напряжение транзистора имеет нормальное (не повышенное) значение.Слайд 22Флэш-память

Накопители на основе ячеек ИЛИ-НЕ широко используются фирмой Intel. Имеются

мнения о конкурентоспособности этих накопителей и в применениях, связанных с

заменой жестких магнитных дисков Флэш-памятью.Структуры с ячейками И-НЕ более компактны, но не обеспечивают режима произвольного доступа и практически используются только в схемах замены магнитных дисков. В схемах на этих ячейках сам накопитель компактнее, но увеличивается количество логических элементов обрамления накопителя.

Слайд 23Флэш-память

Флэш-память с адресным доступом, ориентированная на хранение не слишком часто

изменяемой информации, может иметь одновременное стирание всей информации (архитектура Вulk

Еrаsе) или блочное стирание (архитектура Вооt Blосk Flash Метоrу).Слайд 24Флэш-память

Имея преемственность с ЗУ типов Е2РRОМ и ЕРRОМ, разработанными ранее,

схемы Флэш-памяти предпочтительнее Е2РRОМ по информационной емкости и стоимости в

применениях, где не требуется индивидуальное стирание слов, а в сравнении с ЕРRОМ обладают тем преимуществом, что не требуют специальных условий и аппаратуры для стирания данных, которое к тому же происходит гораздо быстрее.Слайд 25ПЗУ с электрическим стиранием

Они позволяют

производить как запись, так и стирание (или перезапись) информации с

помощью электрических сигналов. Для построения таких ППЗУ применяются структуры с лавинной инжекцией заряда, аналогичные тем, на которых строятся ППЗУ с УФ стиранием, но с дополнительными управляющими затворами, размещаемыми над плавающими затворами.Слайд 26ПЗУ с электрическим стиранием

Подача напряжения на управляющий затвор

приводит к рассасыванию заряда за счет туннелирования носителей сквозь изолирующий

слой и стиранию информации. По этой технологии изготовляют микросхемы К573РР2.Достоинства ППЗУ с электрическим стиранием: высокая скорость перезаписи информации и значительное допустимое число циклов перезаписи — не менее 10000.

Слайд 27Статические ОЗУ

Рассматриваемые типы запоминающих устройств (ЗУ) применяются в компьютерах

для хранения информации, которая изменяется в процессе вычислений, производимых в

соответствии с программой, и называются оперативными (ОЗУ). Информация, записанная в них, разрушается при отключении питания.Главной частью ЗУ является накопитель, состоящий из триггеров

Слайд 30Динамические ОЗУ

Информация в таком элементе хранится

в виде заряда на запоминающем конденсаторе , обкладками которого являются

области стока МОП-транзистора и подложки. Запись и считывание ннформаини производятся путем открывания транзистора по затвору и подключения тем самым заноминаюшей емкости к схеме усилителя-регенератора.Слайд 31Динамические ОЗУ

Последний, по существу является триггерным элементом ,который В зависимости

от предварительной подготовки или принимает (считывает) информацию из емкостной запоминающей

ячейки, устанавливаясь при этом в состояние 0 пли 1,или, наоборот, в режиме записи соответствующим образом заряжает ячейку, будучи предварительно установленным в 0 или 1Слайд 32Динамические ОЗУ

В режиме чтения триггер усилителя — регенератора в начале

специальным управляющим сигналом устанавливается в неустойчивое равновесное состояние, из которого

при подключении к нему запоминающей емкостион переключается в 0 или I.