Слайд 1Занятие ¼. Лекция -2 часа. Цифровые интегральные схемы

Основные вопросы

Понятия

алгебры логики.

Параметры логических элементов.

Диодно-транзисторные логические элементы.

Транзисторно-транзисторные логические элементы.

Учебная цель: изучить

понятия алгебры логики, параметры логических элементов,

диодно-транзисторные логические элементы, транзисторно-транзисторные логические элементы.

1. Понятия

алгебры логики

В состав импульсных цифровых устройств входят логические и запоминающие элементы. Логические элементы (ЛЭ) выполняют простейшие логические операции над цифровой информацией, а запоминающие служат для ее сохранения. Логические элементы могут иметь m входов и один выход, к которому можно подключать входы n последующих логических элементов.

Логическая операция состоит в преобразовании по определенным правилам входной цифровой информации в выходную. Сигналы на входах и выходах логических элементов являются обычно двоичными (бинарными). Они могут принимать лишь два значения, символически обозначаемые 0 или 1. Цифрой 0 кодируют низкий уровень напряжения или отсутствие импульса, а цифрой 1 – высокий уровень напряжения или наличие импульса. Входные сигналы обозначаются также буквами латинского алфавита , , … …, , а выходные сигналы – , , … , … .

Логические преобразования двоичных сигналов выполняются на базе следующих элементарных операций, лежащих в основе так называемой алгебры Буля:

а) Логическое сложение, называемой также дизъюнкцией либо операцией ИЛИ. Обозначается символом " V " или знаком обычного сложения. Данная операция символически записывается в виде и читается: " y есть (равно) или … или ".

б) Логическое умножение, называемое также конъюнкцией либо операцией И. Обозначается символом " Λ " или как обычное умножение " ∙ ", или просто написанием переменных рядом без всякого знака. Данная операция записывается в виде и читается " у есть (равно) , , … и ".

в) Логическое отрицание, называемое также инверсией либо операцией НЕ, обозначается чертой над переменной и читается " у равно не х". Обозначения элементов, выполняющих перечисленные логические операции, показаны на рис.4.1 а,б,в соответственно. Там же представлены таблицы информационных значений и , поясняющие работу логических элементов и называемые переключательными таблицами или таблицами истинности.

Слайд 3Элементы, реализующие операцииИ, ИЛИ, НЕ, являются основными в том смысле,

что с помощью их можно создать ключевое устройство, реализующее сколь

угодно сложную логическую функцию:

, j=1, 2, …, n. (4.1)

Доказано, что для построения сколь угодно сложных логических цепей достаточно использовать только два элемента из трех основных, а именно И и НЕ либо ИЛИ и НЕ. Каждую пару указанных элементов можно объединить и получить универсальный логический элемент. Элемент ИЛИ-НЕ на два входа работает в соответствии с таблицей истинности рис.4.1, г. Второй универсальный элемент И-НЕ и таблица истинности представлены на рис.4.1, д. Широко применяется и универсальный логический элемент И-ИЛИ-НЕ; этот элемент реализует, например, для четырех переменных функцию вида .

,

,

,

Слайд 42. ПАРАМЕТРЫ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ И ИХ

КЛАССИФИКАЦИЯ

Логические элементы классифицируются

по различным признакам:

а) По способу представления чисел 0 и 1

(потенциальные, импульсные и потенциально-импульсные).

б) По связи между сигналами на входах и выходе (дизъюнктор, конъюнктор, инвертор).

в) По типу компонентов, на которых построены логические схемы, реализующие операцию И либо ИЛИ:

резисторно - транзисторные (РТ),

диодно-транзисторные (ДТЛ),

транзисторно-транзисторные (ТТЛ),

транзисторные (Т).

г) По способу соединения полупроводниковых приборов в логической схеме. По этому признаку различают схемы со связанными коллекторами, схемы со связанными эмиттерами. Например, коллекторно-связанная транзисторная логика (КСТЛ), эмиттерно-связанная транзисторная логика или транзисторная логика на переключателях стока (ЭСТЛ или ПТТЛ).

д) По виду связи логической схемы И либо ИЛИ и ключа инвертора: непосредственная (НС), резистивная (РС), резистивно-емкостная (РЕС), диодная (ДС).

Основными параметрами логических элементов являются:

ПОТРЕБЛЯЕМАЯ ПОЩНОСТЬ.

ЛЭ могут находиться во включенном или выключенном состояниях. При этом они потребляют от источников питания различную мощность P0 и P1 во включенном и выключенном состоянии соответственно. Как правило,

P0 > P1 P0=I0En P1= I1En.

, .

В этих выражениях I0 и I1 − токи в цепи питания одного ЛЭ во включенном и выключенном состоянии, а En − напряжение питания

При наличии нескольких источников питания для одного ЛЭ P0 и P1 определяются как суммы потребляемых мощностей от каждого источника. В одном корпусе интегральной микросхемы (ИМС) может быть N одинаковых ЛЭ. Тогда мощности будут определены для всех ЛЭ. Мощности потребляемые одним ЛЭ будут в N раз меньше.

В справочной литературе приводят так называемую среднюю (статическую) потребляемую мощность, считая, что ЛЭ находится во включенном и выключенном состояниях одинаковое время

. (4.2)

Значение Pcp не должно превышать величины, указанной в справочнике.

В ряде ЛЭ в моменты переключений потребляемые мощности возрастают. В этих случаях указывается средняя (динамическая) потребляемая мощность одним ЛЭ для определенной частоты переключений.

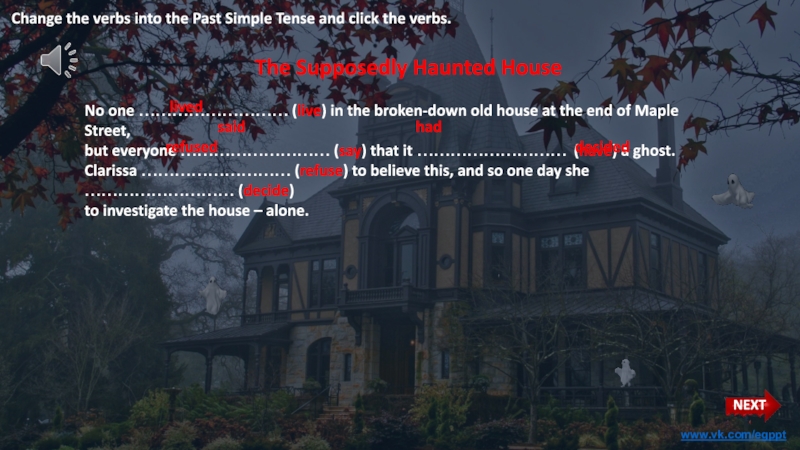

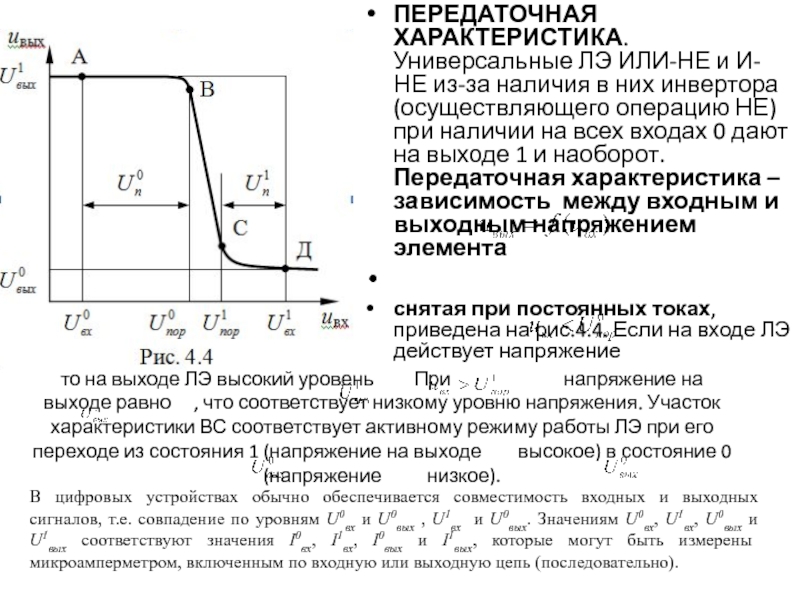

Слайд 5то на выходе ЛЭ высокий уровень

При

напряжение на выходе равно , что соответствует низкому уровню напряжения. Участок характеристики ВС соответствует активному режиму работы ЛЭ при его переходе из состояния 1 (напряжение на выходе высокое) в состояние 0 (напряжение низкое).

ПЕРЕДАТОЧНАЯ ХАРАКТЕРИСТИКА. Универсальные ЛЭ ИЛИ-НЕ и И-НЕ из-за наличия в них инвертора (осуществляющего операцию НЕ) при наличии на всех входах 0 дают на выходе 1 и наоборот. Передаточная характеристика – зависимость между входным и выходным напряжением элемента

снятая при постоянных токах, приведена на рис.4.4. Если на входе ЛЭ действует напряжение

В цифровых устройствах обычно обеспечивается совместимость входных и выходных сигналов, т.е. совпадение по уровням U0вх и U0вых , U1вх и U0вых. Значениям U0вх, U1вх, U0вых и U1вых соответствуют значения I0вх, I1вх, I0вых и I1вых, которые могут быть измерены микроамперметром, включенным по входную или выходную цепь (последовательно).

Слайд 6ПОМЕХОУСТОЙНИВОСТЬ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ.

Это максимально допустимое напряжение помехи, действующей на

входе ЛЭ наряду с регулярными сигналами, при котором еще не

происходит изменение состояния ЛЭ. Помехи могут быть как статическими, например, изменения входных напряжений, связанные с падением напряжения на общих шинах цепей питания, так и импульсными (кратковременными). Импульсные помехи обусловлены как внешними электромагнитными полями, так и индуктивной и емкостной связью между сигнальными линиями цепей, а так же переходными процессами в последних.

Так, если на выходе имеется сигнал 1 (т. А рис.4.4), то запас помехоустойчивости АВ равен разности напряжений U0n =│U0пор - U0вх│, а если сигнал 0 (т. С), то запас помехоустойчивости СД равен разности напряжений. U1n =│U1вх – U1пор│,

БЫСТРОДЕЙСТВИЕ.

Характеризуется средней задержкой распространения , которая позволяет определить максимально возможную частоту переключений

Fмакс =1/tз.ср, tз.ср =(t10 +t01)/2, (4.3)

где t10 − задержка переключения из состояния 1 в состояние 0 или время включения, t01 − задержка переключения из состояния 0 в состояние 1 или время выключения.

Заметим, что при конечной длительности фронта входного сигнала, что обычно и имеет место, задержки включения и выключения сигнала отсчитываются либо на 10%, либо, чаще, на 50%-ных уровнях входного и выходного сигналов.

Для ЛЭ на ИМС tз.ср составляет единицы или десятки наносекунд. Измерять такие величины приборами сложно.

Чтобы определить tз.ср, используют метод «кольцевого генератора». Суть метода. Нечетное число N ЛЭ (N=2a+1, где а=1, 2, 3 …) соединяются последовательно. Выход последнего ЛЭ соединяется с входом первого (N=13 или 15). Образуется генератор колебаний, близких к синусоидальным колебаниям.

Генерация возникает за счет выполнения условий баланса фаз и амплитуд. На участке ВС передаточной характеристики (рис.3.4) коэффициент передачи ЛЭ >>1, что обеспечивает выполнение условия баланса амплитуд.

Слайд 7По условию баланса фаз общий сдвиг фазы в петле положительной

ОС должен быть кратным 2π. N ЛЭ дают сдвиг фазы

N π=(2α+1)π. Недостающее π набегает за счет N tз.ср , т.е. π= ω N tз.ср, где ω − генерируемая круговая частота. Тогда

, (4.4)

где Т – период генерируемых колебаний.

Измерить на экране осциллографа С1-65 величину Т обычным методом (с помощью калибрационных меток) достаточно трудно. Поэтому, получив устойчивую осциллограмму, подсчитывают количество периодов на отрезке 20 мм, отключают кольцевой генератор от «Входа Y», включают метки, подсчитывают длительность отрезка развертки 20 мм в мкс, полученный результат делят на подсчитанное ранее количество периодов в этом отрезке. Это и будет величина Т.

Слайд 8КОЭФФИЦИЕНТ ОБЪЕДИНЕНИЯ (m) определяет число внешних цепей, которые объединяются в

данном элементе при выполнении логической операции И либо ИЛИ (коэффициент

m равен числу входов элемента И либо ИЛИ). Для логических элементов И обычно mи=2..6, а для ЛЭ ИЛИ mили=2..4, . С помощью специальных схем по входу получают m>10.

КОЭФФИЦИЕНТ РАЗВЕТВЛЕНИЯ (n) показывает сколько входов однотипных логических схем может быть подсоединено к выходу рассматриваемой схемы. Коэффициент n отражает нагрузочную способность интегрального логического элемента при его работе на входные цепи нескольких однотипных с ним узлов. Для ЛЭ на ИМС n=4…10.

При большем числе подключенных к выходу входов снижается быстродействие, усиление, помехоустойчивость, возрастает потребляемая мощность, может прекратиться переключение последующих схем. С помощью буферных схем (усилителей мощности) можно получить n=20…50.

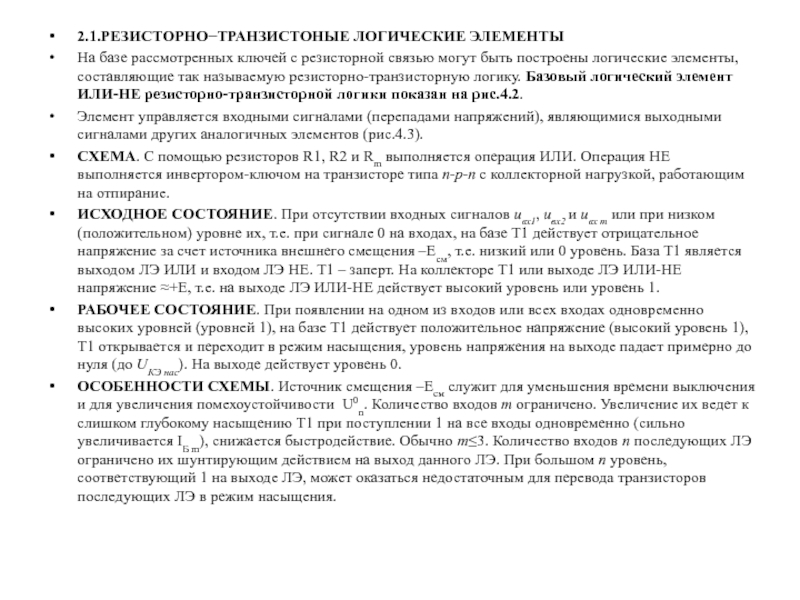

Слайд 92.1.РЕЗИСТОРНО−ТРАНЗИСТОНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

На базе рассмотренных ключей с резисторной связью могут

быть построены логические элементы, составляющие так называемую резисторно-транзисторную логику. Базовый

логический элемент ИЛИ-НЕ резисторно-транзисторной логики показан на рис.4.2.

Элемент управляется входными сигналами (перепадами напряжений), являющимися выходными сигналами других аналогичных элементов (рис.4.3).

СХЕМА. С помощью резисторов R1, R2 и Rm выполняется операция ИЛИ. Операция НЕ выполняется инвертором-ключом на транзисторе типа n-p-n с коллекторной нагрузкой, работающим на отпирание.

ИСХОДНОЕ СОСТОЯНИЕ. При отсутствии входных сигналов uвх1, uвх2 и uвх m или при низком (положительном) уровне их, т.е. при сигнале 0 на входах, на базе Т1 действует отрицательное напряжение за счет источника внешнего смещения –Есм, т.е. низкий или 0 уровень. База Т1 является выходом ЛЭ ИЛИ и входом ЛЭ НЕ. Т1 – заперт. На коллекторе Т1 или выходе ЛЭ ИЛИ-НЕ напряжение ≈+Е, т.е. на выходе ЛЭ ИЛИ-НЕ действует высокий уровень или уровень 1.

РАБОЧЕЕ СОСТОЯНИЕ. При появлении на одном из входов или всех входах одновременно высоких уровней (уровней 1), на базе Т1 действует положительное напряжение (высокий уровень 1), Т1 открывается и переходит в режим насыщения, уровень напряжения на выходе падает примерно до нуля (до UКЭ нас). На выходе действует уровень 0.

ОСОБЕННОСТИ СХЕМЫ. Источник смещения –Есм служит для уменьшения времени выключения и для увеличения помехоустойчивости U0n. Количество входов m ограничено. Увеличение их ведет к слишком глубокому насыщению Т1 при поступлении 1 на все входы одновременно (сильно увеличивается IБ m), снижается быстродействие. Обычно m≤3. Количество входов n последующих ЛЭ ограничено их шунтирующим действием на выход данного ЛЭ. При большом n уровень, соответствующий 1 на выходе ЛЭ, может оказаться недостаточным для перевода транзисторов последующих ЛЭ в режим насыщения.

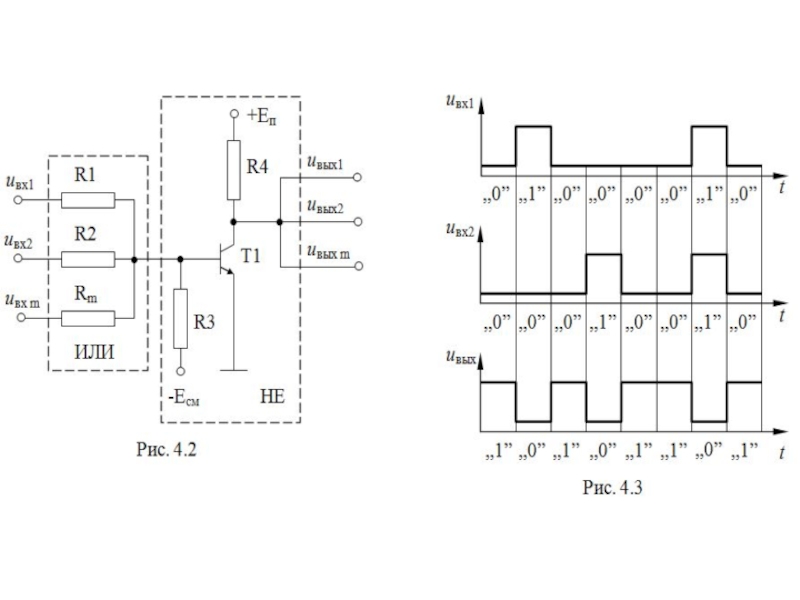

Слайд 113. ДИОДНО-ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Диодно-транзисторная схема (рис.4.5) реализует логическую функцию И-НЕ

входных переменных (сигналов): y=x1,x2 …xm

СХЕМА. С помощью диодов Д1,

Д2, резистора R1 и источника +Е1 реализуется ЛЭ И, выходом которого является точка А. На Т1, R2, R3, +Е1, −Е2, Дсм реализован инвертор − ЛЭ НЕ. Дсм – кремниевый диод смещения, повышающий помехозащищенность инвертора. При токе iД cм , превышающем всего несколько десятков микроампер, диод Дсм открыт, напряжение на нем практически постоянно и не зависит от тока, uДсм=Uсм; причем Uсм ≈0,6 … 0,8 В. Вольтамперная характеристика диода смещения при uДсм>0 расположена практически вертикально. Следовательно, напряжение на диоде положительно и постоянно. Поэтому диод Дсм может рассматриваться как источник постоянного смещения, равного Uсм. В схемах могут использоваться два или больше смещающих диодов.

ИСХОДНОЕ СОСТОЯНИЕ. При низких уровнях uвх1, uвх2 (рис.4.6) диоды Д2 и Д2 открыты, поскольку их катоды через внутренние сопротивления источников входных сигналов соединены с корпусом. Прямые сопротивления диодов и сопротивления источников uвх1 и uвх2 << R1. Почти все напряжение Е1 падает на R1. Напряжение между точкой А и корпусом невелико. Т.о. на выходе ЛЭ и действует низкий уровень напряжения. Через диод смещения и R3 на −Е2 (далее на корпус, через Е1 и R1) протекает небольшой прямой ток, создавая на резисторе R3 небольшое UR3. Напряжение на базе транзистора

UБЭ≈UR3-Е2 поэтому транзистор Т1 заперт. Напряжение на выходе uвых=uк≈Е1, т.е. на выходе действует высокий уровень 1.

РАБОЧЕЕ СОСТОЯНИЕ. При поступлении высокого уровня только на один из входов, например на первый, Д1 закрывается, но общее сопротивление цепи между точкой А и корпусом, а значит, и напряжение между этими точками возрастает незначительно из-за шунтирующего действия Д2. В точке А появляется ложный сигнал, уровень которого близок к уровню 0. При этом Iпр и UR3 возрастают незначительно. UБЭ остается меньше нуля, Т1 остается запертым. Уровень uвых остается единичным. Аналогично схема реагирует на помехи, возникающие по другим причинам. При одновременном воздействии на оба входа единичных уровней (высоких) закрываются и Д1 и Д2. Их обратные сопротивления >> R1. Почти все Е1 теперь падает между точкой А и корпусом, т.е. на выходе ЛЭ И действует высокий уровень 1. Ток резко возрастает. Резко возрастает UR3. Теперь UБЭ = UR3 –Е2 >0 Т1 открывается и переходит в режим насыщения. На выходе действует низкий уровень 0.

ОСОБЕННОСТИ СХЕМЫ. Более высокая помехозащищенность, чем в РТЛ.

Выше быстродействие, поскольку в процессе переключений транзистора диод Дсм выполняет такую же роль, что и заряженный конденсатор в цепях связи. Действительно, когда на входах действуют высокие уровни напряжений, диоды Д1 и Д2 заперты, потенциал в т.А большой, через диод Дсм протекает большой ток базы Т1: в его базе накоплен значительный заряд. Когда потенциал т.А понижается, диод Дсм обеспечивает значительный обратный ток базы, вследствие чего Т1 быстро выключается. Важно, чтобы в качестве Дсм использовался такой диод с накоплением заряда, чтобы время рассасывания заряда в нем было не меньше длительности выключения транзистора.

Иногда используют несколько диодов смещения.

В некоторых схемах роль диода смещения играет эмиттерный переход дополнительного транзистора.

Диод смещения или переход смещения может включаться в эмиттерную (а не базовую) цепь.

Иногда исключают Е2, соединяя R3 с корпусом.

К точке А может подключаться расширительный вход ИЛИ, к которому может подключаться выход другого ЛЭ.

Для увеличения n в состав базового элемента вводят эмиттерный повторитель.

Слайд 13

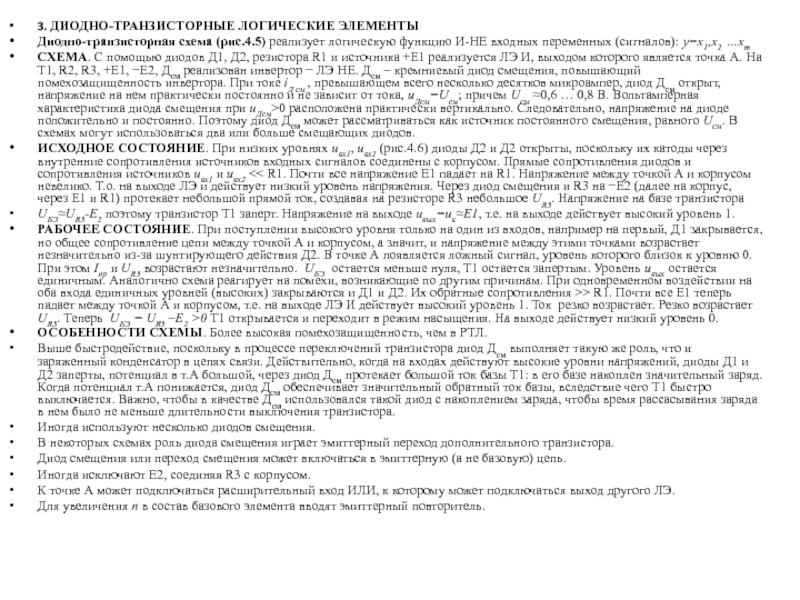

4.1. ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

С ПРОСТЫМ ИНВЕРТОРОМ

СХЕМА. Схема базового элемента И-НЕ

ТТЛ (рис.4.7) отличается от рассмотренной выше схемы ДТЛ тем, что

роль Д1 и Д2 (рис.4.5) здесь выполняют эмиттерные переходы многоэмиттерного транзистора Т1, а роль диода смещения Дсм коллекторный переход Т1. Интегральный эмиттерный транзистор представляет собой совокупность транзисторных структур, имеющих общий коллектор, причем эмиттеры Т1 располагаются так, что взаимодействие между ними через участки пассивной базы практически отсутствуют.

ОСОБЕННОСТИ СХЕМЫ. Меньше габариты и паразитные емкости. Поэтому быстродействие выше в сравнении с ДТЛ.

Большие обратные токи эмиттерных переходов, чем диодов, снижают n.

4. ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

В настоящее время транзисторно-транзисторные ЛЭ являются наиболее распространенными интегральными микросхемами. По качественным показателям и технологичности ТТЛ существенно превосходит ДТЛ.

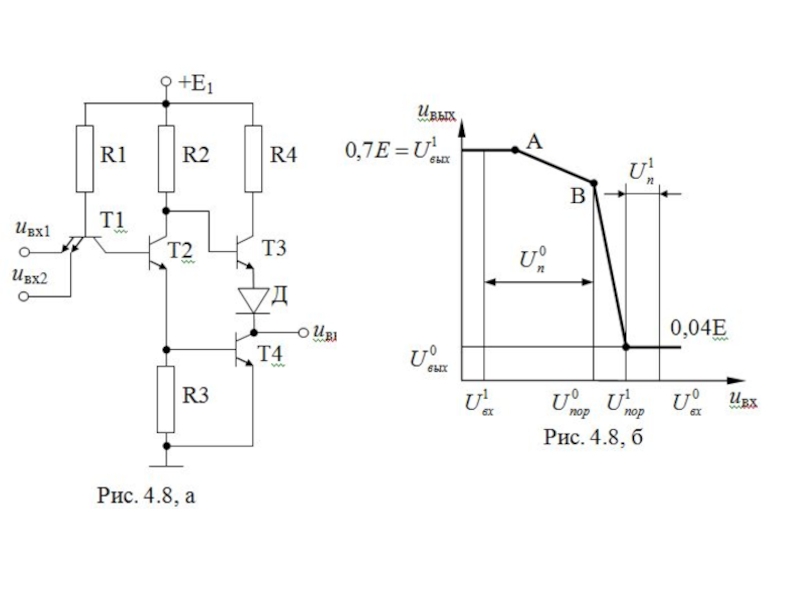

Слайд 144.2. ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СО СЛОЖНЫМ ИНВЕРТОРОМ (С ЭМИТТЕРНЫМ ПОВТОРИТЕЛЕМ)

ТТЛ

со сложным инвертором изображен на рис.4.8,а. Сложный инвертор, собранный на

транзисторах Т2, Т3 и Т4, позволяет повысить нагрузочную способность (увеличить n) и быстродействие логического элемента.

СХЕМА. Сложный инвертор состоит из простого инвертора на Т2 и R2 и эмиттерного повторителя на Т3. Роль эмиттерной нагрузки Т3 выполняет нагрузка, подключаемая к выходу ЛЭ. Транзистор Т4, резисторы R3, R4 и диод Д выполняют вспомогательные функции.

РАБОТА СХЕМЫ. Работу схемы поясним с помощью передаточной характеристики (рис.4.8,б). Соединим оба входа транзистора Т1 и будем увеличивать входное напряжение uвх от 0 до uвх > Uвх1.

При uвх1 = uвх2 ≈0 ток базы IБ1 протекает от +Е через R1, эмиттерные переходы Т1 и источник uвх1 и uвх2 на корпус. UБ1 небольшое положительное и распределяется на делителе, состоящем из коллекторного перехода Т2 и параллельно соединенных эмиттерном переходе Т4 и R3. Поэтому величины UБ1 недостаточно для отпирания этих переходов. Коллекторные переходы Т1, Т1 и Т4 – заперты. UК2 = UБ3 имеет высокий уровень ≈+Е. Т3 открыт и работает в активном режиме.

IБ3 и IКЗ образуют IЭЗ, протекающий через Д и нагрузку, подключенную к выходу. Сопротивление нагрузки велико (оно состоит, главным образом, из параллельно включенных обратных сопротивлений эмиттерных переходов Т1 последующих ЛЭ (в лабораторной работе – это входное сопротивление лампового вольтметра). Таким образом, эмиттерный повторитель (ЭП) на транзисторе Т3 имеет коэффициент передачи близкий к единице, uвых≈0,7Е=Uвых1 и соответствует высокому уровню единицы. За счет действия ООС в ЭП уровень стабилизирован. ЭП имеет малое выходное сопротивление и обеспечивает высокую нагрузочную способность (n≥12).

По мере увеличения uвх1= uвх2 увеличивается uБ1. В точке А передаточной характеристики открываются коллекторный переход Т1 и эмиттерный переход Т2. Т2 переходит в активный режим. Теперь увеличение uБ1 вызывает уменьшение uК2 = uБ3. Начинает уменьшаться uвых. Т.к. Т2 имеет в эмиттерной цепи R3, то за счет ООС (в коллекторно-эмиттерном повторителе) его коэффициент передачи в обоих плечах близок к единице. Поэтому uК2 = uБЭ3 и uвых уменьшается с той же скоростью, что увеличивается uБ1 ≈ uвч1= uвх2. При одинаковых масштабах по осям uвх и uвых передаточная характеристика имеет угол наклона . Эмиттерный переход Т4 еще остается закрытым, т.к. он зашунтирован R3.

При дальнейшем увеличении uвх1= uвх2 открывается эмиттерный переход Т4. Т4 переходит в активный режим. Он все более шунтирует нагрузку и uвых резко уменьшается (от точки В до точки С передаточной характеристики). Происходит переключение инвертора. uвых достигает низкого уровня нуля ≈0,04Е. В момент переключения резко возрастает ток потребляемый ЛЭ, т.к. Т3 и Т4 открыты. Величина этого тока ограничивается R4. В точке С Т2 и Т4 переходят в режим насыщения, а Т3 запирается. Запиранию Т3 способствует наличие диода смещения Д. Т.о. Uвых0 =UЛЭ4нас.

Поскольку сопротивление насыщенного Т4 мало, сложный инвертор сохраняет высокую нагрузочную способность.

Недостатком сложного инвертора являются броски потребляемого тока в моменты переключений, которые могут создать помехи в цепях питания. Этот недостаток ослабляется R4.

В целом такие ЛЭ находят широкое применение.

Слайд 165. ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

СО СВЯЗАННЫМИ КОЛЛЕКТОРАМИ

5.1. НЕПОСРЕДСТВЕННО СВЯЗАННЫЕ ТРАНЗИСТОРНЫЕ

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

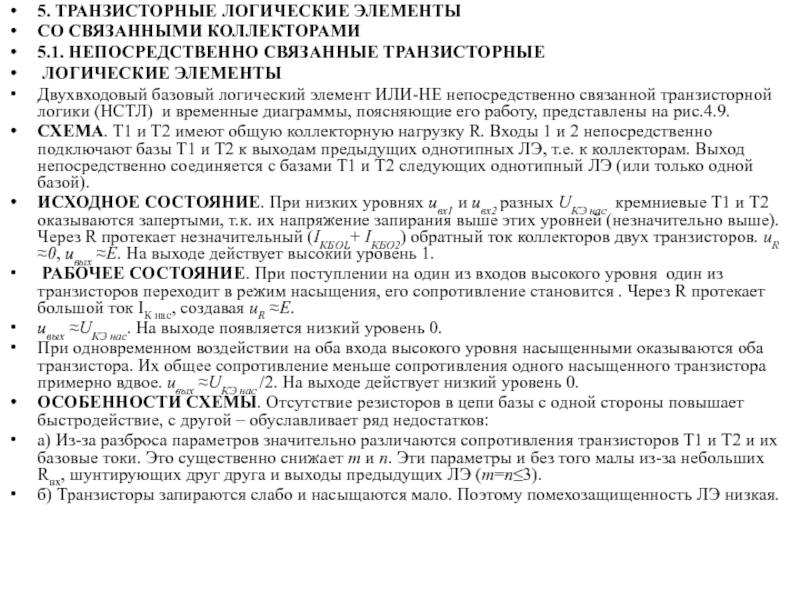

Двухвходовый базовый логический элемент ИЛИ-НЕ непосредственно связанной транзисторной логики

(НСТЛ) и временные диаграммы, поясняющие его работу, представлены на рис.4.9.

СХЕМА. Т1 и Т2 имеют общую коллекторную нагрузку R. Входы 1 и 2 непосредственно подключают базы Т1 и Т2 к выходам предыдущих однотипных ЛЭ, т.е. к коллекторам. Выход непосредственно соединяется с базами Т1 и Т2 следующих однотипный ЛЭ (или только одной базой).

ИСХОДНОЕ СОСТОЯНИЕ. При низких уровнях uвх1 и uвх2 разных UКЭ нас кремниевые Т1 и Т2 оказываются запертыми, т.к. их напряжение запирания выше этих уровней (незначительно выше). Через R протекает незначительный (IКБО1+ IКБО2) обратный ток коллекторов двух транзисторов. uR ≈0, uвых ≈Е. На выходе действует высокий уровень 1.

РАБОЧЕЕ СОСТОЯНИЕ. При поступлении на один из входов высокого уровня один из транзисторов переходит в режим насыщения, его сопротивление становится . Через R протекает большой ток IК нас, создавая uR ≈Е.

uвых ≈UКЭ нас. На выходе появляется низкий уровень 0.

При одновременном воздействии на оба входа высокого уровня насыщенными оказываются оба транзистора. Их общее сопротивление меньше сопротивления одного насыщенного транзистора примерно вдвое. uвых ≈UКЭ нас /2. На выходе действует низкий уровень 0.

ОСОБЕННОСТИ СХЕМЫ. Отсутствие резисторов в цепи базы с одной стороны повышает быстродействие, с другой – обуславливает ряд недостатков:

а) Из-за разброса параметров значительно различаются сопротивления транзисторов Т1 и Т2 и их базовые токи. Это существенно снижает m и n. Эти параметры и без того малы из-за небольших Rвх, шунтирующих друг друга и выходы предыдущих ЛЭ (m=n≤3).

б) Транзисторы запираются слабо и насыщаются мало. Поэтому помехозащищенность ЛЭ низкая.

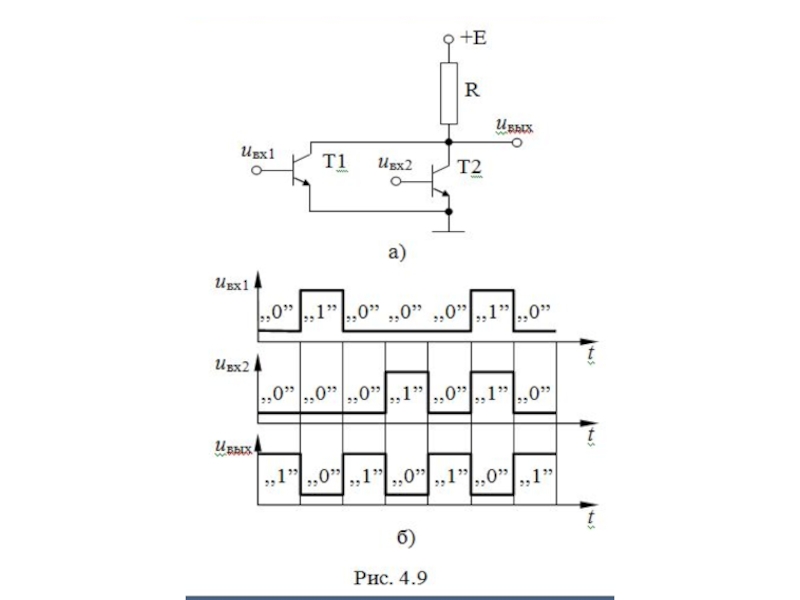

Слайд 185.2. РЕЗИСТОРНО-СВЯЗАННЫЕ ТРАНЗИСТОРНЫЕ ЛЭ

РСТЛ отличаются от НСТЛ только наличием резисторов

между входными выводами и базами, что увеличивает входные сопротивления, выравнивая

их, и уменьшает токи базы. Быстродействие несколько снижается, но увеличиваются m и n, повышается помехоустойчивость.

5.3. РЕЗИСТОРНО-КОНДЕНСАТОРНО-СВЯЗАННЫЕ ТРАНЗИСТОРНЫЕ

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ (РКСТЛ)

РКСТЛ (или РЕСТЛ) отличаются от РСТЛ наличием конденсаторов, включенных параллельно резисторам в цепях баз транзисторов. Такие входные RC-цепи являются ускоряющими, т.е. увеличивают быстродействие. РКСТЛ применяется редко, что связано со сложностью изготовления конденсаторов в ИМС и снижением степени интеграции.

Слайд 196. ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ СО СВЯЗАННЫМИ ЭМИТТЕРАМИ (ПЕРЕКЛЮЧАЮЩАЯ ТОКИ ТРАНЗИСТОРНАЯ

ЛОГИКА)

встроенный источник

Двухвходовый базовый ЛЭ ИЛИ/ИЛИ-НЕ эмиттерно-связанной логики (ЭСТЛ) изображен на

рис.4.10. Основное свойство переключающей токи транзисторной логики (ПТТЛ) заключается в том, что транзисторы переключателя работают без насыщения. Достигается это благодаря переключению постоянного тока определенного значения с помощью малого изменения управляющего напряжения (примерно десятых долей вольта).

Слайд 20СХЕМА. Транзисторы Т1, Т2, Т3, резисторы R1, R2, R3 –

переключатель тока или эмиттерно-связанный ЛЭ. Причем входные управляющие сигналы подаются

на базы Т1 и Т2. Транзистор Т3 – опорный, на его базу подается опорное напряжение UБ3 =( Uвх1+ Uвх0), где Uвх1 и Uвх0 – соответственно высокий и низкий логические уровни входных сигналов. Опорное напряжение получают с помощью встроенного источника фиксированного смещения, собранного на Т4, R4, R5, R6, диодах Д1, Д2. Подбором R5 и R6 задается величина UБ4, обеспечивающая требуемое значение UБ3= UБ4 Эмиттерный повторитель на Т4 и R4 имеет малое Rвых. Т.о. встроенный источник смещения UБ3 имеет малое внутреннее (или выходное) сопротивление. Диоды Д1, Д2 и ООС в ЭП Т4. R4 обеспечивают термостабилизацию.

Выходные сигналы снимаются с соединенных коллекторов входных транзисторов и с коллектора опорного транзистора Т3 через эмиттерные повторители (транзисторы Т5 и Т6). На первом выходе uвых1 реализуется логическая функция ИЛИ-НЕ, а на втором uвых2 – функция ИЛИ входных сигналов:

, (4.5)

Слайд 21Причем принята одинаковая кодировка входных и выходных сигналов: высокий уровень

U1 кодируется 1, низкий уровень U0 кодируется 0 (т.е. если

uвых1 = U1, то y1=0).

ПРИНЦИП РАБОТЫ ЭСТЛ. Рассмотрим вначале режим, когда на все входы действуют низкие уровни: uвх1= uвх2 =U0 (x1 =x2=0). При этом входные транзисторы Т1 и Т2 закрыты и ток в резисторе R3 протекает через опорный транзистор Т3. Потенциал в т.Б на коллекторе Т3 низкий

. (4.6)

Напряжение на базе транзистора Т6 небольшое, напряжение на выходе эмиттерного повторителя uвых2 небольшое.

Итак, u0вых2 – низкий уровень, т.е. y2 =0 и на выходе реализуется логическая функция ИЛИ входных сигналов. Напряжение на первом выходе высокое U1. Действительно, когда все входные транзисторы закрыты, потенциал в т.А высокий, транзистор Т5 сильно открыт, напряжение на выходе 1 u1вых1 =U1, т.е. y1 =1, реализуется операция ИЛИ-НЕ.

Слайд 22Рассмотрим теперь режим, когда хотя бы на одном входе, например,

первом, действует высокий уровень управляющего напряжения: uвх1=U1 (x1 =1); на

другом входе по-прежнему uвх2 =U0 (x2 =0). При этом Т1 открыт и работает в активном режиме, а другой входной транзистор закрыт. Напряжение теперь больше, чем в предыдущем случае. Благодаря увеличению uR3 транзистор Т3 закрыт. Поэтому теперь uб1 и u1вых2 – высокие уровни, т.е. y2 =1, а и соответственно uвых1 – низкие уровни, т.е. y1 =0.

Заметим, что входные транзисторы Т1, Т2 не должны насыщаться при подаче на их базы максимальных отпирающих перепадов напряжения uвх макс =U1; для этого необходимо, чтобы коллекторные переходы открытых транзисторов были бы смещены в обратном направлении (т.е. чтобы напряжение между базой и коллектором uБК) было бы отрицательно или во всяком случае не превосходило бы порогового уровня отпирания p-n перехода). Другими словами, необходимо, чтобы минимальный уровень напряжения на коллекторе (в т.А) был бы выше максимального уровня входного напряжения на базе транзистора.

ОСОБЕННОСТИ СХЕМЫ. Переключатели тока обладают высоким быстродействием, что объясняется следующими причинами:

а) ненасыщенным режимом открытых транзисторов, исключающим время рассасывания избыточных зарядов;

б) транзистор Т3 работает в режиме схемы ОБ и, кроме того, управляется по цепи эмиттера от источника с малым выходным сопротивление – эмиттерного повторителя на транзисторах Т1, Т2, что приводит к быстрому переключению Т3;

в) малым временем перезаряда паразитных емкостей на выходах Т1 (Т2) и Т3 из-за небольшой величины перепадов U0К и U1К;

г) малым временем перезаряда паразитных емкостей на Вых.1 и Вых.2 через малые Rвых ЭП (на Т и Т6).

Помехоустойчивость схемы низкая, т.к. разность U1вых- U0вх= U1вых – U0 вых = U1К – U0К невелика (десятые доли вольта).

Потребление тока от источников питания в процессе работы практически не изменяется. Потребляемая мощность сравнительно невелика.

Уровни 0 и 1 достаточно стабильны, благодаря глубокой ООС за счет RЭ в стационарных состояниях.

ПТТЛ ЛЭ обладают наивысшим быстродействием (4-6 нс), большими n и m.

7. СИСТЕМА УСЛОВНЫХ ОБОЗНАЧЕНИЙ СЕРИЙ ИМС

Различают маркировку ИМС до 1973г. и после 1973г. Например, К1Л6061А до 1973г., К106ЛБ1А после 1973г.

К – ИМС широкого применения, отсутствие К говорит о применении ИМС в специальной аппаратуре. 106 – номер серии, где 1 (или 5, 7) – полупроводниковой технологии; 2, 4, 5, 6 – гибридный; 3 – пленочный; 06 – порядковый номер разработки серии. ЛБ – логический элемент И-НЕ/ИЛИ-НЕ (ЛИ-И, ЛЛ-ИЛИ, ЛН-НЕ, ЛС-И-ИЛИ, ЛР-И-ИЛИ-НЕ, ЛК-И-ИЛИ-НЕ/И-ИЛИ, ЛИ-ИЛИ-НЕ/ИЛИ, ЛП - прочие). 1 (в конце) – порядковый номер разработки внутри серии. А – повышенное быстродействие.

![Звуки [д-д’], [т-т’] и их обозначение буквами Д, Т](/img/thumbs/44fe3d6e4146928340dd63cab5de3a56-800x.jpg)