Слайд 1Лекция

Тема: Структурная организация основной памяти

Слайд 2Функции запоминающего элемента

элемент может находится в одном из двух устойчивых

(или квазиустойчивых) состояний, одно из которых интерпретируется как хранение двоичного

кода

1, а другое — кода 0;

в элемент хотя бы один раз можно записать нужный двоичный код и таким образом целенаправленно установить его состояние;

текущее состояние элемента можно считывать.

Слайд 3Функциональная схема запоминающего элемента

а)

б)

Слайд 4Функциональная схема запоминающего элемента

Элемент имеет три вывода, по которым могут

передаваться электрические сигналы

Сигнал на выводе Выборка выбирает элемент для

выполнения операции

Сигнал на выводе Управление задает режим обращения — запись или чтение

Слайд 5Функциональная схема запоминающего элемента

В режиме записи на третий вывод, Ввод/считывание,

подается сигнал, соответствующий записываемому двоичному коду: 0 или 1

В режиме

чтения третий вывод является выходом и на нем формируется сигнал, соответствующий текущему состоянию элемента: 0 или 1

Слайд 6Логическая структура микросхемы памяти

Запоминающие элементы поступают к конструктору в виде

микросхемы, в которую "упаковано" множество ЗЭ и необходимые для поддержки

их функционирования электронные схемы

Для конструктора модулей полупроводниковой памяти ключевым является вопрос обоснованного выбора количества битов данных, считываемых/записываемых в модуль в одном цикле обращения

Слайд 7Логическая структура микросхемы памяти

Один крайний вариант — физически скомпоновать массив

ячеек в модуле таким образом, чтобы модуль имел длину слова,

соответствующую длине слова всего ЗУ

Запоминающие элементы организуются в виде массива из М слов по В битов в каждом

Например, модуль емкостью 16 Мбит физически компонуется как блок памяти, содержащий 1 М 16-битовых слов

Слайд 9Запоминающий массив

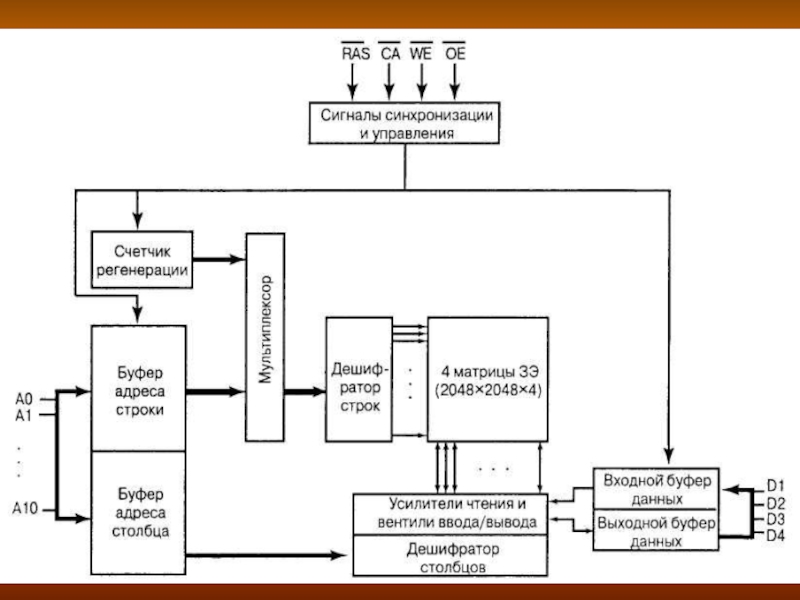

На рисунке показана типичная организация DRAM-модуля емкостью 16 Мбит,

в котором за одно обращение считывается/записывается 4 бит

Запоминающие элементы

в модуле разделены на четыре массива, каждый из которых включает матрицу элементов размером 2048x2048

Каждый элемент массива связан с одной из горизонтальных (по строкам) и одной из вертикальных (по столбцам) линий

Слайд 10Запоминающий массив

Каждая горизонтальная линия подключена к выводам Выборка запоминающих элементов

данной строки матрицы

Каждая вертикальная линия подключена к выводам Управление

запоминающих элементов соответствующего столбца матрицы

Слайд 11Работа схемы

На линии адреса подается код адреса слова, к которому

производится обращение

Количество линий адреса п связано с количеством адресуемых

слов модуля соотношением п = log2M

11 адресных линий используются для выбора одной из 2048 строк матриц

Дешифратор строк имеет 11 входов и 2048 выходов

Слайд 12Работа схемы

Еще 11 адресных линий выбирают один из 2048 столбцов

в каждой из четырех матриц

В результате на шину данных

будет передан код, считанный с элемента, который находится на пересечении выбранной строки и выбранного столбца

Четыре линии данных от четырех матриц используются для передачи записываемого 4-битового кода во входной буфер или считывания из выходного буфера кода, прочитанного из выбранных запоминающих элементов

Слайд 13Работа схемы

В режиме Запись вентиль, подключенный к выходу соответствующего разряда

входного буфера, передает 0 или 1

В режиме Чтение значение с

вывода считывания матрицы передается через усилитель чтения на линию данных, соответствующую номеру матрицы

Слайд 14Работа схемы

Поскольку с одного модуля за одно обращение считывается только

4 бит, запоминающее устройство должно включать несколько однотипных DRAM-модулей, которые

в совокупности и образуют слово нужной длины, передаваемое контроллером памяти на системную магистраль

Слайд 15Работа схемы

Модуль содержит только 11 адресных выводов — ровно половину

от того количества, которое необходимо для адресации 2048х2048=222 элементов

Применяется

последовательная передача 22-разрядного кода адреса порциями по 11 бит по одним и тем же линиям

Слайд 16Работа схемы

Первые 11 бит направляются в схему выборки строки и

сопровождаются внешним сигналом RAS (row address select)

Вторые 11 бит направляются

в схему выборки столбца и сопровождаются внешним сигналом CAS (column address select)

Слайд 17Работа схемы

В составе обрамления DRAM-модуля имеется схема управления регенерацией

При

регенерации обращение к модулю запрещается на время обновления данных во

всех запоминающих элементах

Счетчик регенерации перебирает все номера строк матрицы, и соответственно формируется сигнал выборки строки на выходе дешифратора

Этим сигналом обновляются данные во всех элементах данной строки

Слайд 19RAS (row address select) в схему выборки строки;

CAS (column address

select) в схему выборки столбца;

WE (write enable) - режим записи;

ОЕ

(output enable ) - режим чтения;

Vcc – питание;

Vss – нулевая шина питания;

NC - No Connection - свободный вывод.

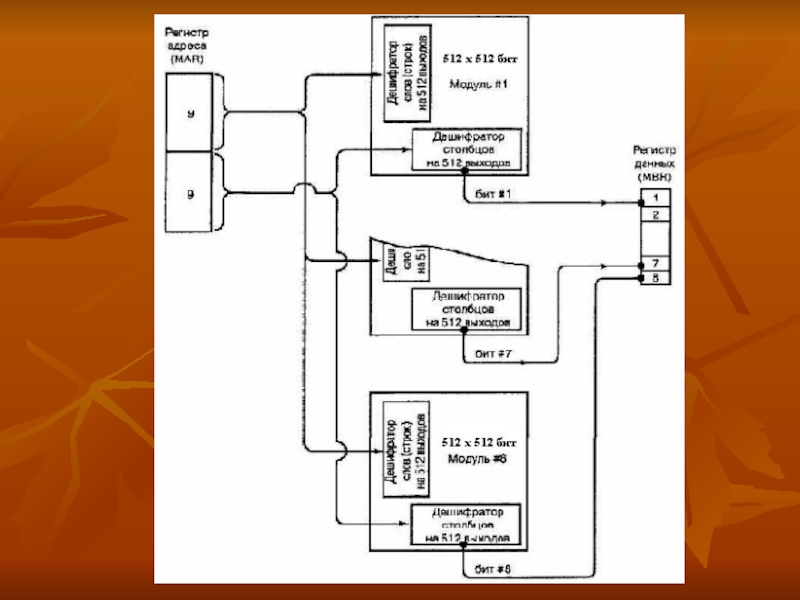

Слайд 20Организация ЗУ из нескольких модулей

Если для построения ЗУ выбраны модули

с организацией 1 бит в корпусе, то потребуется столько модулей,

сколько битов в машинном слове

Рассмотрим структурную схему ЗУ емкостью 256 Кбайт, построенного из RAM-модулей емкостью по 256 Кбит каждый

Слайд 22Организация ЗУ из нескольких модулей

Для адресации одной из 256К ячеек

необходим 18-разрядный код адреса (218= 256К), который поступает в ЗУ

с линий адреса системной магистрали

Контроллер ЗУ передает этот адрес параллельно на все 8 RAM-модулей и получает от каждого один бит выбранного байта

Слайд 23Организация ЗУ из нескольких модулей

Если же требуется построить ЗУ большего

объема, нужно организовать модули в виде массива

Слайд 25Организация ЗУ из нескольких модулей

Емкость рассматриваемого ЗУ 1 Мбайт

В качестве

элементной базы использованы все те же RAM-модули емкостью 256 Кбит

с организацией 256Кх1

Модули организованы в виде матрицы из четырех столбцов

Для адресации 1М слов потребуется 20-разрядный код адреса

Слайд 26Организация ЗУ из нескольких модулей

Младшие 18 разрядов направляются параллельно на

все 32 RAM-модуля устройства

Два старших разряда направляются на вход дешифратора

выбора столбца модулей